LC78857V

# Digital Audio D/A Converter IC with On-Chip Digital Filters

# Preliminaly

# **Overview**

The LC78857V is a sigma-delta type D/A converter for use in digital audio systems. It provides both digital and analog filters on chip.

# **Features**

- Built-in 8x oversampling digital filters: 3-stage FIR structure (31st order, 11th order, and 3rd order filters)

- Analog low-pass filter

- Digital deemphasis (handles Fs = 44.1 kHz operation)

- Digital attenuator

- Soft muting

- Supports a 384fs system clock rate.

- 5-V single-voltage power supply

- Fabricated in a silicon gate CMOS process.

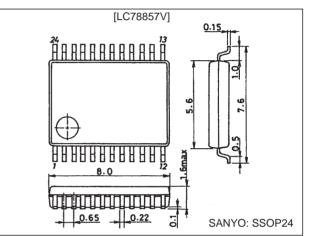

# Package Dimensions

unit: mm

3175A-SSOP24

# Specifications

#### Absolute Maximum Ratings at $V_{SS} = 0 V$

| Parameter              | Symbol              | Conditions | Ratings                      | Unit |

|------------------------|---------------------|------------|------------------------------|------|

| Maximum supply voltage | V <sub>DD</sub> max |            | -0.3 to +7.0                 | V    |

| Input voltage          | V <sub>IN</sub>     |            | –0.3 to V <sub>DD</sub> +0.3 | V    |

| Output voltage         | V <sub>OUT</sub>    |            | –0.3 to V <sub>DD</sub> +0.3 | V    |

| Operating temperature  | Topr                |            | -30 to +75                   | °C   |

| Storage temperature    | Tstg                |            | -40 to +125                  | °C   |

#### Allowable Operating Ranges at $Ta = 25^{\circ}C$

| Parameter             | Symbol Conditions - |  | Ratings |     |                 | Unit |

|-----------------------|---------------------|--|---------|-----|-----------------|------|

| Falameter             |                     |  | min     | typ | max             | Unit |

| Supply voltage        | V <sub>DD</sub>     |  | 3.5     | 5.0 | 5.5             | V    |

| Input voltage         | T <sub>IN</sub>     |  | 0       |     | V <sub>DD</sub> | V    |

| Operating temperature | Topr                |  | -30     |     | +75             | °C   |

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-0005 JAPAN

# DC Characteristics at Ta = –30 to $75^\circ C,\,V_{DD}$ = 3.5 to 5.5 V, $V_{SS}$ = 0 V

| Parameter                    | Cumbol            | Conditions                                                                                          |                     | Ratings |                     | 1.1  |  |

|------------------------------|-------------------|-----------------------------------------------------------------------------------------------------|---------------------|---------|---------------------|------|--|

| Parameter                    | Symbol            | Conditions                                                                                          | min                 | typ     | max                 | Unit |  |

| Input high-level voltage (1) | V <sub>IH</sub> 1 | Pin 15                                                                                              | 0.7 V <sub>DD</sub> |         |                     | V    |  |

| Input low-level voltage (1)  | V <sub>IL</sub> 1 | Pin 15                                                                                              |                     |         | 0.3 V <sub>DD</sub> | V    |  |

| Input high-level voltage (2) | V <sub>IH</sub> 2 | Pins 6, 7, 8, 9, 10, 11, 14, 18, and 19                                                             | 2.2                 |         |                     | V    |  |

| Input low-level voltage (2)  | V <sub>IL</sub> 2 | Pins 6, 7, 8, 9, 10, 11, 14, 18, and 19                                                             |                     |         | 0.8                 | V    |  |

| Output high-level voltage    | V <sub>OH</sub>   | I <sub>OH</sub> = –3 mA, pin 17                                                                     | 2.4                 |         |                     | V    |  |

| Output low-level voltage     | V <sub>OL</sub>   | I <sub>OL</sub> = 3 mA, pin 17                                                                      |                     |         | 0.4                 | V    |  |

| Input leakage current        | IL.               | V <sub>I</sub> = V <sub>SS</sub> , V <sub>DD</sub> :<br>Pins 6, 7, 8, 9, 10, 11, 14, 15, 18, and 19 | -25                 |         | 25                  | μA   |  |

| Allowable power dissipation  | Pd                | V <sub>DD</sub> = 5.0 V                                                                             |                     | 135     | 200                 | mW   |  |

# AC Characteristics at Ta = –30 to $75^\circ C,\,V_{DD}$ = 3.5 to 5.5 V, $V_{SS}$ = 0 V

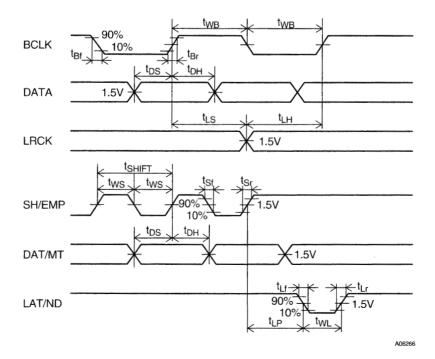

| Deverseden             | Querra ha a l      | Quantitiana. |      | Ratings |      | Unit |

|------------------------|--------------------|--------------|------|---------|------|------|

| Parameter              | Symbol             | Conditions   | min  | typ     | max  |      |

| Oscillator frequency   | f <sub>X</sub>     |              |      | 169     | 18.5 | MHz  |

| BCLK frequency         | f <sub>BCX</sub>   |              |      |         | 3.0  | MHz  |

| BCLK pulse width       | t <sub>WB</sub>    |              | 100  |         |      | ns   |

| BCLK rise time         | t <sub>Br</sub>    |              |      |         | 30   | ns   |

| BCLK fall time         | t <sub>Bf</sub>    |              |      |         | 30   | ns   |

| DATA setup time        | t <sub>DS</sub>    |              | 20   |         |      | ns   |

| DATA hold time         | t <sub>DH</sub>    |              | 20   |         |      | ns   |

| LRCK setup time        | t <sub>LS</sub>    |              | 50   |         |      | ns   |

| LRCK hold time         | t <sub>LH</sub>    |              | 50   |         |      | ns   |

| SH/EMP pulse period    | t <sub>SHIFT</sub> |              | 1000 |         |      | ns   |

| SH/EMP pulse width     | t <sub>WS</sub>    |              | 300  |         |      | ns   |

| SH/EMP rise time       | t <sub>Sr</sub>    |              |      |         | 100  | ns   |

| SH/EMP fall time       | t <sub>Sf</sub>    |              |      |         | 100  | ns   |

| LAT/ND pulse width     | t <sub>WL</sub>    |              | 300  |         |      | ns   |

| Latch pulse input time | t <sub>LP</sub>    |              | 300  |         |      | ns   |

| LAT/ND rise time       | t <sub>Lr</sub>    |              |      |         | 100  | ns   |

| LAT/ND fall time       | t <sub>Lf</sub>    |              |      |         | 100  | ns   |

# **Timing Chart**

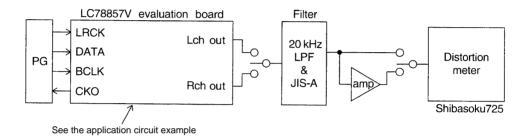

#### Analog Characteristics at Ta = $25^{\circ}$ C, V<sub>DD</sub> = 5.0 V

| Parameter                 | Symbol | Conditions    |     |       | Unit  |      |

|---------------------------|--------|---------------|-----|-------|-------|------|

| Falanielei                | Symbol | Conditions    | min | typ   | max   | Unit |

| Total harmonic distortion | THD+N  | 1kHz, 0 dB    |     | 0.008 | 0.012 | %    |

| Signal-to-noise ratio     | S/N    | JIS-A         | 90  | 96    |       | dB   |

| Crosstalk                 | СТ     | 1kHz, 0 dB    | 88  | 92    |       | dB   |

| Full scale output level   | VFS    | 1 kHz, 0dB    | 2.8 | 3.0   | 3.2   | Vp-p |

| Dynamic range             | DR     | JIS-A         | 84  | 87    |       | dB   |

| Output load resistance    | RL     | Pins 2 and 23 | 5   |       |       | kΩ   |

### **Test Circuit**

PG: Pattern generator (signal generator) Filter: Band limiting filter

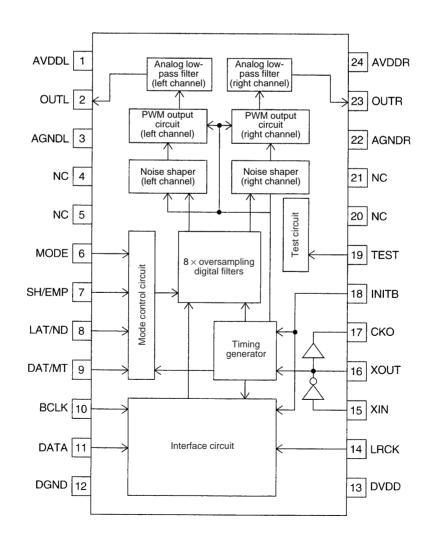

#### **Block Diagram**

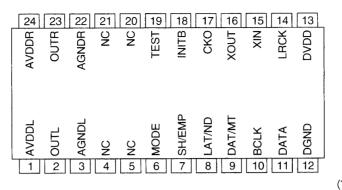

# Pin Assignment

(Top view)

A06269

#### **Pin Functions**

|         |                  | 1                                                                                                                                   |  |  |  |  |

|---------|------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin No. | Symbol           | Function                                                                                                                            |  |  |  |  |

| 1       | AVDDL            | nalog system power supply (left channel)                                                                                            |  |  |  |  |

| 2       | OUTL             | nalog output (left channel)                                                                                                         |  |  |  |  |

| 3       | AGNDL            | nalog system ground (left channel)                                                                                                  |  |  |  |  |

| 4       | NC               | No Connection                                                                                                                       |  |  |  |  |

| 5       | NC               |                                                                                                                                     |  |  |  |  |

| 6       | MODE             | Serial/parallel input mode selection                                                                                                |  |  |  |  |

| 7       | SH/EMP           | When MODE is low: Control data shift signal (serial mode)<br>When MODE is high: Emphasis on/off switching (parallel mode)           |  |  |  |  |

| 8       | LAT/ND           | When MODE is low: Control data latch signal (serial mode)<br>When MODE is high: normal speed/double speed switching (parallel mode) |  |  |  |  |

| 9       | DAT/MT           | When MODE is low: Control data input (serial mode)<br>When MODE is high: Soft muting control input (parallel mode)                  |  |  |  |  |

| 10      | BCLK             | Bit clock input                                                                                                                     |  |  |  |  |

| 11      | DATA             | Digital audio data input                                                                                                            |  |  |  |  |

| 12      | DGND             | Digital system ground                                                                                                               |  |  |  |  |

| 13      | DV <sub>DD</sub> | Digital system power supply                                                                                                         |  |  |  |  |

| 14      | LRCK             | LR clock input                                                                                                                      |  |  |  |  |

| 15      | XIN              | Crystal oscillator element input                                                                                                    |  |  |  |  |

| 16      | XOUT             | Crystal oscillator element output                                                                                                   |  |  |  |  |

| 17      | СКО              | Clock output (384fs)                                                                                                                |  |  |  |  |

| 18      | INITB            | Initialization signal input (The IC internal state is initialized on a low input.)                                                  |  |  |  |  |

| 19      | TEST             | Test pin (This pin must be connected to DGND during normal operation.)                                                              |  |  |  |  |

| 20      | 20               |                                                                                                                                     |  |  |  |  |

| 21      | NC               | No Connection                                                                                                                       |  |  |  |  |

| 22      | AGNDR            | Analog system ground (right channel)                                                                                                |  |  |  |  |

| 23      | OUTR             | Analog output (right channel)                                                                                                       |  |  |  |  |

| 24      | AVDDR            | Analog system power supply (right channel)                                                                                          |  |  |  |  |

#### **Circuit Operation**

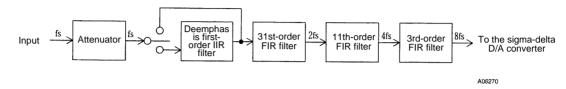

The LC78857V consists of three main blocks: the digital filter block, the sigma-delta D/A converter block, and the analog filter block.

[Digital Filter Block]

The LC78857V performs the following calculations.

• Normal speed mode:

• Double speed mode:

This mode is used, for example, when dubbing a CD to cassette tape at double speed. Although the XIN has the same frequency as normal speed mode, BCLK, LRCK, and DATA are input at twice the rate used in normal speed.

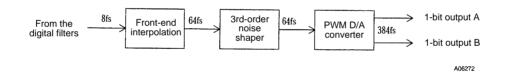

#### [Sigma-Delta D/A Converter Block]

This circuit accepts 8fs data input and outputs a 384fs 1-bit data sequence.

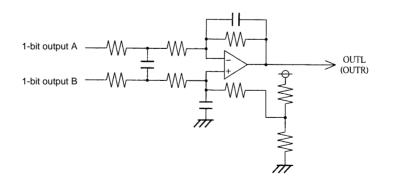

[Analog Low-Pass Filter Block]

This block consists of an analog low-pass filter that consists of on-chip resistors, capacitors, and operational amplifiers. This block converts the 384fs 1-bit data streams A and B directly to an analog voltage output.

A06273

#### Input Setup

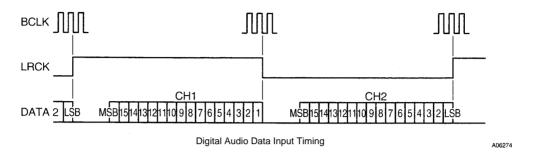

1. Digital audio data input

The digital audio data is a 16-bit serial signal in an MSB-first two's complement format. The 16-bit serial data is input from the DATA pin to an internal register on the rising edge of the BCLK signal, and is read in on the rising and falling edges of the LRCK signal.

2. Mode setup

The method used to set the speed (normal/double), deemphasis, and digital attenuator settings differs depending on the state of the mode pin (MODE).

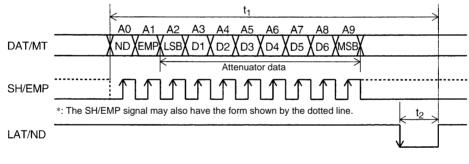

• When MODE is low: serial input mode

In this mode, the speed (normal/double), deemphasis, and digital attenuator settings are set by inputting serial data to the DAT/MT pin.

<Data Format>

Notes:DAT/MT and SH/EMP: These pins must be held fixed (low or high) at all times other than the data transfer period (t1 in the figure). LAT/ND: This pin must be held high at all times other than during data acquisition.

• A0 (ND): Normal/double speed flag

• A1 (EMP): Deemphasis flag

| A0 (ND) | Normal/double speed | A1 (EMP) | Deemphasis |

|---------|---------------------|----------|------------|

| L       | Normal speed        | L        | Off        |

| Н       | Double speed        | Н        | On         |

The deemphasis function supports operation at fs = 44.1 kHz.

A06275

• Attenuator data

The signal can be attenuated by inputting attenuation data (A2 to A9).

The attenuation specified by the attenuation data is given by the following formula:

$20 \cdot \log \left( \frac{\text{Attenuation data}}{128} \right)$  (dB) Note: The attenuation is 0 dB when the data value is 7F (hexadecimal).

However, if A9 (the MSB) is 1, the A2 to A data is ignored and the prior attenuation setting is retained.

|     |    |    | Attenua | tion data |    |    |     |                        |

|-----|----|----|---------|-----------|----|----|-----|------------------------|

| MSB |    |    |         |           |    |    | LSB | Attenuation level (dB) |

| A9  | A8 | A7 | A6      | A5        | A4 | A3 | A2  |                        |

| 0   | 1  | 1  | 1       | 1         | 1  | 1  | 1   | 0                      |

| 0   | 1  | 1  | 1       | 1         | 1  | 1  | 0   | -0.137                 |

| •   | •  | •  | •       | •         | •  | •  | •   | •                      |

| •   | •  | •  | •       | •         | •  | •  | •   | •                      |

| •   | •  | •  | •       | •         | •  | •  | •   | •                      |

| 0   | 0  | 0  | 0       | 0         | 0  | 0  | 1   | -42.14                 |

| 0   | 0  | 0  | 0       | 0         | 0  | 0  | 0   |                        |

If the attenuation level is changed from 0 dB to  $-\infty$  dB, the IC performs a soft muting operation. The soft muting time is  $1/Fs \times 1024$ . Also, the time required to change the attenuation follows the slope of the soft muting function.

If new attenuation data is input while the attenuation is changing, the attenuation level starts to change from the current level to the newly specified level at that point.

Note: If the IC is initialized when the MODE pin is low, the IC is initialized with serial data values of A0 = A1 = A9 = low, and A2 to A8 = high.

However, the LAT/ND must be held high during this initialization.

• When MODE is high: parallel input mode

In this mode, the speed (normal/double), deemphasis, and soft muting settings are specified with the LAT/ND, SH/EMP, and DAT/MT pins. It is not possible to set the attenuation data in this mode.

· Normal speed/double speed setting

| LAT/ND | Normal/double speed |

|--------|---------------------|

| L      | Normal speed        |

| Н      | Double speed        |

| · Deemphasis | setting |

|--------------|---------|

|--------------|---------|

| SH/EMP | Deemphasis |  |  |  |

|--------|------------|--|--|--|

| L      | Off        |  |  |  |

| H On   |            |  |  |  |

| TT1 1  |            |  |  |  |

The deemphasis function supports operation at fs = 44.1 kHz.

$\cdot$  Soft muting setting

The LC78857V uses the digital attenuator to implement a soft muting function. If the input level applied to the DAT/MT pin is changed from low to high, the attenuation changes from 0 dB to  $-\infty$  dB. Inversely, if the DAT/MT pin is changed from high to low, the attenuation changes from  $-\infty$  dB to 0 dB.

The time required for the change is  $1/fs \times 1024$ .

| DAT/MT | Soft muting |

|--------|-------------|

| L      | Off         |

| Н      | On          |

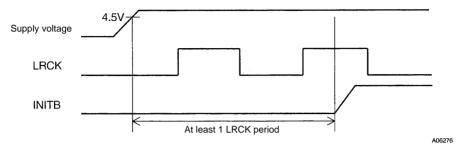

#### 3. Initialization

This IC requires initialization when power is first applied and for system operation switching. After the power-supply voltage has stabilized and XIN, BCLK, and LRCK have been supplied, initialization is achieved by holding the INITB pin at the low level for at least one LRCK period as shown in the figure below. When INITB is low, the digital filter outputs and the noise shaper (sigma-delta D/A converter) internal states are all set to 0, and the analog outputs (OUTL and OUTR) go to the zero cross level.

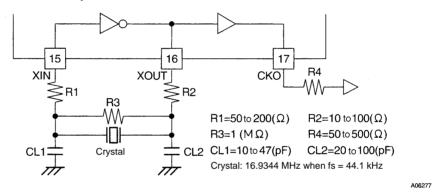

#### System Clock

The LC78857V operates from a 384fs system clock.

The 384fs system clock is generated using a crystal oscillator circuit consisting of a crystal element, resistors, and capacitors as shown in the figure. Optimal values for the resistors and capacitances depend on the peripheral circuits and other conditions. The sigma-delta D/A converter is a sensitive circuit, and the analog characteristics are strongly influenced by the quality of the waveform (e.g. its jitter characteristics) of the system clock input to the XIN pin. When an external signal is input as the system clock, adequate care must be taken to assure the quality of this signal's waveform.

$\cdot$  CKO: Outputs a clock signal with the same frequency as the signal input to the XIN pin.

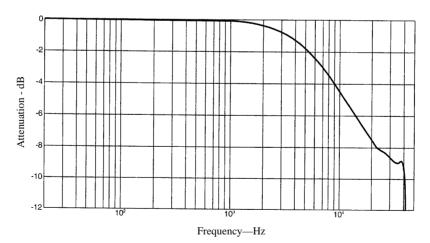

#### **Digital Filter Characteristics**

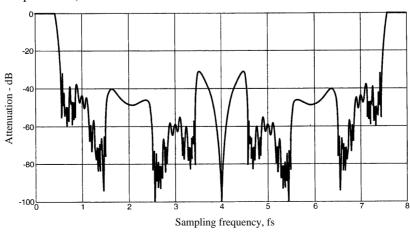

- 1. Frequency characteristics

- · Normal speed (deemphasis off)

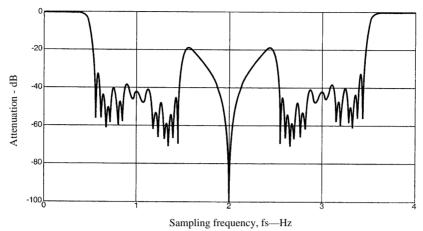

· Double speed (deemphasis off)

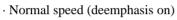

2. Deemphasis on pass band characteristics

· Double speed (deemphasis on)

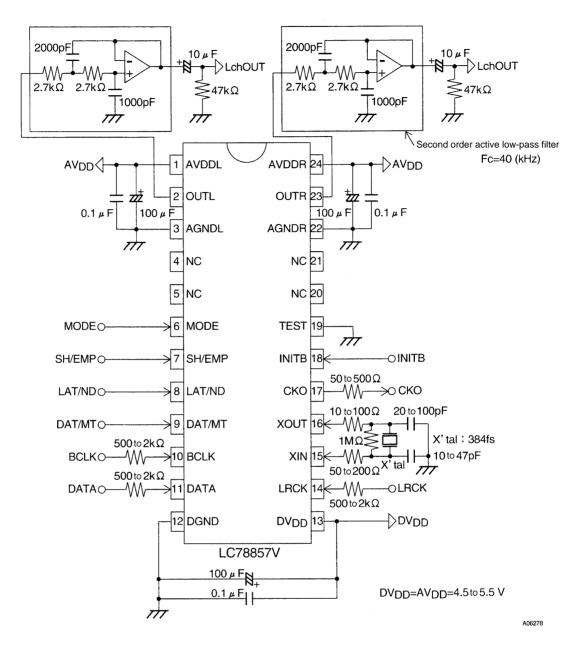

#### **Sample Application Circuit**

Notes: • All DV<sub>DD</sub> nodes in the circuit diagram must be connected to the digital system power supply, and all AV<sub>DD</sub> nodes must be connected to the analog system power supply.

• Since latchup may occur if there is a discrepancy in the times at which the DV<sub>DD</sub> and AV<sub>DD</sub> voltages are applied, applications must be designed so that there is no time difference between the points when these voltages are applied.

· If there is a potential difference between the DV<sub>DD</sub> and AV<sub>DD</sub> voltages, it must not exceed 0.3 V.

The application circuit example is an actual application circuit. Appropriate band limiting filters, which prevent adverse influence of band noise, are required to acquire the analog characteristics listed in the electrical characteristics.

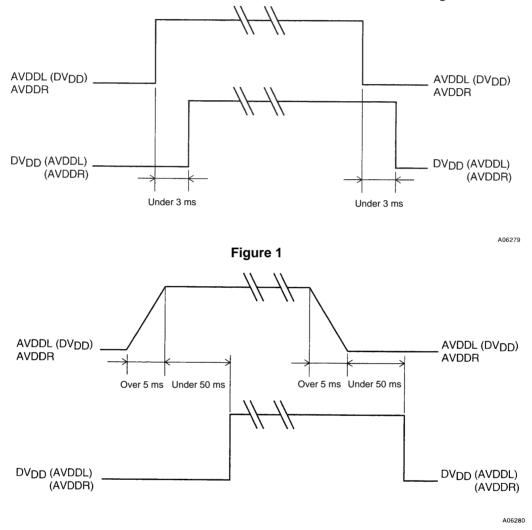

#### **Power Supply Timing**

- The analog system power supplies (AVDDL and AVDDR) and the digital system power supply  $(DV_{DD})$  must be applied and cut at the same time.

- If time lags between these power supplies are unavoidable, the timing must meet one of the following two conditions.

- (1) The power on (and power off) time lag must be under 3 ms as shown in figure 1.

- (2) If the time lag must be over 3 ms, then the rise time for the first power supply to be powered on (or powered off) must exceed 5 ms, and furthermore, the time difference must exceed 50 ms as shown in figure 2.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of December, 1997. Specifications and information herein are subject to change without notice.