# 87C196KT/87C196KS ADVANCED 16-BIT CHMOS MICROCONTROLLER

Automotive

$(-40^{\circ}\text{Ct} + 125^{\circ}\text{C Ambient})$

- High Performance CHMOS 16-Bit CPU

- Up to 32 Kbytes of On-Chip EPROM

- Up to 1 Kbyte of On-Chip Register RAM

- Up to 512 Bytes of Additional RAM (Code RAM)

- Register-Register Architecture

- 8 Channel/10-Bit A/D with Sample/Hold

- 37 Prioritized Interrupt Sources

- Up to Seven 8-Bit (56) I/O Ports

- Full Duplex Serial I/O Port

- Dedicated Baud Rate Generator

- Interprocessor Communication Slave Port

- Selectable Bus Timing Modes for Flexible Interfacing

- Oscillator Fail Detection Circuitry

- High Speed Peripheral Transaction Server (PTS)

- Two Dedicated 16-Bit High-Speed Compare Registers

- 10 High Speed Capture/Compare (EPA)

- Full Duplex Synchronous Serial I/O Port (SSIO)

- Two Flexible 16-Bit Timer/Counters

- Quadrature Counting Inputs

- Flexible 8-/16-Bit External Bus (Programmable)

- Programmable Bus (HLD/HLDA)

- 1.75 µs 16 x 16 Multiply

- 3 µs 32/16 Divide

- 68-Pin PLCC Package

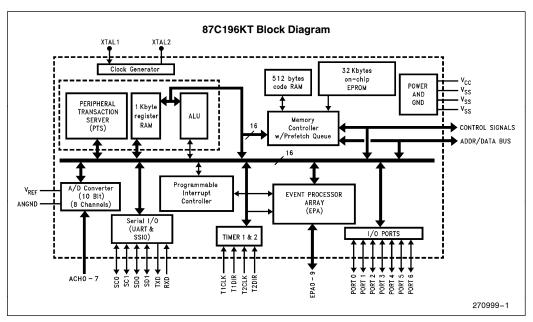

The 87C196Kx devices represents the 4th generation of MCS® 96 microcontroller products implemented on Intel's advanced 1 micron process technology. These products are based on the 80C196KB device with enhancements ideal for automotive applications. The instruction set is a true super set of the 80C196KB with a few new instructions.

The MCS 96 microcontroller family members are all high performance microcontrollers with a 16-bit CPU. The 87C196KT is composed of the high speed (16 MHz) KX macrocore as well as the following peripherals: Up to 32 Kbytes of Program EPROM, up to 1 Kbytes of Register RAM (00-3FFH including SFRs), up to 512 bytes of code RAM (16-bit addressing modes) with the ability to execute from this RAM space, an eight channel-10 Bit  $\pm$ 3LSB analog to digital converter with programmable S/H times with conversion times <20  $\mu$ s at 16 MHz, an asynchronous/synchronous serial I/O port (8096 compatable) with a dedicated 16-bit baud rate generator, an additional synchronous serial I/O port with full duplex master/slave transceivers, a flexible timer/counter structure with prescaler, cascading, and quadrature capabilities, 10 modularized multiplexed high speed I/O for capture and compare (called Event Processor Array) with 250 ns resolution and double buffered inputs, and a sophisticated prioritized interrupt structure with programmable Peripheral Transaction Server (PTS). The PTS has several channel modes, including single/burst block transfers from any memory location to any memory location, a PWM and PWM toggle mode to be used in conjunction with the EPA, and an A/D scan mode.

Additional SFR space is allocated for the EPA and can be "windowed" into the lower Register RAM area.

#### NOTICE:

This datasheet contains information on products in production. The specifications are subject to change without notice. Verify with your local Intel Sales office that you have the latest data sheet before finalizing a design.

\*Other brands and names are the property of their respective owners.

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errate.

November 1995

Order Number: 270999-007

| Device   | Pins/Package | EPROM | Reg RAM | Code RAM | 1/0 | EPA | SIO | SSIO | A/D |

|----------|--------------|-------|---------|----------|-----|-----|-----|------|-----|

| 87C196KT | 68-Pin PLCC  | 32K   | 1K      | 512b     | 56  | 10  | Υ   | Υ    | 8   |

| 87C196KS | 68-Pin PLCC  | 24K   | 1K      | 256b     | 56  | 10  | Υ   | Υ    | 8   |

#### NOTE:

This is a PRODUCT PREVIEW DATA SHEET. The AC and DC parameters contained within this data sheet may change after full automotive temperature characterization of the device has been performed. Contact your local sales office before finalizing the Timing and D.C. characteristics of a design to verify you have the latest information.

#### **ARCHITECTURE**

The KT/KS are new members of the MCS-96 family having the same architecture and use the same instruction set as the 80C196KB. Many new features have been added including:

### **CPU FEATURES**

- **■** Powerdown and Idle Modes

- 16 MHz Operating Frequency

- A High Performance Peripheral Transaction Server (PTS)

- **■** 37 Interrupt Vectors

- Up to 512 Bytes of Additional Code

- Up to 1 Kbyte of Additional Register RAM

- "Windowing" Allows 8-Bit Addressing to some 16-Bit Addresses

- 1.75 µs 16 x 16 Multiply

- 3 µs 32/16 Divide

- Oscillator Fail Detect Circuitry

### **PERIPHERAL FEATURES**

- Programmable A/D Conversion and S/H Times

- 10 Capture/Compare I/O with 2 Flexible Timers (250 ns Resolution and Double Buffered Inputs)

- Synchronous Serial I/O Port for Full Duplex Serial I/O

- Synchronous/Asynchronous Serial I/O Port (with Dedicated 16-Bit Baud Rate Generator)

- Total Utilization of ALL Available Pins (I/O Mux'd with Control)

- (2) 16-Bit Timers with Prescale, Cascading, and Quadrature Counting Capabilities

- Up to 12 Externally Triggered Interrupts

#### **NEW INSTRUCTIONS**

XCH/XCHB Exchange the contents of two locations, either Word or Byte is support-

ons, enner word or byte is

ed.

BMOVI Interruptable Block Move Instruction, allows the user to be interrupted dur-

ing long executing Block Moves.

TIJMP Table Indirect JUMP. This instruction incorportes a way to do complex

CASE level branches through one instruction. An example of such code savings: several interrupt sources and only one interrupt vector. The TIJMP instruction will sort through the sources and branch to the appropriate subcode level in one instruction. This instruction was added especially for the EPA structure, but has other code sav-

ing advantages.

EPTS/DPTS Enable and Disable Interrupts (Works

like EI and DI).

#### SFR OPERATION

A total of 1 Kbyte of Register RAM is implemented on the 87C196KT/KS devices. These locations support the on-chip peripherals that the 87C196KT/KS has (SFR's), as well as offering a data storage area. These locations are all 8-bit directly addressable by use of the windowing technique. Any 32-, 64- or 128-byte section can be relocated into the upper 32-, 64-or 128-byte area of the Register RAM area 080H-0FFH.

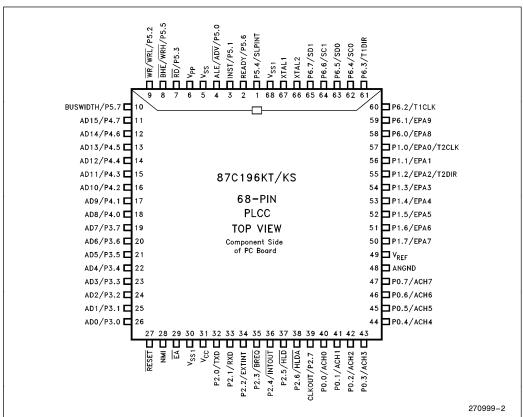

## PIN DESCRIPTIONS

| Symbol                                                | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>                                       | Main supply voltage (+5V).                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>SS</sub> , V <sub>SSI</sub> , V <sub>SSI</sub> | Digital circuit ground (0V). There are three V <sub>SS</sub> pins, all of which MUST be connected.                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>REF</sub>                                      | Reference for the A/D converter ( $\pm$ 5V). V <sub>REF</sub> is also the supply voltage to the analog portion of the A/D converter and the logic used to read Port 0. Must be connected for A/D and Port 0 to function.                                                                                                                                                                                                                                                             |

| V <sub>PP</sub>                                       | Programming voltage for the EPROM parts. It should be $\pm$ 12.5V for programming. It is also the timing pin for the return from powerdown circuit. Connect this pin with a 1 $\mu$ F capacitor to V <sub>SS</sub> and a 1 M $\Omega$ resistor to V <sub>CC</sub> . If this function is not used, V <sub>PP</sub> may be tied to V <sub>CC</sub> .                                                                                                                                   |

| ANGND                                                 | Reference ground for the A/D converter. Must be held at nominally the same potential as $V_{SS}$ .                                                                                                                                                                                                                                                                                                                                                                                   |

| XTAL1                                                 | Input of the oscillator inverter and the internal clock generator.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| XTAL2                                                 | Output of the oscillator inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P2.7/CLKOUT                                           | Output of the internal clock generator. The frequency is $1/2$ the oscillator frequency. It has a 50% duty cycle. Also LSIO pin.                                                                                                                                                                                                                                                                                                                                                     |

| RESET                                                 | Reset input to the chip. Input low for at least 16 state times will reset the chip. The subsequent low to high transition resynchronizes CLKOUT and commences a 10-state time sequence in which the PSW is cleared, bytes are read from 2018H and 201AH loading the CCBs, and a jump to location 2080H is executed. Input high for normal operation. RESET has an internal pullup.                                                                                                   |

| P5.7/BUSWIDTH                                         | Input for bus width selection. If CCR bit 1 is a one and CCR1 bit 2 is a one, this pin dyamically controls the Buswidth of the bus cycle in progress. If BUSWIDTH is low, an 8-bit cycle occurs, if BUSWIDTH is high, a 16-bit cycle occurs. If CCR bit 1 is "0" and CCR1 bit 2 is "1", all bus cycles are 8-bit, if CCR bit 1 is "1" and CCR1 bit 2 is "0", all bus cycles are 16-bit. CCR bit 1 = "0" and CCR1 bit 2 = "0" is illegal. Also an LSIO pin when not used as BUSWIDTH. |

| NMI                                                   | A positive transition causes a non maskable interrupt vector through memory location 203EH.                                                                                                                                                                                                                                                                                                                                                                                          |

| P5.1/INST                                             | Output high during an external memory read indicates the read is an instruction fetch. INST is valid throughout the bus cycle. INST is active only during external memory fetches, during internal EPROM fetches INST is held low. Also LSIO when not INST.                                                                                                                                                                                                                          |

| ĒĀ                                                    | Input for memory select (External Access). $\overline{EA}$ equal to a high causes memory accesses to locations 2000H through 9FFFH to be directed to on-chip EPROM/ROM. $\overline{EA}$ equal to a low causes accesses to these locations to be directed to off-chip memory. $\overline{EA} = +12.5 \text{V}$ causes execution to begin in the Programming Mode. $\overline{EA}$ is latched at reset.                                                                                |

| P5.0/ALE/ADV                                          | Address Latch Enable or Address Valid output, as selected by CCR. Both pin options provide a latch to demultiplex the address from the address/data bus. When the pin is ADV, it goes inactive (high) at the end of the bus cycle. ADV can be used as a chip select for external memory. ALE/ADV is active only during external memory accesses. Also LSIO when not used as ALE.                                                                                                     |

| P5.3/RD                                               | Read signal output to external memory. $\overline{\text{RD}}$ is active only during external memory reads or LSIO when not used as $\overline{\text{RD}}$ .                                                                                                                                                                                                                                                                                                                          |

| P5.2/WR/WRL                                           | Write and Write Low output to external memory, as selected by the CCR, $\overline{WR}$ will go low for every external write, while $\overline{WRL}$ will go low only for external writes where an even byte is being written. $\overline{WR/WRL}$ is active during external memory writes. Also an LSIO pin when not used as $\overline{WR/WRL}$ .                                                                                                                                   |

## PIN DESCRIPTIONS (Continued)

| Symbol                          | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P5.5/BHE/WRH                    | Byte High Enable or Write High output, as selected by the CCR. $\overline{BHE}=0$ selects the bank of memory that is connected to the high byte of the data bus. $A0=0$ selects that bank of memory that is connected to the low byte. Thus accesses to a 16-bit wide memory can be to the low byte only $(A0=0,\overline{BHE}=1)$ , to the high byte only $(A0=1,\overline{BHE}=0)$ or both bytes $(A0=0,\overline{BHE}=0)$ . If the $\overline{WRH}$ function is selected, the pin will go low if the bus cycle is writing to an odd memory location. $\overline{BHE}/\overline{WRH}$ is only valid during 16-bit external memory write cycles. Also an LSIO pin when not BHE/ $\overline{WRH}$ . |

| P5.6/READY                      | Ready input to lengthen external memory cycles, for interfacing with slow or dynamic memory, or for bus sharing. If the pin is high, CPU operation continues in a normal manner. If the pin is low prior to the falling edge of CLKOUT, the memory controller goes into a wait state mode until the next positive transition in CLKOUT occurs with READY high. When external memory is not used, READY has no effect. The max number of wait states inserted into the bus cycle is controlled by the CCR/CCR1. Also an LSIO pin when READY is not selected.                                                                                                                                         |

| P5.4/SLPINT                     | Dual function I/O pin. As a bidirectional port pin or as a system function. The system function is a Slave Port Interrupt Output Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P6.2/T1CLK                      | Dual function I/O pin. Primary function is that of a bidirectional I/O pin, however, it may also be used as a TIMER1 Clock input. The TIMER1 will increment or decrement on both positive and negative edges of this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P6.3/T1DIR                      | Dual function I/O pin. Primary function is that of a bidirectional I/O pin, however, it may also be used as a TIMER1 Direction input. The TIMER1 will increment when this pin is high and decrements when this pin is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PORT1/EPA0-7<br>P6.0-6.1/EPA8-9 | Dual function I/O port pins. Primary function is that of bidirectional I/O. System function is that of High Speed capture and compare. EPA0 and EPA2 have yet another function of T2CLK and T2DIR of the TIMER2 timer/counter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PORT 0/ACH0-7                   | 8-bit high impedance input-only port. These pins can be used as digital inputs and/or as analog inputs to the on-chip A/D converter. These pins are also used as inputs to EPROM parts to select the Programming Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P6.3-6.7/SSIO                   | Dual function I/O ports that have a system function as Synchronous Serial I/O. Two pins are clocks and two pins are data, providing full duplex capability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PORT 2                          | 8-bit multi-functional port. All of its pins are shared with other functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PORT 3 and 4                    | 8-bit bidirectional I/O ports with open drain outputs. These pins are shared with the multiplexed address/data bus which has strong internal pullups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

### 87C196KT/87C196KS

### **CCB** (2018H : Byte)

| - | _ \  |   | · · · · · · · · · · · · · · · · · · ·                                                         |

|---|------|---|-----------------------------------------------------------------------------------------------|

| 0 | PD   | _ | "1" Enables Powerdown                                                                         |

| 1 | BW0  | = | See Table                                                                                     |

| 2 | WR   | = | "1" = $\overline{\text{WR}}/\text{BHE}$ - "0" = $\overline{\text{WRL}}/\overline{\text{WRH}}$ |

| 3 | ALE  | = | "1" = ALE - "0" = $\overline{ADV}$                                                            |

| 4 | IRC0 | = | } See Table                                                                                   |

| 5 | IRC1 | = | See Table                                                                                     |

| 6 | LOC0 | = | See Table                                                                                     |

| 7 | LOC1 | = | See Table                                                                                     |

| CCB1 (201/ | AH : B | yte) |

|------------|--------|------|

|            | ه ٦    | 0    |

| 0 | 0     | - | Reserved Must Be "0"  |

|---|-------|---|-----------------------|

| 1 | IRC2  | = | See Table             |

| 2 | BW1   | = | See Table             |

| 3 | WDE   | = | "0" = Always Enabled  |

| 4 | 1     | = | Reserved Must Be "01" |

| 5 | 0     | = | neserved ividst be of |

| 6 | MSEL0 | = | See Table             |

| 7 | MSEL1 | = | J See Table           |

|   |       |   |                       |

| LOC1 | LOC0 | Function                 |  |

|------|------|--------------------------|--|

| 0    | 0    | Read and Write Protected |  |

| 0    | 1    | Write Protected Only     |  |

| 1    | 0    | Read Protected Only      |  |

| 1    | 1    | No Protection            |  |

| IRC2 | IRC1 | IRC0 | Max Wait States  |

|------|------|------|------------------|

| 0    | 0    | 0    | Zero Wait States |

| 1    | 0    | 0    | 1 Wait State     |

| 1    | 0    | 1    | 2 Wait States    |

| 1    | 1    | 0    | 3 Wait States    |

| 1    | 1    | 1    | INFINITE         |

| MSEL1 | MSEL0 | Bus Timing Mode    |  |

|-------|-------|--------------------|--|

| 0     | 0     | Mode 0 (1-Wait KR) |  |

| 0     | 1     | Mode 1             |  |

| 1     | 0     | Mode 2             |  |

| 1     | 1     | Mode 3 (KR)        |  |

|   |   | •                  |

|---|---|--------------------|

| 0 | 0 | Mode 0 (1-Wait KR) |

| 0 | 1 | Mode 1             |

| 1 | 0 | Mode 2             |

| 1 | 1 | Mode 3 (KR)        |

|   |   |                    |

Mode 0 Designed to be similar to the 87C196KR bus (1-Wait KR): timing with 1 automatic wait state.

See AC Timings section for actual timings data.

$\overline{RD}$ ,  $\overline{WR}$ , advanced 1 TOSC Mode 1:

ALE advanced 0.5 T<sub>OSC</sub>

ALE pulse width remains 1 T<sub>OSC</sub>

Mode 2:

AD, WR, advanced 1 T<sub>OSC</sub>

ALE advanced 0.5 T<sub>OSC</sub>

ALE pulse width remains 1 T<sub>OSC</sub>

Address advanced 0.5 T<sub>OSC</sub>

Mode 3 (KR): Designed to be similar to the 87C196KR bus timing.

See AC Timings section for actual timings data.

## **ABSOLUTE MAXIMUM RATINGS\***

| Storage Temperature $\dots -60^{\circ}\text{C}$ to $+150^{\circ}\text{C}$                                                       |

|---------------------------------------------------------------------------------------------------------------------------------|

| Voltage from V <sub>PP</sub> or $\overline{\text{EA}}$ to V <sub>SS</sub> or ANGND                                              |

| Voltage from Any Other Pin to V <sub>SS</sub> or ANGND0.5 to +7.0V <i>This includes V<sub>PP</sub> on ROM and CPU devices</i> . |

| Power Dissipation0.5W                                                                                                           |

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

## **OPERATING CONDITIONS**

| Symbol           | Parameter                      | Min  | Max   | Units        |

|------------------|--------------------------------|------|-------|--------------|

| T <sub>A</sub>   | Ambient Temperature Under Bias | -40  | + 125 | °C           |

| V <sub>CC</sub>  | Digital Supply Voltage         | 4.50 | 5.50  | V            |

| V <sub>REF</sub> | Analog Supply Voltage          | 4.50 | 5.50  | V            |

| Fosc             | Oscillator Frequency           | 4    | 16    | MHz (Note 4) |

#### NOTE:

ANGND and  $\ensuremath{\text{V}_{\text{SS}}}$  should be nominally at the same potential.

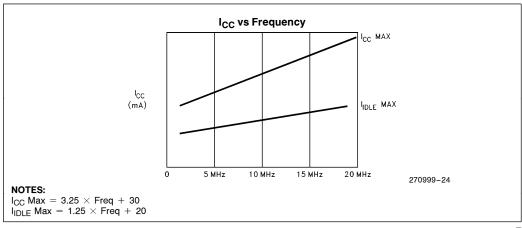

## DC CHARACTERISTICS (Under Listed Operating Conditions)

| Symbol            | Parameter                                                   | Test Conditions                          | Min                 | Тур | Max                   | Units |

|-------------------|-------------------------------------------------------------|------------------------------------------|---------------------|-----|-----------------------|-------|

| Icc               | V <sub>CC</sub> Supply Current<br>(-40°C to +125°C Ambient) | $V_{CC} = V_{PP} = V_{REF} = 5.5V$       |                     |     | 82                    | mA    |

| I <sub>REF</sub>  | A/D Reference Supply Current                                | (While device in Reset)                  |                     |     | 5                     | mA    |

| I <sub>IDLE</sub> | Idle Mode Current                                           | $V_{CC} = V_{PP} = V_{REF} = 5.5V$       |                     |     | 40                    | mA    |

| I <sub>PD</sub>   | Powerdown Mode Current                                      | $V_{CC} = V_{PP} = V_{REF} = 5.5V(6, 9)$ |                     | 50  | TBD                   | μΑ    |

| V <sub>IL</sub>   | Input Low Voltage (all pins)                                | For PORT0 <sup>(8)</sup>                 | -0.5V               |     | 0.3 V <sub>CC</sub>   | ٧     |

| V <sub>IH</sub>   | Input High Voltage                                          | For PORT0 <sup>(8)</sup>                 | 0.7 V <sub>CC</sub> |     | V <sub>CC</sub> + 0.5 | ٧     |

| V <sub>IH1</sub>  | Input High Voltage XTAL1                                    | XTAL1 Input Pin Only(1)                  | 0.7 V <sub>CC</sub> |     | V <sub>CC</sub> + 0.5 | ٧     |

| V <sub>IH2</sub>  | Input High Voltage on RESET                                 | RESET input pin only                     | 0.7 V <sub>CC</sub> |     | V <sub>CC</sub> + 0.5 | V     |

## DC CHARACTERISTICS (Under Listed Operating Conditions) (Continued)

| Symbol           | Parameter                                                       | Test Conditions                                                                      | Min                                                | Тур  | Max                  | Units          |

|------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------|------|----------------------|----------------|

| V <sub>OL</sub>  | Output Low Voltage<br>(Outputs Configured as<br>Complementary)  | $I_{OL} = 200 \ \mu A^{(3,5)}$<br>$I_{OL} = 3.2 \ mA$<br>$I_{OL} = 7.0 \ mA$         |                                                    |      | 0.3<br>0.45<br>1.5   | V<br>V<br>V    |

| V <sub>OH</sub>  | Output High Voltage<br>(Outputs Configured as<br>Complementary) | $I_{OH} = -200 \ \mu A^{(3,5)}$<br>$I_{OH} = -3.2 \ mA$<br>$I_{OH} = -7.0 \ mA$      | $V_{CC} - 0.3$<br>$V_{CC} - 0.7$<br>$V_{CC} - 1.5$ |      |                      | V<br>V<br>V    |

| ILI              | Input Leakage Current (Std. Inputs)                             | $V_{SS} < V_{IN} < V_{CC}$                                                           |                                                    |      | ±10                  | μΑ             |

| I <sub>LI1</sub> | Input Leakage Current (Port 0)                                  | V <sub>SS</sub> < V <sub>IN</sub> < V <sub>REF</sub>                                 |                                                    |      | ± 1.5                | μΑ             |

| V <sub>OH1</sub> | SLPINT (P5.4) and HLDA (P2.6)<br>Output High Voltage in RESET   | $I_{OH} = 0.8 \text{ mA}^{(7)}$                                                      | 2.0                                                |      |                      | ٧              |

| V <sub>OH2</sub> | Output High Voltage in RESET                                    | $I_{OH} = -15 \mu A^{(1,8)}$                                                         | V <sub>CC</sub> - 1V                               |      |                      | ٧              |

| I <sub>OH2</sub> | Output High Current in RESET                                    | $V_{OH2} = V_{CC} - 1.0V$<br>$V_{OH2} = V_{CC} - 2.5V$<br>$V_{OH2} = V_{CC} - 4.0V$  | -30<br>-75<br>-90                                  |      | -120<br>-240<br>-280 | μΑ<br>μΑ<br>μΑ |

| Cs               | Pin Capacitance (Any pin to V <sub>SS</sub> )                   | f <sub>test</sub> = 1.0 MHz(6)                                                       |                                                    |      | 10                   | pF             |

| V <sub>OL3</sub> | Output Low Voltage in RESET<br>(RESET Pin Only)                 | $I_{OL3} = 4 \text{ mA}(10)$<br>$I_{OL3} = 6 \text{ mA}$<br>$I_{OL3} = 8 \text{ mA}$ |                                                    |      | 0.3<br>0.5<br>0.8    | V              |

| R <sub>WPU</sub> | Weak Pullup Resistance                                          | (Note 6)                                                                             |                                                    | 150K |                      | Ω              |

| R <sub>RST</sub> | Reset Pullup Resistor                                           |                                                                                      | 65K                                                |      | 180K                 | Ω              |

- All BD (bidirectional) pins except INST and CLKOUT. INST and CLKOUT are excluded due to their not being weakly pulled high in reset. BD pins include Port1, Port2, Port3, Port4, Port5 and Port6 except SPLINT (P5.4) and HLDA (P2.6).

- 2. Standard input pins include XTAL1, EA, RESET, and Port 1/2/5/6 when setup as inputs.

- 3. All bidirectional I/O pins when configured as Outputs (Push/Pull).

- 4. Device is static and should operate below 1 Hz, but only tested down to 4 MHz.

- 5. Maximum I<sub>OL</sub>/I<sub>OH</sub> currents per pin will be characterized and published at a later date.

- 6. Typicals are based on limited number of samples and are not guaranteed. The values listed are at room temperature and  $V_{REF} = V_{CC} = 5.0V.$

- 7. Violating these specifications in reset may cause the device to enter test modes (P5.4 and P2.6).

8. When P0 is used as analog inputs, refer to A/D specifications for this characteristic.

- 9. For temperatures <100°C typical is 10  $\mu$ A.

- 10. This specification is not tested in production and is based upon theoretical estimates and/or product characterization.

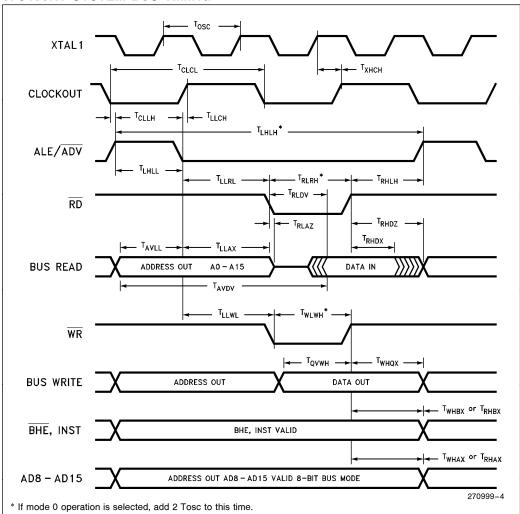

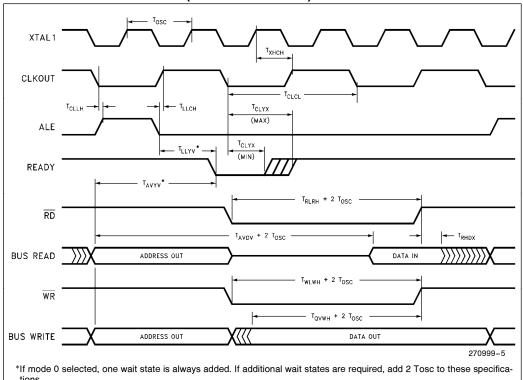

## **AC CHARACTERISTICS** (Over Specified Operating Conditions)

Test Conditions: Capacitance Load on All Pins = 100 pF, Rise and Fall Times = 10 ns.

The 87C196KT will meet these specifications

| Symbol            | Parameter                            | Min                   | Max                   | Units             |

|-------------------|--------------------------------------|-----------------------|-----------------------|-------------------|

| F <sub>XTAL</sub> | Frequency on XTAL1                   | 4.0                   | 16.0                  | MHz(1)            |

| Tosc              | XTAL1 Period (1/F <sub>XTAL</sub> )  | 62.5                  | 250                   | ns                |

| T <sub>XHCH</sub> | XTAL1 High to CLKOUT High or Low     | +20                   | 110                   | ns                |

| T <sub>OFD</sub>  | Clock Failure to Reset Pulled Low(6) | 4                     | 40                    | μs                |

| T <sub>CLCL</sub> | CLKOUT Period                        | 2 T                   | osc                   | ns                |

| T <sub>CHCL</sub> | CLKOUT High Period                   | T <sub>OSC</sub> - 10 | T <sub>OSC</sub> + 30 | ns                |

| T <sub>CLLH</sub> | CLKOUT Low to ALE/ADV High           | -10                   | + 15                  | ns                |

| T <sub>LLCH</sub> | ALE/ADV Low to CLKOUT High           | -25                   | + 15                  | ns                |

| T <sub>LHLH</sub> | ALE/ADV Cycle Time                   | 4 T                   | osc                   | ns <sup>(5)</sup> |

| T <sub>LHLL</sub> | ALE/ADV High Time                    | T <sub>OSC</sub> - 10 | T <sub>OSC</sub> + 10 | ns                |

| T <sub>AVLL</sub> | Address Valid to ALE Low             | T <sub>OSC</sub> - 15 |                       | ns                |

| T <sub>LLAX</sub> | Address Hold After ALE/ADV Low       | T <sub>OSC</sub> - 40 |                       | ns                |

| T <sub>LLRL</sub> | ALE/ADV Low to RD Low                | T <sub>OSC</sub> - 40 |                       | ns                |

| T <sub>RLCL</sub> | RD Low to CLKOUT Low                 | -5                    | + 35                  | ns                |

| T <sub>RLRH</sub> | RD Low Period                        | T <sub>OSC</sub> - 5  |                       | ns(5)             |

| T <sub>RHLH</sub> | RD High to ALE/ADV High              | T <sub>OSC</sub>      | T <sub>OSC</sub> + 25 | ns(3)             |

| T <sub>RLAZ</sub> | RD Low to Address Float              |                       | +5                    | ns                |

| $T_LLWL$          | ALE/ADV Low to WR Low                | T <sub>OSC</sub> - 10 |                       | ns                |

| T <sub>CLWL</sub> | CLKOUT Low to WR Low                 | -10                   | + 25                  | ns                |

| T <sub>QVWH</sub> | Data Valid before WR High            | T <sub>OSC</sub> - 23 |                       | ns                |

| T <sub>CHWH</sub> | CLKOUT High to WR High               | -10                   | + 15                  | ns                |

| T <sub>WLWH</sub> | WR Low Period                        | T <sub>OSC</sub> - 30 |                       | ns(5)             |

| T <sub>WHQX</sub> | Data Hold after WR High              | T <sub>OSC</sub> - 30 |                       | ns                |

| T <sub>WHLH</sub> | WR High to ALE/ADV High              | T <sub>OSC</sub> - 10 | T <sub>OSC</sub> + 15 | ns <sup>(3)</sup> |

| T <sub>WHBX</sub> | BHE, INST Hold after WR High         | T <sub>OSC</sub> - 10 |                       | ns                |

| T <sub>WHAX</sub> | AD8-15 Hold after WR High            | T <sub>OSC</sub> - 30 |                       | ns(4)             |

| T <sub>RHBX</sub> | BHE, INST Hold after RD High         | T <sub>OSC</sub> - 10 |                       | ns                |

| T <sub>RHAX</sub> | AD8-15 Hold after RD High            | T <sub>OSC</sub> - 30 |                       | ns <sup>(4)</sup> |

- Testing performed at 4.0 MHz, however, the device is static by design and will typically operate below 1 Hz.

Typical specifications, not guaranteed.

Assuming back-to-back bus cycles.

- 4. 8-bit bus only.

- 5. If wait states are used, add 2 Tosc × n, where n = number of wait states. If mode 0 (1 automatic wait state added) operation is selected, add 2 Tosc to specification.

- 6. T<sub>OFD</sub> is the time for the oscillator fail detect circuit (OFD) to react to a clock failure. The OFD circuitry is enabled by programming the UPROM location 0778H with the value 0004H. KT/KS customer QROM codes need to equate location 2016H to the value 0CDEH if the oscillator fail detect (OFD) function is desired. Intel manufacturing uses location 2016H as a flag to determine whether or not to program the Clock Detect Enable (CDE) bit. Programming the CDE bit enables oscillator fail detection.

## **AC CHARACTERISTICS** (Over Specified Operating Conditions)

Test Conditions: Capacitance Load on All Pins = 100 pF, Rise anf Fall Times = 10 ns.

The system must meet these specifications to work with the 87C196KT.

| Symbol            | Parameter                         | Min | Max                     | Units             |

|-------------------|-----------------------------------|-----|-------------------------|-------------------|

| T <sub>AVYV</sub> | Address Valid to Ready Setup      |     | 2 T <sub>OSC</sub> - 75 | ns(3)             |

| T <sub>LLYV</sub> | ALE Low to READY Setup            |     | T <sub>OSC</sub> - 70   | ns <sup>(3)</sup> |

| T <sub>YLYH</sub> | Non READY Time                    | No  | Upper Limit             | ns                |

| T <sub>CLYX</sub> | READY Hold after CLKOUT Low       | 0   | T <sub>OSC</sub> - 30   | ns <sup>(1)</sup> |

| T <sub>AVGV</sub> | Address Valid to BUSWIDTH Setup   |     | 2 T <sub>OSC</sub> - 75 | ns(2, 3)          |

| T <sub>LLGV</sub> | ALE Low to BUSWIDTH Setup         |     | T <sub>OSC</sub> - 60   | ns(2, 3)          |

| T <sub>CLGX</sub> | BUSWIDTH Hold after CLKOUT Low    | 0   |                         | ns                |

| T <sub>AVDV</sub> | Address Valid to Input Data Valid |     | 3 T <sub>OSC</sub> - 55 | ns <sup>(2)</sup> |

| T <sub>RLDV</sub> | RD active to input Data Valid     |     | T <sub>OSC</sub> - 30   | ns <sup>(2)</sup> |

| T <sub>CLDV</sub> | CLKOUT Low to Input Data Valid    |     | T <sub>OSC</sub> - 60   | ns                |

| T <sub>RHDZ</sub> | End of RD to Input Data Float     |     | T <sub>OSC</sub>        | ns                |

| T <sub>RHDX</sub> | Data Hold after RD High           | 0   |                         | ns                |

#### NOTES:

- 1. If Max is exceeded, additional wait states will occur.

- 2. If wait states are used, add 2 Tosc × n, where n = number of wait states.

3. If mode 0 is selected, one wait state minimum is always added. If additional wait states are required, add 2 Tosc to the specification.

## 87C196KT SYSTEM BUS TIMING

## 87C196KT READY TIMINGS (ONE WAIT STATE)

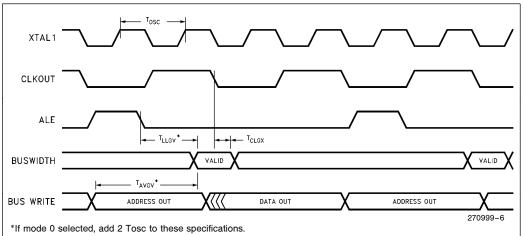

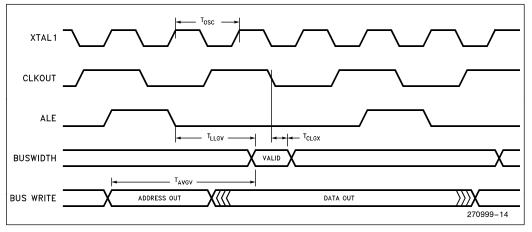

## 87C196KT BUSWIDTH TIMINGS

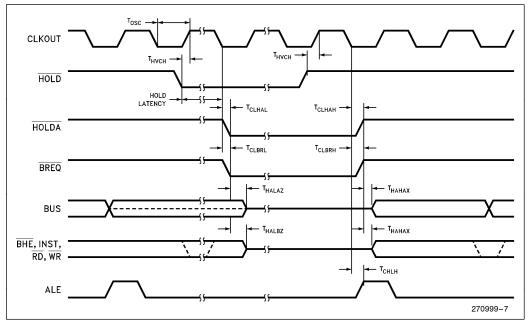

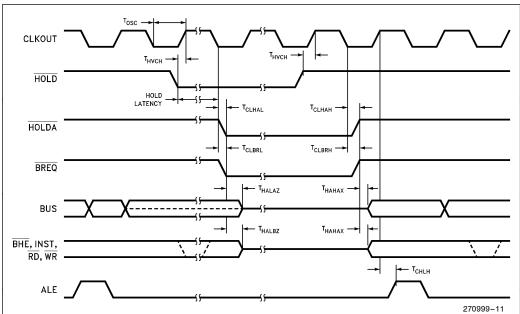

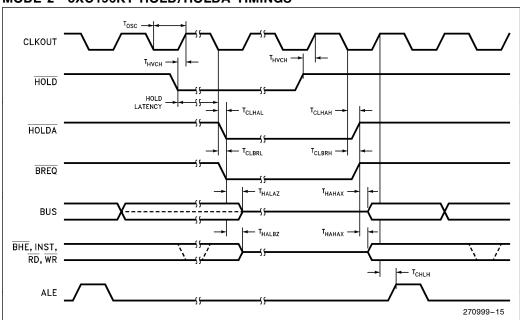

## **HOLD/HOLDA TIMINGS** (Over Specified Operation Conditions)

Test Conditions: Capacitance Load on All Pins = 100 pF, Rise and Fall Times = 10 ns.

| Symbol             | Parameter                                   | Min | Max  | Units |

|--------------------|---------------------------------------------|-----|------|-------|

| T <sub>HVCH</sub>  | HOLD Setup Time                             | +65 |      | ns(1) |

| T <sub>CLHAL</sub> | CLKOUT Low to HLDA Low                      | -15 | +15  | ns    |

| T <sub>CLBRL</sub> | CLKOUT Low to BREQ Low                      | -15 | +15  | ns    |

| T <sub>AZHAL</sub> | HLDA Low to Address Float                   |     | +20  | ns    |

| T <sub>BZHAL</sub> | HLDA Low to BHE, INST, RD, WR Weakly Driven |     | + 25 | ns    |

| T <sub>CLHAH</sub> | CLKOUT Low to HLDA High                     | -25 | + 15 | ns    |

| T <sub>CLBRH</sub> | CLKOUT Low to BREQ High                     | -25 | + 25 | ns    |

| T <sub>HAHAX</sub> | HLDA High to Address No Longer Float        | -15 |      | ns    |

| T <sub>HAHBV</sub> | HLDA High to BHE, INST, RD, WR Valid        | -10 | +15  | ns    |

## NOTE:

1. To guarantee recognition at next clock.

## 8XC196KT HOLD/HOLDA TIMINGS

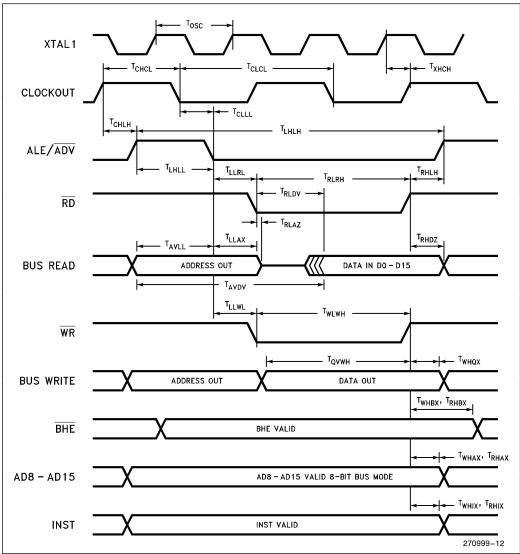

## BUS MODE 1—AC CHARACTERISTICS (Over Specified Operating Conditions) Test Conditions: Capacitance Load on All Pins = 100 pF, Rise and Fall Times = 10 ns.

The 87C196KT will meet these specifications

| Symbol            | Parameter                           | Min                       | Max                       | Units             |

|-------------------|-------------------------------------|---------------------------|---------------------------|-------------------|

| F <sub>XTAL</sub> | Frequency on XTAL1                  | 8.0                       | 16.0                      | MHz(1)            |

| Tosc              | XTAL1 Period (1/F <sub>XTAL</sub> ) | 62.5                      | 125                       | ns                |

| T <sub>XHCH</sub> | XTAL1 High to CLKOUT High or Low    | +20                       | 110                       | ns                |

| T <sub>CLCL</sub> | CLKOUT Period                       | 2 T                       | OSC                       | ns                |

| T <sub>CHCL</sub> | CLKOUT High Period                  | T <sub>OSC</sub> - 10     | T <sub>OSC</sub> + 27     | ns                |

| T <sub>CHLH</sub> | CLKOUT HIGH to ALE/ADV High         | 0.5 T <sub>OSC</sub> - 15 | 0.5 T <sub>OSC</sub> + 20 | ns                |

| T <sub>CLLL</sub> | CLKOUT LOW to ALE/ADV Low           | 0.5 T <sub>OSC</sub> — 25 | 0.5 T <sub>OSC</sub> + 15 | ns                |

| T <sub>LHLH</sub> | ALE/ADV Cycle Time                  | 4 T                       | OSC                       | ns <sup>(5)</sup> |

| T <sub>LHLL</sub> | ALE/ADV High Time                   | T <sub>OSC</sub> - 10     | T <sub>OSC</sub> + 10     | ns                |

| T <sub>AVLL</sub> | Address Valid to ALE Low            | 0.5 T <sub>OSC</sub> - 15 |                           | ns                |

| T <sub>LLAX</sub> | Address Hold After ALE/ADV Low      | 0.5 T <sub>OSC</sub> - 20 |                           | ns                |

| T <sub>LLRL</sub> | ALE/ADV Low to RD Low               | 0.5 T <sub>OSC</sub> - 30 |                           | ns                |

| T <sub>RLCL</sub> | RD Low to CLKOUT Low                | T <sub>OSC</sub> - 10     | T <sub>OSC</sub> + 30     | ns                |

| T <sub>RLRH</sub> | RD Low Period                       | 2 T <sub>OSC</sub> — 20   |                           | ns <sup>(5)</sup> |

| T <sub>RHLH</sub> | RD High to ALE/ADV High             | 0.5 T <sub>OSC</sub>      | 0.5 T <sub>OSC</sub> + 25 | ns(3)             |

| T <sub>RLAZ</sub> | RD Low to Address Float             |                           | +5                        | ns                |

| T <sub>LLWL</sub> | ALE/ADV Low to WR Low               | 0.5 T <sub>OSC</sub> - 10 |                           | ns                |

| T <sub>CLWL</sub> | CLKOUT Low to WR Low                | T <sub>OSC</sub> - 15     | T <sub>OSC</sub> +25      | ns                |

| T <sub>QVWH</sub> | Data Valid before WR High           | 2 T <sub>OSC</sub> - 23   |                           | ns                |

| T <sub>CHWH</sub> | CLKOUT High to WR High              | -10                       | +15                       | ns                |

| T <sub>WLWH</sub> | WR Low Period                       | 2 T <sub>OSC</sub> - 15   |                           | ns(5)             |

| T <sub>WHQX</sub> | Data Hold after WR High             | 0.5 T <sub>OSC</sub> — 25 |                           | ns                |

| T <sub>WHLH</sub> | WR High to ALE/ADV High             | 0.5 T <sub>OSC</sub> - 10 | 0.5 T <sub>OSC</sub> + 15 | ns <sup>(3)</sup> |

| T <sub>WHBX</sub> | BHE Hold after WR High              | T <sub>OSC</sub> - 15     |                           | ns                |

| T <sub>WHIX</sub> | INST Hold after WR High             | 0.5 T <sub>OSC</sub> - 15 |                           |                   |

| T <sub>WHAX</sub> | AD8-15 Hold after WR High           | 0.5 T <sub>OSC</sub> - 30 |                           | ns(4)             |

| T <sub>RHBX</sub> | BHE Hold after RD High              | T <sub>OSC</sub> - 32     |                           | ns                |

| T <sub>RHAX</sub> | AD8-15 Hold after RD High           | 0.5 T <sub>OSC</sub> - 32 |                           |                   |

| T <sub>RHAX</sub> | AD8-15 Hold after RD High           | 0.5 T <sub>OSC</sub> - 30 |                           | ns <sup>(4)</sup> |

- 1. Testing performed at 8.0 MHz, however, the device is static by design and will typically operate below 1 Hz.

- Typical specifications, not guaranteed.

Assuming back-to-back bus cycles.

8-bit bus only.

If wait states are used, add 2 T<sub>OSC</sub> × n, where n = number of wait states.

**BUS MODE 1—AC CHARACTERISTICS** (Over Specified Operating Conditions) (Continued) Test Conditions: Capacitance Load on All Pins = 100 pF, Rise and Fall Times = 10 ns.

The system must meet these specifications to work with the 87C196KT.

| Symbol            | Parameter                         | Min | Max                       | Units             |

|-------------------|-----------------------------------|-----|---------------------------|-------------------|

| T <sub>AVYV</sub> | Address Valid to Ready Setup      |     | 2 T <sub>OSC</sub> — 75   | ns                |

| T <sub>LLYV</sub> | ALE Low to READY Setup            |     | 1.5 T <sub>OSC</sub> - 70 | ns                |

| $T_{YLYH}$        | Non READY Time                    | N   | o Upper Limit             | ns                |

| T <sub>CLYX</sub> | READY Hold after CLKOUT Low       | 0   | T <sub>OSC</sub> - 30     | ns <sup>(1)</sup> |

| T <sub>AVGV</sub> | Address Valid to BUSWIDTH Setup   |     | 2 T <sub>OSC</sub> — 75   | ns                |

| T <sub>LLGV</sub> | ALE Low to BUSWIDTH Setup         |     | 1.5 T <sub>OSC</sub> - 60 | ns                |

| T <sub>CLGX</sub> | BUSWIDTH Hold after CLKOUT Low    | 0   |                           | ns                |

| $T_{AVDV}$        | Address Valid to Input Data Valid |     | 3 T <sub>OSC</sub> - 65   | ns <sup>(2)</sup> |

| T <sub>RLDV</sub> | RD active to input Data Valid     |     | 2 T <sub>OSC</sub> - 44   | ns <sup>(2)</sup> |

| T <sub>CLDV</sub> | CLKOUT Low to Input Data Valid    |     | T <sub>OSC</sub> - 60     | ns                |

| T <sub>RHDZ</sub> | End of RD to Input Data Float     |     | T <sub>OSC</sub>          | ns                |

| T <sub>RHDX</sub> | Data Hold after RD High           | 0   |                           | ns                |

#### NOTES:

<sup>1.</sup> If Max is exceeded, additional wait states will occur.

This was deceded, add 2  $T_{OSC} \times n$ , where n = number of wait states. If mode 0 (1 automatic wait state added) operation is selected, add 2  $T_{OSC}$  to specification.

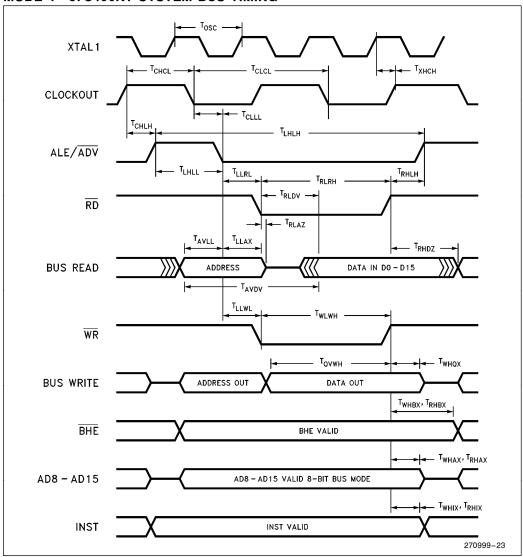

## MODE 1-87C196KT SYSTEM BUS TIMING

## BUS MODE 1—HOLD/HOLDA TIMINGS (Over Specified Operation Conditions)

Test Conditions: Capacitance Load on All Pins = 100 pF, Rise and Fall Times = 10 ns.

| Symbol             | Parameter                                   | Min | Max  | Units |

|--------------------|---------------------------------------------|-----|------|-------|

| T <sub>HVCH</sub>  | HOLD Setup Time                             | +65 |      | ns(1) |

| T <sub>CLHAL</sub> | CLKOUT Low to HLDA Low                      | -15 | +15  | ns    |

| T <sub>CLBRL</sub> | CLKOUT Low to BREQ Low                      | -15 | +15  | ns    |

| T <sub>AZHAL</sub> | HLDA Low to Address Float                   |     | + 25 | ns    |

| T <sub>BZHAL</sub> | HLDA Low to BHE, INST, RD, WR Weakly Driven |     | + 25 | ns    |

| T <sub>CLHAH</sub> | CLKOUT Low to HLDA High                     | -25 | +15  | ns    |

| T <sub>CLBRH</sub> | CLKOUT Low to BREQ High                     | -25 | +15  | ns    |

| T <sub>HAHAX</sub> | HLDA High to Address No Longer Float        | -15 |      | ns    |

| T <sub>HAHBV</sub> | HLDA High to BHE, INST, RD, WR Valid        | -10 |      | ns    |

### NOTE:

1. To guarantee recognition at next clock.

## MODE 1—8XC196KT HOLD/HOLDA TIMINGS

## BUS MODE 2—AC CHARACTERISTICS (Over Specified Operating Conditions) Test Conditions: Capacitance Load on All Pins = 100 pF, Rise and Fall Times = 10 ns.

The 87C196KT will meet these specifications

| Symbol            | Parameter                           | Min                       | Max                       | Units              |

|-------------------|-------------------------------------|---------------------------|---------------------------|--------------------|

| $F_{XTAL}$        | Frequency on XTAL1                  | 8.0                       | 16.0                      | MHz <sup>(1)</sup> |

| T <sub>OSC</sub>  | XTAL1 Period (1/F <sub>XTAL</sub> ) | 62.5                      | 125                       | ns                 |

| T <sub>XHCH</sub> | XTAL1 High to CLKOUT High or Low    | +20                       | +85                       | ns                 |

| T <sub>CLCL</sub> | CLKOUT Period                       | 2 T                       | OSC                       | ns                 |

| T <sub>CHCL</sub> | CLKOUT High Period                  | T <sub>OSC</sub> - 10     | T <sub>OSC</sub> + 27     | ns                 |

| T <sub>CHLH</sub> | CLKOUT HIGH to ALE/ADV High         | 0.5 T <sub>OSC</sub> - 15 | 0.5 T <sub>OSC</sub> + 20 | ns                 |

| T <sub>CLLL</sub> | CLKOUT LOW to ALE/ADV Low           | 0.5 T <sub>OSC</sub> - 25 | 0.5 T <sub>OSC</sub> + 15 | ns                 |

| T <sub>LHLH</sub> | ALE/ADV Cycle Time                  | 4 T                       | OSC                       | ns <sup>(5)</sup>  |

| T <sub>LHLL</sub> | ALE/ADV High Time                   | T <sub>OSC</sub> - 10     | T <sub>OSC</sub> + 10     | ns                 |

| T <sub>AVLL</sub> | Address Valid to ALE Low            | T <sub>OSC</sub> - 15     |                           | ns                 |

| $T_{LLAX}$        | Address Hold After ALE/ADV Low      | 0.5 T <sub>OSC</sub> - 20 |                           | ns                 |

| T <sub>LLRL</sub> | ALE/ADV Low to RD Low               | 0.5 T <sub>OSC</sub> - 30 |                           | ns                 |

| T <sub>RLCL</sub> | RD Low to CLKOUT Low                | T <sub>OSC</sub> - 10     | T <sub>OSC</sub> + 30     | ns                 |

| T <sub>RLRH</sub> | RD Low Period                       | 2 T <sub>OSC</sub> — 20   |                           | ns <sup>(5)</sup>  |

| T <sub>RHLH</sub> | RD High to ALE/ADV High             | 0.5 T <sub>OSC</sub> - 5  | 0.5 T <sub>OSC</sub> + 25 | ns(3)              |

| T <sub>RLAZ</sub> | RD Low to Address Float             |                           | +5                        | ns                 |

| $T_{LLWL}$        | ALE/ADV Low to WR Low               | 0.5 T <sub>OSC</sub> - 10 |                           | ns                 |

| $T_{CLWL}$        | CLKOUT Low to WR Low                | T <sub>OSC</sub> - 22     | T <sub>OSC</sub> + 25     | ns                 |

| $T_{QVWH}$        | Data Valid before WR High           | 2 T <sub>OSC</sub> — 25   |                           | ns                 |

| T <sub>CHWH</sub> | CLKOUT High to WR High              | -10                       | +15                       | ns                 |

| $T_{WLWH}$        | WR Low Period                       | 2 T <sub>OSC</sub> - 20   |                           | ns(5)              |

| $T_{WHQX}$        | Data Hold after WR High             | 0.5 T <sub>OSC</sub> - 25 |                           | ns                 |

| T <sub>WHLH</sub> | WR High to ALE/ADV High             | 0.5 T <sub>OSC</sub> - 10 | 0.5 T <sub>OSC</sub> + 10 | ns <sup>(3)</sup>  |

| T <sub>WHBX</sub> | BHE Hold after WR High              | T <sub>OSC</sub> - 15     |                           | ns                 |

| T <sub>WHIX</sub> | INST Hold after WR High             | 0.5 T <sub>OSC</sub> - 15 |                           |                    |

| T <sub>WHAX</sub> | AD8-15 Hold after WR High           | 0.5 T <sub>OSC</sub> - 30 |                           | ns(4)              |

| T <sub>RHBX</sub> | BHE Hold after RD High              | T <sub>OSC</sub> - 32     |                           | ns                 |

| T <sub>RHIX</sub> | INST Hold after RD High             | 0.5 T <sub>OSC</sub> - 32 |                           |                    |

| T <sub>RHAX</sub> | AD8-15 Hold after RD High           | 0.5 T <sub>OSC</sub> - 30 |                           | ns <sup>(4)</sup>  |

- 1. Testing performed at 8.0 MHz, however, the device is static by design and will typically operate below 1 Hz.

- Typical specifications, not guaranteed.

Assuming back-to-back bus cycles.

8-bit bus only.

If wait states are used, add 2 T<sub>OSC</sub> × n, where n = number of wait states.

## BUS MODE 2—AC CHARACTERISTICS (Over Specified Operating Conditions)

Test Conditions: Capacitance Load on All Pins = 100 pF, Rise and Fall Times = 10 ns.

The system must meet these specifications to work with the 87C196KT.

| Symbol            | Parameter                         | Min | Max                       | Units             |

|-------------------|-----------------------------------|-----|---------------------------|-------------------|

| T <sub>AVYV</sub> | Address Valid to Ready Setup      |     | 2.5 T <sub>OSC</sub> - 75 | ns                |

| T <sub>LLYV</sub> | ALE Low to READY Setup            |     | 1.5 T <sub>OSC</sub> - 70 | ns                |

| T <sub>YLYH</sub> | Non READY Time                    | N   | o Upper Limit             | ns                |

| T <sub>CLYX</sub> | READY Hold after CLKOUT Low       | 0   | T <sub>OSC</sub> - 30     | ns <sup>(1)</sup> |

| T <sub>AVGV</sub> | Address Valid to BUSWIDTH Setup   |     | 2.5 T <sub>OSC</sub> - 75 | ns                |

| T <sub>LLGV</sub> | ALE Low to BUSWIDTH Setup         |     | 1.5 T <sub>OSC</sub> - 60 | ns                |

| T <sub>CLGX</sub> | BUSWIDTH Hold after CLKOUT Low    | 0   |                           | ns                |

| T <sub>AVDV</sub> | Address Valid to Input Data Valid |     | 3.5 T <sub>OSC</sub> - 60 | ns <sup>(2)</sup> |

| T <sub>RLDV</sub> | RD active to Input Data Valid     |     | 2 T <sub>OSC</sub> - 44   | ns <sup>(2)</sup> |

| T <sub>CLDV</sub> | CLKOUT Low to Input Data Valid    |     | T <sub>OSC</sub> - 60     | ns                |

| T <sub>RHDZ</sub> | End of RD to Input Data Float     |     | 0.5 T <sub>OSC</sub>      | ns                |

| T <sub>RHDX</sub> | Data Hold after RD High           | 0   |                           | ns                |

#### NOTES:

- 1. If Max is exceeded, additional wait states will occur.

- If wait states are used, add 2 T<sub>OSC</sub> × n, where n = number of wait states. If mode 0 (1 automatic wait state added) operation is selected, add 2 T<sub>OSC</sub> to specification.

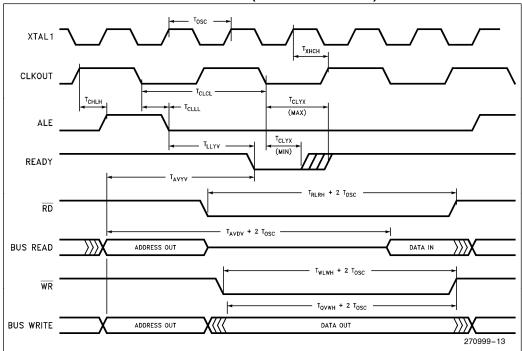

## MODE 2-87C196KT SYSTEM BUS TIMING

## MODE 2—87C196KT READY TIMINGS (ONE WAIT STATE)

## MODE 2—87C196KT BUSWIDTH TIMINGS

## BUS MODE 2—HOLD/HOLDA TIMINGS (Over Specified Operation Conditions)

Test Conditions: Capacitance Load on All Pins = 100 pF, Rise and Fall Times = 10 ns.

| Symbol             | Parameter                                   | Min | Max  | Units |

|--------------------|---------------------------------------------|-----|------|-------|

| T <sub>HVCH</sub>  | HOLD Setup Time                             | +65 |      | ns(1) |

| T <sub>CLHAL</sub> | CLKOUT Low to HLDA Low                      | -15 | +15  | ns    |

| T <sub>CLBRL</sub> | CLKOUT Low to BREQ Low                      | -15 | +15  | ns    |

| T <sub>AZHAL</sub> | HLDA Low to Address Float                   |     | + 25 | ns    |

| T <sub>BZHAL</sub> | HLDA Low to BHE, INST, RD, WR Weakly Driven |     | + 25 | ns    |

| T <sub>CLHAH</sub> | CLKOUT Low to HLDA High                     | -25 | + 15 | ns    |

| T <sub>CLBRH</sub> | CLKOUT Low to BREQ High                     | -25 | +15  | ns    |

| T <sub>HAHAX</sub> | HLDA High to Address No Longer Float        | -15 |      | ns    |

| T <sub>HAHBV</sub> | HLDA High to BHE, INST, RD, WR Valid        | -10 |      | ns    |

### NOTE:

1. To guarantee recognition at next clock.

## MODE 2—8XC196KT HOLD/HOLDA TIMINGS

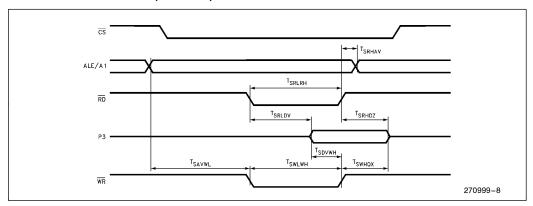

## AC CHARACTERISTICS—SLAVE PORT

## SLAVE PORT WAVEFORM—(SLPL = 0)

## SLAVE PORT TIMING—(SLPL = 0, 1, 2, 3)

| Symbol             | Parameter                   | Min              | Max | Units |

|--------------------|-----------------------------|------------------|-----|-------|

| T <sub>SAVWL</sub> | Address Valid to WR Low     | 50               |     | ns    |

| T <sub>SRHAV</sub> | RD High to Address Valid    | 60               |     | ns    |

| T <sub>SRLRH</sub> | RD Low Period               | T <sub>OSC</sub> |     | ns    |

| T <sub>SWLWH</sub> | WR Low Period               | T <sub>OSC</sub> |     | ns    |

| T <sub>SRLDV</sub> | RD Low to Output Data Valid |                  | 60  | ns    |

| T <sub>SDVWH</sub> | Input Data Setup to WR High | 20               |     | ns    |

| T <sub>SWHQX</sub> | WR High to Data Invalid     | 30               |     | ns    |

| T <sub>SRHDZ</sub> | RD High to Data Float       | 15               |     | ns    |

## NOTES:

- 1. Test Conditions: F<sub>OSC</sub> = 16 MHz, T<sub>OSC</sub> = 60 ns. Rise/Fall Time = 10 ns. Capacitive Pin Load = 100 pF.

2. These values are not tested in production, and are based upon theoretical estimates and/or laboratory tests.

3. Specifications above are advanced information and are subject to change.

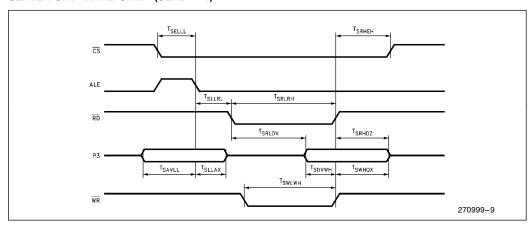

## AC CHARACTERISTICS—SLAVE PORT (Continued)

## SLAVE PORT WAVEFORM—(SLPL = 1)

### SLAVE PORT TIMING—(SLPL = 1, 2, 3)

| Symbol             | Parameter                   | Min              | Max | Units |

|--------------------|-----------------------------|------------------|-----|-------|

| T <sub>SELLL</sub> | CS Low to ALE Low           | 20               |     | ns    |

| T <sub>SRHEH</sub> | RD or WR High to CS High    | 60               |     | ns    |

| T <sub>SLLRL</sub> | ALE Low to RD Low           | T <sub>OSC</sub> |     | ns    |

| T <sub>SRLRH</sub> | RD Low Period               | T <sub>OSC</sub> |     | ns    |

| T <sub>SWLWH</sub> | WR Low Period               | T <sub>OSC</sub> |     | ns    |

| T <sub>SAVLL</sub> | Address Valid to ALE Low    | 20               |     | ns    |

| T <sub>SLLAX</sub> | ALE Low to Address Invalid  | 20               |     | ns    |

| T <sub>SRLDV</sub> | RD Low to Output Data Valid |                  | 60  | ns    |

| T <sub>SDVWH</sub> | Input Data Setup to WRHigh  | 20               |     | ns    |

| T <sub>SWHQX</sub> | WR High to Data Invalid     | 30               |     | ns    |

| T <sub>SRHDZ</sub> | RD High to Data Float       | 15               |     | ns    |

- **NOTES:**1. Test Conditions:  $F_{OSC} = 16$  MHz,  $T_{OSC} = 60$  ns. Rise/Fall Time = 10 ns. Capacitive Pin Load = 100 pF.

2. These values are not tested in production, and are based upon theoretical estimates and/or laboratory tests.

3. Specifications above are advanced information and are subject to change.

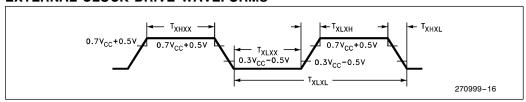

## **EXTERNAL CLOCK DRIVE**

| Symbol              | Parameter                             | Min                     | Max                   | Units |

|---------------------|---------------------------------------|-------------------------|-----------------------|-------|

| 1/T <sub>XLXL</sub> | Oscillator Frequency                  | 4                       | 16                    | MHz   |

| T <sub>XLXL</sub>   | Oscillator Period (T <sub>OSC</sub> ) | 62.5                    | 250                   | ns    |

| T <sub>XHXX</sub>   | High Time                             | 0.35 × T <sub>OSC</sub> | 0.65 T <sub>OSC</sub> | ns    |

| T <sub>XLXX</sub>   | Low Time                              | 0.35 × T <sub>OSC</sub> | 0.65 T <sub>OSC</sub> | ns    |

| T <sub>XLXH</sub>   | Rise Time                             |                         | 10                    | ns    |

| T <sub>XHXL</sub>   | Fall Time                             |                         | 10                    | ns    |

## **EXTERNAL CLOCK DRIVE WAVEFORMS**

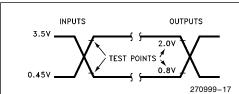

#### AC TESTING INPUT, OUTPUT WAVEFORMS

AC Testing inputs are driven at 3.5V for a logic "1" and 0.45V for a logic "0". Timing measurements are made at 2.0V for a logic "1" and 0.8V for logic "0".

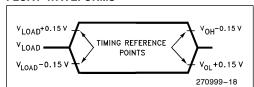

### FLOAT WAVEFORMS

For timing purposes a Port Pin is no longer floating when a 150 mV change from load voltage occurs and begins to float when a 150 mV change from the loading  $V_{OH}/V_{OL}$  level occurs  $I_{OL}/I_{OH} \leq$  15 mA.

## THERMAL CHARACTERISTICS

| Device and Package              | $\theta_{JA}$ | $\theta$ JC |

|---------------------------------|---------------|-------------|

| AN87C196KT/KS<br>(68-Lead PLCC) | 36.5°C/W      | 13°C/W      |

#### NOTES:

- 1.  $\theta_{\rm JA}=$  Thermal resistance between junction and the surrounding environmental (ambient). Measurements are taken 1 ft. away from case in air flow environment.  $\theta_{\rm JC}=$  Thermal resistance between junction and package surface (case).

- 2. All values of  $\theta_{JA}$  and  $\theta_{JC}$  may fluctuate depending on the environment (with or without airflow, and how much airflow) and device power dissipation at temperature of operation. Typical variations are  $\pm 2^{\circ}$ C/W.

- 3. Values listed are at a maximum power dissipation of 0.50W.

## **EXPLANATION OF AC SYMBOLS**

Each symbol is two pairs of letters prefixed by "T" for time. The characters in a pair indicate a signal and its condition, respectively. Symbols represent the time between the two signal/condition points.

| Conditions: | Signals:   |                        |

|-------------|------------|------------------------|

| H—High      | A—Address  | HA— <del>HLDA</del>    |

| L—Low       | B—BHE      | L—ALE/ADV              |

| V—Valid     | BR—BREQ    | Q—Data Out             |

| X—No Longer | C—CLKOUT   | $RD$ — $\overline{RD}$ |

| Valid       | D—DATA     | W—WR/WRH/WRI           |

| Z—Floating  | G—Buswidth | X—XTAL1                |

Y-READY

H—HOLD

## **EPROM SPECIFICATIONS**

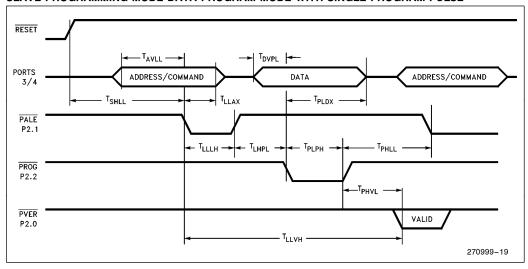

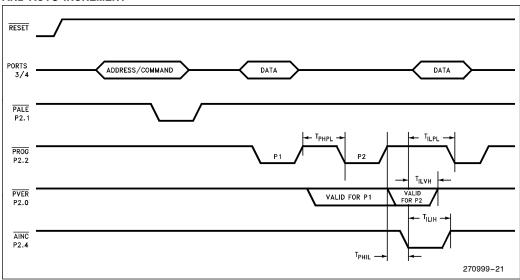

#### AC EPROM PROGRAMMING CHARACTERISTICS

Operating Conditions: Load Capacitance = 150 pF;  $T_C = 25^{\circ}C$   $\pm 5^{\circ}C$ ,  $V_{CC}$ ,  $V_{REF} = 5.0V$   $\pm 0.5V$ ,  $V_{SS}$ , ANGND = 0V.

$V_{PP} =$  12.5V  $\pm 0.25$ V;  $\overline{EA} =$  12.5V  $\pm 0.25$ V; Fosc = 5.0 MHz.

| Symbol            | Paramter                        | Min  | Max | Units            |

|-------------------|---------------------------------|------|-----|------------------|

| T <sub>AVLL</sub> | Address Setup Time              | 0    |     | Tosc             |

| T <sub>LLAX</sub> | Address Hold Time               | 100  |     | Tosc             |

| T <sub>DVPL</sub> | Data Setup Time                 | 0    |     | T <sub>OSC</sub> |

| T <sub>PLDX</sub> | Data Hold Time                  | 400  |     | T <sub>OSC</sub> |

| T <sub>LLLH</sub> | PALE Pulse Width                | 50   |     | Tosc             |

| T <sub>PLPH</sub> | PROG Pulse Width <sup>(2)</sup> | 50   |     | Tosc             |

| T <sub>LHPL</sub> | PALE High to PROG Low           | 220  |     | Tosc             |

| T <sub>PHLL</sub> | PROG High to next PALE Low      | 220  |     | T <sub>OSC</sub> |

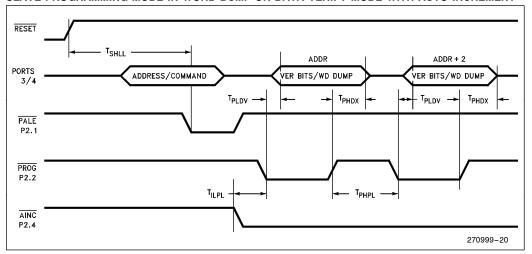

| T <sub>PHDX</sub> | Word Dump Hold Time             |      | 50  | T <sub>OSC</sub> |

| T <sub>PHPL</sub> | PROG High to next PROG Low      | 220  |     | T <sub>OSC</sub> |

| T <sub>LHPL</sub> | PALE High to PROG Low           | 220  |     | Tosc             |

| T <sub>PLDV</sub> | PROG Low to Word Dump Valid     |      | 50  | Tosc             |

| T <sub>SHLL</sub> | RESET High to First PALE Low    | 1100 |     | T <sub>OSC</sub> |

| T <sub>PHIL</sub> | PROG High to AINC Low           | 0    |     | T <sub>OSC</sub> |

| T <sub>ILIH</sub> | AINC Pulse Width                | 240  |     | T <sub>OSC</sub> |

| T <sub>ILVH</sub> | PVER Hold after AINC Low        | 50   |     | T <sub>OSC</sub> |

| T <sub>ILPL</sub> | AINC Low to PROG Low            | 170  |     | Tosc             |

| T <sub>PHVL</sub> | PROG High to PVER Valid         |      | 220 | T <sub>OSC</sub> |

### DC EPROM PROGRAMMING CHARACTERISTICS

| Symbol | Parameter                                  | Min | Max | Units |

|--------|--------------------------------------------|-----|-----|-------|

| Ірр    | V <sub>PP</sub> Programming Supply Current |     | 200 | mA    |

$V_{PP}$  must be within 1V of  $V_{CC}$  while  $V_{CC} < 4.5$ V.  $V_{PP}$  must not have a low impedance path to ground or  $V_{SS}$  while  $V_{CC} > V_{PP}$

<sup>1.</sup> Run-time programming is done with Fosc = 6.0 MHz to 10.0 MHz,  $V_{CC}$ ,  $V_{PD}$ ,  $V_{REF}$  = 5V  $\pm$ 0.5V,  $T_{C}$  = 25°C  $\pm$ 5°C and  $V_{PP}$  = 12.5V  $\pm$ 0.25V. For run-time programming over a full operating range, contact factory. 2. Programming specifications are not tested, but guaranteed by design.

<sup>3.</sup> This specification is for the word dump mode. For programming pulses use 300 Tosc + 100  $\mu$ s.

## **EPROM PROGRAMMING WAVEFORMS**

### SLAVE PROGRAMMING MODE DATA PROGRAM MODE WITH SINGLE PROGRAM PULSE

## SLAVE PROGRAMMING MODE IN WORD DUMP OR DATA VERIFY MODE WITH AUTO INCREMENT

### SLAVE PROGRAMMING MODE TIMING IN DATA PROGRAM MODE WITH REPEATED PROG PULSE AND AUTO INCREMENT

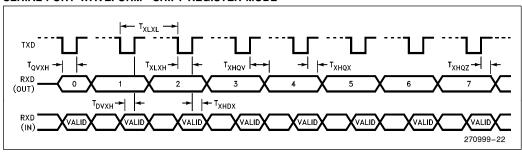

## AC CHARACTERISTICS—SERIAL PORT-SHIFT REGISTER MODE

SERIAL PORT TIMING—SHIFTING REGISTER MODE Test Conditions:  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ ;  $V_{CC} = 5.0V \pm 10\%$ ;  $V_{SS} = 0.0V$ ; Load Capacitance = pF

| Symbol                | Parameter                                      | Min                      | Max                     | Units |

|-----------------------|------------------------------------------------|--------------------------|-------------------------|-------|

| T <sub>XLXL</sub>     | Serial Port Clock Period                       | 8 T <sub>OSC</sub>       |                         | ns    |

| T <sub>XLXH</sub>     | Serial Port Clock Falling Edge to Rising Edge  | 4 T <sub>OSC</sub> - 50  | T <sub>OSC</sub> + 50   | ns    |

| T <sub>QVXH</sub>     | Output Data Setup to Clock Rising Edge         | 3 T <sub>OSC</sub>       |                         | ns    |

| T <sub>XHQX</sub>     | Output Data Hold after Clock Rising Edge       | 2 T <sub>OSC</sub> - 50  |                         | ns    |

| T <sub>XHQV</sub>     | Next Output Data Valid after Clock Rising Edge |                          | 2 T <sub>OSC</sub> + 50 | ns    |

| T <sub>DVXH</sub>     | Input Data Setup to Clock Rising Edge          | 2 T <sub>OSC</sub> + 200 |                         | ns    |

| T <sub>XHDX</sub> (8) | Input Data Hold after Clock Rising Edge        | 0                        |                         | ns    |

| T <sub>XHQZ</sub> (8) | Last Clock Rising to Output Float              |                          | 5 T <sub>OSC</sub>      | ns    |

8. Parameters not tested.

### WAVEFORM—SERIAL PORT—SHIFT REGISTER MODE

#### SERIAL PORT WAVEFORM—SHIFT REGISTER MODE

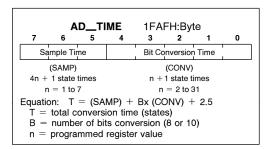

#### A TO D CHARACTERISTICS

The sample and conversion time of the A/D converter in the 8-bit or 10-bit modes is programmed by loading a byte into the AD\_TIME Special Function Register. This allows optimizing the A/D operation for specific applications. The AD\_TIME register is functional for all possible values, but the accuracy of the A/D converter is only guaranteed for the times specified in the operating conditions table.

The value loaded into AD\_TIME bits 5, 6, 7 determines the sample time, SAMP. The value loaded into AD\_TIME bits 0, 1, 2, 3 and 4 determines the bit conversion time, CONV. These bits, as well as the equation for calculating the total conversion time, T, are shown in the following table:

The converter is ratiometric, so absolute accuracy is dependent on the accuracy and stability of  $V_{\text{REF}}$  was to close to  $V_{\text{CC}}$  since it supplies both the resistor ladder and the analog portion of the converter and input port pins. There is also an AD\_TEST SFR that allows for conversion on ANGND and  $V_{\text{REF}}$  as well as adjusting the zero offset. The absolute error listed is without doing any adjustments.

#### A/D CONVERTER SPECIFICATION

The specifications given assume adherence to the operating conditions section of this data sheet. Testing is performed with  $V_{REF}=5.12V$  and 16 MHz operating frequency. After a conversion is started, the device is placed in IDLE mode until the conversion is complete.

## 10-BIT MODE A/D OPERATING CONDITIONS

| Symbol            | Description            | Min  | Max   | Units             |

|-------------------|------------------------|------|-------|-------------------|

| T <sub>A</sub>    | Ambient Temperature    | -40  | + 125 | °C                |

| V <sub>CC</sub>   | Digital Supply Voltage | 4.50 | 5.50  | V                 |

| V <sub>REF</sub>  | Analog Supply Voltage  | 4.50 | 5.50  | V(1)              |

| T <sub>SAM</sub>  | Sample Time            | 2.0  |       | μS <sup>(2)</sup> |

| T <sub>CONV</sub> | Conversion Time        | 15   | 18    | μS <sup>(2)</sup> |

| Fosc              | Oscillator Frequency   | 4.0  | 16.0  | MHz               |

#### NOTES:

- V<sub>REF</sub> must be within 0.5V of V<sub>CC</sub>.

The value of AD\_TIME is selected to meet these specifications.

## 10-BIT MODE A/D CHARACTERISTICS (Using Above Operating Conditions)(6)

| Parameter                                                                       | Typ*(1)                 | Min        | Max        | Units*                           |

|---------------------------------------------------------------------------------|-------------------------|------------|------------|----------------------------------|

| Resolution                                                                      |                         | 1024<br>10 | 1024<br>10 | Level<br>Bits                    |

| Absolute Error                                                                  |                         | 0          | ±3.0       | LSBs                             |

| Full Scale Error                                                                | 0.25 ±0.5               |            |            | LSBs                             |

| Zero Offset Error                                                               | 0.25 ±0.5               |            |            | LSBs                             |

| Non-Linearity                                                                   | 1.0 ±2.0                |            | ±3.0       | LSBs                             |

| Differential Non-Linearity                                                      |                         | -0.75      | + 0.75     | LSBs                             |

| Channel-to-Channel Matching                                                     | ±0.1                    | 0          | ±1.0       | LSBs                             |

| Repeatability                                                                   | ±0.25                   | 0          |            | LSBs <sup>(1)</sup>              |

| Temperature Coefficients:<br>Offset<br>Full Scale<br>Differential Non-Linearity | 0.009<br>0.009<br>0.009 |            |            | LSB/C(1)<br>LSB/C(1)<br>LSB/C(1) |

| Off Isolation                                                                   |                         | -60        |            | dB(1,2,3)                        |

| Feedthrough                                                                     | -60                     |            |            | dB(1,2)                          |

| V <sub>CC</sub> Power Supply Rejection                                          | -60                     |            |            | dB(1,2)                          |