# **OKI** Semiconductor

# MSM6962/6963

Single Chip CODEC

# **GENERAL DESCRIPTION**

The MSM6962 and MSM6963 are a single-channel CODEC CMOSICs containing filters for A/D and D/A converting of the voice signal ranging from 300 Hz to 3400 Hz.

# **FEATURES**

Compliance with ITU-T companding Law

MSM6962: μ-law MSM6963: A-law

Enable independent operation of transmission and reception

Transmission clock: 512, 1024, 1536, 1544, 2048 kHz

• Built-in an Auto compensation circuit for off set voltage, so long steady operation is held

• Built-in reference voltage source

· Low Power Dissipation

(55 mW Typ.) Operating Standby ( 6 mW Typ.)

• Package:

(DIP16-P-300) 16-pin plastic DIP

Note: The product names are indicated in PIN CONFIGURATION.

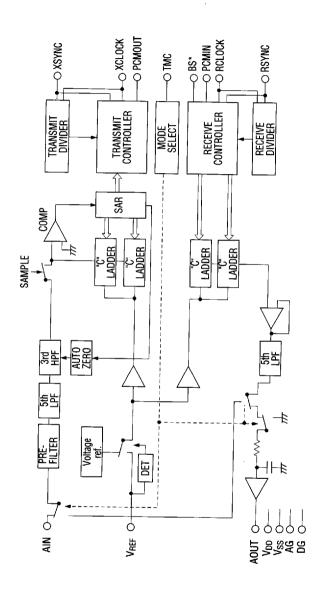

# **BLOCK DIAGRAM**

<sup>\*</sup> Only the MSM6962. The pin is not connected in the MSM6963.

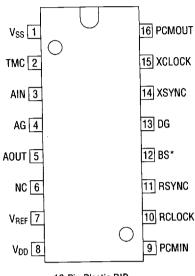

# PIN CONFIGURATION (TOP VIEW)

16-Pin Plastic DIP MSM6962RS/MSM6963RS

Notes:

Indication of product depends on abbreviation type, M6962 or M6963.

BS is only for the MSM6962, and is not connected in the MSM6963.

NC: No connect pin

# PIN AND FUNCTIONAL DESCRIPTIONS

#### V<sub>SS</sub> pin1

Negative voltage power supply. The range of power supply voltage is  $-5 \text{ V} \pm 5\%$ .

## TMC pin2

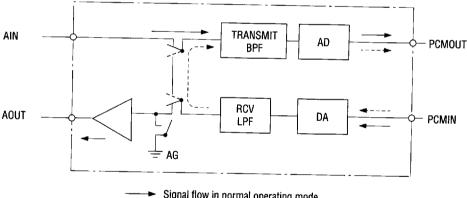

Control signal input for mode selection.

The normal operating mode or analog loop-back mode can be selected.

| "TMC"   | Mode                | "AIN"                 | "AOUT"                                                              |

|---------|---------------------|-----------------------|---------------------------------------------------------------------|

| > 2.0 V | Normal<br>Operation | Transmit signal input | Receive signal output Connected to RCV <sub>FIL</sub> output "AOUT" |

| < 0.8 V | Analog<br>Loop-back | Disconnected          | 0 V                                                                 |

Signal flow in normal operating mode

Signal flow in analog loop-back mode

Since the TMC input signal is monitored on each frame by internal XSYNC pulse, the control for mode selection by TMC signal is not executed in the no-signal state of XSYNC and XCLOCK.

#### AIN pin 3

AIN is an analog signal input and is normally connected to the transmit filter input.

$The input analog signal is bandwidth-limited to (300\,Hz to 3400\,Hz) and is converted to the 8-bit PCM and the support of the 1000 Hz to 10000$

signal.

The input signal amplitude range is  $5\,V_{P.P.}$  In analog loop-back mode, the state of this pin is left open. Since this pin is high impedance input, a resister of  $20\,\mathrm{k}\Omega$  or less should be connected between this pin and AG pin, in the case of AC connection circuit to this pin. (Where DC current is cut off to this pin by external condenser.)

## AG pin 4

Analog signal ground.

#### AOUT pin 5

Analog signal output.

AOUT is connected to an output of the receive filter. The output signal amplitude range is  $5\,\mathrm{V}_{\mathrm{P-P}}$ . The signal level is  $0\,\mathrm{V}$  at analog loop-back mode. This output signal is able to drive a resister load of  $10\,\mathrm{k}\Omega$  or more, but it is recommendable to drive as higher resister as possible. A level of this pin is fixed to  $0\,\mathrm{V}$ , when powered down.

## NC pin 6

Non-connected.

#### V<sub>REF</sub> pin 7

Input of the external reference voltage source.

When a state of this pin is open or less than 2 V, the internal reference voltage source is applied. When the internal reference voltage source is used, the pin should be connected to the AG pin.

When an external reference voltage source is used, the power dissipation of this device is reduced by 20%, and the external reference voltage should be  $+2.5 \text{ V} \pm 5\%$ .

#### V<sub>DD</sub> pin 8

Positive voltage power supply.

The range of supply voltage is  $+5 \text{ V} \pm 5\%$ .

#### PCMIN pin 9

PCM signal input.

The serial input PCM signal is converted from digital to analog, synchronizing with the synchronous signal RSYNC and clock signal RCLOCK.

The data rate of PCM signal is one of 512, 1024, 1536, 1544, and 2048 kbps.

The PCM signal is read at the falling edge of the clock signal and latched into the internal register when finished to read eight bits data.

The top of the PCM data is specified by RSYNC pulse timing.

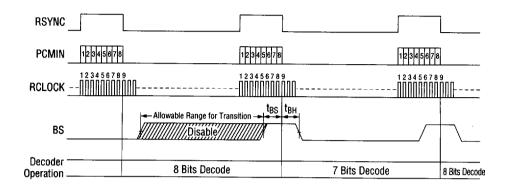

## **RCLOCK pin 10**

Receive clock pulse input.

The frequency of this clock pulse should be identified with the data rate of PCM input signal at the PCMIN pin.

This clock pulse needs to be continious signal, and is used for the clock signal in SCF filter and timing signal in D/A converter by directly dividing this frequency count.

The frequency deviation must be in  $\pm 50$  ppm or less, to guarantee frequency characteristics of the filter. But where the frequency characteristics of an applied system is not specified exactly, the RCLOCK clock pulse count's between pules of RSYNC are allowed within the range of table shown below, for the normal operation mode.

But the electrical characteristics of this device can not be guaranteed.

| PCMIN Data Rate | Clock Pulse Count between RSYNC Pulse |      |      |  |  |  |  |

|-----------------|---------------------------------------|------|------|--|--|--|--|

|                 | Ave.                                  | Min. | Max. |  |  |  |  |

| 512 kbps        | 64                                    | 64   | 65   |  |  |  |  |

| 1024 kbps       | 128                                   | 127  | 130  |  |  |  |  |

| 1536 kbps       | 192                                   | 190  | 195  |  |  |  |  |

| 1544 kbps       | 193                                   | 190  | 195  |  |  |  |  |

| 2048 kbps       | 256                                   | 253  | 257  |  |  |  |  |

#### RSYNC pin 11

Receive synchronizing signal input.

Eight required bits are selected from serial PCM signals on the PCMIN pin by the receive synchronizing signal.

The whole timing signal in the receive section are synchronized by this synchronizing signal.

This signal must be synchronize in phase with RCLOCK.

The frequency should be 8 kHz  $\pm 50$  ppm to guarantee the AC characteristics of receive section. However, same as the RCLOCK frequency, this device can operate in the range of 8 kHz  $\pm 4$  kHz, with no guarantee of adherence to the electrical characteristics in this specification as a catalogue value. Fixing this signal to logic "1" or "0", the receive circuit is driver in a power down state.

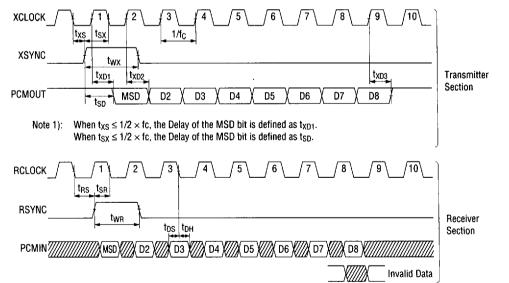

#### BS pin 12

Control signal input for decoding seven bits signal.

The PCM signal from first bit through seventh bit in a frame including the transition point of a signal to this pin, is decoded. The least significant bit is invalid.

Normally, this pin is fixed level "H" or "L".

The MSM6963 does not include this function.

## DG pin 13

Ground for digital signal.

This pin is not connected to the AG pin.

#### XSYNC pin 14

Transmit synchronizing signal input.

The PCM output signal from PCMOUT pin is output in synchronization with this transmit synchronizing signal.

All transmit timing signals are triggered to synchronize with this signal. This signal should be synchronized in phase with XCLOCK pulse.

The frequency should be 8 kHz ±50 ppm to guarantee the AC characteristics of transmit section.

In the frequency range of 8 kHz ±4 kHz, even if the device circuit operates, same as on XCLOCK, the specification for the electrical characteristics is not guaranteed.

Fixing this signal to logic "1" or "0", the transmit circuit is driver in a power down state.

#### XCLOCK pin 15

Transmit clock input.

The PCM output data rate from the PCMOUT pin is set by this clock frequency.

The usable clock frequency is one of 512, 1024, 1536, 1544, and 2048 kHz.

This clock pulse must to be a continuous signal since the clock pulse is used as the clock pulse of SCF filter and the timing signal of A/D convertion.

To guarantee the frequency characteristics of the filter, the frequency deviation of the clock signal must be  $\pm 50$  ppm or less.

However when the frequency characteristic of an applicate system is not specified exactly, if the XCLOCK clock counts in between the pulses of signal XSYNC are allowed in the range of table shown below, the device operates but the specified electrical characteristics is not guaranteed.

| Clock Frequency | Clock Pulse Count between XSYNC Pulse Perio |      |      |  |  |  |  |

|-----------------|---------------------------------------------|------|------|--|--|--|--|

| Olock Frequency | Ave.                                        | Min. | Max. |  |  |  |  |

| 512 kHz         | 64                                          | 64   | 65   |  |  |  |  |

| 1024 kHz        | 128                                         | 127  | 130  |  |  |  |  |

| 1536 kHz        | 192                                         | 190  | 195  |  |  |  |  |

| 1544 kHz        | 193                                         | 190  | 195  |  |  |  |  |

| 2048 kHz        | 256                                         | 253  | 257  |  |  |  |  |

#### PCMOUT pin 16

PCM signal output.

The PCM output signal is output in synchronization with the rising edge of XCLOCK pulse orderly from MSB first. (The first bit of the PCM signal may output at the rising edge of XSYNC pulse, according to mutual timing of XSYNC and XCLOCK pulse.). During the PCMOUT signal output except the 8 bit- pulses, the pin is in an open state, therefore, multiple connections by wired-OR are easily possible at this pin.

The code companding law and output code format depend on ITU-T Recommendation G. 711, and for the MSM6963 (A-law) the output PCM signals are obtained by inverting the even bits of signals.

| input/Output |                 |   |   |   |   |                 | F | CMIN/ | PCMOU | IT |   |   |   |          |   |    |

|--------------|-----------------|---|---|---|---|-----------------|---|-------|-------|----|---|---|---|----------|---|----|

| Level        | MSM6962 (μ-law) |   |   |   |   | MSM6963 (A-law) |   |       |       |    |   |   |   |          |   |    |

| +Full scale  | 1               | 0 | 0 | 0 | 0 | 0               | 0 | 0     | 1     | 0  | 1 | 0 | 1 | 0        | 1 | 0  |

| +0           | 1               | 1 | 1 | 1 | 1 | 1               | 1 | 1     | 1     | 1  | 0 | 1 | 0 | 1        | 0 | 1  |

| -0           | 0               | 1 | 1 | 1 | 1 | 1               | 1 | 1     | 0     | 1  | 0 | 1 | 0 | 1        | 0 | 1  |

| -Full scale  | 0               | 0 | 0 | 0 | 0 | 0               | 0 | 0     | 0     | 0  | 1 | 0 | 1 | <u>·</u> | 1 | 'n |

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter             | Symbol           | Condition    | Rating                           | Unit |

|-----------------------|------------------|--------------|----------------------------------|------|

| Power Supply Voltage  | V <sub>DD</sub>  | <del>_</del> | 0 to 7                           | ٧    |

|                       | V <sub>SS</sub>  |              | -7 to 0                          | ٧    |

| Reference Voltage     | V <sub>REF</sub> | <del>_</del> | 0 to V <sub>DD</sub>             | ٧    |

| Analog Input Voltage  | VAIN             | _            | $V_{DD}$ = 0.3 to $V_{DD}$ + 0.3 | ٧    |

| Digital Input Voltage | V <sub>DIN</sub> | _            | -0.3 to V <sub>DD</sub> + 0.3    | ٧    |

| Operating Temperature | Top              | _            | -10 to 80                        | °C   |

| Storage Temperature   | T <sub>STG</sub> | *****        | -55 to 150                       | °C   |

#### RECOMMENDED OPERATING CONDITIONS

(Ta = 0°C to 70°C)

| Parameter                                | Symbol           | Condition                            | Min.  | Тур.                             | Max.            | Unit |  |

|------------------------------------------|------------------|--------------------------------------|-------|----------------------------------|-----------------|------|--|

| Power Supply Voltage                     | V <sub>DD</sub>  | _                                    | 4.75  | 5                                | 5.25            | ٧    |  |

| rower supply voltage                     | V <sub>SS</sub>  | _                                    | -5.25 | -5                               | -4.75           | ٧    |  |

| Reference Voltage                        | V <sub>REF</sub> | When using external V <sub>REF</sub> | 2.475 | 2.5                              | 2.525           | ٧    |  |

| Analog Input Voltage                     | V <sub>AIN</sub> |                                      | _     | -                                | 5               | Vp.p |  |

| Input High Voltage                       | V <sub>IH</sub>  | XSYNC, XCLOCK, PCMIN,                | 2.0   | 2.4                              | V <sub>DD</sub> | ٧    |  |

| Input Low Voltage                        | V <sub>IL</sub>  | RSYNC, RCLOCK, TMC, BS               | 0     | 0                                | 0.8             | ٧    |  |

| Clock Frequency                          | f <sub>C</sub>   | XCLOCK, RCLOCK                       |       | 512, 1024<br>1536, 1544,<br>2048 | _               | kHz  |  |

| Sync Pulse Frequency                     | fs               | XSYNC, RSYNC                         | _     | 8                                | _               | kHz  |  |

| Clock Duty Ratio                         | DL               | XCLOCK, RCLOCK                       | 40    | 50                               | 60              | %    |  |

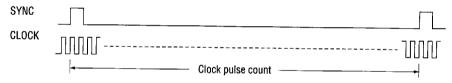

| Digital Input Rise Time                  | tir              | XSYNC, XCLOCK, PCMIN,                | _     | _                                | 50              | ns   |  |

| Digital Input Fall Time                  | t <sub>if</sub>  | RSYNC, RCLOCK (Fig. 1)               | _     |                                  | 50              | ns   |  |

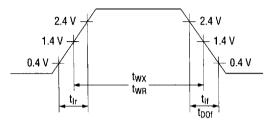

| T                                        | txs              | XCLOCK→XSYNC (Fig. 2)                | 50    | _                                | <del></del>     | ns   |  |

| Transmit Sync Timing                     | t <sub>SX</sub>  | XSYNC→XCLOCK (Fig. 2)                | 100   | _                                |                 | ns   |  |

| Receive Sync Timing                      | t <sub>RS</sub>  | RCLOCK→RSYNC (Fig. 2)                | 50    | _                                | _               | ns   |  |

| neceive sync rinning                     | t <sub>SR</sub>  | RSYNC→RCLOCK (Fig. 2)                | 100   | _                                | _               | ns   |  |

| Transmit Sync Pulse Width                | t <sub>WX</sub>  | _                                    | 1/fc  | _                                | 117             | μs   |  |

| Receive Sync Pulse Width                 | twR              | _                                    | 1/fc  | _                                | 117             | μS   |  |

| PCMIN Set-up Time                        | t <sub>DS</sub>  | _                                    | 100   | _                                |                 | ns   |  |

| PCMIN Hold Time                          | t <sub>DH</sub>  | <del>_</del>                         | 100   | _                                | _               | ns   |  |

| BS Set-up Time *                         | t <sub>BS</sub>  | _                                    | 200   | _                                | _               | ns   |  |

| BS Hold Time *                           | tвн              | _                                    | 200   | _                                |                 | ns   |  |

| Analog Output Lood                       | R <sub>AL</sub>  | AOUT                                 | 10    | 20                               | _               | kΩ   |  |

| Analog Output Load                       | CAL              | AOUT                                 | _     | _                                | 100             | pF   |  |

| Digital Output Load                      | R <sub>DL</sub>  | PCMOUT                               | 1     | _                                | _               | kΩ   |  |

| Digital Output Loau                      | C <sub>DL</sub>  | PUNDUT                               | _     |                                  | 100             | pF   |  |

| Allowable Analog Input<br>Offset Voltage | V <sub>IO</sub>  | _                                    | -200  | _                                | 200             | mV   |  |

<sup>\*:</sup> The value for the MSM6962

## **ELECTRICAL CHARACTERISTICS**

## **DC and Digital Interface Characteristics**

$(V_{DD} = +5 \text{ V } \pm 5\%, V_{SS} = -5 \text{ V } \pm 5\%, Ta = 0^{\circ}\text{C to } 70^{\circ}\text{C})$

| Parameter                    | Symbol           | Condition                             | Min. | Тур.  | Max. | Unit |  |

|------------------------------|------------------|---------------------------------------|------|-------|------|------|--|

| Power Supply Current         | I <sub>DD1</sub> | XCLOCK, RCLOCK                        | _    | 5.5   | 11   |      |  |

| (Operating)                  | I <sub>SS1</sub> | 2048 kHz                              | _    | 5.0   | 11   | mA   |  |

| Power Supply Current         | I <sub>DD2</sub> |                                       | _    | 0.8   | 3.0  |      |  |

| (Stand-by)                   | I <sub>SS2</sub> | _                                     | _    | 0.3   | 1.5  | mA   |  |

| Reference Current            | IREF             | When external V <sub>REF</sub> input. | _    | 5     | 100  | μА   |  |

| Input High Voltage           | ViH              |                                       | 2.0  | _     |      | ٧    |  |

| Input Low Voltage            | V <sub>IL</sub>  |                                       | _    |       | 0.8  | V    |  |

| Insut Lookaga Current        | lін              |                                       | _    | < 0.5 | 2.0  |      |  |

| Input Leakage Current        | I <sub>IL</sub>  |                                       | _    | < 0.2 | 0.5  | μΑ   |  |

| Output Low Voltage           | V <sub>OL</sub>  |                                       | _    | 0.1   | 0.4  | ٧    |  |

| Output Leakage Current       | Іон              |                                       |      | < 5   | 10   | μА   |  |

| Analog Output Offset Voltage | V <sub>OFF</sub> |                                       | -150 | 0     | 150  | mV   |  |

| Input Capacitance            |                  | Except for AIN                        | _    | 5     | _    |      |  |

|                              | Cin              | AIN                                   | _    | 5     | _    | pF   |  |

| Analog Input Resistance      | R <sub>IN</sub>  | f <sub>IN</sub> < 3.4 kHz             | _    | 1     | _    | MΩ   |  |

#### **AC Characteristics**

$(V_{DD} = +5 \text{ V} \pm 5\%, V_{SS} = -5 \text{ V} \pm 5\%, Ta = 0^{\circ}\text{C to } 70^{\circ}\text{C})$

|                                       |                     |       | Condition |    |       |           |             | <u> </u> |

|---------------------------------------|---------------------|-------|-----------|----|-------|-----------|-------------|----------|

| Parameter                             | Symbol              | Freq. | Level     |    | Min.  | Тур.      | Max.        | Unit     |

|                                       |                     | (Hz)  | (dBmO)    |    |       |           |             |          |

|                                       | Loss T1             | 60    |           |    | 20    | 26        | _           |          |

|                                       | L <sub>OSS</sub> T2 | 300   | ]         |    | ~0.1  | -0.03     | 0.2         |          |

| Tanamit Farance Danas                 | Loss T3             | 820   | ] ,       |    |       | Reference |             | ا ا      |

| Transmit Frequency Response           | Loss T4             | 2020  | 0         | =  | -0.1  | 0.0       | 0.2         | dB       |

|                                       | L <sub>OSS</sub> T5 | 3000  |           |    | -0.1  | 0.10      | 0.2         |          |

|                                       | Loss T6             | 3400  | 1         |    | 0     | 0.45      | 0.8         | 1        |

|                                       | L <sub>OSS</sub> R1 | 300   |           |    | -0.1  | -0.02     | 0.2         |          |

|                                       | L <sub>OSS</sub> R2 | 820   |           |    |       | Reference |             | 1        |

| Receive Frequency Response            | L <sub>OSS</sub> R3 | 2020  | 0         | ļ  | -0.1  | 0.0       | 0.2         | dB       |

|                                       | Loss R4             | 3000  |           |    | -0.1  | 0.10      | 0.2         | 1        |

|                                       | L <sub>OSS</sub> R5 | 3400  |           |    | 0     | 0.65      | 0.8         | 1        |

|                                       | SD T1               |       | 3         |    | 37    | 43        | 1           |          |

| Torresia Circulas Districtor          | SD T2               | 1020  | 0         |    | 37    | 41        | <del></del> | 1        |

| Transmit Signal to Distortion         | SD T3               | or    | -30       |    | 37    | 40        |             | dB       |

| Ratio *1                              | SD T4               | 820   | -40       | *2 | 32/31 | 34.5/33   | _           |          |

|                                       | SD T5               |       | -45       | *2 | 28/26 | 31/28.5   | _           |          |

|                                       | SD R1               |       | 3         |    | 37    | 44        |             |          |

| Descive Cianal to Distortion          | SD R2               | 1020  | 0         |    | 37    | 41        | _           |          |

| Receive Signal to Distortion Ratio *1 | SD R3               | or    | -30       |    | 37    | 41        | _           | dB       |

| nauo i                                | SD R4               | 820   | -40       | *2 | 32/32 | 35.5/35   | _           |          |

|                                       | SD R5               |       | -45       | *2 | 28/26 | 34/28.5   | _           | 1        |

|                                       | GT T1               |       | 3         | _  | -0.2  | -0.01     | 0.2         |          |

|                                       | GT T2               | 1020  | -10       |    |       | Reference |             |          |

| Transmit Gain Tracking                | GT T3               | or    | -40       |    | -0.2  | 0.05      | 0.2         | dB       |

|                                       | GT T4               | 820   | -50       |    | -0.4  | 0.25      | 0.4         |          |

|                                       | GT T5               |       | -55       |    | -0.8  | 0.10      | 0.8         |          |

|                                       | GT R1               |       | 3         |    | -0.2  | 0.02      | 0.2         |          |

|                                       | GT R2               | 1020  | -10       |    |       | Reference | l           |          |

| Receive Gain Tracking                 | GT R3               | or    | -40       |    | -0.2  | -0.05     | 0.2         | dB       |

|                                       | GT R4               | 820   | -50       |    | -0.4  | -0.16     | 0.4         |          |

|                                       | GT R5               |       | -55       |    | -0.8  | -0.31     | 0.8         |          |

Notes: \*1 The measurement is taken with P-message filter

<sup>\*2</sup> The value before "/" is for the MSM6962 and the value after "/" for the MSM6963

## **AC Characteristics (Continued)**

$(V_{DD} = +5 \text{ V} \pm 5\%, V_{SS} = -5 \text{ V} \pm 5\%, Ta = 0^{\circ}\text{C to } 70^{\circ}\text{C})$

|                                 |                  |                    |                            | Conditio | n<br>n               |      |       |       | T      |  |

|---------------------------------|------------------|--------------------|----------------------------|----------|----------------------|------|-------|-------|--------|--|

| Paramete                        | Parameter        |                    | Freq.                      | Level    | ]                    | Min. | Тур.  | Max.  | Unit   |  |

|                                 |                  |                    | (Hz)                       | (dBmO)   |                      |      |       |       |        |  |

| Idle Channel                    | Transmit         | N <sub>IDL</sub> T | _                          | _        |                      | _    | -89   | -75   | 40     |  |

| Noise *1                        | Receive          | N <sub>IDL</sub> R | _                          | _        | 1                    | _    | -89   | -75   | dBmOp  |  |

| Absolute Gain *3                | Transmit         | AV T               | 1020 or 820                | 0        |                      | -0.5 | 0     | 0.5   | - J.D. |  |

| Absolute dalli                  | Receive          | AV R               | 1020 or 820                | 0        |                      | -0.5 | 0     | 0.5   | dB     |  |

| Absolute Delay Time             |                  | t <sub>D</sub>     |                            | 0        |                      | _    | 0.47  | 0.5   | ms     |  |

|                                 |                  | t <sub>GD</sub> T1 | 500                        | -        |                      | _    | 0.2   | 0.75  |        |  |

|                                 |                  | t <sub>GD</sub> T2 | 600                        |          |                      |      | 0.1   | 0.35  |        |  |

| Transmit Group Delay            | Time *4          | t <sub>GD</sub> T3 | 1000                       | 0        |                      |      | 0     | 0.125 | ms     |  |

|                                 |                  | t <sub>GD</sub> T4 | 2600                       |          |                      |      | 0.05  | 0.125 |        |  |

|                                 |                  | t <sub>GD</sub> T5 | 2800                       |          |                      | _    | 0.07  | 0.75  | 1      |  |

|                                 |                  | t <sub>GD</sub> R1 | 500                        |          |                      | _    | -0.02 | 0.75  |        |  |

|                                 |                  | t <sub>GD</sub> R2 | 600                        |          |                      | _    | -0.02 | 0.35  |        |  |

| Receive Group Delay T           | ime *4           | t <sub>GD</sub> R3 | 1000                       | 1000 0   |                      | _    | -0.03 | 0.125 | ms     |  |

|                                 |                  | t <sub>GD</sub> R4 | R4 2600                    |          |                      | _    | 0.07  | 0.125 |        |  |

|                                 |                  | t <sub>GD</sub> R5 | 2800                       |          |                      | _    | 0.10  | 0.75  | 1      |  |

| Crosstalk Attenuation           | T to R           | C <sub>R</sub> T   | 1020 or 820                |          |                      | _    | 78    | 66    | - JD   |  |

| - Grossiaik Atteriuation        | R to T           | C <sub>R</sub> R   | 1020 or 820                | _        |                      | _    | 90    | 66    | dB     |  |

| Out-of-Band Spurious            |                  | S                  | 300 to 3400                | 0        |                      | -30  | -33   |       | dBm0   |  |

| Intermodulation Distor          | tion             | IMD 1              | $f_a = 470$<br>$f_b = 320$ | -4       | $2 \times f_a - f_b$ | _    | -40   | -35   | dBm0   |  |

| Discrimination                  |                  | DIS                | 4.6 kHz to<br>72 kHZ       | 0        |                      | 30   | 32    | _     | dB     |  |

| V <sub>DD</sub> Noise Rejection | Transmit         | PPSR T             | -                          |          |                      |      | 30    | _     |        |  |

| Ratio                           | Receive          | PPSR R             | 0 to 300                   | 200      |                      |      | 30    |       | -      |  |

| V <sub>SS</sub> Noise Rejection | ction Transmit N |                    | kHz                        | mVp-p    |                      |      | 30    | _     | dB     |  |

| Ratio                           | Receive          | NPSR R             |                            |          |                      | _    | 30    |       | 1      |  |

| Digital Output Delay Time       |                  | tsD                |                            |          | .,                   | 50   | 150   | 300   |        |  |

|                                 |                  | t <sub>XD1</sub>   | $R_{DL} = 2 ks$            | Ω        | ļ                    | 50   | 100   | 300   |        |  |

|                                 |                  | t <sub>XD2</sub>   | C <sub>DL</sub> = 100      | pF       |                      | 50   | 100   | 300   | ns     |  |

|                                 |                  | t <sub>XD3</sub>   |                            |          | Ī                    | 50   | 180   | 300   |        |  |

| Digital Output Fall Time        |                  | t <sub>DO</sub>    |                            |          |                      | _    | 20    | 100   | ns     |  |

Notes:

- \*1 The measurement is taken with P-message filter

- \*2 The value before "/" is for the MSM6962 and the value after "/" for the MSM6963

- \*3 0 dB + 1.252 Vrms

- \*4 Reference: 1800 Hz

#### **TIMING DIAGRAM**

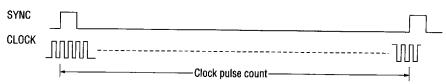

#### **Wave Time Measurement Level**

Note: Timing between signal waves is judged at 1.4 V

Figure 1

#### **Basic Timing**

Note 2): Transmit synchronizing and clock pulse, and Receive synchronizing and clock pulse may be asynchronous mutually.

Note 3): The threshold level is 1.4 V.

Figure 2

# Timing for 7 Bits Decode (Specified for MSM6962)

Figure 3

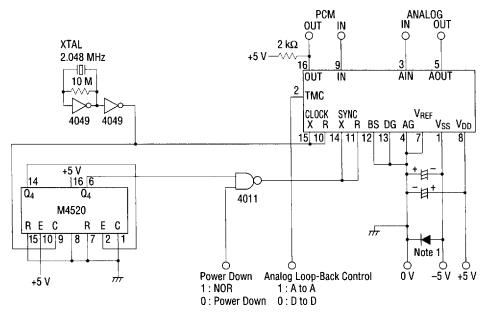

#### APPLICATION CIRCUIT

#### **Basic Circuit**

Notes:

- Insert diode for preventing from Latch-Up at turn on Power. Recommended Diode Specification.

- High Speed Switching

- Allowerable Power dissipation 250 mW to 300 mW

- Forward Voltage Drop <1.3 V (at 100 mA)

- AG and DG must be connected in the printed circuit board mounted this device, for preventing from Latch-Up.

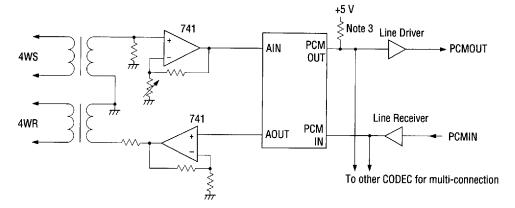

#### **Four-Wire Line Connection**

Connections of power source and clock depend on the basic circuit.

Note: 3. In the case of multi-connection to other CODEC, the pull-up resistance is possibly  $1\,k\Omega$  up to a maximum of 8 CODECs. In this case, take notice that the delay of PCMOUT is larger.

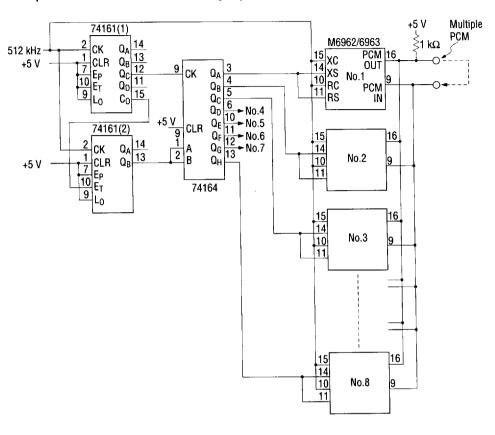

## **Example of Multi-Channel Connections (8ch)**

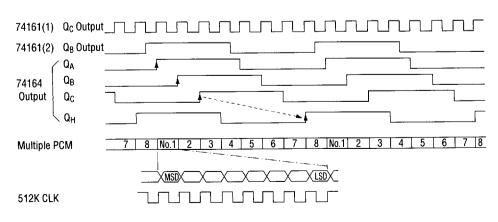

# **Example of Multi-Channel Timing**

## RECOMMENDATIONS FOR ACTUAL DESIGN

- To assure proper electrical characteristics, use bypass capacitors with excellent high frequency characteristics for the power supply and keep them as close as possible to the device pins.

- Connect the AG pin and the DG pin each other as close as possible.

Connected to the system ground with low impedance.

- Mount the device directly on the board when mounted on printed circuit board.

Do not use IC sockets.

If an IC socket is unavoidable, use the short lead type socket.

- When mounted on a frame, use electro-magnetic shielding, if any electro-magnetic wave source such as power supply transformers surround the device.

- Keep the voltage on the V<sub>DD</sub> pin not lower than -0.3 V and the voltage on the V<sub>SS</sub> pin more than +0.3 V even instantaneously to avoid latch-up phenomenon when turning the power on.

- Use a low noise (particularly, low level type of high frequency spike noise or pulse noise) power supply to avoid erroneous operation and the degradation of the characteristics of these devices.