### **Features**

- 4-pin serial interface

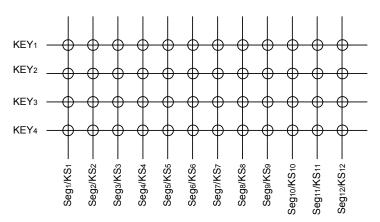

- Key scanning (12x4 matrices)

- Programming display modes (16-digit & 12segment to 8-digit & 20-segment)

- Programming dimming step

- High-voltage output (V<sub>DD</sub>-35V max)

- 5 channels LED ports

- 4-pin general-purpose input port

- Built-in oscillator

- No external resistor necessary for driver outputs

# **General Description**

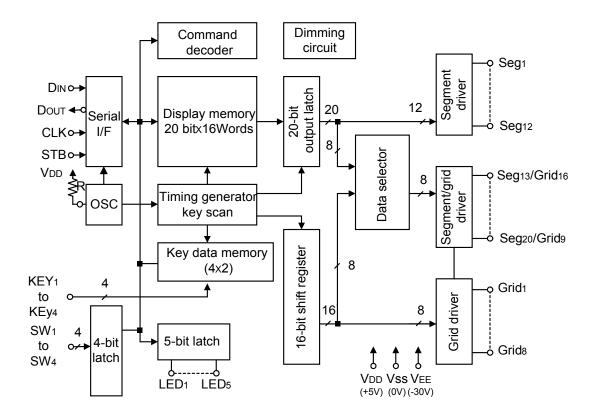

The AD6311 is a VFD (Vacuum Fluorescent Display) controller/driver that is driven on a 1/8- to 1/16 duty factor (include key scan). It consists of 12 segment/key scan output lines, 8 grid output lines, 8 segment/grid output drive lines, a display memory, a control circuit, and a key scan circuit. Serial data is input to the AD6311 through a four-line serial interface.

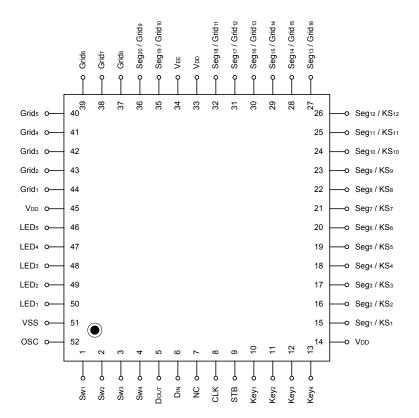

## **Pin Assignments**

Use all the power pins.

# **■** Pin Descriptions

| Symbol                                                                           | Name                               | No.                | Description                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------|------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

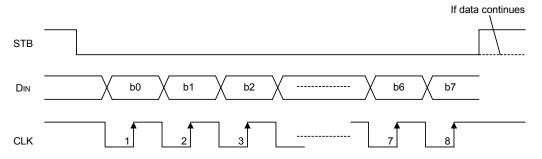

| D <sub>IN</sub>                                                                  | Data input                         | 6                  | Input serial data at rising edge of shift clock, starting from the low order bit.                                                                                                                                                                                                                                       |

| D <sub>OUT</sub>                                                                 | Data output                        | 5                  | Output serial data at the falling edge of the shift clock, starting from low order bit. This is N-ch open-drain output pin.                                                                                                                                                                                             |

| STB                                                                              | Strobe                             | 9                  | Initializes serial interface at the rising or falling edge of the AD6311. It then waits for reception of a command. Data input after STB falling is processed as a command. While command data is processed, current processing is stopped, and the serial interface is initialized. While STB is high, CLK is ignored. |

| CLK                                                                              | Clock input                        | 8                  | Reads serial data at the rising edge, and outputs data at the falling edge.                                                                                                                                                                                                                                             |

| OSC                                                                              | Oscillator pin                     | 52                 | Connect resistor in between this pin and Vdd to set up the oscillation frequency.                                                                                                                                                                                                                                       |

| Seg <sub>1</sub> /KS <sub>1</sub> to<br>Seg <sub>12</sub> /KS <sub>12</sub>      | High-voltage output                | 15 to 26           | Multi-function pins, Segment output pins (Dual function as key scan source)                                                                                                                                                                                                                                             |

| Grid₁ to Grid <sub>8</sub>                                                       | High-voltage output (Grid)         | 37 to 44           | Grid output pins                                                                                                                                                                                                                                                                                                        |

| Seg <sub>13</sub> /Grid <sub>16</sub> to<br>Seg <sub>20</sub> /Grid <sub>9</sub> | High-voltage output (Segment/grid) | 27 to 32<br>35, 36 | These pins are selectable for segment or grid driving.                                                                                                                                                                                                                                                                  |

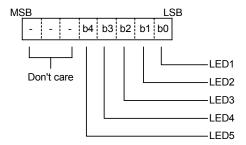

| LED <sub>1</sub> to LED <sub>5</sub>                                             | LED output                         | 46 to 50           | CMOS output                                                                                                                                                                                                                                                                                                             |

| KEY <sub>1</sub> to KEY <sub>4</sub>                                             | Key data input                     | 10 to 13           | Data input to these pins is latched at the end of the display cycle.                                                                                                                                                                                                                                                    |

| $V_{DD}$                                                                         | Logic power                        | 14, 33, 45         | Logic power supply                                                                                                                                                                                                                                                                                                      |

| V <sub>SS</sub>                                                                  | Logic ground                       | 51                 | Connect this pin to system GND.                                                                                                                                                                                                                                                                                         |

| V <sub>EE</sub>                                                                  | Pull-down level                    | 34                 | Driver power supply                                                                                                                                                                                                                                                                                                     |

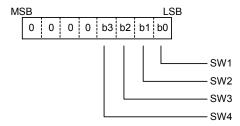

| SW <sub>1</sub> to SW <sub>4</sub>                                               | Switch input                       | 1 to 4             | These pins constitute a 4-bit general-purpose input port.                                                                                                                                                                                                                                                               |

| NC                                                                               | NC                                 | 7                  | No connection                                                                                                                                                                                                                                                                                                           |

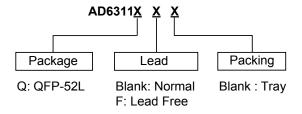

# Ordering Information

# **■** Block Diagram

# ■ Absolute Maximum Ratings (T<sub>A</sub>=25°C,V<sub>SS</sub>=0V)

| Parameter                     | Symbol           | Rating                         | Unit                   |

|-------------------------------|------------------|--------------------------------|------------------------|

| Logic supply voltage          | $V_{DD}$         | -0.5 to +7.0                   | V                      |

| Driver supply voltage         | $V_{EE}$         | $V_{DD}$ +0.5 to $V_{DD}$ -40  | V                      |

| Logic input voltage           | V <sub>I1</sub>  | -0.5 to V <sub>DD</sub> +0.5   | V                      |

| VFD driver output voltage     | V <sub>O2</sub>  | $V_{EE}$ -0.5 to $V_{DD}$ +0.5 | V                      |

| LED driver output current     | I <sub>01</sub>  | +15                            | mA                     |

| VFD driver output current     | l <sub>O2</sub>  | -40(grid) -15 (segment)        | mA                     |

| Operating ambient temperature | T <sub>OPT</sub> | -25 to +85                     | $^{\circ}\!\mathbb{C}$ |

| Storage temperature           | T <sub>STG</sub> | -50 to +125                    | $^{\circ}\!\mathbb{C}$ |

# ■ Operating Conditions (T<sub>A</sub>=0 to +70°C, V<sub>SS</sub>=0V)

| Parameter                | Symbol   | Conditions | Min.               | Тур. | Max.                | Unit |

|--------------------------|----------|------------|--------------------|------|---------------------|------|

| Logic supply voltage     | $V_{DD}$ |            | 4.5                | 5    | 5.5                 | V    |

| High-level input voltage | $V_{IH}$ |            | $0.7 \cdot V_{DD}$ |      | $V_{DD}$            | V    |

| Low-level input voltage  | $V_{IL}$ |            | 0                  |      | $0.3xV_{DD}$        | V    |

| Driver supply voltage    | $V_{EE}$ |            | 0                  |      | V <sub>DD</sub> -35 | V    |

# ■ DC Characteristics $(T_a=0 \text{ to } 70^{\circ}\text{C}, V_{DD}=4.5 \text{ to } 5.5\text{V}, V_{SS}=0\text{V}, V_{EE}=V_{DD}-35\text{V})$

| Parameter                 | Symbol             | Conditions                                                                                                                                                    | Min.        | Тур. | Max.        | Unit     |

|---------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|-------------|----------|

| High-level output voltage | $V_{OH1}$          | LED <sub>1</sub> -LED <sub>5</sub> ,I <sub>OH1</sub> =-1mA                                                                                                    | $0.9V_{DD}$ |      |             | <b>V</b> |

| Low-level output voltage  | $V_{OL1}$          | LED <sub>1</sub> -LED <sub>5</sub> ,I <sub>OL1</sub> =12mA                                                                                                    |             |      | 1           | V        |

| Low-level output voltage  | $V_{OL2}$          | D <sub>OUT</sub> ,I <sub>OL2</sub> =2mA                                                                                                                       |             |      | 0.4         | V        |

| High-level output current | I <sub>OH21</sub>  | V <sub>O</sub> =V <sub>DD</sub> -2V,Seg <sub>1</sub> to Seg <sub>12</sub>                                                                                     | -3          |      |             | mA       |

| High-level output current | I <sub>OH22</sub>  | V <sub>O</sub> =V <sub>DD</sub> -2V,Grid <sub>1</sub> to Grid <sub>8</sub> ,<br>Seg <sub>13</sub> /Grid <sub>16</sub> to Seg <sub>20</sub> /Grid <sub>9</sub> | -15         |      |             | mA       |

| Driver leakage current    | I <sub>OLEAK</sub> | V <sub>O</sub> =V <sub>DD</sub> -35V, driver off                                                                                                              |             |      | -10         | $\mu A$  |

| Output pull-down resistor | $R_L$              | Driver output                                                                                                                                                 | 50          | 100  | 150         | kΩ       |

| High-level input voltage  | V <sub>IH</sub>    |                                                                                                                                                               | $0.7V_{DD}$ |      |             | V        |

| Low-level input voltage   | $V_{IL}$           |                                                                                                                                                               |             |      | $0.3V_{DD}$ | V        |

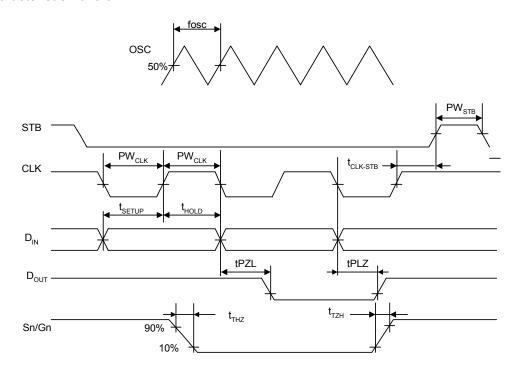

# ■ AC Characteristics $(T_a=0 \text{ to } +70^{\circ}\text{C}, V_{DD}=4.5 \text{ to } 5.5 \text{ V})$

| Parameter               | Symbol               | Conditions           | Min. | Тур. | Max. | Unit   |

|-------------------------|----------------------|----------------------|------|------|------|--------|

| Oscillation frequency   | f <sub>OSC</sub>     | R=51 kΩ              | 350  | 500  | 650  | $KH_Z$ |

| Maximum clock frequency | f <sub>max.</sub>    | Duty=50%             |      |      | 1    | MHz    |

| Clock pulse width       | PW <sub>CLK</sub>    |                      | 500  |      |      | ns     |

| Strobe pulse width      | PW <sub>STB</sub>    |                      | 1    |      |      | μs     |

| Data setup time         | t <sub>SETUP</sub>   |                      | 100  |      |      | ns     |

| Data hold time          | t <sub>HOLD</sub>    |                      | 100  |      |      | ns     |

| Clock-strobe time       | t <sub>CLK-STB</sub> | CLK ↑ →STB ↑         | 1    |      |      | μs     |

| Wait time               | t <sub>WAIT</sub>    | CLK ↑ → CLk ↓ (Note) | 1    |      |      | μs     |

Note: Refer to page 8.

## **■** Function Description

#### 1.0 Command

A command sets the display mode and status of the VFD driver. The first 1 byte input to the AD6311 through the Din pin after the STB pin has fallen is regarded as a command. If STB is made high while a command/data is transmitted, serial communication is initialized, and the command/data being transmitted is invalid (however, the command/data already transmitted remains valid).

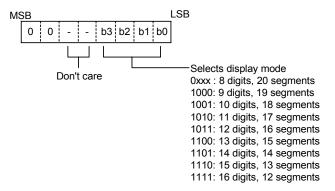

#### 1.1 Display mode setting command

This command initializes the AD6311 and selects the number of segments and number of grids (8 grid & 20 segments to 16 grid & 12 segments). When this command is executed, display is forcibly turned off, and key scanning is also stopped. To resume display, a display ON command must be executed. If the same mode is selected, however, nothing is performed.

On power application, the 16-digit, 12-segment mode is selected.

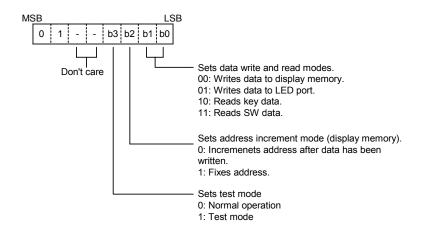

#### 1.2 Data setting command

This command sets data write and data read modes. On power application, the normal operation mode and address increment mode are set.

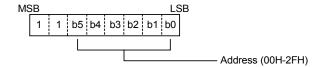

### 1.3 Address setting command

This command sets an address of the display memory. If address 30H or higher is set, the data is ignored, until a correct address is set. On power application, the address is set to 00H.

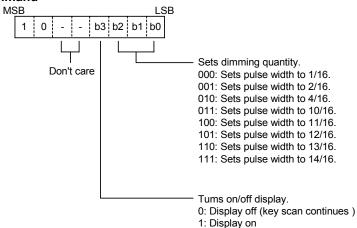

#### 1.4 Display control command

On power application, the 1/16-pulse width is set, the display is turned off and key scanning is stopped.

#### 2.0 Display RAM Address and Display Mode

The display RAM stores the data transmitted from an external device to the AD6311 through the serial interface, and is assigned addresses as follows, in units of 8 bits:

| Seg <sub>1</sub>          | Seg <sub>4</sub> Seg <sub>8</sub> | S                 | eg <sub>12</sub>   | Seg <sub>16</sub> | Seg <sub>20</sub>  |

|---------------------------|-----------------------------------|-------------------|--------------------|-------------------|--------------------|

| 00 H <sub>L</sub>         | :00 H <sub>U</sub>                | 01 H <sub>L</sub> | :01 H <sub>υ</sub> |                   | GRID <sub>1</sub>  |

| 03 H <sub>L</sub>         | 03 H <sub>U</sub>                 | 04 H <sub>L</sub> | 04 H <sub>υ</sub>  | 05 H <sub>L</sub> | GRID <sub>2</sub>  |

| 06 H <sub>L</sub>         | 06 H <sub>∪</sub>                 | 07 H <sub>L</sub> | $07~H_{U}$         | 08 H <sub>L</sub> | GRID₃              |

| 09 H <sub>L</sub>         | :09 H <sub>∪</sub>                | 0 AH <sub>L</sub> | 0 AH <sub>U</sub>  | 0 BH <sub>L</sub> | GRID₄              |

| 0 CH <sub>L</sub>         | 0 CH <sub>υ</sub>                 | 0 DH <sub>L</sub> | 0 DH <sub>υ</sub>  |                   | GRID₅              |

| $0 \text{ FH}_{\text{L}}$ | 0 FH <sub>∪</sub>                 | 10 H <sub>L</sub> | 10 H <sub>υ</sub>  | 11 H <sub>L</sub> | GRID <sub>6</sub>  |

| 12 H <sub>L</sub>         | 12 H <sub>∪</sub>                 | 13 H <sub>L</sub> | 13 H <sub>υ</sub>  | 14 H <sub>L</sub> | GRID <sub>7</sub>  |

| 15 H <sub>L</sub>         | 15 H <sub>∪</sub>                 | 16 H <sub>L</sub> | 16 H <sub>υ</sub>  | 17 H <sub>L</sub> | GRID <sub>8</sub>  |

| 18 H <sub>L</sub>         | 18 H <sub>∪</sub>                 | 19 H <sub>L</sub> | :19 H <sub>ປ</sub> | 1 AH <sub>L</sub> |                    |

| 1 BH <sub>L</sub>         | 1 BH <sub>∪</sub>                 | 1 CH <sub>L</sub> | 1 CH <sub>∪</sub>  | 1 DH <sub>L</sub> | GRID <sub>10</sub> |

| 1 EH <sub>L</sub>         | ¦1 EH <sub>∪</sub>                | 1 FH <sub>L</sub> | :1 FH <sub>∪</sub> | 20 H <sub>L</sub> | GRID <sub>11</sub> |

| 21 H <sub>L</sub>         | 21 H <sub>∪</sub>                 | 22 H <sub>L</sub> | <u>22 Η</u> υ      | 23 H <sub>L</sub> | GRID <sub>12</sub> |

| 24 H <sub>L</sub>         | 24 H <sub>∪</sub>                 | 25 H <sub>L</sub> | 25 H <sub>υ</sub>  | 26 H <sub>L</sub> | GRID <sub>13</sub> |

| $27 H_L$                  | 27 H <sub>∪</sub>                 | 28 H <sub>L</sub> | 28 H <sub>∪</sub>  | 29 H <sub>L</sub> | GRID <sub>14</sub> |

| $2 AH_L$                  | ¦2 AH <sub>∪</sub>                | $2 BH_L$          | 2 BH <sub>U</sub>  |                   | GRID <sub>15</sub> |

| $2 DH_L$                  | ¦2 DH <sub>∪</sub>                | 2 EH <sub>L</sub> | 2 EH <sub>U</sub>  | 2 FH <sub>L</sub> | GRID <sub>16</sub> |

| b <u>0</u>                | b3 b4 b7                          | •                 |                    |                   |                    |

| $XX H_L$                  | $XXH_{U}$                         |                   |                    |                   |                    |

## 1/8- to 1/16 Duty VFD Controller/Driver

Lower 4 bits Higher 4 bits

Only the lower 4 bits of the addresses assigned to  $Seg_{17}$  through  $Seg_{20}$  are valid, and the higher 4 bits are ignored.

#### 3.0 LED Port

Data is written to the LED port by a write command, starting from the least significant bit of the port. When a bit of this port is 0, the corresponding LED lights; when the bit is 1, the LED goes off . The data of bits 6 through 8 is ignored.

On power application, all the LEDs remain dark.

### 4.0 Key Matrix and Key-Input data Storage RAM

The key matrix is of 12x4 configuration, as shown below.

The data of each key is stored as illustrated below, and is read by a read command, starting from the least significant bit. When the most significant bit of data ( $Seg_{12} b_7$ ) has been read, the least significant bit of the next data ( $Seg_1 b_0$ ) is read.

|   | KEY1KEY4   | KEY1KEY4   |   |                  |

|---|------------|------------|---|------------------|

| - | NETTNET4   | NETTNET4   |   |                  |

|   | Seg1/KS1   | Seg2/KS2   | 1 |                  |

| Ī | Seg3/KS3   | Seg4/KS4   |   |                  |

|   | Seg5/KS5   | Seg6/KS6   |   |                  |

|   | Seg7/KS7   | Seg8/KS8   |   |                  |

| ſ | Seg9/KS9   | Seg10/KS10 |   | Reading sequence |

|   | Seg11/KS11 | Seg12/KS12 | ₩ |                  |

|   | b0b3       | b4b7       |   |                  |

### 5.0 SW Data

The SW data is read by a read command, starting from the least significant bit. Bits 5 through 8 of the SW data are 0.

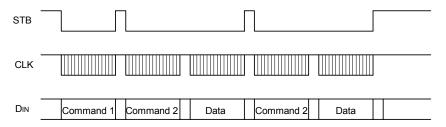

## **■** Timing Diagram

### (1) Serial Communication Format

Reception (command/write data)

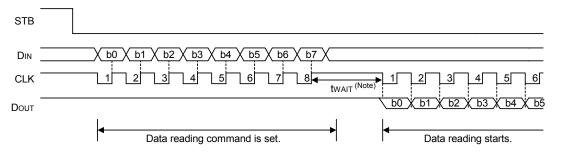

### Transmission (read data)

Because the  $D_{OUT}$  pin is an N-ch, open-drain output pin, be sure to connect an external pull-up resistor to this pin (1k $\Omega$  to 10 k $\Omega$ ).

Note: When data is read, a wait time  $t_{WAIT}$  of 1  $\mu$ s is necessary since the rising of the eighth clock that has set the command, until the falling of the first clock that has read the data.

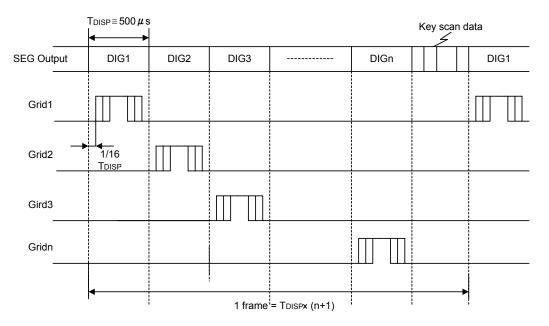

### (2) Key Scanning and Display Timing

One cycle of key scanning consists of two frames, and data of 12x 4 matrices is stored in RAM.

### AC characteristic waveform

### **Applications**

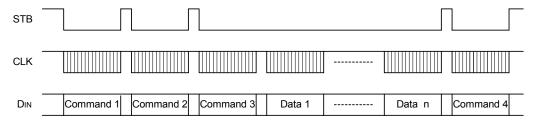

Updating display memory by incrementing address

Command 1: sets display mode

Command 2: sets data(write data to display memory)

Command 3: sets address

Data 1 to n: transfers display data (48 bytes max.)

Command 4: controls display

Updating specific display memory

Command 1: sets data Command 2: sets address Data: display data

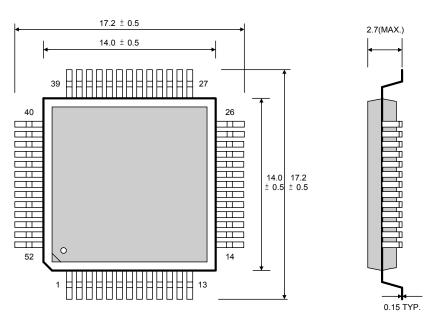

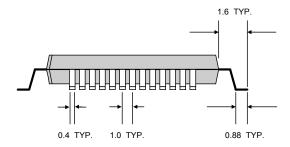

# ■ Package Information

52 pins QFP dimension Unit: mm

# ■ Marking Information