**3V 400MHZ LINEAR AMPLIFIER**

Typical Applications

- 3V TETRA Cellular Handsets

- 3V CDMA Cellular Handsets

• Portable Battery-Powered Equipment

## **Product Description**

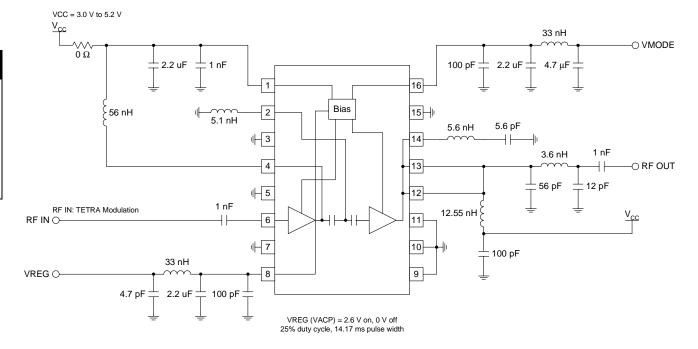

The RF2175 is a high-power, high-efficiency linear amplifier IC targeting 3V handheld systems. The device is manufactured on an advanced Gallium Arsenide Heterojunction Bipolar Transistor (HBT) process, and has been designed for use as the final RF amplifier in TETRA hand-held digital cellular equipment, spread-spectrum systems, and other applications in the 380MHz to 512MHz band. The RF2175 has an analog bias control voltage to maximize efficiency. The device is self-contained with 50 $\Omega$  input, and the output can be easily matched to obtain optimum power, efficiency, and linearity characteristics. The package is a small SSOP-16 plastic with backside ground.

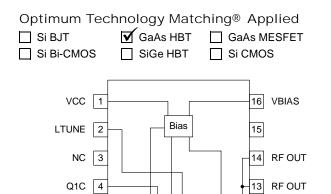

Functional Block Diagram

12

11

10

9

RF OUT

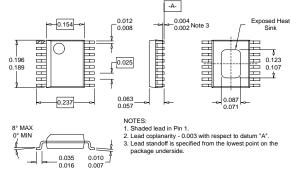

## Package Style: SSOP-16 Slug

## Features

- Single 3V Supply

- 31.8dBm Linear Output Power

- 37.5dB Linear Gain

- 30% Linear Efficiency

- On-Board Power Down Mode

- 380MHz to 512MHz Operation

Ordering Information RF2175 3V 400MHz Linear Amplifier RF2175 PCBA Fully Assembled Evaluation Board RF Micro Devices, Inc. Tel (336) 664 1233 7628 Thorndike Road Fax (336) 664 0454 Greensboro, NC 27409, USA http://www.rfmd.com

GND1 5

RF IN 6

VREG 8

7

## **Absolute Maximum Ratings**

| Parameter                           | Rating          | Unit            |

|-------------------------------------|-----------------|-----------------|

| Supply Voltage (RF Off)             | +8.0            | V <sub>DC</sub> |

| Supply Voltage (RF Applied)         | +4.5            | V <sub>DC</sub> |

| Mode Voltage (V <sub>BIAS</sub> )   | +5.0            | V <sub>DC</sub> |

| Control Voltage (V <sub>REG</sub> ) | +5.0            | V <sub>DC</sub> |

| Input RF Power (Avg.)               | +5              | dBm             |

| Output VSWR - Inband                | 6:1             |                 |

| Output VSWR - Out of Band           | 20:1            |                 |

| Operating Ambient Temperature       | -30 to +100     | °C              |

| Storage Temperature                 | -40 to +120     | °C              |

| Moisture Sensitivity                | JEDEC Level 5 * |                 |

RF Micro Devices believes the furnished information is correct and accurate at the time of this printing. However, RF Micro Devices reserves the right to make changes to its products without notice. RF Micro Devices does not assume responsibility for the use of the described product(s).

| Parameter                                         | Specification |            | Unit        | Condition  |                                                                                                                                                              |  |

|---------------------------------------------------|---------------|------------|-------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Faialletei                                        | Min.          | Тур.       | Max.        |            | Condition                                                                                                                                                    |  |

| Overall                                           |               |            |             |            | T=25°C, V <sub>CC</sub> =3.6V, Freq=410MHz to<br>420MHz unless otherwise specified, 25%<br>duty cycle. P <sub>OUT</sub> =31.8dBm                             |  |

| Usable Frequency Range<br>Typical Frequency Range | 380           | 410 to 420 | 512         | MHz<br>MHz |                                                                                                                                                              |  |

| Linear Gain<br>Harmonic                           | 35.0          | 37.5       | 39.0<br>-30 | dB<br>dBc  |                                                                                                                                                              |  |

| P3dB Output Power                                 | 34            |            | -30         | dBm        |                                                                                                                                                              |  |

| Linear Output Power<br>(TETRA Modulation)         | 31.8          |            |             | dBm        |                                                                                                                                                              |  |

| Total Linear Efficiency                           | 25            | 30         |             | %          |                                                                                                                                                              |  |

| Adjacent Channel Power Rejec-<br>tion             | -35           |            |             | dBc        | ACPR @ 25 kHz, TETRA modulation                                                                                                                              |  |

|                                                   | -45           |            |             | dBc        | ACPR @ 50 kHz, TETRA modulation                                                                                                                              |  |

| Power Supply                                      |               |            |             |            |                                                                                                                                                              |  |

| Power Supply Voltage                              | 3.0           | 3.6        | 4.5         | V          |                                                                                                                                                              |  |

| Idle Current                                      |               | 230        | 300         | mA         | All V <sub>CC</sub> pins, no RF input.                                                                                                                       |  |

| V <sub>CC</sub> Current                           |               |            | 1650        | mA         | All V <sub>CC</sub> pins, P <sub>OUT</sub> =31.8dBm                                                                                                          |  |

| V <sub>REG</sub> Current                          |               |            | 13          | mA         | Pin 8                                                                                                                                                        |  |

| V <sub>BIAS</sub> Current                         |               |            | 3           | mA         | Pin 16                                                                                                                                                       |  |

| Turn On/Off Time                                  |               |            | <150        | μs         | Time for power to rise to 95% of its final value. Measured with $4.7 \mu$ F and $2.2 \mu$ F capacitors on both V <sub>REG</sub> and V <sub>BIAS</sub> lines. |  |

| Total Current (Power Down)                        |               |            | 10          | μA         | V <sub>REG</sub> =Low                                                                                                                                        |  |

| V <sub>REG</sub> "Low" Voltage                    |               | 0          | 0.2         | V          |                                                                                                                                                              |  |

| V <sub>REG</sub> "High" Voltage                   | 2.7           | 2.8        | 2.9         | V          |                                                                                                                                                              |  |

| V <sub>BIAS</sub> Control Voltage Range           |               | 2.8        | 2.9         | V          |                                                                                                                                                              |  |

\* The RF2175 is considered JEDEC Level 5 for moisture sensitivity with a maximum peak reflow temperature of 220°C. To assure reliable performance, this part must be handled in accordance with JEDEC specifications for a Level 5 part.

| <b>RF2175</b> |

|---------------|

|---------------|

| Pin         | Function      | Description                                                                                                                                                                                                                                                                                                                                                                                                                               | Interface Schematic |

|-------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

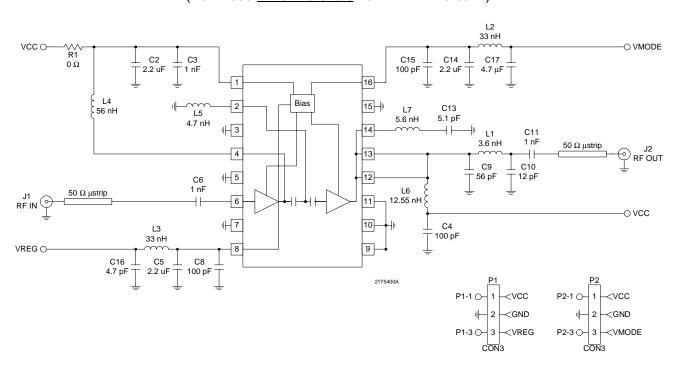

| 1           | VCC           | Power supply for input bias circuitry. A 1nF high frequency bypass capacitor is recommended.                                                                                                                                                                                                                                                                                                                                              |                     |

| 2           | L TUNE        | Interstage Tuning. A shunt inductor to GND is required to optimize the match.                                                                                                                                                                                                                                                                                                                                                             |                     |

| 3           | NC            | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |

| 4           | Q1C           | Power supply for stage 1. $V_{CC}$ should be fed through a 25nH or greater inductor with a decoupling capacitor on the $V_{CC}$ side.                                                                                                                                                                                                                                                                                                     |                     |

| 5           | GND1          | Ground for stage 1. For best performance, keep traces physically short<br>and connect immediately to ground plane. This ground should be iso-<br>lated from the backside ground contact.                                                                                                                                                                                                                                                  |                     |

| 6           | RF IN         | RF input. An external DC blocking capacitor is required if this port is connected to a DC path to ground or a DC voltage.                                                                                                                                                                                                                                                                                                                 |                     |

| 7           | NC            | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |

| 8           | VREG          | Power Down control. When this pin is "low", all circuits are shut off.<br>When this pin is 2.8 V, all circuits are operating normally. $V_{PD}$ requires a<br>regulated 2.8 V for the amplifier to operate properly over all specified<br>temperature and voltage ranges. A dropping resistor from a higher reg-<br>ulated voltage may be used to provide the required 2.8 V. A 100 pF high<br>frequency bypass capacitor is recommended. |                     |

| 9           | NC            | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |

| 10          | NC            | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |

| 11          | NC            | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |

| 12          | RF OUT        | RF output and power supply for the output stage. The bias for the output stage is provided through this pin and pin 13. An external matching network is required to provide the optimum load impedance; see the application schematics for details.                                                                                                                                                                                       |                     |

| 13          | <b>RF OUT</b> | Same as pin 12.                                                                                                                                                                                                                                                                                                                                                                                                                           |                     |

| 14          | RF OUT        | Harmonic trap. This pin connects to the RF output but is used for providing a low impedance to the second harmonic of the operating frequency. An inductor or transmission line resonating with a shunt capacitor at $2f_0$ is connected to this pin.                                                                                                                                                                                     |                     |

| 15          | NC            | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |

| 16          | VBIAS         | The bias pin allows higher efficiency in low power power modes. When operating at full output, VBIAS should be 2.8V.                                                                                                                                                                                                                                                                                                                      |                     |

| Pkg<br>Base | GND           | Ground connection. The backside of the package should be soldered to<br>a top side ground pad, which is connected to the ground plane with<br>multiple vias. The pad should have a short thermal path to the ground<br>plane.                                                                                                                                                                                                             |                     |

2

POWER AMPLIFIERS

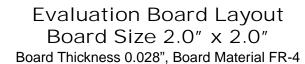

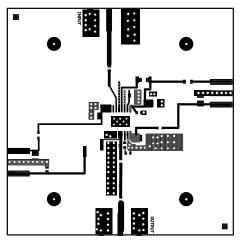

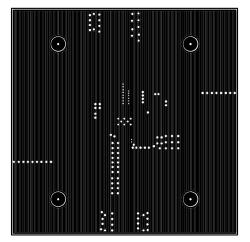

Evaluation Board Schematic (Download <u>Bill of Materials</u> from www.rfmd.com.)