# **Product Preview**

# Low Power DC - 1.8 GHz LNA and Mixer

The MC13141 is intended to be used as a first amplifier and down converter for RF applications. It features wide band operation, low noise, high gain and high linearity while maintaining low current consumption. The circuit consists of a Low Noise Amplifier (LNA), a Local Oscillator amplifier (LO $_{\rm amp}$ ), a mixer, an Intermediate Frequency amplifier (IF $_{\rm amp}$ ) and a dc control section.

Wide RF Bandwidth: DC-1.8 GHz

Wide Mixer Bandwidth: DC-1.8 GHz

Wide IF Bandwidth: DC-100 MHz

Low Power: 7.7 mA @ V<sub>CC</sub> = 2.7–6.5 V

High Mixer Linearity: Pi<sub>1.0 dB</sub> = −2.0 dBm, IP<sub>3in</sub> = 3.0 dBm

Linearity Adjustment Increases IP3in (Not Available in SOIC8)

Up to +20 dBm

Single–Ended 50 Ω Mixer Input

Double Balanced Mixer Operation

Single–Ended 800 Ω Mixer Output

Single–Ended 50 Ω LO Input

#### **ORDERING INFORMATION**

| Device     | Operating<br>Temperature Range | Package |  |

|------------|--------------------------------|---------|--|

| MC13141D1  |                                | SO8     |  |

| MC13141D   | T <sub>A</sub> = -40° to +85°C | SO-14   |  |

| MC13141FTB |                                | TQFP-20 |  |

### LOW POWER DC – 1.8 GHz LNA AND MIXER

SEMICONDUCTOR

TECHNICAL DATA

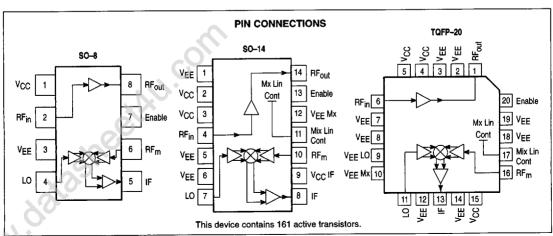

D1 SUFFIX PLASTIC PACKAGE CASE 751 (SO-8)

D SUFFIX

PLASTIC PACKAGE

CASE 751A

(SO-14)

FTB SUFFIX PLASTIC PACKAGE CASE 976 (Thin QFP)

# MAXIMUM RATINGS (TA = 25°C, unless otherwise noted.)

| Rating                         | Symbol | Value     | Unit<br>Vdc |  |

|--------------------------------|--------|-----------|-------------|--|

| Power Supply Voltage           | Vcc    | 7.0 (max) |             |  |

| Operating Supply Voltage Range | Vcc    | 2.7-6.5   | Vdc         |  |

# ELECTRICAL CHARACTERISTICS (SOIC8 Package, V<sub>CC</sub> = 3.0 V, T<sub>A</sub> = 25°C, LO<sub>in</sub> = -10 dBm @ 950 MHz, IF @ 50 MHz.)

| Characteristic                                          | Symbol                | Min                                              | Тур   | Max | Unit |

|---------------------------------------------------------|-----------------------|--------------------------------------------------|-------|-----|------|

| Supply Current (Power Down)                             | lcc                   |                                                  | 100   |     | pA   |

| Supply Current (Power Up)                               | lcc                   | <del>                                     </del> | 7.7   |     | mA   |

| Amplifier Gain (50 $\Omega$ Insertion Gain)             | S21                   | _                                                | 12    | _   | dB   |

| Amplifier Reverse Isolation                             | S12                   |                                                  | -33   |     | dB   |

| Amplifier Input Match                                   | r <sub>in amp</sub>   | <b>†</b> -                                       | -10   |     | dB   |

| Amplifier Output Match                                  | Γ <sub>out amp</sub>  | <del>  -</del>                                   | -15   | _   | dB   |

| Amplifier 1.0 dB Gain Compression                       | Pin_1.0 dB            | _                                                | -15   |     | dBm  |

| Amplifier Input Third Order Intercept                   | 1P3 <sub>in</sub>     | _                                                | - 5.0 | _   | dBm  |

| Amplifier Gain @ N.F. (Application Circuit)             | GNF                   |                                                  | 17    |     | dB   |

| Amplifier Noise Figure (50 $\Omega$ )                   | NF                    | _                                                | 1.8   | _   | dB   |

| Mixer Voltage Conversion Galn (Rp = RL = 800 $\Omega$ ) | VGC                   |                                                  | 15    | _   | dB   |

| Mixer Power Conversion Gain (Rp = RL = 800 $\Omega$ )   | PGC                   |                                                  | 7.0   | _   | dB   |

| Mixer Input Match                                       | Γ <sub>in M</sub>     | _                                                | -20   |     | dB   |

| Mixer SSB Noise Figure                                  | NFSSBM                | _                                                | 16.0  | _   | dB   |

| Mixer 1.0 dB Gain Compression                           | Pin_1.0 dBM           | <del>                                     </del> | -10   |     | dBm  |

| Mixer Input Third Order Intercept                       | IP3 <sub>inM</sub>    |                                                  | -3.0  |     | dBm  |

| Mixer 3 dB RF Bandwidth                                 | M <sub>x-3 dBBW</sub> | _                                                | 1.8   | _   | GHz  |

| LO Drive Level                                          | LOIn                  |                                                  | -10   | _   | dBm  |

| LO Input Match                                          | Γ <sub>in LO</sub>    | _                                                | -20   |     | dB   |

| RF <sub>in</sub> Feedthrough to RF <sub>m</sub>         | PRFin-RFin            | <u> </u>                                         | -13   |     | dB   |

| RF <sub>out</sub> Feedthrough to RF <sub>m</sub>        | PRFout-RFm            |                                                  | -30   |     | dB   |

| LO Feedthrough to IF                                    | P <sub>LO</sub> -IF   |                                                  | -25   |     | dB   |

| LO Feedthrough to RFin                                  | PLO-RFin              | <del>  -</del>                                   | -30   |     | dB   |

| LO Feedthrough to RF <sub>m</sub>                       | PLO-RFm               | <del>  _</del>                                   | -50   |     | dB   |

| Mixer RF Feedthrough to IF                              | PRFm-IF               |                                                  | -50   |     | dB   |

| Mixer RF Feedthrough to RFin                            | PRFm-RFin             | _                                                | -25   | _   | dB   |

#### CIRCUIT DESCRIPTION

#### General

The MC13141 is a low power LNA, double-balanced mixer. This device is designated for use as the front-end section in analog and digital FM systems such as Digital European Cordless Telephone (DECT), PHS, PCS, Cellular, UHF and 800 MHz Special Mobile Radio (SMR), UHF Family Radio Services and 902 to 928 MHz cordless telephones. It features a mixer linearity control to preset or auto preset or auto program the mixer dynamic range, an enable function and buffered IF output for increased overall gain. Further details are covered in the Pin Function Description which shows the equivalent internal circuit and external circuit requirements.

#### **Current Regulation/Enable**

Temperature compensating voltage independent current regulators are controlled by the the enable function in which "high" powers up the IC.

#### Low Noise Amplifier (LNA)

The LNA is internally biased at low supply current (approximately 2.0 mA emitter current) for optimal noise

figure and gain. Input and output matching may be achieved at various frequencies using few external components (see Application Circuit). Matching the LNA for maximum stable gain (MSG) yields noise performance within a few tenths of a dB of the minimum noise figure. Typical performance at 1.0 GHz is 17 dB gain and 1.8 dB noise figure for Vcc at 3.0 to 5.0 Vdc.

#### Mixer

The mixer is a double–balanced four quadrant multiplier biased class AB allowing for programmable linearity control via an external current source. An input third order intercept point of 20 dBm may be achieved. All 3 ports of the mixer are designed to work up to 1.8 GHz. The mixer has a 50  $\Omega$  single–ended RF input and IF output buffer amplifier. The linear gain of the mixer is approximately 7.0 dB with a SSB noise figure of 16 dB.

#### **Local Oscillator**

It requires an external local oscillator source at -10 dBm input level to maximize the mixer gain.

#### PIN FUNCTION DESCRIPTION

| 14 Pin<br>SOIC | 20 Pin<br>TQFP   | Symbol | Equivalent Internal Circuit<br>(20 Pin TQFP) | Functional Description/External<br>Circuit Requirements                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|------------------|--------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4              | 6                | RFin   | RFout V <sub>ref1</sub>                      | RF Input The input is the base of an NPN low noise amplifier. Minimum external matching is required to optimize the input return loss and gain.                                                                                                                                                                                                                                                                         |

| 2, 3           | 4, 5             | Vcc    | 6 NFin 2, 3, 7 2.0 mA                        | VCC – Positive Supply Voltage Two V <sub>CC</sub> pins are provided for the Local Oscillator and LO Buffer Amplifier. The operating supply voltage range is from 2.7 Vdc to 6.5 Vdc. In the PCB layout, the V <sub>CC</sub> trace must be kept as wide as feasible to minimize inductive reactances along the trace. V <sub>CC</sub> should be decoupled to VEE at the IC pin as shown in the component placement view. |

| 1,5            | 2, 3, 7<br>and 8 | VEE    | VEE VCC                                      | VEE - Negative Supply VEE pin is taken to an ample dc ground plane through a low impedance path. The path should be kept as short as possible. A two sided PCB is implemented so that ground returns can be easily made through via holes.                                                                                                                                                                              |

| 14             | 1                | RFout  | VEE _                                        | RF Output The output is from the collector of the LNA. As shown in the 926 MHz application receiver the output is conjugately matched with a shunt L, and series L and C network.                                                                                                                                                                                                                                       |

| 7              | 11               | LO     | V <sub>ref3</sub> 33  11  0  11  33          | Local Oscillator Input 50 Ω single—ended buffered LO input.                                                                                                                                                                                                                                                                                                                                                             |

#### PIN FUNCTION DESCRIPTION (continued)

| 14 Pin<br>SOIC | 20 Pin<br>TQFP   | Symbol          | Equivalent Internal Circuit (20 Pin TQFP) | Functional Description/External Circuit Requirements                                                                                                                                                                                                                                                                                           |

|----------------|------------------|-----------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5, 6           | 9, 10,<br>12, 14 | VEE             | V <sub>ref2</sub> = 2.0 Vbe               | VEE - Negative Supply These pins are VEE supply for the IF and LO. In the application PC board these pins are tied to a common VEE trace with other VEE pins.                                                                                                                                                                                  |

| 8              | 13               | IF              | 9, 10,<br>12, 14                          | IF Output The IF is a 800 $\Omega$ single—ended output which must be externally matched to 50 $\Omega$ for optimal performance.                                                                                                                                                                                                                |

| 10             | 16               | RFm             | V <sub>CC</sub> V <sub>ref4</sub>         | Mixer RF Input The mixer input impedance is broadband 50 $\Omega$ for applications up to 1.8 GHz. It easily interfaces with a RF ceramic filter as shown in the application schematic. The pin dc bias is set at 1.0 Vbe.                                                                                                                      |

| 11             | 17               | Mix Lin<br>Cont | RFm 17 Wix Un Cont                        | Mixer Linearity Control The mixer linearity control circuit accepts approximately 0 to 2.3 mA control current to set the dynamic range of the mixer. An Input Third Order Intercept Point, IIP3 of 20 dBm may be achieved at 2.3 mA of control current (approximately 7.0 mA of additional supply current). The pin dc bias is set at 2.0 Vbe. |

| 12             | 18, 19           | VEE             | 400 μΑ                                    | VEE - Negative Supply These pins are VEE supply for the mixer input.                                                                                                                                                                                                                                                                           |

| 13             | 20               | EN              | 20 40 k<br>EN 2.0 Vbe                     | Enable The device is enabled by pulling up to V <sub>CC</sub> or greater than 2.0 Vbe.                                                                                                                                                                                                                                                         |

#### **APPLICATIONS INFORMATION**

#### **Evaluation PC Board**

The evaluation PCB is very versatile and is intended to be used across the entire useful frequency range of this device. The PC board accommodates all SMT components on the circuit side (see Circuit Side Component Placement View). This evaluation board will be discussed and referenced in this section.

#### **Component Selection**

The evaluation PC board is designed to accommodate specific components, while also being versatile enough to use components from various manufacturers and coil types. The circuit side placement view is illustrated for the components specified in the application circuit. The application circuit schematic specifies particular components that were used to achieve the results given and specified in the tables but alternate components of the same Q and value should give similar results.

6367253 0102153 057

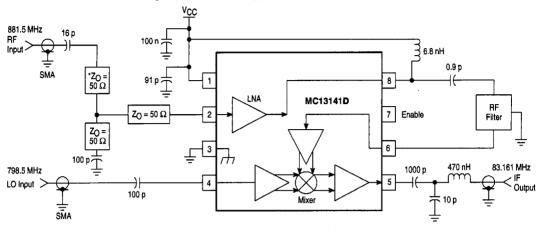

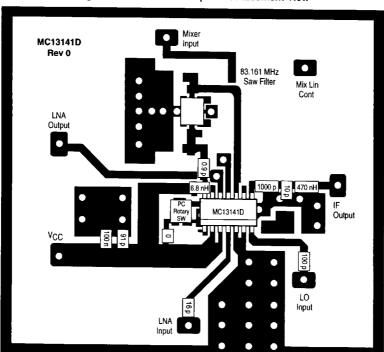

Figure 1. MC13141D1 Application Circuit (881.5 MHZ)

NOTE: \*50  $\Omega$  Microstrip Transmission Line; length shown in Figure 2.

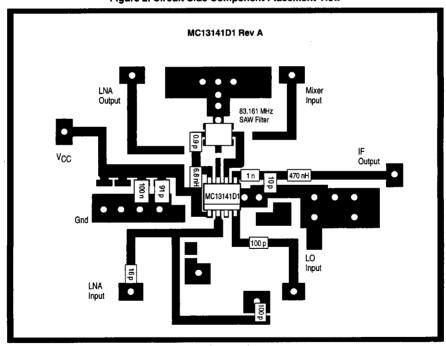

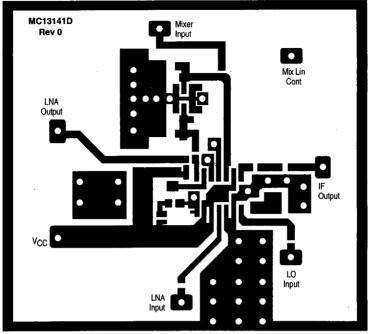

Figure 2. Circuit Side Component Placement View

NOTES: 881.5 MHz SAW filter in the ceramic surface mount package is available from several sources: Siemens part # B39881–B4608–Z010 is an example.

Other suppliers include Toko and Murata.

The PCB accommodates ceramic dielectric filters for applications in Cellular, DECT, PHS and ISM bands at 902–928 and 2.4–2.5 GHz. Toko makes a full line-up covering the above bands.

The PCB may be used without an image filter; ac couple the LNA to the mixer. Traces are provided on the PCB to evaluate the LNA and mixer separately. The component placement view shows external circuit components used in the 881.5 MHz application circuit. It is necessary to cut a section in the trace before placing the 0.9 pF capacitor. Capacitors should be 0805 size; the 6.8 nH inductor is a Toko type LL2012.

■ 6367253 0102154 T93 **■**

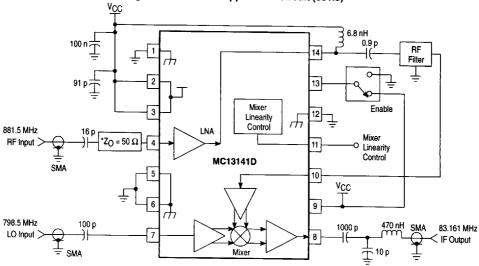

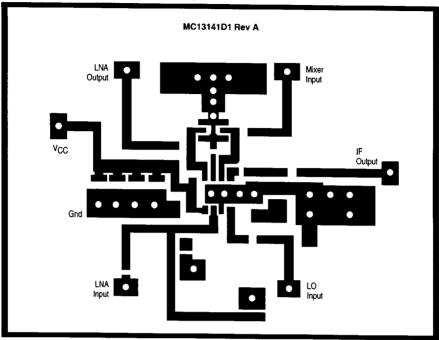

Figure 3. MC13141D Application Circuit (881.5)

NOTE: \*50  $\Omega$  Microstrip Transmission Line; length shown in Figure 4.

Figure 4. Circuit Side Component Placement View

NOTES: 881.5 MHz SAW filter in the ceramic surface mount package is available from several sources: Siemens part # B39881-B4608-Z010 is an example. Other suppliers include Toko and Murata.

The PCB accommodates ceramic dielectric filters for applications in Cellular, DECT, PHS and ISM bands at 902–928 and 2.4–2.5 GHz. Toko makes a full line-up covering the above bands.

The PCB may be used without an image filter; ac couple the LNA to the mixer. Traces are provided on the PCB to evaluate the LNA and mixer separately. The component placement view shows external circuit components used in the 881.5 MHz application circuit. It is necessary to cut a section in the trace before placing the 0.9 pF capacitor. Capacitors should be 0805 size; the 6.8 nH inductor is a Toko type LL2012.

#### Input Matching/Components

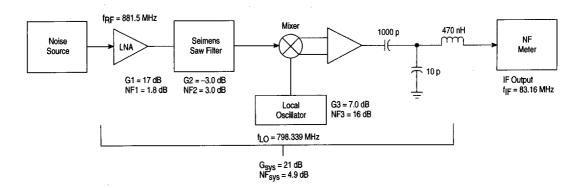

It is desirable to use a RF ceramic or SAW filter before the mixer to provide image frequency rejection. The filter is selected based on cost, size and performance tradeoffs. Typical RF filters have 3.0 to 5.0 dB insertion loss. The PC board layout accommodates both ceramic and SAW RF filters which are offered by various suppliers such as Siemens, Toko and Murata. Interface matching between the LNA, RF filter and the mixer will be required. The interface matching networks shown in the application circuit are designed for 50  $\Omega$  interfaces.

The LNA is conjugately matched to 50  $\Omega$  input and output at 3.0 Vdc V<sub>CC</sub>. 17 dB gain and 1.8 dB noise figure is typical at 881.5 MHz. The mixer measures 7.0 dB gain and 16 dB noise figure as shown in the application circuit. Typical insertion loss of the Siemens SAW filter is 3.0 dB.

#### **System Noise Considerations**

The block diagram shows the cascaded noise stages of the MC13141 in the front-end receiver subsystem; it represents the application circuit. In the cascaded noise analysis the system noise equation is:

$$F_{system} = F1 + [(F2-1)/G1] + [(F3-1)] / [(G1)(G2)]$$

#### where:

F1 = the Noise Factor of the MC13142 LNA

G1 = the Gain of the LNA

F2 = the Noise factor of the RF Ceramic Filter

G2 = the Gain of the Ceramic Filter

F3 = the Noise factor of the Mixer

Note: the above terms are defined as linear relationships and are related to the log form for gain and noise figure by the following:

$F = Log^{-1}$  [(NF in dB)/10] and similarly

$G = Log^{-1} [(Gain in dB)/10]$

Calculating in terms of gain and noise factor yields the following:

F1 = 1.51 ; G1 = 50.11

F2 = 1.99; G2 = 0.5

F3 = 39.8

Thus, substituting in the equation for subsystem noise factor:

F<sub>subsystem</sub> = 3.08 ; NF<sub>subsystem</sub> = 4.9 dB Overall Subsystem Gain = 21 dB

Figure 5. Front-End Subsystem Block Diagram for Noise Analysis

Figure 6. Circuit Side View

NOTES: Critical dimensions are 50 mil centers lead to lead in SO–8 footprint.

Also line widths to labeled ports excluding V<sub>CC</sub> are 50 mil (0.050 inch).

FR4 PCB, 1/32 inch.

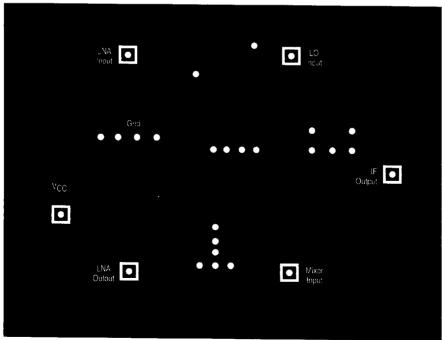

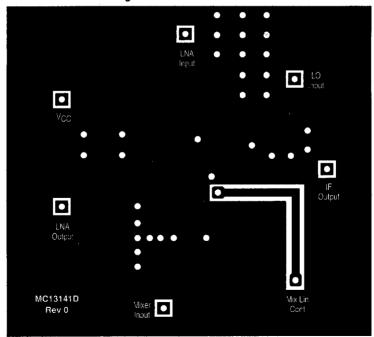

Figure 7. MC13141D1 Rev A - Ground Side View

NOTE: FR4 PCB, 1/32 inch.

■ 6367253 O1O2157 7T2 **■** -

Figure 8. Circuit Side View

NOTES: Critical dimensions are 50 mil centers lead to lead in SO–14 footprint. Also line widths to labeled ports excluding  $V_{CC}$  are 50 mil (0.050 inch). FR4 PCB, 1/32 inch.

Figure 9. Ground Side View

NOTE: FR4 PCB, 1/32 inch.