# NEC Electronics Inc.

#### μPD72020 **CMOS Graphics Display Controller**

T-52-33-47

#### Description

The µPD72020 is an enhanced graphics display controller resulting from the implementation of CMOS technology on the  $\mu$ PD7220A.

In addition to the functions of the  $\mu$ PD7220A, the μPD72020 incorporates address space expansion, video RAM control, and write mask functions. It is suitable for a wide range of applications from simple display terminals to high-resolution graphics display devices.

This data sheet covers only functions additional to those of the  $\mu$ PD7220A. For further details of the  $\mu$ PD72020, refer to the µPD72020 User's Manual.

#### **Features**

- Enhanced functions compared with the μPD7220A

- Video memory space: 2M bytes maximum (1M 16-bit words)

- Control of dual-port RAM (video RAM)

- Write-masking of any desired bit

- Enhanced external synchronization function

- CMOS technology

- □ μPD7220A-compatible functions

- High-speed graphics drawing: 500 ns/dot (operating at 8 MHz)

- Selection of drawing timing: flashless/flash mode

- Drawing of straight lines, arcs, quadrilaterals, graphic characters

- Any kind of line specifiable

- Four different dot-correction modes

- Enlarged drawing/enlarged display

- Panning and scrolling

- Automatic cursor shifting

- Attributes assignable character by character

- Interlaced/noninterlaced scanning

- DRAM refreshing

- Master/slave operation

- Video memory control independent of main

- 16 x 9-bit on-chip input/output FIFO

- DMA control

- -- Single +5-volt power supply

#### **Applications**

Some application functions implemented by use of this product in conjunction with other products may infringe on U.S. Patent No. 4,197,590 and Re. 31,200 etc. held by CADTRAK Corporation of the United States, and the corresponding patents in various countries. Problems may arise from such patents even when a different graphics display controller or discrete circuitry is used, and thus resolution on the basis of this product alone is not possible. Therefore, the user is requested to undertake as his or her own responsibility an investigation of measures to cope with this situation before designing an application system.

#### Ordering Information

| Part No.         | Package                 |

|------------------|-------------------------|

| μPD72020C-8      | 40-pin plastic DIP      |

| μPD72020GC-8-3B6 | 52-pin plastic miniflat |

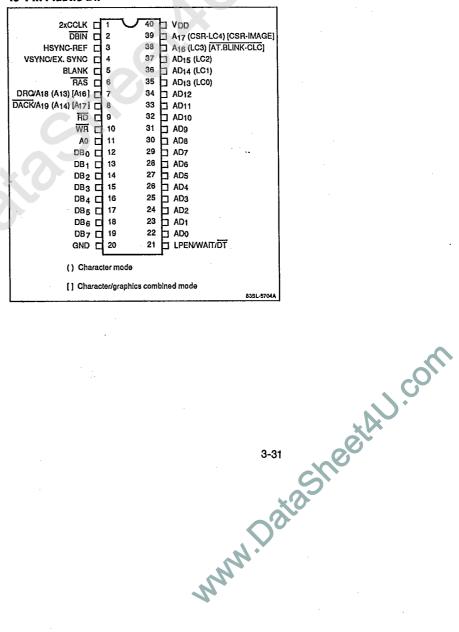

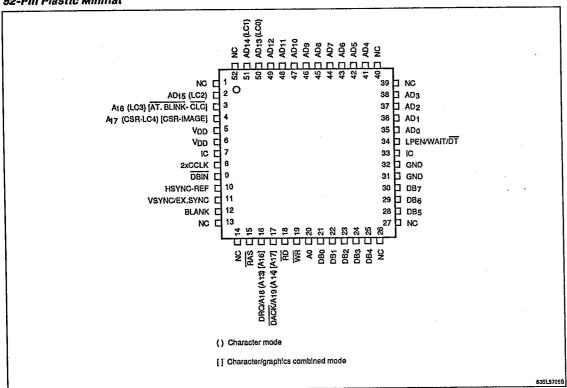

#### Pin Configurations

#### 40-Pin Plastic DIP

T-52-33-47

#### 52-Pin Plastic Miniflat

#### Pin Identification

| Symbol                                                                   | Function                                          |

|--------------------------------------------------------------------------|---------------------------------------------------|

| A0                                                                       | Address select input for microprocessor interface |

| AD <sub>0</sub> -AD <sub>12</sub>                                        | Address-data lines to display memory              |

| AD <sub>13</sub> /LC0, AD <sub>14</sub> /LC1,<br>AD <sub>15</sub> /LC2   | See text and table 3.                             |

| A <sub>16</sub> /LC3/AT.BLINK-CLC,<br>A <sub>17</sub> /CSR-LC4/CSR-IMAGE | See text and table 3.                             |

| BLANK                                                                    | CRT blanking output                               |

| DACK/A <sub>19</sub> /A <sub>14</sub> /A <sub>17</sub>                   | See text and table 1.                             |

| DB <sub>0</sub> -DB <sub>7</sub>                                         | Bidirectional data bus to host microprocessor     |

| DBIN                                                                     | Display memory read input flag                    |

| DRQ/A <sub>18</sub> /A <sub>13</sub> /A <sub>16</sub>                    | See text and table 1.                             |

| HSYNC-REF                                                                | Horizontal video sync output                      |

| Symbol          | Function                                              |

|-----------------|-------------------------------------------------------|

| LPEN/WAIT/DT    | See text and table 2.                                 |

| RAS             | Row address strobe                                    |

| RD              | Read strobe input for microprocessor<br>interface     |

| VSYNC/EX.SYNC   | Vertical video sync output or external<br>VSYNC input |

| WR .            | Write strobe input for microprocessor<br>interface    |

| 2xCCLK          | Clock input                                           |

| GND             | Ground                                                |

| V <sub>DD</sub> | +5-volt power supply                                  |

| IC              | Internal connection                                   |

| NG              | No connection                                         |

T-52-33-47

#### **PIN FUNCTIONS**

Pins on the  $\mu$ PD7220A and the  $\mu$ PD72020 have similar functions. Differences are described below.

#### Pins DRQ and DACK

The functions of these pins depend on the setting of the PN bit by the WMASK command, which validates the address extension functions See table 1.

A<sub>13</sub>, A<sub>14</sub>, A<sub>16</sub>-A<sub>19</sub>. When the address extension function is selected by setting PN of the WMASK command, the upper 2 bits (of the extended address) are output in the video memory in each display/draw mode.

After the address extension function has been selected, the DMA-related functions cannot be used. Use the CHR and G bits of the SYNC command to set the display/ draw mode (as with the  $\mu$ PD7220A).

DRQ (DMA Request). When the DMAR or DMAW command is executed, the DMA request signal is output. This signal is input to the DRQ pin of the DMA controller.

After the DMA-related functions have been selected, the address extension functions cannot be used.

DACK (DMA Acknowledge). A signal indicating DMA transfer is input. This signal is output from the DACK pin of the DMA controller.

#### Pin LPEN/WAIT/DT

The functions of this pin depend on the setting of the DTE bit by the WMASK command, which validates the DT signal generation function. See table 2.

$\overline{\text{DT}}$  (Data Transfer). When the  $\overline{\text{DT}}$  signal generation function is selected by setting DTE of the WMASK command, the  $\overline{\text{DT}}$  signal is output to indicate the display address supply timings for the  $\mu\text{PD41264-type}$  video RAMs (VRAMs).

After the  $\overline{\text{DT}}$  signal generation function has been selected, the LPEN and WAIT functions cannot be used.

LPEN (Light Pen Strobe). When the light pen detects a light input, the H-level signal is input.

After the LPEN function has been selected, the  $\overline{\rm DT}$  signal generation function cannot be used.

WAIT (Drawing Wait). When a signal that remains at the H-level for a period of at least four clocks is input in the drawing stop mode, the  $\mu\text{PD72020}$  will stop drawing temporarily if it is executing drawing and output a display address.

After the WAIT function has been selected, the  $\overline{\text{DT}}$  signal generation function cannot be used.

#### Pins AD<sub>13</sub>-AD<sub>15</sub>, A<sub>16</sub>, and A<sub>17</sub>

The functions of some other pins depend on the operating mode: character, graphics, or character/graphics combined. See table 3.

Table 1. Pin Functions Available Through Address Extension

| Pin Symbol                                             | PN Bit (WMASK Command) | Action                     | Mode      | 1/0    | Pin Function    |

|--------------------------------------------------------|------------------------|----------------------------|-----------|--------|-----------------|

| DRQ/A <sub>18</sub> /A <sub>13</sub> /A <sub>16</sub>  | 0                      | Action similar to μPD7220A | ·         | Output | DRQ             |

|                                                        | 1                      | Address extension          | Graphics  | Output | A <sub>18</sub> |

|                                                        |                        |                            | Character | Output | A <sub>13</sub> |

|                                                        |                        |                            | Combined  | Output | A <sub>16</sub> |

| DACK/A <sub>19</sub> /A <sub>14</sub> /A <sub>17</sub> | 0                      | Action similar to μPD7220A |           | Input  | DACK            |

|                                                        | 1                      | Address extension          | Graphics  | Output | A <sub>19</sub> |

|                                                        |                        |                            | Character | Output | A <sub>14</sub> |

|                                                        |                        |                            | Combined  | Output | A <sub>17</sub> |

#### Table 2. Pin Functions Available Through DT Signal Generation

| Pin Symbol    | DTE Bit (WMASK Command) | Action                     | 1/0    | Pin Function |

|---------------|-------------------------|----------------------------|--------|--------------|

| LPEN/WAIT/ DT | 0                       | Action similar to μPD7220A | Input  | LPEN/WAIT    |

|               | 1                       | DT signal generation       | Output | ĎΪ           |

T-52-33-47

Table 3. Multifunction Pins AD<sub>13</sub>-AD<sub>15</sub>, A<sub>16</sub>, and A<sub>17</sub>

| Pin Symbol                         | Mode               | 1/0    | Function                                   |  |  |  |

|------------------------------------|--------------------|--------|--------------------------------------------|--|--|--|

| AD <sub>13</sub> -AD <sub>15</sub> | Graphics; combined | I/Q    | Address-data lines 13-15 to display memory |  |  |  |

| LCO-LC2 Character                  |                    | Output | Line counter bits 0-2                      |  |  |  |

| A <sub>16</sub>                    | Graphics           | Output | Address bit 16                             |  |  |  |

| LC3                                | Character          | Output | Line counter bit 3                         |  |  |  |

| AT.BLINK-CLC                       | Combined           | Output | Attribute blink and clear line counter     |  |  |  |

| A <sub>17</sub>                    | Graphics           | Output | Address bit 17                             |  |  |  |

| CSR-LC4                            | Character          | Output | Cursor and line counter bit 4              |  |  |  |

| CSR-IMAGE                          | Combined           | Output | Cursor and bit-map area flag               |  |  |  |

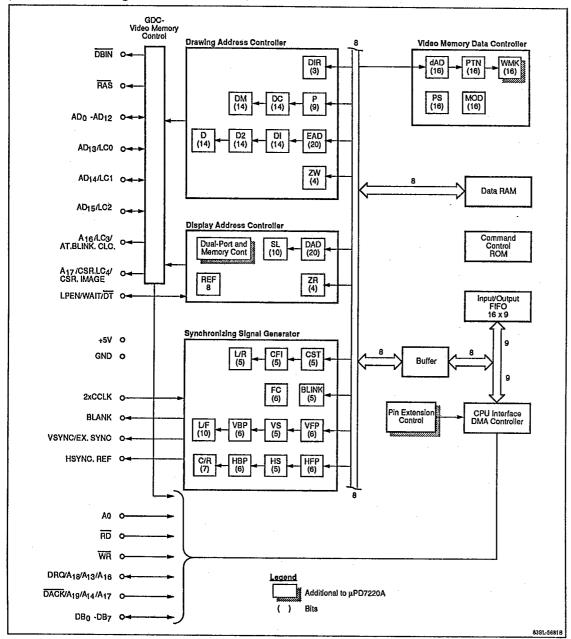

#### ADDED BLOCK FUNCTIONS

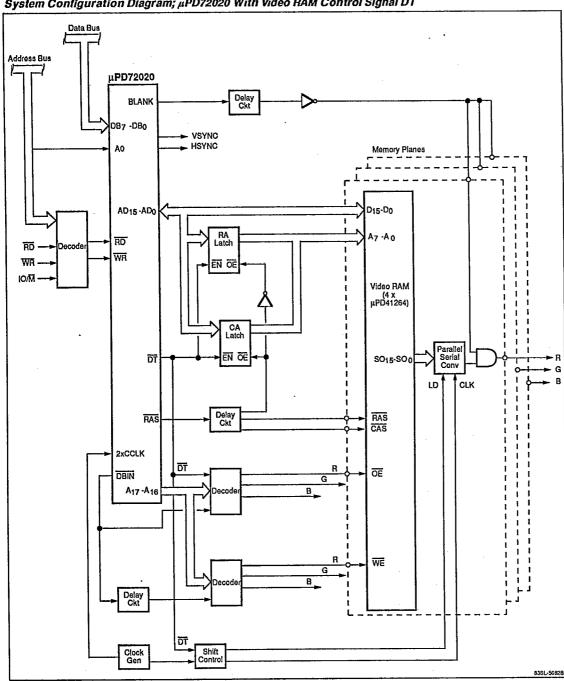

Refer to the  $\mu PD72020$  Block Diagram and the System Configuration Diagram.

#### Video RAM Control

Additional blocks generate the  $\overline{\text{DT}}$  signal, which indicates the display-address supply timings for the video RAMs. Data within the RAMs can be transferred to the serial register.

#### **Pin Extension Control**

The video memory address is extended 2 bits (with the address space extended fourfold) in each of the character, character/graphics combined, and graphics modes.

These bits are used for both  $\overline{DACK}$  pin and DRQ pin in each mode:  $A_{14}$  and  $A_{16}$ ;  $A_{17}$  and  $A_{16}$ ;  $A_{19}$  and  $A_{18}$ .

#### **WMASK Register**

This 16-bit register is used to mask the data for multicolor synchronous drawing with one word in 8/4/2/1-bit configuration.

#### **IMPROVED FUNCTIONS**

The  $\mu$ PD72020 functions have been improved while maintaining compatibility with the  $\mu$ PD7220A in both hardware and software. Table 4 compares functions of the  $\mu$ PD72020 and the  $\mu$ PD7220A.

The µPD72020 is initialized by reset input so that it can function similarly to the µPD7220A.

T-52-33-47

#### μPD72020 Block Diagram

T-52-33-47

System Configuration Diagram; µPD72020 With Video RAM Control Signal DT

T-52-33-47

#### Table 4. Comparison of µPD72020 and µPD7220A Functions

μPD72020

μPD7220A

WMASK Command

WMASK command is used to validate the new functions of the μPD72020.

WMASK command is not used.

DB2 DB7 DB6 DB5 DB4 DB3 DB1 DB0 CMD 0 0 0 0 P1 WMKL P2 **WMKH** P3 PN TM DTE CY1 CY0 0 0 0

Sets the WMASK register value. WMK

PN Sets the address extension function.

TM Changes the initializing timing of the horizontal synchronization counter in the slave mode for external synchronization, and sets the initializing function of the field

counter

DTE Sets the function of generating the DT signal.

Set the DT signal output mode and the BLANK signal CY mask.

LPEN Command Light pen address (LAD) extension function is not available.

Light pen address (LAD) is extended 2 bits by setting PN of the WMASK command.

PN 0 Same as µPD7220A

> 1 EAD is extended 2 bits.

|     | DB7 | DB6 | DB5 | DB4 | DB3 | DB2      | DB1 | DBO |

|-----|-----|-----|-----|-----|-----|----------|-----|-----|

| CMD | 1   | 1   | 0   | 0   | 0   | 0        | 0   | 0   |

| D1  |     |     |     | LA  | DL  | <b>.</b> |     | ·   |

| D2  |     |     |     | LA  | DΜ  |          |     |     |

| D3  | Х   | Х   | Х   | х   | ľ   | LA       | DH  |     |

|     | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| CMD | 1   | 1   | 0   | 0   | 0   | 0   | 0   | 0   |

| D1  |     |     |     | LA  | DL  |     |     |     |

| D2  |     |     |     | LA  | DH  |     |     |     |

| D3  | Х   | Х   | Х   | х   | Х   | Х   | LA  | DH  |

#### CSRW Command

Draw execution address (EAD) Is extended 2 bits by setting PN of the WMASK command.

Draw execution address (EAD) extension function is not available.

PN Same as µPD7220A

EAD is extended 2 bits.

#### **Character Mode**

|     | DB7 | DB6    | DB5 | DB4 | DB3 | DB2 | DB1 | DBO |  |  |  |

|-----|-----|--------|-----|-----|-----|-----|-----|-----|--|--|--|

| CMD | 0   | 1      | 0   | 0   | 1   | 0   | 0   | 1   |  |  |  |

| P1  |     | EADL   |     |     |     |     |     |     |  |  |  |

| P2  | 0   | 0 EADH |     |     |     |     |     |     |  |  |  |

|     | DB7 | DB6 | DB5 | DB4 | DB3 | DB2  | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|------|-----|-----|

| CMD | 0   | 1   | 0   | 0   | 1   | 0    | 0   | 1   |

| P1  |     |     |     | ĒΑ  | DL  |      |     |     |

| P2  | 0   | 0   | 0   |     |     | EADH |     |     |

#### Table 4. Comparison of μPD72020 and μPD7220A Functions (cont)

μPD72020

μPD7220A

CSRW Command (cont)

#### Character/Graphics Combined Mode (Character Display)

|     | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| CMD | 0   | 1   | 0   | 0   | 1   | 0   | 0   | 1   |

| P1  |     |     |     | EA  | DL. |     |     |     |

| P2  |     |     |     | EA  | DM  |     |     |     |

| P3  | 0   | 0   | 0   | 0   | 0   | 0   | EA  | DH  |

|     | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DBO |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| CMD | 0   | 1   | 0   | 0   | 1   | 0   | 0   | 1   |

| P1  |     |     |     | EA  | DL  |     |     |     |

| P2  |     |     |     | EA  | DH  |     |     |     |

### Character/Graphics Combined Mode (Graphics Display/Drawing)

|     | DB7 | DB6 | DB5      | DB4 | DB3 | DB2 | DB1 | DBO |

|-----|-----|-----|----------|-----|-----|-----|-----|-----|

| CMD | 0   | 1   | 0        | 0   | 1   | 0   | 0   | 1   |

| P1  |     |     | <u> </u> | EA  | DL  |     |     |     |

| P2  |     |     |          | EA  | ,DM |     |     |     |

| P3  |     | d   | AD       |     | 0   | 0   | EA  | DH  |

| P4  | WG  | 0   | 0        | 0   | 0   | 0   | 0   | 0   |

|     | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DBO |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| CMD | 0   | 1   | 0   | 0   | 1   | 0   | 0   | 1   |

| P1  | ^   |     |     | EA  | DL  |     |     |     |

| P2  |     |     |     | EA  | DН  |     |     |     |

| P3  |     | d/  | AD. |     | WG  | 0   | 0   | 0   |

#### **Graphics Mode**

|     | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| CMD | 0   | 1   | 0   | 0   | 1   | 0   | 0   | 1   |

| P1  |     |     |     | EA  | DL  |     |     |     |

| P2  |     |     |     | EA  | MD  |     |     |     |

| РЗ  |     | d   | AD  |     |     | EA  | DH  |     |

| P4  | WG  | 0   | 0   | 0   | 0   | 0   | 0   | Q   |

|     | DB7 | DB6  | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |  |  |

|-----|-----|------|-----|-----|-----|-----|-----|-----|--|--|

| CMD | 0   | 1    | 0   | 0   | 1   | 0   | 0   | 1   |  |  |

| P1  |     | EADL |     |     |     |     |     |     |  |  |

| P2  |     | EADM |     |     |     |     |     |     |  |  |

| P3  |     | d    | AD  |     | WG  | 0   | EA  | DH  |  |  |

#### **CSRR** Command

Draw execution address (EAD) is extended 2 bits by setting PN of the WMASK command.

Draw execution address (EAD) extension function is not available.

- Same as µPD7220A 0

- EAD is extended 2 bits.

|     | DB7 | DB6      | DB5       | DB4 | DB3 | DB2 | DB1 | DBO |

|-----|-----|----------|-----------|-----|-----|-----|-----|-----|

| CMD | 1   | 1        | 1         | 0   | 0   | 0   | 0   | 0   |

| D1  |     | <u> </u> |           | EA  | DL  |     |     |     |

| D2  |     | EADM     |           |     |     |     |     |     |

| D3  | х   | Х        | х         | Х   |     | EA  | DH  |     |

| D4  |     |          | <b>L.</b> | dA  | DL  |     |     |     |

| D5  |     |          |           | ďΑ  | DH  |     |     |     |

|     | DB7 | DB6              | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |  |  |

|-----|-----|------------------|-----|-----|-----|-----|-----|-----|--|--|

| CMD | 1   | 1                | 1   | 0   | 0   | 0   | 0   | 0   |  |  |

| D1  |     | EADL             |     |     |     |     |     |     |  |  |

| D2  |     | EADM             |     |     |     |     |     |     |  |  |

| D3  | х   | X X X X X X EADH |     |     |     |     |     |     |  |  |

| D4  |     | dADL             |     |     |     |     |     |     |  |  |

| D5  |     | dADH             |     |     |     |     |     |     |  |  |

T-52-33-47

#### Table 4. Comparison of μPD72020 and μPD7220A Functions (cont)

μPD72020

μPD7220A

#### SCROLL Command

Display start address (SAD) is extended 2 bits by setting PN of the WMASK command.

Display start address (SAD) extension function is not available.

PN

0 Same as μPD7220A

1 SAD is extended 2 bits.

#### Character Mode Built-In RAM Map

|       | MSB |    |            |          |    |   | LSB |  |  |  |

|-------|-----|----|------------|----------|----|---|-----|--|--|--|

| RA    |     |    | Conten     | ts or RA | M  |   | •   |  |  |  |

| 0     |     |    | SA         | D1L      |    | - |     |  |  |  |

| 1     | 0   |    |            | SAD1F    | 1  |   | -   |  |  |  |

| 2     |     | SI | -1L        | 0        | 0  | 0 | 0   |  |  |  |

| 3     | *   | 0  | SL1H       |          |    |   |     |  |  |  |

| 4     |     |    | SAD2L      |          |    |   |     |  |  |  |

| 5     | 0   |    | SAD2H      |          |    |   |     |  |  |  |

| 6     |     | ŞI | SL2L 0 0 0 |          |    |   |     |  |  |  |

| 7     | *   | 0  | 0 SL2H     |          |    |   |     |  |  |  |

| 8     |     |    | SA         | D3L      |    |   |     |  |  |  |

| ø     | 0   |    |            | SAD3H    | 1  |   |     |  |  |  |

| A     |     | SI | -3L        | 0        | 0  | 0 | 0   |  |  |  |

| В     | *   | 0  |            | SL.      | зн |   |     |  |  |  |

| С     |     |    | SA         | D4L      |    |   |     |  |  |  |

| D     | 0   |    |            | SAD4H    |    |   |     |  |  |  |

| E     |     | ŞL | .4L        | 0        | 0  | 0 | 0   |  |  |  |

| F     | *   | o  |            | SL.      | 4H |   |     |  |  |  |

| * DAL | )+2 |    |            |          |    |   |     |  |  |  |

|     | MSB |        |            |        | l "     |       |          | LSE |

|-----|-----|--------|------------|--------|---------|-------|----------|-----|

| RA  |     |        | С          | ontent | s or R/ | M     | ·        |     |

| 0   |     |        |            | SA     | D1L     |       |          |     |

| 1   | 0   | 0      | 0          |        |         | SAD1F | 1        | _   |

| 2   |     | SL     | .1L        |        | 0       | 0     | 0        | 0   |

| 3   | *   | 0      |            |        | SL      | 1H    | <u> </u> |     |

| 4   |     |        |            | SAI    | D2L     |       |          |     |

| 5   | 0   | 0      | 0          |        |         | SAD2H | 1        |     |

| 6   |     | SL     | SL2L 0 0 0 |        |         |       |          |     |

| 7   | *   | 0 SL2H |            |        |         |       |          |     |

| 8   |     |        |            | SAI    | D3L     |       |          |     |

| 9   | 0   | 0      | 0          |        |         | SAD3H | l        |     |

| Α   |     | SL     | .3L        |        | 0       | 0     | 0        | 0   |

| В   | *   | 0      |            |        | SL      | зн    |          |     |

| С   |     |        |            | SAI    | D4L     |       |          |     |

| D   | 0   | 0      | 0          |        |         | SAD4H |          |     |

| E   |     | SL     | 4L         |        | 0       | 0     | 0        | 0   |

| F   | *   | 0 SL4H |            |        |         |       |          |     |

| DAD | )+2 |        |            |        |         |       |          |     |

#### Table 4. Comparison of µPD72020 and µPD7220A Functions (cont)

μPD72020 μPD7220A

SCROLL Command (cont)

#### Character/Graphics Combined Mode (Character Display) Built-In RAM Map

|      |     |        |     |          |       |     | 1     |  |  |

|------|-----|--------|-----|----------|-------|-----|-------|--|--|

| L    | MSB |        |     | <u> </u> |       |     | LSB   |  |  |

| RA   | l   |        | С   | ontents  | of RA | М   |       |  |  |

| 0    |     |        |     | SAE      | )1L   |     |       |  |  |

| 1    |     |        |     | SAD      | 1M    |     |       |  |  |

| 2    |     | SL     | .1L |          | 0     | 0   | SAD1H |  |  |

| 3    | *   | 0 SL1H |     |          |       |     |       |  |  |

| 4    |     | SAD2L  |     |          |       |     |       |  |  |

| 5    |     | SAD2M  |     |          |       |     |       |  |  |

| 6    |     | SL     | .2L |          | . 0   | 0   | SAD2H |  |  |

| 7    | *   | 0 SL2H |     |          |       |     |       |  |  |

| 8    |     |        |     | SAI      | D3L   |     |       |  |  |

| 9    |     |        |     | ŞAE      | МЕС   |     |       |  |  |

| Α    |     | SI     | .3L |          | 0     | 0   | SAD3H |  |  |

| В    | *   | 0      |     |          | SL    | зн  |       |  |  |

| С    |     |        |     | SA       | D4L   |     |       |  |  |

| D    |     |        |     | SAI      | D4M · |     |       |  |  |

| E    |     | SI     | .4L |          | 0     | 0   | SAD4H |  |  |

| F    | *   | 0      |     |          | SL    | .4H |       |  |  |

| * DA | D+2 |        |     |          |       |     |       |  |  |

|    | MSB |        |     |         |       |     |   | LSE |  |

|----|-----|--------|-----|---------|-------|-----|---|-----|--|

| RA |     |        | C   | ontents | of RA | M   |   |     |  |

| 0  |     |        |     | SAE     | )1L   |     |   |     |  |

| 1  |     |        |     | SAE     | н     |     |   |     |  |

| 2  |     | SL     | .1L |         | 0     | 0   | 0 | 0   |  |

| 3  | *   | 0      |     |         | SL    | 1H  |   |     |  |

| 4  |     | SAD2L  |     |         |       |     |   |     |  |

| 5  |     | SAD2H  |     |         |       |     |   |     |  |

| 6  |     | SL     | .2L | 0 0 0 0 |       |     |   |     |  |

| 7  | *   | 0 SL2H |     |         |       |     |   |     |  |

| 8  |     |        |     | SAI     | D3L   |     |   |     |  |

| 9  |     |        | •   | SAD     | эн    |     |   |     |  |

| Α  |     | SI     | .3L |         | 0     | 0   | 0 | 0   |  |

| В  | *   | 0      |     |         | SL    | .3H |   |     |  |

| C  |     |        |     | SAI     | 04L   |     |   |     |  |

| D  |     |        |     | SAI     | 04H   |     |   |     |  |

| E  |     | SI     | _4L |         | 0     | 0   | 0 | 0   |  |

| F  | *   | 0      |     |         | SL    | .4H |   |     |  |

### Character/Graphics Combined Mode (Graphics Display/Drawing)

#### Built-In RAM Map

|    | MSB |    |          |         |       |     | .   | LSE |

|----|-----|----|----------|---------|-------|-----|-----|-----|

| RA |     |    | C        | Content | of RA | M   |     |     |

| 0  |     |    |          | SAI     | )1L   | •   |     |     |

| 1  |     |    |          | SAE     | 1M    |     |     |     |

| 2  |     | SI | .1L      |         | 0     | 0   | SAD | 1H  |

| 3  | *   | IM |          |         | SL    | .1H |     |     |

| 4  |     |    |          | SAI     | D2L   |     |     |     |

| 5  | 1   |    |          | SAE     | D2M   |     |     |     |

| 6  | 1   | SI | _2L      |         | 0     | 0   | SAL | 2H  |

| 7  | *   | IM | <u> </u> |         | SL    | .2H | ·   |     |

|    | MSB |    |     |         |         |    | , | LSB |

|----|-----|----|-----|---------|---------|----|---|-----|

| RA |     |    | (   | Content | s of RA | М  |   |     |

| 0  |     |    |     | SA      | D1L     |    |   |     |

| 1  |     |    |     | SAI     | D1H     |    |   |     |

| 2  |     | SL | .1L |         | 0       | 0  | 0 | 0   |

| 3  | *   | IM |     |         | SL      | 1H |   |     |

| 4  |     |    |     | SA      | D2L     |    |   |     |

| 5  |     |    |     | SA      | D2H     |    |   |     |

| 6  |     | SI | .2L |         | 0       | 0  | 0 | 0   |

| 7  | *   | IM | T   |         | SL      | 2H |   |     |

T-52-33-47

#### Table 4. Comparison of µPD72020 and µPD7220A Functions (cont)

μPD72020 Scroll Command (cont)

#### **Graphics Mode** Built-In RAM Map

| MSB      |                 |            |             |                                        |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LSB                                                                            |

|----------|-----------------|------------|-------------|----------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| <u> </u> | Contents or RAM |            |             |                                        |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |

|          | SAD1L           |            |             |                                        |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |

|          |                 |            | SAD         | D1M                                    |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |

|          | SL              | .1L        | 1L S/       |                                        |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |

| *        | IM              | SL1H       |             |                                        |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |

|          |                 |            | SAI         | D2L                                    |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |

|          |                 |            | SAI         | 2M                                     |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |

|          | SL              | SL2L SAD2H |             |                                        |                                                               | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                |

| *        | IM              | SL2H       |             |                                        |                                                               | ÷                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                |

|          | *               | SI.        | SL1L *   IM | Contents SAI SAI SL1L * IM SAI SAI SAI | Contents or R/  SAD1L   SAD1M   SL1L     SAD2L   SAD2M   SL2L | Contents or RAM   SAD1L   SAD1M   SL1L   SAI   SAI   SAD2L   SAD2M   SL2L   SAI   SAI | Contents of RAM   SAD1L   SAD1M   SAD1H   SAD1H   SAD2L   SAD2M   SL2L   SAD2H |

|    | MSB      |                 |    |     |      |     |     | LSE |  |

|----|----------|-----------------|----|-----|------|-----|-----|-----|--|

| RA | <u> </u> | Contents or RAM |    |     |      |     |     |     |  |

| 0  |          | SAD1L           |    |     |      |     |     |     |  |

| 1  |          |                 |    | SAD | 1M   |     |     |     |  |

| 2  |          | SL1L            |    |     | 0    | 0   | SAD | 1H  |  |

| 3  | *        | IM              |    |     | SL1H |     |     |     |  |

| 4  |          |                 |    | SAU | )2L  | •   |     |     |  |

| 5  | Ī        |                 |    | SAE | 2M   |     |     |     |  |

| 6  |          | ŞL              | 2L |     | 0    | 0   | SAD | 2H  |  |

| 7  | *        | IM              |    |     | SL   | .2H |     |     |  |

#### **COMMANDS**

The  $\mu$ PD72020 supports all commands of the  $\mu$ PD720A. Although command names are different, opcodes are the same. The  $\mu$ PD72020 can activate the software created for use with the  $\mu$ PD7220A.

The improved functions of the  $\mu$ PD72020 can be used by setting the new WMASK command. Once the RESET command is input, however, the WMASK command becomes inactive and the  $\mu$ PD72020 maintains the same functions as those of the  $\mu$ PD7220A.

This section describes the WMASK command as well as the SCROLL, LPEN, CSRW, and CSRR commands, which are affected by the setting of the WMASK command.

#### **WMASK Command**

This new command (figure 1) controls four new functions.

- · WMASK register setting

- Address extension

- Selection of additional functions in the external slave mode

- DT signal generation

Figure 1. WMASK Command Format

|     | DB7       | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----------|-----|-----|-----|-----|-----|-----|-----|

| CMD | 0         | 1   | 0   | 1   | 1   | 0   | 1   | 0   |

| P1  |           |     |     | W   | ΛKL |     |     |     |

| P2  | · · · · · |     |     | W٨  | 1KH |     |     |     |

| P3  | PN        | TM  | DTE | CY1 | CY0 | 0   | 0   | 0   |

WMK Bit. The  $\mu$ PD72020 is equipped with the conventional MASK register and a 16-bit WMASK register. The WMK bit is used to set this WMASK register.

The 16-bit WMASK register is used for write mask of the multicolor, simultaneously-drawn data with one word set in 8-, 4-, 2- and 1-bit formats. Each bit of the WMASK register corresponds to each bit of the drawn data.

- (1) When a WMASK register bit is set to 0 by the WMK, the drawn data bit corresponding to the WMASK register bit set to 0 is not affected by drawing.

- (2) When a WMASK register bit is set to 1 by the WMK, operation is similar to the μPD7220A. Thus, the

drawn data bit corresponding to the WMASK register bit set to 1 is affected by drawing.

When the RESET command is input, the  $\mu$ PD72020 is set to this mode.

PN Bit. PN is used to set the address extension function for the video memory.

(1) When PN = 0, operation is similar to the  $\mu$ PD7220A. Thus, the address extension function cannot be used.

When the RESET command is input, the  $\mu$ PD72020 is set to this mode.

(2) When PN = 1, the video memory address is extended 2 bits (with the address space expanded fourfold).

The DRQ/A $_{18}$ /A $_{13}$ /A $_{16}$  pin and the  $\overline{DACK}$ /A $_{19}$ /A $_{14}$ /A $_{17}$  pin output the upper 2 bits of the extended address. The DMA-related functions cannot be used.

The address to be output depends on the display and drawing modes. See table 1. The address space is shown in table 5.

Table 5. Address Space With Extended Address

|         | Character<br>Mode | Character/Graphics<br>Combined Mode | Graphics<br>Mode |  |

|---------|-------------------|-------------------------------------|------------------|--|

| Address | 15 bits           | 18 bits                             | 20 bits          |  |

| space   | (32K words)       | (256K words)                        | (1M words)       |  |

As the address space is expanded, the following command bits are also extended.

- LAD bit of LPEN command

- EAD bit of CSRW command

- EAD bit of CSRR command

- · SAD bit of SCROLL command

Refer to the description of each command for details.

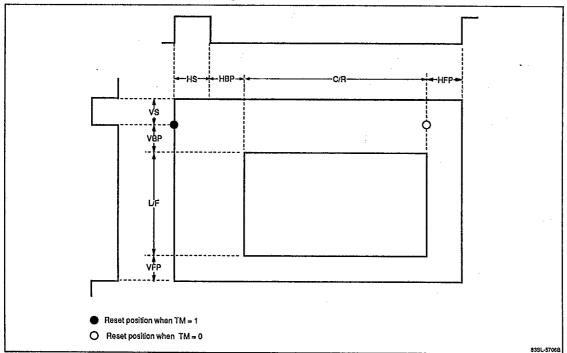

TM Bit. TM has been added to solve the following two problems with the  $\mu$ PD7220A.

Because the vertical and horizontal counters are initialized at the start of VFP and HFP, respectively, when the external synchronizing signal is input to the μPD7220A, horizontal positioning cannot be readily done for synchronization with the μPD7220A by inputting a synchronizing signal from the external device.

T-52-33-47

When the μPD7220A is operated in the interlace mode, input of the external synchronizing signal causes no effect on the field counter. Thus, if the synchronizing signal is unconditionally input from the external device when the μPD7220A is in the second field, the second and first fields are reversed in subsequent frames and the fields do not conform with the external device.

When the  $\mu$ PD72020 operates in the slave mode for external synchronization, the setting of the TM bit will cause the  $\mu$ PD72020 to operate differently from the  $\mu$ PD7220A in the following operations.

- The timing of initializing the horizontal synchronous counter is changed.

- The initializing function of the field counter is validated.

When TM = 0, the function similar to the external synchronizing function of the  $\mu$ PD7220A is carried out. When the RESET command is input, the  $\mu$ PD72020 is set to this mode.

When TM = 1, the following two operations differ from those of the  $\mu$ PD7220A.

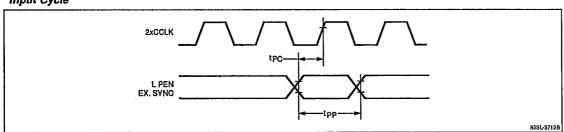

- (1) When the RESET command is executed or the EX.SYNC (external synchronizing signal) is input, the horizontal counter is reset at the rising edge of the HS. See figure 2.

- (2) When the RESET command is executed in the interlace mode or the EX.SYNC signal is input, the field counter is unconditionally reset to the first field mode.

Thus, the VSYNC signal in the second field should be removed externally so that the synchronizing signal applied to the EX.SYNC pin serves as the VSYNC signal in the first field (in the interlace mode).

30E D

30E D

#### µPD72020

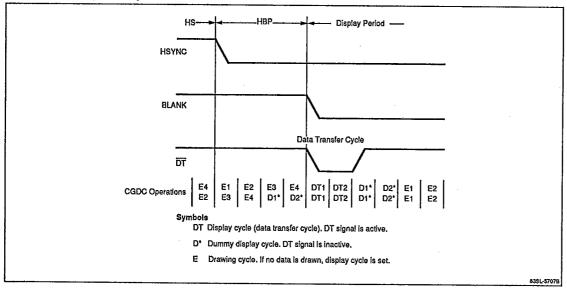

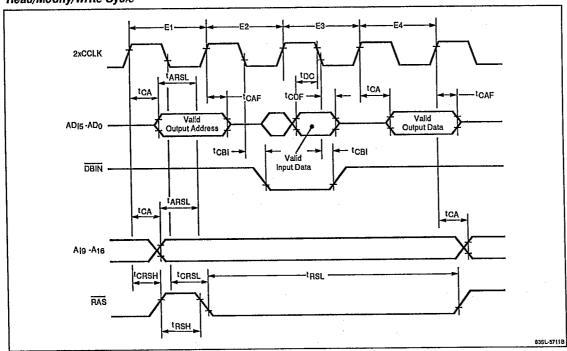

DTE, CY1, CY0 Bits. To prevent the display screen from becoming blurred during drawing operations, the μPD7220A normally performed drawing in the flashless drawing mode. Thus, the drawing period was limited and it was difficult to improve the drawing efficiency.

To solve this problem, video RAMs can be used for the  $\mu$ PD72020. Through the use of VRAMs, both drawing and display can be carried out simultaneously in the flashless drawing mode with the result that the drawing efficiency can be improved. DTE, CY1, and CY0 are used to control the µPD41264-type VRAMs and the BLANK signal.

Table 6. DT Signal Output Modes

| DTE | CY1 | CY0 | Function                                      |

|-----|-----|-----|-----------------------------------------------|

| ō   | 0   | . 0 | GDC mode 0                                    |

| 0   | 0   | 1   | GDC mode 1 (BLANK signal mask †)              |

| 0   | 1   | 0   | Inhibited                                     |

| 0   | 1   | 1   | Inhibited                                     |

| 1   | 0   | 0   | DT signal output mode 0 (BLANK signal mask t) |

| 1   | 0   | 1   | Inhibited                                     |

| 1   | 1   | 0   | DT signal output mode 1 (BLANK signal mask †) |

| 1   | 1   | 1   | DT signal output mode 2 (BLANK signal mask †) |

† If the µPD72020 has started drawing operations in the display mode, the BLANK signal is not set to H.

DTE = 0. Operation is similar to the  $\mu$ PD7220A. The  $\overline{\text{DT}}$ signal functions cannot be used. The LPEN/WAIT/DT pin performs the LPEN or WAIT functions.

The following two modes are available by setting CY1 or CY0 (table 6).

- (1) GDC mode 0 operation is similar to the μPD7220A. When the RESET command is input, the µPD72020 is set to this mode.

- (2) GDC mode 1 operation is similar to GDC mode 0 except if the µPD72020 starts drawing operations during the display period, the BLANK signal is not set to H even in the flash screen mode.

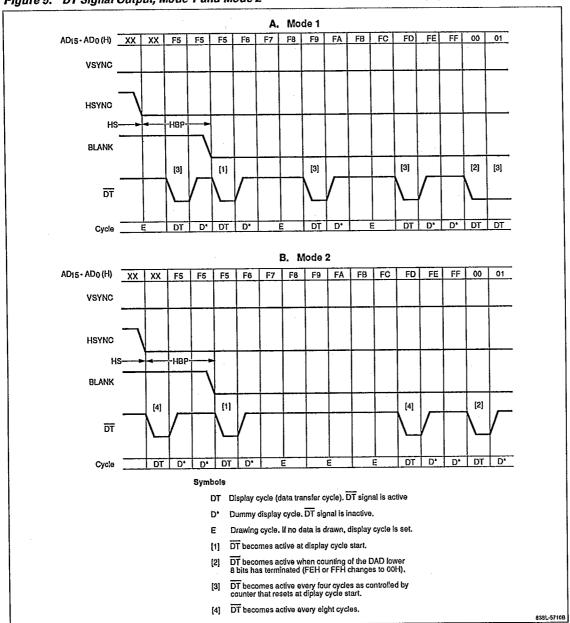

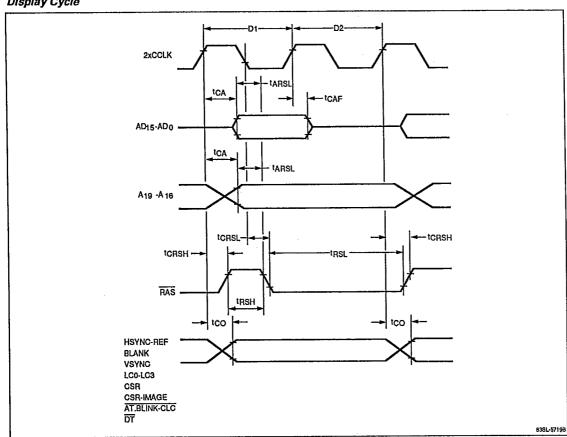

DTE = 1. The  $\overline{DT}$  signal functions are enabled and the DT signal is output from the LPEN/WAIT/DT pin. The DT signal is used for display timing when the display memory consists of dual-port video RAMs. The VRAMs allow drawing during both drawing and display cycles.

When DTE is set to 1, the  $\mu$ PD72020 internally tracks the display address and outputs it and the  $\overline{\text{DT}}$  signal under either of two conditions.

- (1) At the start of every horizontal scan line (figure 3).

- (2) When the lower 8 bits of the display address (DAD) internal counter are 0.

The starting display address should be set before setting DTE to 1. The µPD72020 will temporarily stop a drawing operation before issuance of the DT signal, as in the case of the µPD7220A WAIT function.

The  $\overline{\text{DT}}$  signal output timing depends on the setting of the IM and DAD+2 bits of the SCROLL command. CY0 and CY1 determine which of the following three DT signal output modes is used.

μPD72020

T-52-33-47

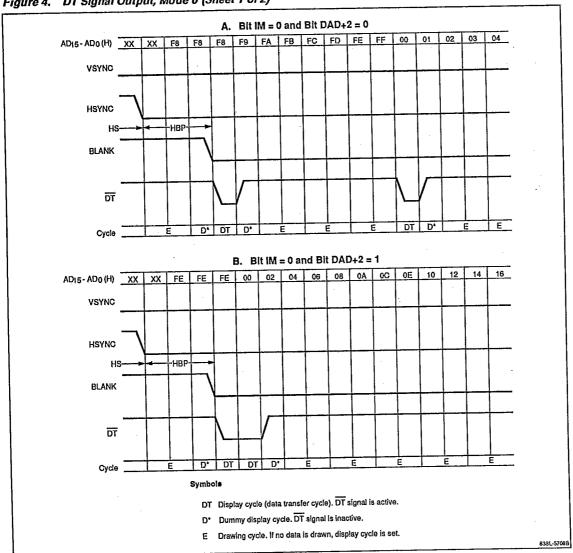

Mode 0 With DTE = 1. In mode 0, the  $\overline{DT}$  signal is output as shown in figure 4.

- (1) At the start of every horizontal scan line.

- (2) When the lower 8 bits of the DAD counter change from FEH or FFH to 00H.

Additionally, the  $\overline{DT}$  signal active state in mode 0 has the following qualifications.

- (1) DT may become active in succession; for example, when the DAD counter changes to 00H just after the start of a horizontal scan line as in figure 4C.

- (2) When the lower 8 bits of the DAD counter become 00H in succession, DT becomes active during the first cycle only. See figure 4D.

- (3) DT will not become active during HFP, HS, HBP, VFP, VS, or VBP periods.

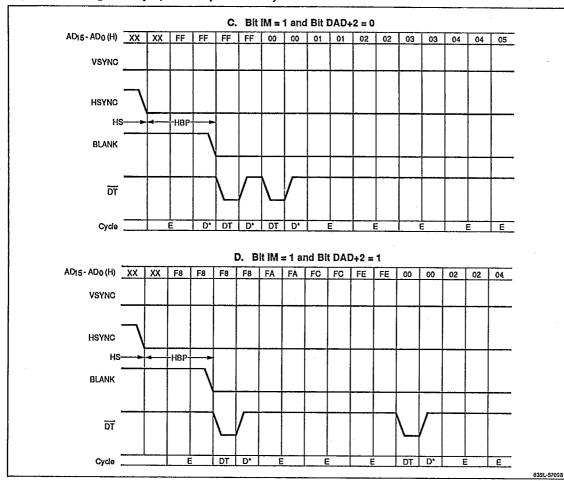

**Mode 1 With DTE** = 1. In mode 1, the  $\overline{DT}$  signal is outut as shown in figure 5A.

(1) At the start of every horizontal scan line.

(2) When the lower 8 bits of the DAD counter change from FEH or FFH to 00H.

Additionally, the  $\overline{\text{DT}}$  signal active state in mode 1 has the following qualifications.

- (1) DT may become active in succession.

- (2) When the lower 8 bits of the DAD counter change to 00H in succession, DT is active only during the first cycle.

- (3) DT can become active during HFP, HS, HBP, VFP, VS, or VBP periods.

- (4) DT will not become active while the DMA refresh operation is disabled (D-bit of SYNC command set to 1).

- (5) DT becomes active every four cycles.

Mode 2 With DTE = 1. In mode 2, the  $\overline{DT}$  signal output is the same as described for mode 1 except  $\overline{DT}$  is active every eight cycles instead of every four cycles. See figure 5B.

Figure 3. DT Signal Output for Each Horizontal Line

T-52-33-47

$\mu$ PD72020

T-52-33-47

Figure 4. DT Signal Output, Mode 0 (Sheet 2 of 2)

3

30E D

#### μPD72020

T-52-33-47

Figure 5. DT Signal Output, Mode 1 and Mode 2

T-52-33-47

#### **LPEN Command**

When the address extension function is set by the WMASK command (with PN set to 1), the upper 2 bits of the light pen address (LAD) in the LPEN command are extended and a maximum of 20 bits can be used.

When PN = 0, the light pen address (LAD) is the same as with the  $\mu PD7220A.$

The LPEN command format with the extended LAD is shown in figure 6.

Figure 6. LPEN Command Format

| DB7 | DB6 | DB5 | DB4   | DB3                                   | DB2                   | ĎΒ1                     | DBO                         |

|-----|-----|-----|-------|---------------------------------------|-----------------------|-------------------------|-----------------------------|

| 1   | 1   | 0   | 0     | 0                                     | 0                     | 0                       | 0                           |

|     | •   |     | LA    | DL                                    | <del></del>           | ·                       |                             |

|     |     | •   | LA    | DM                                    |                       |                         |                             |

| Х   | х   | Х   | X     | · · · · · · · · · · · · · · · · · · · | LA                    | DH                      |                             |

|     | DB7 | 1 1 | 1 1 0 | 1 1 0 0<br>LA                         | 1 1 0 0 0 0 LADL LADM | 1 1 0 0 0 0 0 LADL LADM | 1 1 0 0 0 0 0 0 0 LADL LADM |

#### **CSRW** Command

When the address extension function is set by the WMASK command (with PN set to 1), the upper 2 bits of the drawing execution address (EAD) in the LPEN command are extended.

When PN = 0, the drawing execution address (EAD) is the same as with the  $\mu$ PD7220A.

Address extension causes the WG bits to be positioned differently in the character/graphics combined mode (character display/drawing) or the graphics mode.

The CSRW command formats are included in table 4.

#### **CSRR** Command

When the address extension function is set by the WMASK command (with PN set to 1), the upper 2 bits of the drawing execution address (EAD) in the LPEN command are extended and a maximum of 20 bits can be used.

When PN = 0, the drawing execution address (EAD) is the same as with the  $\mu$ PD7220A.

The CSRR command format with the extended EAD is shown in figure 7.

#### Figure 7. CSRR Command Format

|      | DB7 | DB6          | DB5 | DB4 | DB3 | DB2 | DB1 | DBO |  |

|------|-----|--------------|-----|-----|-----|-----|-----|-----|--|

| CMD  | 1   | 1            | 1   | 0   | 0   | 0   | Q   | 0   |  |

| D1 - |     | EADL         |     |     |     |     |     |     |  |

| D2   |     | EADM         |     |     |     |     |     |     |  |

| D3   | X   | X X X X EADH |     |     |     |     |     |     |  |

| D4   |     | dADL         |     |     |     |     |     |     |  |

| D5   |     | dADH         |     |     |     |     |     |     |  |

#### **SCROLL Command**

When the address extension function is set by the WMASK command (with PN set to 1), the upper 2 bits of the display start address (SAD) in the SCROLL command are extended.

When PN = 0, the display start address (SAD) is the same as with the  $\mu$ PD7220A.

The SCROLL command format is shown in figure 8. The built-in RAM map with the extended SAD is included in table 4.

#### Figure 8. SCROLL Command Format

|     | D87 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| CMD | 0   | 1   | 1   | 1   |     | R   | A   |     |

30E D

#### μPD72020

T-52-33-47

### Absolute Maximum Ratings

| Supply voltage, V <sub>DD</sub>                                                          | -0.5 to +7.0 V                                               |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Input voltage, V <sub>I</sub>                                                            | - 0.5 to V <sub>DD</sub> + 0.3 V                             |

| Output voltage, Vo                                                                       | -0.5 to V <sub>DD</sub> + 0.3 V                              |

| Operating temperature, TOPT                                                              | - 10 to +70°C                                                |

| Storage temperature, TSTG                                                                | -65 to +150°C                                                |

| Exposure to Absolute Maximum Ratio affect device reliability; exceeding the nent damage. | ngs for extended periods may<br>ne ratings could cause perma |

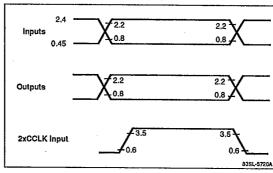

DC Characteristics T<sub>A</sub> = -10 to +70°C; V<sub>DD</sub> = +5.0 V ±10%

| Parameter                              | Symbol           | Min                 | Max                   | Unit | Conditions                                                   |

|----------------------------------------|------------------|---------------------|-----------------------|------|--------------------------------------------------------------|

| Low-level input                        | V <sub>IL</sub>  | - 0.5               | 0.8                   | ٧    | Except 2xCCLK                                                |

| voltage                                | ,                | -0.5                | 0,6                   | ٧    | 2xCCLK                                                       |

| High-level input<br>voltage            | V <sub>IH</sub>  | 2.2                 | V <sub>CC</sub> + 0.5 | ٧    | Except<br>2xCCLK, WR                                         |

|                                        |                  | 3.5                 | V <sub>CC</sub> + 0.5 | ٧    | 2xCCLK                                                       |

|                                        |                  | 2.5                 | V <sub>CC</sub> + 0.5 | ٧    | WR                                                           |

| Low-level<br>output voltage            | V <sub>OL</sub>  |                     | 0.45                  | ٧    | I <sub>OL</sub> = 2.2 mA                                     |

| High-level<br>output voltage           | Vон              | 0.7 V <sub>DD</sub> |                       | ٧    | $l_{OH} = -400 \mu\text{A}$                                  |

| Low-level input<br>leakage current     | ILIL             |                     | -10                   | μА   | V <sub>I</sub> = 0 V;<br>except<br>VSYNC, DACK               |

|                                        |                  |                     | -500                  | μА   | V <sub>I</sub> = 0 V;<br>VSYNC, DACK                         |

| High-level input<br>leakage current    |                  | -                   | 10                    | μА   | V <sub>I</sub> = V <sub>DD</sub> ;<br>except<br>LPEN/WAIT/DT |

|                                        |                  |                     | 500                   | μА   | V <sub>I</sub> = V <sub>DD</sub> ;<br>LPEN/WAIT/DT           |

| Low-level<br>output leakage<br>current | I <sub>LOL</sub> | <u> </u>            | -10                   | μА   | V <sub>O</sub> = 0 V                                         |

| High-level output leakage current      | Ісон             |                     | 10                    | μА   | V <sub>O</sub> = V <sub>DD</sub>                             |

| Supply current                         | lcc              |                     | 70                    | mA   |                                                              |

Capacitance T<sub>A</sub> = +25°C; V<sub>DD</sub> = GND = 0 V

| Item         | Symbol           | Min | Max | Unit | Condition                 |

|--------------|------------------|-----|-----|------|---------------------------|

| Input        | Ci               |     | 15  | pF   | f = 1 MHz;                |

| Output       | Co               |     | 20  | рF   | 0 V except for tested pin |

| Input/output | C <sub>I/O</sub> | •   | 20  | рF   |                           |

| Clock input  | CC               |     | 20  | pF   |                           |

AC Characteristics  $T_A = -10 \text{ to } +70^{\circ}\text{C}; V_{DD} = +5.0 \text{ V} \pm 10\%$

| A = -10 to +70 O;                      | 400 - i          | -0.0 V = 1              | 0,70                     |      |                            |

|----------------------------------------|------------------|-------------------------|--------------------------|------|----------------------------|

| tem                                    | Symbol           | Min                     | Max                      | Unit | Conditions                 |

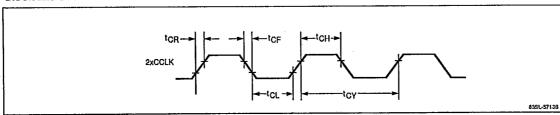

| Clock 2xCCLK                           |                  |                         |                          |      |                            |

| Clock cycle                            | tcy              | 125                     | 10,000                   | ns   |                            |

| High-level clock<br>width              | <sup>†</sup> СН  | 52                      |                          | ns   |                            |

| Low-level clock<br>width               | tCL              | 52                      |                          | ns   |                            |

| Clock rise time                        | <sup>t</sup> CR  |                         | 15                       | ns   |                            |

| Clock fall time                        | t <sub>CF</sub>  |                         | 15                       | ns   | <del></del>                |

| Read Cycle                             |                  |                         |                          |      |                            |

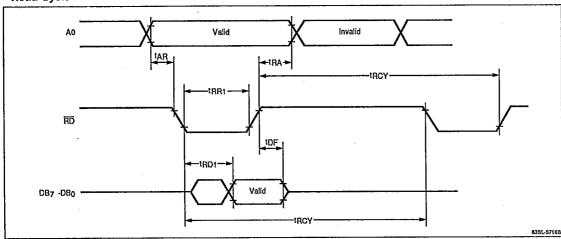

| Address setup time<br>to RD \$         | t <sub>AR</sub>  | 0                       |                          | ns   |                            |

| Address hold time<br>from RD↑          | t <sub>RA</sub>  | 0                       |                          | ns   |                            |

| RD pulse width                         | t <sub>RR1</sub> | <sup>†</sup> RD1<br>+20 |                          | ns   |                            |

| Data output delay<br>time from RD ↓    | <sup>†</sup> RD1 |                         | 55                       | ns   | C <sub>L</sub> = 50 pF     |

| Data float delay<br>time from RD ↑     | t <sub>DF</sub>  | 0                       | 55                       | ns   |                            |

| RD pulse cycle                         | tRCY             | 4.5 t <sub>CY</sub>     |                          | ns   | DE = 0                     |

|                                        |                  | 12 t <sub>CY</sub>      |                          | ns   | DE = 1                     |

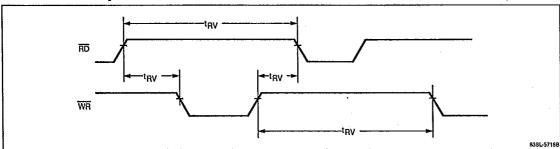

| RD recovery time                       | t <sub>RV</sub>  | 2 t <sub>CY</sub>       |                          | ns   | Also valid in<br>DMA cycle |

| Write Cycle                            |                  |                         |                          |      |                            |

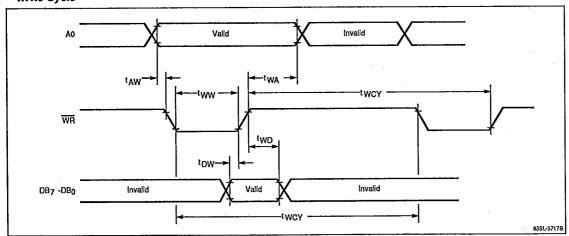

| Address setup time to WR↓              | t <sub>AW</sub>  | 0                       |                          | ns   |                            |

| Address hold time from WR ↑            | t <sub>WA</sub>  | 10                      |                          | ns   |                            |

| WR pulse width                         | tww              | 60                      |                          | ns   |                            |

| Data setup time to WR ↑                | tow              | 45                      |                          | ns.  |                            |

| Data hold time<br>from WR ↑            | t <sub>WD</sub>  | 10                      |                          | ns   |                            |

| WR pulse cycle                         | twcy             | 4.5 t <sub>CY</sub>     |                          | ns   |                            |

| WR recovery time                       | t <sub>RV</sub>  | 2 t <sub>CY</sub>       |                          | ns   | Also valid ir<br>DMA cycle |

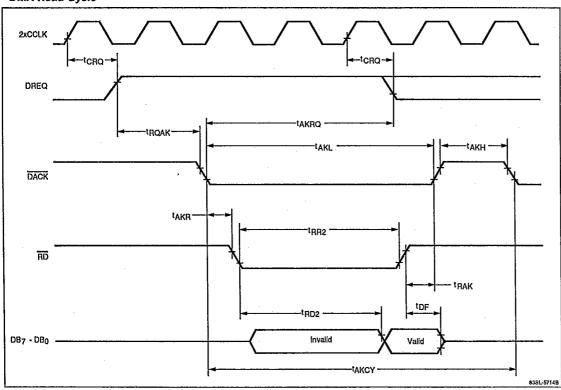

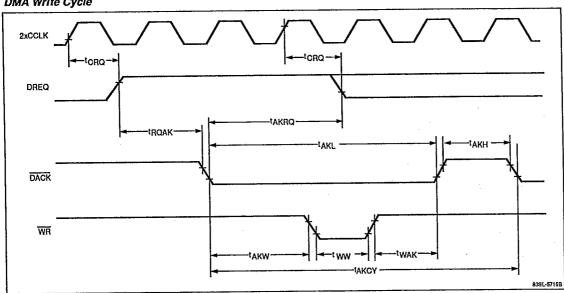

| DMA Read Cycl                          | e                |                         |                          |      |                            |

| DACK setup time to RD ↓                | t <sub>AKR</sub> | 0                       |                          | ns   |                            |

| DACK hold time from RD ↑               | t <sub>RAK</sub> | 0                       |                          | ns   |                            |

| RD pulse width                         | t <sub>RR2</sub> | t <sub>RD2</sub><br>+20 |                          | ns   |                            |

| Data output<br>delay time from<br>RD ↓ | t <sub>RD2</sub> |                         | 2 t <sub>CY</sub><br>+60 |      | C <sub>L</sub> = 50 pF     |

|                                        |                  |                         |                          |      |                            |

$\mu$ PD72020

T-52-33-47

#### AC Characteristics (cont)

| $T_A = -10 \text{ to } +70^{\circ}\text{C}$       | $T_A = -10 \text{ to } +70^{\circ}\text{C}; V_{DD} = +5.0 \text{ V} \pm 10\%$ |                             |                                |      |                        |  |  |  |  |  |

|---------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------|--------------------------------|------|------------------------|--|--|--|--|--|