**TENTATIVE**

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC90A18AF

## TIME COMPRESSION LSI FOR EDTV-II WIDE-SCREEN TVs

TC90A18AF is a time-compression LSI for wide-screen TVs. With a compression ratio of 0.5 to 2, the device can display a 4:3 aspect ratio NTSC/PAL signal on a 16:9 aspect ratio TV screen.

Using horizontal 16-point variable compression, this LSI can realize digital super live mode.

Among the wide range of functions offered by the LSI are EDTV-II broadcast detection, letterbox detection, and caption detection.

Weight: 1.6 g (Typ.)

#### **FEATURES**

- Fixed ratio compression processing

- 0.5 to 1 × fixed ratio compression (64 steps)

- 1 to 1.5 x fixed ratio expansion (32 steps)

- 2 x expansion

- Digital super live mode

- Compression and expansion with specified ratio within a horizontal period (16 points settable)

- EDTV-II

- NRZ pattern detection

- DC offset detection

- Top and bottom blank portion detection

- Letterbox detection

- Caption detection

- Incorporates two 8-bit ADCs for Y/V and I/Q inputs

- Incorporates three 8-bit DACs for Y, I, and Q outputs

- Incorporates 1368fHVCO

- I<sup>2</sup>C bus control (slave address : 40H)

- 3.3 V single power supply

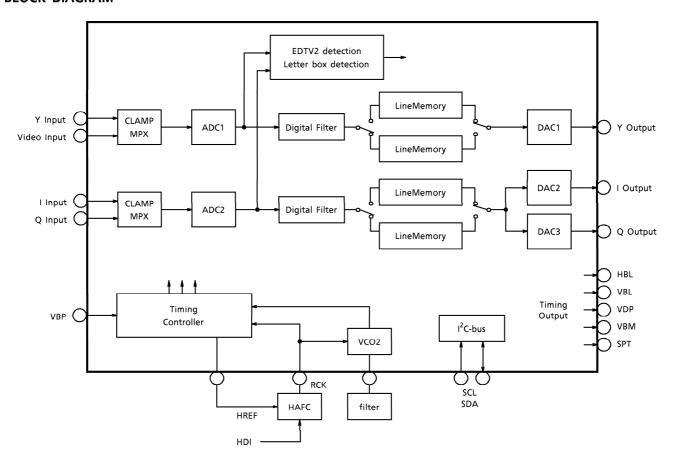

## **BLOCK DIAGRAM**

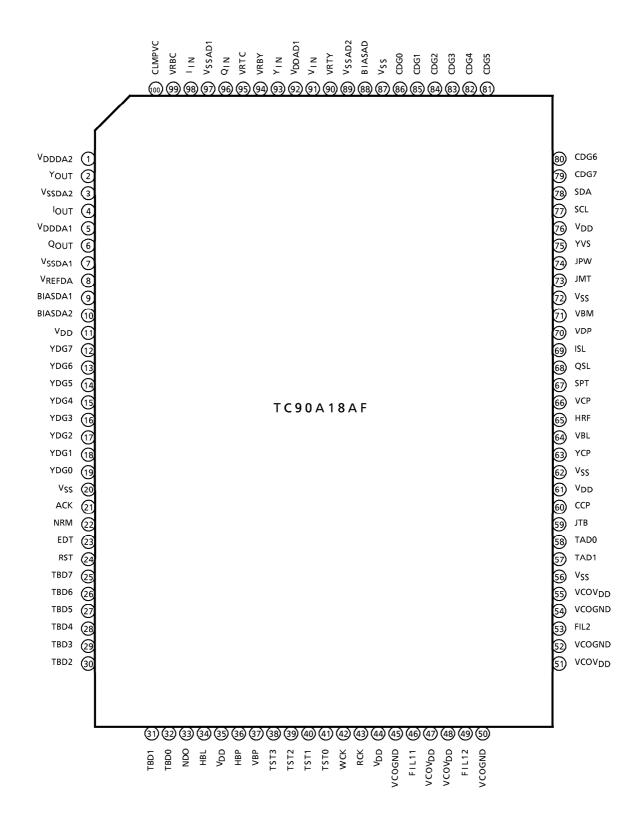

### **TERMINAL CONNECTION DIAGRAM**

## TERMINAL FUNCTION

| IEKMIN     | NAL FUNCTION       |     |                                                    |                                                 |

|------------|--------------------|-----|----------------------------------------------------|-------------------------------------------------|

| PIN<br>No. | PIN NAME           | 1/0 | FUNCTION                                           | OPERATING CONDITIONS                            |

| 1          | V <sub>DDDA2</sub> | _   | Analog power supply                                | + 3.3 V                                         |

| 2          | Yout               | _   | Luminance signal analog output                     | D range : V <sub>DD</sub> to V <sub>REFDA</sub> |

| 3          | V <sub>SSDA2</sub> | _   | Analog GND                                         | _                                               |

| 4          | lout               | _   | I signal analog output                             | D range : V <sub>DD</sub> to V <sub>REFDA</sub> |

| 5          | V <sub>DDDA1</sub> | _   | Analog power supply                                | + 3.3 V                                         |

| 6          | Q <sub>OUT</sub>   | _   | Q signal analog output                             | D range : V <sub>DD</sub> to V <sub>REFDA</sub> |

| 7          | V <sub>SSDA1</sub> | _   | Analog GND                                         | _                                               |

| 8          | VREFDA             | _   | DAC reference voltage supply pin                   | V <sub>DD</sub> - 1.5 V                         |

| 9          | BIASDA1            | _   | DAC bias voltage pin 1                             | _                                               |

| 10         | BIASDA2            | _   | DAC bias voltage pin 2                             | _                                               |

| 11         | $V_{DD}$           | I   | Digital power supply                               | + 3.3 V                                         |

| 12         | YDG7               | I   | Test input (normally connect to VSS)               | _                                               |

| 13         | YDG6               | ı   | Test input (normally connect to V <sub>SS</sub> )  | _                                               |

| 14         | YDG5               | ı   | Test input (normally connect to V <sub>SS</sub> )  | _                                               |

| 15         | YDG4               | I   | Test input (normally connect to V <sub>SS</sub> )  | _                                               |

| 16         | YDG3               | I   | Test input (normally connect to V <sub>SS</sub> )  | _                                               |

| 17         | YDG2               | I   | Test input (normally connect to V <sub>SS</sub> )  | _                                               |

| 18         | YDG1               | I   | Test input (normally connect to V <sub>SS</sub> )  | _                                               |

| 19         | YDG0               | I   | Test input (normally connect to VSS)               | _                                               |

| 20         | VSS                | _   | Digital GND                                        | _                                               |

| 21         | ACK                | 0   | Test output                                        | _                                               |

|            | NIDA               |     | I <sup>2</sup> C bus subaddress 30H : NRM contents |                                                 |

| 22         | NRM                | 0   | output (data from microcontroller)                 | _                                               |

| 23         | EDT                | 0   | Unmatch output of ED2 signal NRZ pattern           |                                                 |

| 23         |                    | 0   | (for each field, unmatch : L, match : H)           | _                                               |

| 24         | RST                | I   | System reset input (normal : H, reset : L)         | _                                               |

| 25         | TBD7               | I   | Test input (normally connect to V <sub>SS</sub> )  | _                                               |

| 26         | TBD6               | I   | Test input (normally connect to V <sub>SS</sub> )  | _                                               |

| 27         | TBD5               | I   | Test input (normally connect to V <sub>SS</sub> )  | _                                               |

| 28         | TBD4               | I   | Test input (normally connect to V <sub>SS</sub> )  | _                                               |

| 29         | TBD3               | I   | Test input (normally connect to V <sub>SS</sub> )  | _                                               |

| 30         | TBD2               | I   | Test input (normally connect to V <sub>SS</sub> )  | _                                               |

| 31         | TBD1               | I   | Test input (normally connect to V <sub>SS</sub> )  | _                                               |

| 32         | TBD0               | I   | Test input (normally connect to V <sub>SS</sub> )  | _                                               |

| 33         | NDO                | 0   | Test output                                        | _                                               |

| 34         | HBL                | 0   | Horizontal blanking signal output                  | _                                               |

| 35         | $V_{DD}$           | _   | Digital power supply                               | <del>_</del>                                    |

| 36         | НВР                | I   | Horizontal sync signal input                       | <u> </u>                                        |

| 37         | VBP                | I   | Vertical sync signal input                         | _                                               |

| 38         | TST3               | I   | Test mode setting                                  | _                                               |

|            |                    |     | (normally connect to V <sub>DD</sub> )             |                                                 |

| 39         | TST2               | I   | Test mode setting (normally connect to VSS)        | <del>_</del>                                    |

| 40         | TST1               | I   | Test mode setting                                  | _                                               |

|            |                    |     | (normally connect to V <sub>DD</sub> )             |                                                 |

| PIN<br>No. | PIN NAME           | I/O | FUNCTION                                                 | OPERATING CONDITIONS |

|------------|--------------------|-----|----------------------------------------------------------|----------------------|

| 41         | TST0               | -   | Test mode setting (normally connect to V <sub>DD</sub> ) | _                    |

| 42         | WCK                | I   | Test input (normally connect to VSS)                     | _                    |

| 43         | RCK                | I   | Memory read clock input (1824fH)                         | _                    |

| 44         | $V_{DD}$           | _   | Digital power supply                                     | + 3.3 V              |

| 45         | VCOGND             | _   | VCO GND                                                  | _                    |

| 46         | FIL11              | _   | External filter pin 1 for VCO1                           | _                    |

| 47         | vcov <sub>DD</sub> | _   | VCO power supply                                         | + 3.3 V              |

| 48         | vcov <sub>DD</sub> | _   | VCO power supply                                         | + 3.3 V              |

| 49         | FIL12              | _   | External filter pin 2 for VCO1                           | _                    |

| 50         | VCOGND             | _   | VCO GND                                                  | _                    |

| 51         | vcov <sub>DD</sub> | _   | VCO power supply                                         | + 3.3 V              |

| 52         | VCOGND             | _   | VCO GND                                                  | _                    |

| 53         | FIL2               | _   | External filter pin for VCO2                             | _                    |

| 54         | VCOGND             | _   | VCO GND                                                  | _                    |

| 55         | vcov <sub>DD</sub> | _   | VCO power supply                                         | + 3.3 V              |

| 56         | V <sub>SS</sub>    | _   | Digital GND                                              | _                    |

| 57         | TAD1               | 0   | Test output                                              | _                    |

| 58         | TAD0               | 0   | Test output                                              | _                    |

| 59         | JTB                | 0   | Timing signal for caption position                       | _                    |

| 60         | CCP                | 0   | I <sup>2</sup> C bus acknowledge output (active H)       | _                    |

| 61         | $V_{DD}$           | _   | Digital power supply                                     | + 3.3 V              |

| 62         | V <sub>SS</sub>    | _   | Digital GND                                              | _                    |

| 63         | YCP                | 0   | Clamp pulse position output for luminance                | _                    |

| 64         | VBL                | 0   | Vertical blanking signal output                          | _                    |

| 65         | HRF                | 0   | Horizontal AFC reference signal output                   | _                    |

| 66         | VCP                | 0   | Clamp pulse position output for video                    | _                    |

| 67         | SPT                | 0   | Side panel position output                               | _                    |

| 68         | QSL                | 0   | 684fH output                                             | _                    |

| 69         | ISL                | 0   | 684fH output (QSL reverse output)                        | _                    |

| 70         | VDP                | 0   | Vertical drive pulse output                              | _                    |

| 71         | VBM                | 0   | Timing signal for vertical black masking                 | _                    |

| 72         | V <sub>SS</sub>    | _   | Digital GND                                              | _                    |

| 73         | JMT                | 0   | Caption detection signal (caption : H, no caption : L)   | _                    |

| 74         | JPW                | 0   | PWM output                                               | _                    |

| 75         | YVS                | 0   | Video/luminance switching signal output (22H, 285H)      | _                    |

| 76         | $V_{DD}$           | _   | Digital power supply                                     | _                    |

| 77         | SCL                | I   | I <sup>2</sup> C bus clock input                         | _                    |

| 78         | SDA                | 1/0 | I <sup>2</sup> C bus data input/output                   | _                    |

| PIN<br>No. | PIN NAME           | 1/0 | FUNCTION                                            | OPERATING CONDITIONS |

|------------|--------------------|-----|-----------------------------------------------------|----------------------|

| 79         | CDG7               | I   | Test input (normally connect to V <sub>SS</sub> )   | _                    |

| 80         | CDG6               | I   | Test input (normally connect to V <sub>SS</sub> )   | _                    |

| 81         | CDG5               | I   | Test input (normally connect to V <sub>SS</sub> )   | _                    |

| 82         | CDG4               | I   | Test input (normally connect to VSS)                | _                    |

| 83         | CDG3               | I   | Test input (normally connect to V <sub>SS</sub> )   | _                    |

| 84         | CDG2               | I   | Test input (normally connect to V <sub>SS</sub> )   | _                    |

| 85         | CDG1               | I   | Test input (normally connect to VSS)                | _                    |

| 86         | CDG0               | _   | Test input (normally connect to VSS)                | _                    |

| 87         | VSS                | _   | Digital GND                                         | _                    |

| 88         | BIASAD             | _   | ADC bias voltage pin                                | _                    |

| 89         | V <sub>SSAD2</sub> | _   | Analog GND                                          | _                    |

| 90         | VRTY               | _   | Video / luminance ADC reference voltage (H side)    | 208LSB               |

| 91         | V <sub>IN</sub>    | _   | Video signal input                                  | Pedestal clamp       |

| 92         | V <sub>DDAD1</sub> | _   | Analog power supply                                 | + 3.3 V              |

| 93         | Y <sub>IN</sub>    | _   | Luminance signal input                              | Pedestal clamp       |

| 94         | VRBY               | _   | Video / luminance ADC reference voltage<br>(L side) | 64LSB                |

| 95         | VRTC               | _   | I/Q ADC reference voltage (H side)                  | 208LSB               |

| 96         | Q <sub>IN</sub>    | _   | Q signal input                                      |                      |

| 97         | V <sub>SSAD1</sub> | _   | Analog GND                                          | _                    |

| 98         | I <sub>IN</sub>    | _   | I signal input                                      | _                    |

| 99         | VRBC               | _   | I/Q ADC reference voltage (L side)                  | 64LSB                |

| 100        | CLMPVC             | _   | I/Q clamp pin                                       | _                    |

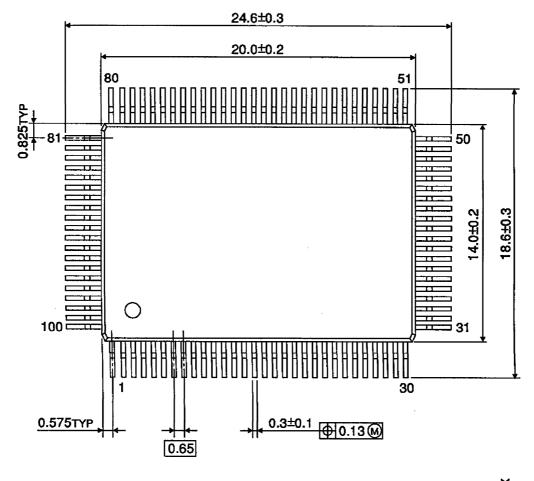

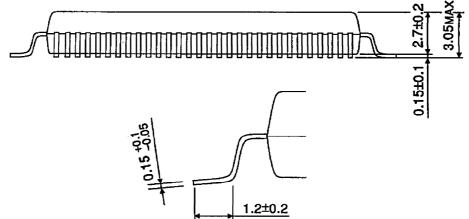

## **PACKAGE DIMENSIONS**

QFP100-P-1420-0.65A Unit: mm

Weight: 1.6 g (Typ.)

#### **RESTRICTIONS ON PRODUCT USE**

000707EBA

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- ◆ The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.