# VT6103

# Fast Ethernet 10 / 100 1-Port PHY / Transceiver

**Revision 1.1 April 15, 2002**

VIA TECHNOLOGIES, INC.

# **Copyright Notice:**

Copyright © 2001, 2002 VIA Technologies Incorporated. Printed in the United States. ALL RIGHTS RESERVED.

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise without the prior written permission of VIA Technologies Incorporated.

VT6103 may only be used to identify products of VIA Technologies, Inc.

is a registered trademark of VIA Technologies, Incorporated.

PS/2<sup>TM</sup> is a registered trademark of International Business Machines Corp.

Pentium<sup>TM</sup>, Pentium-Pro<sup>TM</sup>, Pentium-III<sup>TM</sup>, Pentium-III<sup>TM</sup>, Celeron<sup>TM</sup>, and GTL+<sup>TM</sup> are registered trademarks of Intel Corp. Windows 95<sup>TM</sup>, Windows 98<sup>TM</sup>, Windows NT<sup>TM</sup>, and Plug and Play<sup>TM</sup> are registered trademarks of Microsoft Corp.

PCI<sup>TM</sup> is a registered trademark of the PCI Special Interest Group.

All trademarks are the properties of their respective owners.

## **Disclaimer Notice:**

No license is granted, implied or otherwise, under any patent or patent rights of VIA Technologies. VIA Technologies makes no warranties, implied or otherwise, in regard to this document and to the products described in this document. The information provided by this document is believed to be accurate and reliable to the publication date of this document. However, VIA Technologies assumes no responsibility for any errors in this document. Furthermore, VIA Technologies assumes no responsibility for the use or misuse of the information in this document and for any patent infringements that may arise from the use of this document. The information and product specifications within this document are subject to change at any time, without notice and without obligation to notify any person of such change.

# Offices:

**USA Office:** 940 Mission Court Fremont, CA 94539 USA

Tel: (510) 683-3300

Fax: (510) 683-3301 or (510) 687-4654

Web: http://www.viatech.com

Taipei Office:

8<sup>th</sup> Floor, No. 533 Chung-Cheng Road, Hsin-Tien Taipei, Taiwan ROC

Tel: (886-2) 2218-5452 Fax: (886-2) 2218-5453 Web: http://www.via.com.tw

# **REVISION HISTORY**

| Document Release | Date    | Revision                                                                               | Initials |

|------------------|---------|----------------------------------------------------------------------------------------|----------|

| 1.0              | 4/9/02  | Initial Public Release – same as internal release 0.4 except for update of legal page, | DH       |

|                  |         | fix of miscellaneous document formatting errors, update of document title,             |          |

|                  |         | addition of typical system block diagram, fix of RXER and TXER pin                     |          |

|                  |         | descriptions, update of application schematics, and addition of marking spec           |          |

| 1.1              | 4/15/02 | Revised document title and page headers                                                | DH       |

|                  |         | Fixed Taiwan office fax number on legal page                                           |          |

|                  |         | Cleaned up schematics and added as figures                                             |          |

# TABLE OF CONTENTS

| REVISION HISTORY                             | I  |

|----------------------------------------------|----|

| TABLE OF CONTENTS                            | II |

| LIST OF FIGURES                              | IV |

| LIST OF TABLES                               | IV |

| PRODUCT FEATURES                             | 1  |

| OVERVIEW                                     | 2  |

| PINOUTS                                      | 3  |

| PIN DIAGRAM                                  |    |

| PIN LIST                                     | 3  |

| PIN DESCRIPTIONS                             | 4  |

| REGISTERS                                    | 7  |

| REGISTER OVERVIEW                            | 7  |

| REGISTER DESCRIPTIONS                        | 9  |

| FUNCTIONAL DESCRIPTION                       | 16 |

| GENERAL                                      | 16 |

| 802.3u MII                                   |    |

| Serial Management Register Access            | 18 |

| Serial Management Access Protocol            |    |

| Preamble Suppression                         |    |

| PHY Address Sensing                          |    |

| Nibble-Wide MII Data Interface               |    |

| Collision Detect                             |    |

| Carrier Sense                                |    |

| MII Isolate Mode                             | 19 |

| LINK INTEGRITY AND AUTONEGOTIATION           | 20 |

| General                                      |    |

| 10Base-T Link Integrity Algorithm – 10Mbps   |    |

| 100Base-TX Link Integrity Algorithm -100Mbps |    |

| AutoNegotiation Algorithm                    |    |

| AutoNegotiation Outcome Indication           |    |

| AutoNegotiation Status                       |    |

| AutoNegotiation Enable                       |    |

| Auto Negotiation Reset                       |    |

| Link Indication                              | 20 |

| ENCODER                                      | 21 |

| 4B5B Encoder – 100 Mbps                      | 21 |

| Manchester Encoder – 10 Mbps                 | 21 |

| DECODER                                      | 21 |

| 4B5B Encoder – 100 Mbps                      |    |

| Manchester Encoder – 10 Mbps                 |    |

| CLOCK AND DATA RECOVERY                      |    |

|                                              |    |

| Clock Recovery – 100 Mbps                |    |

|------------------------------------------|----|

| Data Recovery – 100 Mbps                 | 22 |

| Clock Recovery – 10 Mbps                 | 22 |

| Data Recovery – 10 Mbps                  |    |

| SCRAMBLER / DESCRAMBLER                  | 22 |

| 100 Mbps Scrambler                       | 22 |

| 10 Mbps Scrambler                        |    |

| 100 Mbps Descrambler                     | 22 |

| 10 Mbps Descrambler                      | 22 |

| TWISTED PAIR TRANSMITTER                 | 23 |

| Transmitter - 100 Mbps                   | 23 |

| Transmitter - 10 Mbps                    | 23 |

| TWISTED PAIR RECEIVER                    | 24 |

| Receiver - 100 Mbps                      | 24 |

| Receiver - 10 Mbps                       | 24 |

| MISCELLANEOUS FUNCTIONS                  | 25 |

| Smart Squelch                            | 25 |

| Collision Detection                      | 25 |

| Carrier Sense                            |    |

| Normal Link Pulse Detection / Generation | 25 |

| Jabber Function                          | 26 |

| Status Information                       |    |

| Automatic Link Polarity Detection        |    |

| Internal Loopback                        |    |

| 100BASE-FX                               | 27 |

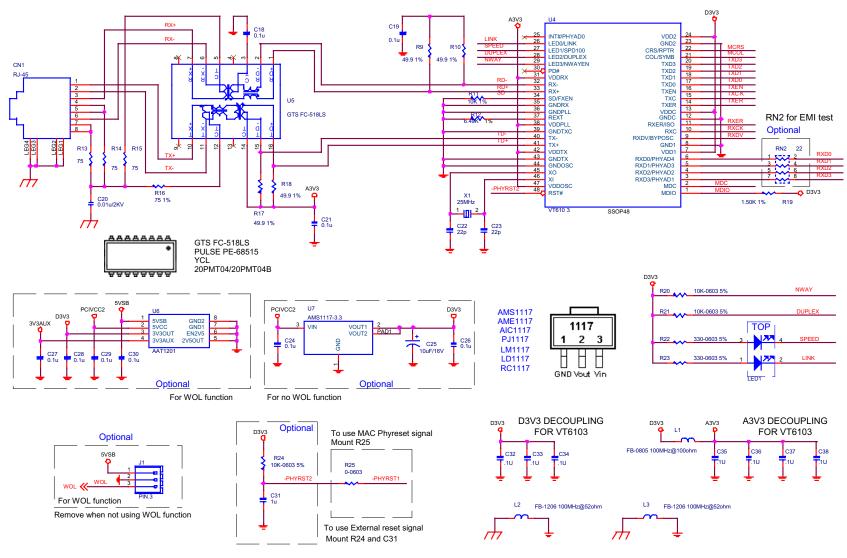

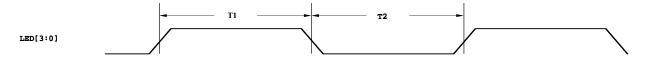

| APPLICATION SCHEMATICS                   | 28 |

| ELECTRICAL SPECIFICATIONS                | 31 |

| ABSOLUTE MAXIMUM RATINGS                 | 31 |

| DC CHARACTERISTICS                       | 31 |

| AC CHARACTERISTICS                       | 31 |

| 100BaseT Transmitter Characteristics     | 32 |

| 10BaseT Transmitter Characteristics      |    |

| Crystal Oscillator Characteristics       |    |

| PLL Frequency Multiplier Characteristics |    |

| FX Characteristics                       |    |

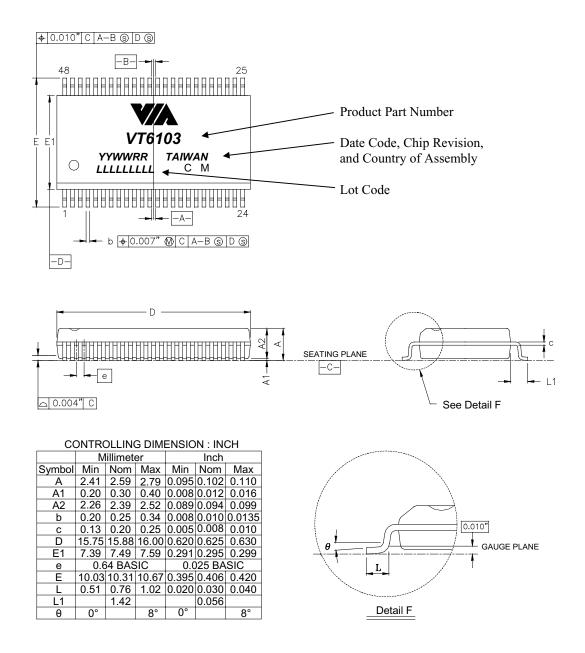

| PACKAGE MECHANICAL SPECIFICATIONS        | 40 |

# **LIST OF FIGURES**

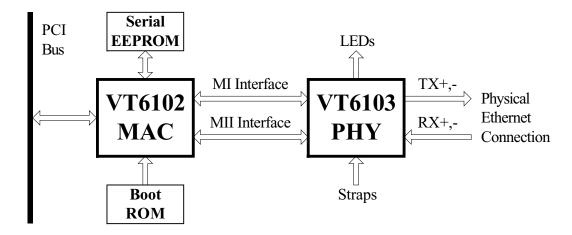

| FIGURE 1. TYPICAL SYSTEM BLOCK DIAGRAM                     | 2  |

|------------------------------------------------------------|----|

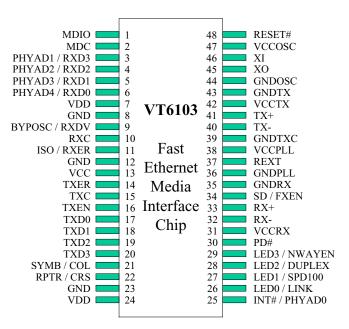

| FIGURE 2. PIN DIAGRAM                                      |    |

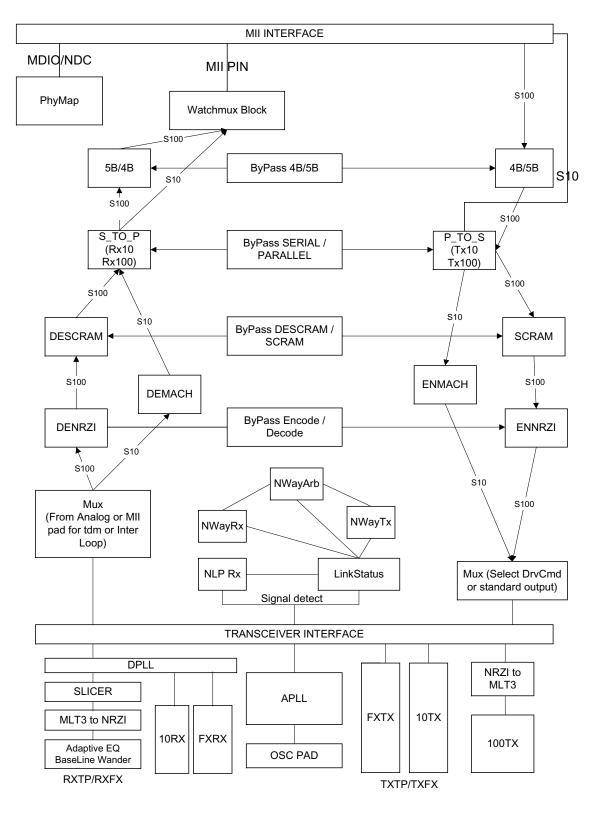

| FIGURE 3. INTERNAL BLOCK DIAGRAM                           | 17 |

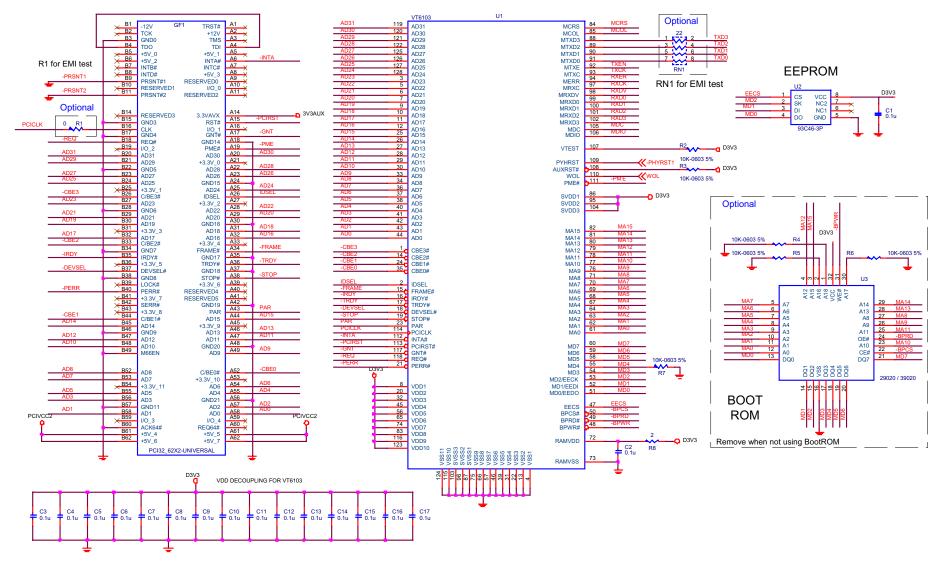

| FIGURE 4. APPLICATION SCHEMATIC EXAMPLE PAGE 1             | 29 |

| FIGURE 5. APPLICATION SCHEMATIC EXAMPLE PAGE 2             | 30 |

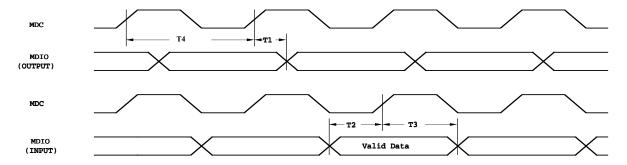

| FIGURE 6. MI INTERFACE MDIO TIMING                         | 34 |

| FIGURE 7. MI INTERFACE MDIO INTERRUPT PULSE TIMING         | 34 |

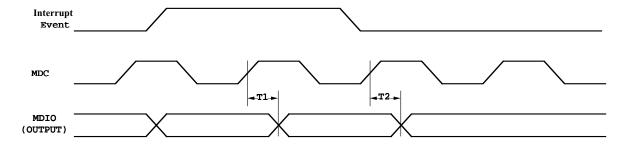

| FIGURE 8. LED ON / OFF TIMING                              | 35 |

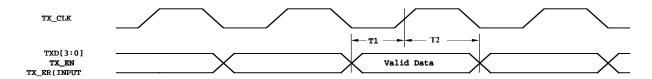

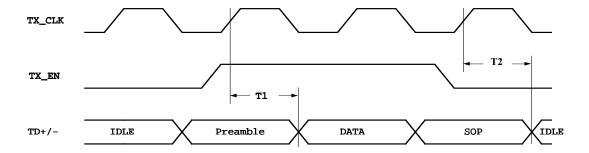

| FIGURE 9. MII TRANSMIT DATA TIMING                         | 35 |

| FIGURE 10. MII RECEIVE DATA TIMING                         | 35 |

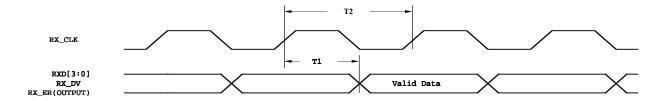

| FIGURE 11. MII HEARTBEAT TIMING                            |    |

| FIGURE 12. MII JABBER TIMING                               |    |

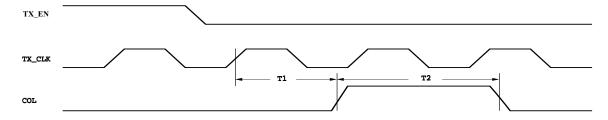

| FIGURE 13. MII NORMAL LINK PULSE TIMING                    | 37 |

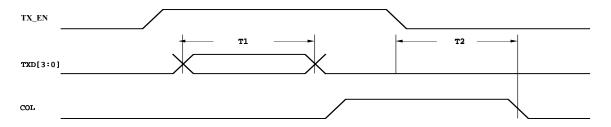

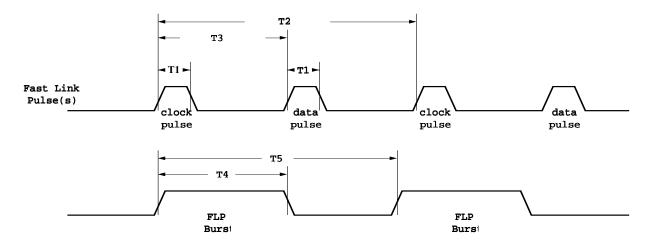

| FIGURE 14. MII AUTO-NEGOTIATION FAST LINK PULSE TIMING     | 37 |

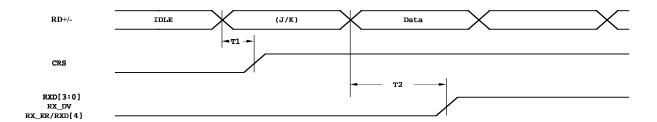

| FIGURE 15. 100MB/S RECEIVE PACKET TIMING                   |    |

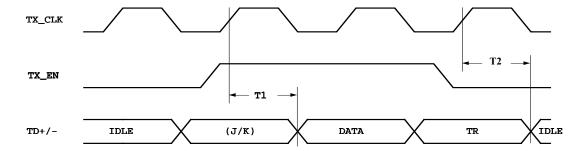

| FIGURE 16. 100MB/S TRANSMIT PACKET TIMING                  |    |

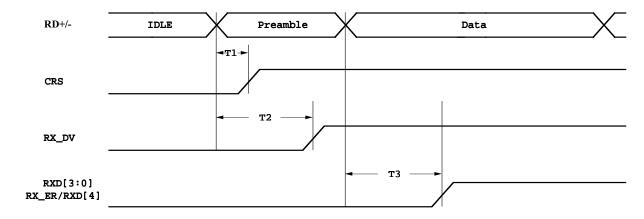

| FIGURE 17. 10MB/S RECEIVE PACKET TIMING                    |    |

| FIGURE 18. 10MB/S TRANSMIT PACKET TIMING                   |    |

| FIGURE 19. MECHANICAL SPECIFICATIONS – 48 PIN SSOP PACKAGE | 40 |

# LIST OF TABLES

| TABLE 1. PIN LIST (ALPHABETICAL ORDER)                      | 3    |

|-------------------------------------------------------------|------|

| TABLE 2. PIN DESCRIPTIONS                                   | 4    |

| TABLE 3. REGISTER SUMMARY                                   | 7    |

| TABLE 4. REGISTER BIT SUMMARY – REGISTERS DEFINED BY 802.3U |      |

| TABLE 5. REGISTER BIT SUMMARY - VENDOR DEFINED REGISTERS    |      |

| TABLE 6. LED FUNCTION DEFINITION                            |      |

| TABLE 7. MI INTERFACE MDIO OUTPUT TIMING                    | . 34 |

| TABLE 8. MI INTERFACE MDIO INTERRUPT PULSE TIMING           | 34   |

| TABLE 9. LED ON / OFF TIMING                                | 35   |

| TABLE 10. MII TRANSMIT DATA TIMING                          | 35   |

| TABLE 11. MII RECEIVE DATA TIMING                           | 35   |

| TABLE 12. MII HEARTBEAT TIMING                              | 36   |

| TABLE 13. MII JABBER TIMING                                 | 36   |

| TABLE 14. MII 10BASE-T NORMAL LINK PULSE TIMING             | 37   |

| TABLE 15. MII AUTO-NEGOTIATION FAST LINK PULSE TIMING       | 37   |

| TABLE 16. 100MB/S RECEIVE PACKET TIMING                     | 38   |

| TABLE 17. 100MB/S TRANSMIT PACKET TIMING                    | 38   |

| TABLE 18. 10MB/S RECEIVE PACKET TIMING                      |      |

| TABLE 19. 10MB/S TRANSMIT PACKET TIMING                     | 39   |

|                                                             |      |

# VT6103

# FAST ETHERNET 10 / 100 1-PORT PHY / TRANSCEIVER

#### PRODUCT FEATURES

- Single Chip 100Base-TX / 10Base-T Physical Layer Solution

- **Dual Speed 100 / 10 Mbps**

- Half and Full Duplex

- MII Interface to Ethernet Controller

- MII Interface to Configuration & Status

- Optional Repeater Interface

- Auto Negotiation: 10 / 100, Full / Half Duplex

- Meet All Applicable IEEE 802.3, 10Base-T and 100Base-Tx Standards

- On Chip Wave Shaping No External Filters Required

- Adaptive Equalizer

- Baseline Wander Correction

- LED Outputs

- Link Status

- Duplex status

- Speed Status

- Collision

- 48 Pin SSOP Package

## **OVERVIEW**

The VT6103 is a Physical Layer device for Ethernet 10Base-T and 100Base-TX using category 5 Unshielded, Type 1 Shielded, and Fiber Optic cables. This VLSI device is designed for easy implementation of 10 / 100 Mb/s Fast Etherent LANs. It interfaces to a MAC through an MII interface ensuring interoperability between products from different vendors.

Figure 1. Typical System Block Diagram

# **PINOUTS**

#### Pin Diagram

Figure 2. Pin Diagram

#### Pin List

Table 1. Pin List (Alphabetical Order)

| Pin# |        | Pin Name      | Pin # |        | Pin Name      |

|------|--------|---------------|-------|--------|---------------|

| 21   | O / I  | COL / SYMB    | 5     | IO / I | RXD1 / PHYAD3 |

| 22   | O / I  | CRS / RPTR    | 4     | IO / I | RXD2 / PHYAD2 |

| 8    | P      | GND           | 3     | IO / I | RXD3 / PHYAD1 |

| 12   | P      | GND           | 9     | IO / I | RXDV / BYPOSC |

| 23   | P      | GND           | 11    | O / I  | RXER / ISO    |

| 44   | P      | GNDOSC        | 34    | I/I    | SD / FXEN     |

| 36   | P      | GNDPLL        | 40    | О      | TX-           |

| 35   | P      | GNDRX         | 41    | О      | TX+           |

| 43   | P      | GNDTX         | 15    | О      | TXC           |

| 39   | P      | GNDTXC        | 17    | I      | TXD0          |

| 25   | O / I  | INT# / PHYAD0 | 18    | I      | TXD1          |

| 26   | O / I  | LED0 / LINK   | 19    | I      | TXD2          |

| 27   | O / I  | LED1 / SPD100 | 20    | I      | TXD3          |

| 28   | O / I  | LED2 / DUPLEX | 16    | I      | TXEN          |

| 29   | O / I  | LED3 / NWAYEN | 14    | I      | TXER          |

| 2    | I      | MDC           | 13    | P      | VCC           |

| 1    | IO     | MDIO          | 47    | P      | VCCOSC        |

| 30   | I      | PD#           | 38    | P      | VCCPLL        |

| 48   | I      | RESET#        | 31    | P      | VCCRX         |

| 37   | A      | REXT          | 42    | P      | VCCTX         |

| 32   | I      | RX-           | 7     | P      | VDD           |

| 33   | I      | RX+           | 24    | P      | VDD           |

| 10   | O      | RXC           | 46    | I      | XI            |

| 6    | IO / I | RXD0 / PHYAD4 | 45    | О      | XO            |

## **Pin Descriptions**

**Table 2. Pin Descriptions**

| Management Interface (MI) |       |     |                                                                                                       |  |  |

|---------------------------|-------|-----|-------------------------------------------------------------------------------------------------------|--|--|

| Signal Name               | Pin # | I/O | Signal Description                                                                                    |  |  |

| MDIO                      | 1     | IO  | Management Interface (MI) Data I/O. Received from the external MAC.                                   |  |  |

| MDC                       | 2     | I   | <b>Management Interface (MI) Clock.</b> Received from the external MAC as a timing reference for MDIO |  |  |

| INT# / PHYAD0             | 25    | 0   | Management Interface (MI) Interrupt Out. Active low.                                                  |  |  |

| Media Independent Interface (MII) |                   |     |                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-----------------------------------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Signal Name                       | Pin #             | I/O | Signal Description                                                                                                                                                                                                                                                                                                                                            |  |  |

| RXC                               | 10                | О   | <b>Receive Clock.</b> Timing reference for transfer of RXD and RXDV. 25 MHz when operating at 100 Mbps and 2.5 MHz when operating at 10 Mbps (always active).                                                                                                                                                                                                 |  |  |

| RXD3 / PHYAD1,                    | 3                 | О   | <b>Receive Data.</b> These bits transition with RXC. RXD[3:0] should accepted by the external                                                                                                                                                                                                                                                                 |  |  |

| RXD2 / PHYAD2,                    | 4                 |     | MAC for each RXC period in which RXDV is asserted. RXD0 is the least significant bit.                                                                                                                                                                                                                                                                         |  |  |

| RXD1 / PHYAD3,                    | 5                 |     | While RXDV is de-asserted, RXD[3:0] have no effect upon the switch's MAC and the                                                                                                                                                                                                                                                                              |  |  |

| RXD0 / PHYAD4                     | 6                 |     | value of RXD[3:0] is unspecified.                                                                                                                                                                                                                                                                                                                             |  |  |

| RXDV / BYPOSC                     | 9                 | O   | <b>Receive Data Valid.</b> RXDV is driven to indicate that nibbles are being presented on the MII for receiving. RXDV transitions synchronous to RXC. It is asserted synchronously with the first nibble of the preamble and remains asserted while all nibbles to be received are presented to the MII.                                                      |  |  |

| RXER / ISO                        | 11                | О   | <b>Receive Error.</b> The VT6103 asserts this output when it receives invalid symbols from the network                                                                                                                                                                                                                                                        |  |  |

| TXC                               | 15                | О   | <b>Transmit Clock.</b> Timing reference for transfer of TXD and TXEN. 25MHz when operating at 100 Mbps and 2.5 MHz when operating at 10 Mbps (always active).                                                                                                                                                                                                 |  |  |

| TXD[3-0]                          | 20, 19,<br>18, 17 | I   | <b>Transmit Data.</b> These bits transition relative to TXC. TXD[3:0] are accepted from the external MAC for each TXC period in which TXEN is asserted. TXD0 is the least significant bit. While TXEN is de-asserted, TXD[3:0] have no effect and the value of TXD[3:0] is unspecified.                                                                       |  |  |

| TXEN                              | 16                | I   | <b>Transmit Enable.</b> Indicates transmit active from the MII port. TXEN transitions synchronous to TXC. TXEN indicates that the nibbles presented on TXD[3-0] are valid for transmission. TXEN is asserted synchronously with the first nibble of the preamble and remains asserted while all nibbles to be transmitted are presented to the MII interface. |  |  |

| TXER                              | 14                | Ι   | <b>Transmit Error.</b> The MAC asserts this input when an error has occurred in the input stream.                                                                                                                                                                                                                                                             |  |  |

| COL / SYMB                        | 21                | О   | <b>Collision Detect.</b> Asserted asynchronously upon detection of a collision on the medium and remains asserted while the collision condition persists.                                                                                                                                                                                                     |  |  |

| CRS / RPTR                        | 22                | О   | <b>Carrier Sense.</b> Asserted asynchronously upon detection of a non-idle medium or while TXEN is asserted. Deasserted asynchronously upon detection of idle conditions on both transmit and receive media. Remains asserted throughout the duration of a collision condition.                                                                               |  |  |

| Physical Cable Connection |       |     |                                                                                         |  |  |

|---------------------------|-------|-----|-----------------------------------------------------------------------------------------|--|--|

| Signal Name               | Pin # | I/O | Signal Description                                                                      |  |  |

| TX+                       | 41    | O   | <b>Transmit Plus.</b> Differential outputs for FX, 100BaseTx, or 10BaseT transmission.  |  |  |

| TX-                       | 40    | О   | <b>Transmit Minus.</b> Differential outputs for FX, 100BaseTx, or 10BaseT transmission. |  |  |

| RX+                       | 33    | I   | Receive Plus. Differential inputs for FX, 100BaseTx, or 10BaseT reception.              |  |  |

| RX-                       | 32    | I   | Receive Minus. Differential inputs for FX, 100BaseTx, or 10BaseT reception.             |  |  |

| Strap Options                      |                   |     |                                                                                                                                                                                                                                                                                                                |  |  |

|------------------------------------|-------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Signal Name                        | Pin #             | I/O | Signal Description                                                                                                                                                                                                                                                                                             |  |  |

| SYMB / COL                         | 21                | I   | <b>Symbol Mode.</b> Latched into register 16 (register 10h) bit-2 at power-up / reset. Internally pulled low for default disabled.                                                                                                                                                                             |  |  |

| RPTR / CRS                         | 22                | I   | <b>Repeater Mode.</b> Latched into register 16 (register 10h) bit-4 at power-up / reset. Internally pulled low for default disabled.                                                                                                                                                                           |  |  |

| ISO / RXER                         | 11                | I   | <b>Isolate.</b> Latched into register 0 bit-10 at power-up / reset. Internally pulled low for default disabled.                                                                                                                                                                                                |  |  |

| <b>PHYAD[4:0]</b> / RXD[0:3], INT# | 6, 5, 4,<br>3, 25 | I   | <b>PHY Address.</b> Latched into register 16 (register 10h) bits 15-11 at power-up / reset. Internally pulled low, low, low, low, and high for default 00001b.                                                                                                                                                 |  |  |

| LINK / LED0                        | 26                | I   | <b>Test Mode Enable.</b> 0=Enable, 1=Disable. Do not leave floating. Pull high with 10K ohms if not used.                                                                                                                                                                                                      |  |  |

| SPD100 / LED1                      | 27                | I   | <b>Speed Select.</b> Latched into register 0 bit-13 at power-up / reset (0=Speed 10, 1=Speed100). If NWAYEN is not pulled down at power-up / reset, this pin is also latched as Speed support in register 4 (Auto-Negotiation Advertisement Base Page). Do not leave floating. Pull high or low with 10K ohms. |  |  |

| DUPLEX / LED2                      | 28                | I   | <b>Duplex Mode Select.</b> Latched into register 0 bit-8 at power-up / reset (0=Half, 1=Full). If NWAYEN is not pulled down at power-up / reset, this pin is also latched as Duplex support in register 4 (Auto-Negotiation Advertisement Base Page). Do not leave floating. Pull high or low with 10K ohms.   |  |  |

| NWAYEN / LED3                      | 29                | I   | <b>N-Way Enable.</b> Latched into register 0 bit-12 (Auto-Negotiation Enable) at power-up / reset (0=Disable, 1=Enable). Do not leave floating. Pull low with 10K ohms if not used.                                                                                                                            |  |  |

| FXEN / SD                          | 34                | I   | <b>Fiber Mode Enable.</b> Latched into register 16 (register 10h) bit-10 at power-up / reset (0=Disable, 1=Enable). Do not leave floating. Pull low with 10K ohms if not used.                                                                                                                                 |  |  |

Note: For the pins listed above, pullup / pulldown status is latched during powerup / reset. External strap option values may be set by connecting the indicated pin to a 10K ohm pull down for 0 (L) or to a 10K pull up for 1 (H).

| LED Outputs   |       |     |                                                                                 |  |  |  |

|---------------|-------|-----|---------------------------------------------------------------------------------|--|--|--|

| Signal Name   | Pin # | I/O | Signal Description                                                              |  |  |  |

| LED0 / LINK   | 26    | IO  | <b>LED Output 0.</b> See Register 16 (10h) bits 5-6 & Table 6 for LED function. |  |  |  |

| LED1 / SPD100 | 27    | IO  | <b>LED Output 1.</b> See Register 16 (10h) bits 5-6 & Table 6 for LED function. |  |  |  |

| LED2 / DUPLEX | 28    | IO  | <b>LED Output 2.</b> See Register 16 (10h) bits 5-6 & Table 6 for LED function. |  |  |  |

| LED3 / NWAYEN | 29    | IO  | <b>LED Output 3.</b> See Register 16 (10h) bits 5-6 & Table 6 for LED function. |  |  |  |

| Resets, Clocks, Control and Status |       |     |                                                                                                                                                                        |  |  |

|------------------------------------|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Signal Name                        | Pin # | I/O | Signal Description                                                                                                                                                     |  |  |

| XI                                 | 46    | Ι   | <b>Crystal In.</b> Connect to 25 MHz crystal and to 22pF 5% to GNDOSC. Can alternately be driven by an external clock source (3.3V voltage swing) with XO unconnected. |  |  |

| XO                                 | 45    | О   | <b>Crystal Feedback.</b> Connect to other side of 25 MHz crystal and to 22pF 5% to GNDOSC                                                                              |  |  |

| BYPOSC / RXDV                      | 9     | I   | <b>Bypass Oscillator.</b> Connect to pullup to use an external oscillator instead of a crystal.                                                                        |  |  |

| REXT                               | 37    | A   | External Resistor. Connect 6.49K 1% resistor to GNDOSC.                                                                                                                |  |  |

| SD / FXEN                          | 34    | I   | Signal Detect. Used in fiber mode.                                                                                                                                     |  |  |

| PD#                                | 30    | I   | Power Down. Active low.                                                                                                                                                |  |  |

| RESET#                             | 48    | I   | <b>Reset.</b> Active low. Schmitt input for improved noise immunity                                                                                                    |  |  |

| Power and Ground |       |     |                                                                                         |  |

|------------------|-------|-----|-----------------------------------------------------------------------------------------|--|

| Signal Name      | Pin # | I/O | Signal Description                                                                      |  |

| VDD              | 7, 24 | P   | <b>Digital I/O Power.</b> 3.3V nominal (3.15V to 3.45V). For digital I/O                |  |

| GND              | 8, 23 | P   | <b>Ground.</b> Connect to primary motherboard ground plane.                             |  |

| VCC              | 13    | P   | <b>Core Power.</b> 3.3V nominal (3.15V to 3.45V). For internal digital logic.           |  |

| GND              | 12    | P   | Core Ground. Connect to primary motherboard ground plane.                               |  |

| VCCOSC           | 47    | P   | Oscillator Power. 3.3V. Isolate from digital supply voltage with a ferrite bead         |  |

| GNDOSC           | 44    | P   | Oscillator Ground. Connect to primary motherboard ground plane.                         |  |

| VCCRX            | 31    | P   | <b>Receiver Power.</b> 3.3V. Isolate from digital supply voltage with a ferrite bead    |  |

| GNDRX            | 35    | P   | Receiver Ground. Connect to primary motherboard ground plane.                           |  |

| VCCTX            | 42    | P   | <b>Transmitter Power.</b> 3.3V. Isolate from digital supply voltage with a ferrite bead |  |

| GNDTX            | 43    | P   | <b>Transmitter Ground.</b> Connect to primary motherboard ground plane.                 |  |

| GNDTXC           | 39    | P   | Transmit Clock Ground. Connect to primary motherboard ground plane.                     |  |

| VCCPLL           | 38    | P   | PLL Power. 3.3V. Isolate from digital supply voltage with a ferrite bead                |  |

| GNDPLL           | 36    | P   | PLL Ground. Connect to primary motherboard ground plane.                                |  |

### **REGISTERS**

#### **Register Overview**

The VT6103 internal register set consists of thirty-two 16-bit MI (Management Interface) registers (of which 9 registers are currently undefined / reserved).

The bits of PHY registers 0-8 are defined by the IEEE 802.3u standard. The remaining PHY registers have vendor specific bit definitions. All register bits implemented by the VT6103 are described in this data sheet (see register summary table below, bit summary table on the next page, and detailed register descriptions on following pages).

PHY registers are addressed by the MAC by sending register address pointer information via the MI interface (serially over the MDIO pin clocked by MDC) with register read / write data transfer via the same pins. For more information on this mechanism, refer to IEEE 802.3 section 22.2.4.

In the register descriptions that follow, the following abbreviations are used:

RW = Read / Write

RO = Read Only

SC = Self Clearing

LH = Latch High

LL = Latch Low

"Self Clearing" bits are normally 0. If set to 1 they will perform the indicated function then automatically be cleared back to 0 by the chip. "Latch High" and "Latch Low" bits are used to record that an event (level) occurred. For Latch High bits, if the bit ever goes high, it will latch at that high level until read (the read will clear the bit). For "Latch Low" bits, if the bit goes low, it will stay at a low level until read (the read will set the bit high).

**Table 3. Register Summary**

| Offset | Offset | Management Interface Registers        | <b>Bits</b> | <b>Default</b> | Acc | <b>Page</b> |

|--------|--------|---------------------------------------|-------------|----------------|-----|-------------|

| 00     | 00h    | Management Interface Control          | 16          | 3100h          | RW  | 9           |

| 01     | 00h    | Management Interface Status           | 16          | 7849h          | RO  | 9           |

| 02     | 01h    | PHY Identifier 0                      | 16          | 0101h          | RO  | 9           |

| 03     | 02h    | PHY Identifier 1                      | 16          | 8F20h          | RO  | 9           |

| 04     | 03h    | Auto-Negotiation Advertisement Base   | 16          | 05E1h          | RW  | 10          |

| 05     | 04h    | Link Partner Advertisement Base       | 16          | 0000h          | RO  | 10          |

| 06     | 05h    | Auto-Negotiation Expansion            | 16          | 0004h          | RO  | 10          |

| 07     | 06h    | Auto-Negotiation Advertisement Next   | 16          | 2001h          | RW  | 10          |

| 08     | 07h    | Link Partner Advertisement Next       | 16          | 0000h          | RO  | 10          |

| 9-15   | 09-0Fh | -reserved-                            | _           |                |     |             |

| 16     | 10h    | PHY Configuration 1                   | 16          | 0800h          | RW  | 11          |

| 17     | 11h    | PHY Configuration 2                   | 16          | F7FFh          | RW  | 11          |

| 18     | 12h    | PHY Configuration 3                   | 16          | 0800h          | RW  | 11          |

| 19     | 13h    | PHY Configuration 4                   | 16          | FFFCh          | RW  | 12          |

| 20     | 14h    | PHY Status                            | 16          | 0000h          | RO  | 12          |

| 21     | 15h    | Link Fail Counter                     | 16          | 0000h          | RO  | 13          |

| 22     | 16h    | Invalid Symbol / Jabber Error Counter | 16          | 0000h          | RO  | 13          |

| 23     | 17h    | False Carrier / SQE Counter           | 16          | 0000h          | RO  | 13          |

| 24-25  | 18-19h | -reserved-                            | _           |                |     |             |

| 26     | 1Ah    | PHY Test Configuration 1              | 16          | 0012h          | RW  | 14          |

| 27     | 1Bh    | PHY Test Configuration 2              | 16          | C500h          | RW  | 14          |

| 28     | 1Ch    | PHY Test Configuration 3              | 16          | 0208h          | RW  | 15          |

| 29     | 1Dh    | PHY Test Configuration 4              | 16          | 0030h          | RW  | 15          |

| 30     | 1Eh    | PHY Test Configuration 5              | 16          | 001Bh          | RW  | 15          |

| 31     | 1Fh    | PHY Test Configuration 6              | 16          | 0000h          | RW  | 15          |

Table 4. Register Bit Summary - Registers Defined by 802.3u

| Bit | Register 0   | Register 1    | Register 2 | Register3 | Register4 | Register 5 | Register 6         | Register 7  | Register 8  |

|-----|--------------|---------------|------------|-----------|-----------|------------|--------------------|-------------|-------------|

| 15  | Reset        | Cap 100T4     |            |           | Next Pg   | LP Next Pg |                    | Next Page   | LP NxtPg    |

| 14  | Loop Back    | Cap Tx100F    |            |           | Ack       | LP Ack     |                    | Ack1        | LP Ack1     |

| 13  | Speed        | Cap Tx100H    |            |           | Rem Flt   | LP Rem Flt |                    | Msg Page    | LP MP       |

| 12  | Aneg Ena     | Cap Tx10F     |            | OUI (lsb) | _         | _          |                    | Ack2        | LP Ack2     |

| 11  | Power Down   | Cap Tx10H     |            |           | _         | -          |                    | Toggle      | LP Toggle   |

| 10  | Isolate      | Cap 100T2F    |            |           | Pause     | LP Pause   | _                  |             |             |

| 9   | Aneg Restart | Cap 100T2H    |            |           | 100T4     | LP 100T4   |                    |             |             |

| 8   | Duplex       | Extd Status   | OUI (msb)  |           | Tx100F    | LP Tx100F  |                    |             | Link        |

| 7   | COL Test     | _             |            | Part      | Tx100H    | LP Tx100H  |                    | Message     | Partner     |

| 6   |              | Cap Supr      |            | Number    | Tx10F     | LP Tx10F   |                    | Code Field  | Message     |

| 5   |              | Aneg Complete |            |           | Tx10H     | LP Tx10H   |                    | or          | Code Field  |

| 4   |              | Remote Fault  |            |           |           |            | Parallel Fault Det | Unformatted | or          |

| 3   | _            | Cap Aneg      |            |           |           | Link       | LP Cap Next Pg     | Code Field  | Unformatted |

| 2   |              | Link Status   |            | Revision  | Selector  | Partner    | Cap Next Page      |             | Code Field  |

| 1   |              | Jabber Detect |            | Number    | Field     | Selector   | Aneg Page Rcvd     |             |             |

| 0   |              | Extd Reg      |            |           |           | Field      | LP Cap Aneg        |             |             |

Table 5. Register Bit Summary - Vendor Defined Registers

| Bit | Register 16 | Register 17 | Register 18 | Register 19             | Register 20           | Rx21  | Rx22    | Rx23    | 26-31 |

|-----|-------------|-------------|-------------|-------------------------|-----------------------|-------|---------|---------|-------|

| 15  |             | Jabber Det  | Byp Scram   | Mask Interrupt          | Polarity Invert       |       |         |         |       |

| 14  | PHY         | SQE Detect  | Byp 4B5B    | Mask Link Up Int        | Link Up Status        |       |         |         |       |

| 13  | Address     | Pol Correct | Byp Align   | Mask Link Fail Int      | Link Fail Status      |       |         |         |       |

| 12  |             | FarEndFault | Byp NRZI    | Mask Link Change Int    | Link Status           |       |         |         |       |

| 11  |             | ChangeSeed  | LostSyncEna | Mask Aneg Compete Int   | Aneg Comp Status      |       |         |         |       |

| 10  | Fiber Mode  |             | LostSyncSel | Mask Page Rcvd Int      | Page Rcvd Status      |       |         |         |       |

| 9   | Cable Type  |             |             | Mask Jabber Int         | Jabber Status         | Link  | Receive | False   | Used  |

| 8   | Force Link  |             |             | Mask Rcvd Code Err Int  | Rcvd Code Err Status  | Fail  | Error   | Carrier | For   |

| 7   | 10LoSquSel  |             |             | Mask Bad SSD Int        | Bad SSD Status        | Count | Count   | Count   | Test  |

| 6   | Repeater    |             |             | Mask Bad ESD Int        | Bad ESD Status        |       |         |         |       |

| 5   | LED         | Seed        | _           | Mask SQE Err Int        | SQE Err Status        |       |         |         |       |

| 4   | Select      |             |             | Mask LnkFail MaxCnt Int | LnkFail MaxCnt Status |       |         |         |       |

| 3   | Int Select  |             |             | Mask Rx Err MaxCnt Int  | Rx Err MaxCnt Status  |       |         |         |       |

| 2   | Symbol      |             |             | Mask FalCarr MaxCnt Int | FalseCarr MaxCnt Stat |       |         |         |       |

| 1   | _           |             |             | =                       | Speed                 |       |         |         |       |

| 0   | _           |             |             | _                       | Duplex                |       |         |         |       |

## **Register Descriptions**

| Offset ( | (00h) | - MI Control (3100h)RW                 |

|----------|-------|----------------------------------------|

| 15       | PHY   | <b>Reset</b> default = 0, SC           |

| 14       | Loop  | back Mode                              |

|          | 0     | Disabledefault                         |

|          | 1     | Enable                                 |

| 13       | Speed | d Select LSB                           |

|          | 0     | 10                                     |

|          | 1     | 100default                             |

| 12       | Auto  | -Negotiation Process                   |

|          | 0     | Disable                                |

|          | 1     | Enabledefault                          |

| 11       | Powe  | er Down                                |

|          | 0     | Disabledefault                         |

|          | 1     | Enable                                 |

| 10       | Elect | rically Isolate PHY from MII           |

|          | 0     | Disabledefault                         |

|          | 1     | Enable                                 |

| 9        |       | -Negotiation Restartdefault = $0$ , SC |

| 8        | Dupl  | ex Mode Select                         |

|          | 0     | Half                                   |

|          | 1     | Fulldefault                            |

| 7        | COL   |                                        |

|          | 0     | Disabledefault                         |

|          | 1     | Enable                                 |

| 6        | -     | d Select MSBreserved, always reads 0   |

| 5_0      | Dagai | ryad always reads 0                    |

| Offset 1 | (01h) – MI Status (7849h)RO                             |

|----------|---------------------------------------------------------|

| 15       | Capable of 100 Base-T4 Operationdef=0                   |

| 14       | Capable of 100 Base-TX Full Duplexdef=1                 |

| 13       | Capable of 100 Base-TX Half Duplexdef=1                 |

| 12       | Capable of 10 Base-TX Full Duplexdef=1                  |

| 11       | Capable of 10 Base-TX Half Duplexdef=1                  |

| 10       | Capable of 100 Base-T2 Full Duplexdef=0                 |

| 9        | Capable of 100 Base-T2 Half Duplex $def\!=\!0$          |

| 8        | Extended Status Information in  Rx15def = 0             |

| 7        | <b>Reserved</b> always reads 0                          |

| 6        | Capable of Accepting MI Frames                          |

|          | with MI Preamble Suppresseddef=1                        |

| 5        | Auto-Negotiation Process Completeddef = 0               |

| 4        | <b>Remote Fault Condition Detected</b> LH, def=0        |

| 3        | Capable of Auto-Negotiation Operation def = 1           |

| 2        | Link StatusLL, def=0                                    |

| 1        | $\textbf{Jabber Condition Detected}LH, def \!\!=\!\! 0$ |

| 0        | Capable of Extended Registerdef=1                       |

| Offset 2 | (02h) DHV Identifier 0 (0101h) DO                       |

|          | (02h) – PHY Identifier 0 (0101h)RO                      |

| 15-0     | Company ID MSBsalways reads 0101h                       |

| Offset 3 | (03h) - PHY Identifier 1 (8F20h)RO                      |

| 15-10    | Company ID LSBsalways reads 23h                         |

| 9-4      | Manufacturer's Part numberalways reads 32h              |

| 3-0      | Manufacturer's Revision Numberalways reads 0            |

| Offset 4 | 4 (04h) – AutoNegotiation Advertisement Base Page       | Offset        | 7 (07h) – AutoNegotiation Advertisement Next Page    |

|----------|---------------------------------------------------------|---------------|------------------------------------------------------|

| (05E1h   | )RW                                                     | <u>(2001h</u> | )RW                                                  |

| 15       | <b>Next Page</b> default = 0                            | 15            | <b>Next Page</b> default = 0                         |

| 14       | <b>Received Code Word Recognized</b> RO, default = 0    | 14            | <b>Received Code Word Recognized</b> RO, default = 0 |

| 13       | <b>Remote Fault</b> default = 0                         | 13            | Message Pagedefault = 1                              |

| 12-11    | <b>Reserved</b> always reads 0                          | 12            | Capable of Complying with Message default = 0        |

| 10       | <b>Pause Operation for Full Duplex Link</b> default = 1 | 11            | <b>Toggle Bit</b> RO, default = 0                    |

| 9        | <b>100 Base-T4 Capable</b> default = 0                  | 10-0          | Message Code Field or Unformatted Code Field         |

| 8        | <b>100 Base-TX Full DuplexCapable</b> default = 1       |               | default = 001h                                       |

| 7        | <b>100 Base-TX Half Duplex Capable</b> default = 1      |               |                                                      |

| 6        | <b>10</b> Base-TX Full Duplex Capable default = 1       |               |                                                      |

| 5        | <b>10</b> Base-TX Half Duplex Capable default = 1       |               |                                                      |

| 4-0      | Selector Fielddefault = 00001b                          |               |                                                      |

| Offset 5 | 5 (05h) – Link Partner Advertisement Base Page          | Offset        | 8 (08h) – Link Partner Advertisement Next Page       |

|          | RO                                                      |               | )RO                                                  |

| 15       | Next Page default = 0                                   | 15            | Next Page $default = 0$                              |

| 14       | <b>Received Code Word Recognized</b> default = 0        | 14            | <b>Received Code Word Recognized</b> default = 0     |

| 13       | <b>Remote Fault</b> default = 0                         | 13            | Message Pagedefault = 0                              |

| 12-11    |                                                         | 12            | Capable of Complying with Message default = $0$      |

| 10       | <b>Pause Operation for Full Duplex Link</b> default = 0 | 11            | <b>Toggle Bit</b> default = 0                        |

| 9        | <b>100 Base-T4 Capable</b> default = 0                  | 10-0          | Message Code Field or Unformatted Code Field         |

| 8        | <b>100 Base-TX Full DuplexCapable</b> default = 0       |               | default = 0                                          |

| 7        | <b>100 Base-TX Half Duplex Capable</b> default = 0      |               |                                                      |

| 6        | 10 Base-TX Full Duplex Capable default = 0              |               |                                                      |

| 5        | 10 Base-TX Half Duplex Capable default = 0              |               |                                                      |

| 4-0      | Selector Field default = 0                              |               |                                                      |

|          |                                                         |               |                                                      |

|          |                                                         |               |                                                      |

| Offset 6 | 6 (06h) – Auto-Negotiation Expansion (0004h)RO          |               |                                                      |

| 15-5     | Reserved always reads 0                                 |               |                                                      |

| 4        | Parallel Fault Detect in Auto-Negotiation Process       |               |                                                      |

|          | LH, default = 0                                         |               |                                                      |

| 3        | Link Partner Capable of Next Page Process               |               |                                                      |

|          | $\dots default = 0$                                     |               |                                                      |

| 2        | Capable of Next Page Process default = 0                |               |                                                      |

| 1        | Page Received in Auto-Negotiation Process               |               |                                                      |

|          | LH, default = $0$                                       |               |                                                      |

| 0        | Link Partner Capable of Auto-Negotiation                |               |                                                      |

|          | Process $default = 0$                                   |               |                                                      |

| 001h) | )                                | RW                        |

|-------|----------------------------------|---------------------------|

| 15    | Next Page                        | default = 0               |

| 14    | Received Code Word Recogniz      | <b>ed</b> RO, default = 0 |

| 13    | Message Page                     | default = 1               |

| 12    | Capable of Complying with Mo     | essage default = (        |

| 11    | Toggle Bit                       | RO, default = 0           |

| 10-0  | Message Code Field or Unform     | atted Code Field          |

|       |                                  | default = 0011            |

|       |                                  |                           |

|       |                                  |                           |

|       |                                  |                           |

|       |                                  |                           |

|       |                                  |                           |

|       | 8 (08h) – Link Partner Advertise |                           |

| met 1 | <u>6 (101</u> | <u>1) – PHY Co</u> | nfiguration  | l (0800h                                | <u>)KW</u>    |

|-------|---------------|--------------------|--------------|-----------------------------------------|---------------|

| 15-11 | PHY           | Address            |              |                                         | default = 01h |

| 10    | Fiber         | Mode               |              |                                         |               |

|       | 0             | Disable            |              |                                         | default       |

|       | 1             | Enable             |              |                                         |               |

| 9     | Cable         | е Туре             |              |                                         |               |

|       | 0             | UTP5 and S         | STP (100 ohm | ı) cable                                | default       |

|       | 1             | STP 150 oh         | m cable      |                                         |               |

| 8     | Force         | PHY in Li          | ık Good Stat | us                                      |               |

|       | 0             | Disable            |              | • • • • • • • • • • • • • • • • • • • • | default       |

|       | 1             | Enable             |              |                                         |               |

| 7     | Basel         |                    | quelch Level |                                         |               |

|       | 0             | _                  | _            |                                         | default       |

|       | 1             | _                  | (> 100 meter | /                                       |               |

| 6-5   | Progr         |                    | ED Output S  |                                         |               |

|       |               | LED0               | LED1         | LED2                                    | LED3          |

|       |               |                    |              |                                         | COLdef        |

|       |               |                    | Link/RxAct   |                                         |               |

|       |               |                    | Speed10      |                                         |               |

|       |               |                    | Link/RxAct   | Speed                                   | COL           |

| 4     | -             | ater Mode          |              |                                         |               |

|       | 0             |                    |              | •••••                                   | default       |

| _     | 1             | Enable             |              |                                         |               |

| 3     |               | rupt Select        |              |                                         | 1.0.1.        |

|       | 0             |                    | _            |                                         | default       |

| •     | 1             |                    | rupt on MDIC |                                         | <b>D</b> O    |

| 2     | -             |                    |              |                                         | RO            |

|       | 0             |                    | •••••        | •••••                                   | default       |

|       | 1             | Enable             |              |                                         |               |

| Offset 1 | 7 (11h) – PHY Configuration 2 (F7FFh)             | RW    |

|----------|---------------------------------------------------|-------|

| 15       | Jabber Detect                                     |       |

|          | 0 Disable                                         |       |

|          | 1 Enable <b>de</b>                                | fault |

| 14       | Signal Quality Error Detect                       |       |

|          | 0 Disable                                         |       |

|          | 1 Enable <b>de</b>                                | fault |

| 13       | <b>Auto-Polarity Correction</b>                   |       |

|          | 0 Disable                                         |       |

|          | 1 Enable <b>de</b>                                | fault |

| 12       | Far End Fault Detect                              |       |

|          | 0 Disable                                         |       |

|          | 1 Enable <b>de</b>                                | fault |

| 11       | Change Seed Self Clea                             | ring  |

|          | 0 Disablede                                       | fault |

|          | 1 Enable                                          |       |

| 10-0     | Seeddefault = 7                                   | 7FFh  |

| Offset 1 | 8 (12h) – PHY Configuration 3 (0800h)             | RW    |

| 15       | Bypass Scrambler and Descrambler Functions        |       |

| 10       | 0 Disable                                         |       |

|          | 1 Enable                                          |       |

| 14       | <b>Bypass 4B5B Encoding and Decoding Functio</b>  | ns    |

|          | 0 Disablede                                       |       |

|          | 1 Enable                                          |       |

| 13       | <b>Bypass Symbol Alignment Function</b>           |       |

|          | 0 Disablede                                       | fault |

|          | 1 Enable                                          |       |

| 12       | <b>Bypass NRZI Encoding and Decoding Function</b> | ns    |

|          | 0 Disablede                                       | fault |

|          | 1 Enable                                          |       |

| 11       | Loss Sync Function Self Clea                      | ring  |

|          | 0 Disable                                         |       |

|          | 1 Enablede                                        | fault |

| 10       | <b>Lost Sync Timer Select</b>                     |       |

|          | 0 722 usecde                                      | fault |

|          | 1 2 msec                                          |       |

| 9-0      | Reservedalways rea                                | ads 0 |

| Offset | 19 (13h) – PHY Configuration 4 (FFFCh)RW                               | Offset | 20 (14h) – PHY Status (0000h)RC                                       |

|--------|------------------------------------------------------------------------|--------|-----------------------------------------------------------------------|

| 15     | Mask Interrupt Function                                                | 15     | Polarity Inversion Base10-Tx                                          |

|        | 0 Disable                                                              |        | 0 Disabledefaul                                                       |

|        | 1 Enabledefault                                                        |        | 1 Enable                                                              |

| 14     | Mask Interrupt on Link-Up Status                                       | 14     | Link Up StatusLH, default = (                                         |

|        | 0 Disable                                                              |        | •                                                                     |

|        | 1 Enabledefault                                                        |        |                                                                       |

| 13     | Mask Interrupt on Link-Fail Status                                     | 13     | Link Fail Status LL, default = (                                      |

|        | 0 Disable                                                              |        |                                                                       |

|        | 1 Enabledefault                                                        |        |                                                                       |

| 12     | Mask Interrupt on Link Status Change                                   | 12     | Link Statusdefault = (                                                |

|        | 0 Disable                                                              |        |                                                                       |

|        | 1 Enabledefault                                                        |        |                                                                       |

| 11     | Mask Interrupt on Auto-Negotiation Process                             | 11     | <b>Auto-Negotiation Process Complete</b> default = (                  |

|        | Complete                                                               |        |                                                                       |

|        | 0 Disable                                                              |        |                                                                       |

|        | 1 Enabledefault                                                        |        |                                                                       |

| 10     | Mask Interrupt on Page Received in Auto-                               | 10     | Page Received in Auto-Negotiation Process                             |

|        | Negotiation Process                                                    |        | LH, default = 0                                                       |

|        | 0 Disable                                                              |        |                                                                       |

|        | 1 Enabledefault                                                        |        |                                                                       |

| 9      | Mask Interrupt on Jabber Condition Detect                              | 9      | <b>Jabber Condition Detect</b> LH, default = 0                        |

|        | 0 Disable                                                              |        |                                                                       |

|        | 1 Enabledefault                                                        |        |                                                                       |

| 8      | Mask Interrupt on Invalid Symbol Received                              | 8      | <b>Error Code Symbol Received</b> LH, default = 0                     |

|        | 0 Disable                                                              |        |                                                                       |

|        | 1 Enabledefault                                                        |        |                                                                       |

| 7      | Mask Interrupt on SSD Delimiter Error Detected                         | 7      | Start of Stream Delimiter ErrorLH, default = 0                        |

|        | 0 Disable                                                              |        |                                                                       |

| _      | 1 Enabledefault                                                        | _      |                                                                       |

| 6      | Mask Interrupt on ESD Delimiter Error Detected                         | 6      | End of Stream Delimiter ErrorLH, default = 0                          |

|        | 0 Disable                                                              |        |                                                                       |

| _      | 1 Enabledefault                                                        | _      |                                                                       |

| 5      | Mask Interrupt on Signal Quality Error Detected                        | 5      | <b>Signal Quality Error Detected</b> LH, default = 0                  |

|        | 0 Disable                                                              |        |                                                                       |

|        | 1 Enabledefault                                                        | 4      | TILE TO A DATE AND THE                                                |

| 4      | Mask Interrupt on Link Fail Counter in Rx15                            | 4      | Link Fail Counter in Rx15 Count to Max                                |

|        | Count to Max 0 Disable                                                 |        | LH, default = 0                                                       |

|        |                                                                        |        |                                                                       |

| 2      | 1 Enable default                                                       | 2      | Invalid Symbol Dessived Country in Dv16 Coun                          |

| 3      | Mask Interrupt on Invalid Symbol Received Counter in Rx16 Count to Max | 3      | Invalid Symbol Received Counter in Rx16 Counter to MaxLH, default = 0 |

|        | 0 Disable                                                              |        | to waxEn, default – (                                                 |

|        | 1 Enabledefault                                                        |        |                                                                       |

| 2      | Mask Interrupt on False Carrier Counter in Rx17                        | 2      | False Carrier Counter in Rx17 Count to Max                            |

|        | Count to Max                                                           | 2      | LH, default = (                                                       |

|        | 0 Disable                                                              |        | Lii, delauit – (                                                      |

|        | 1 Enabledefault                                                        |        |                                                                       |

| 1-0    | Reserved always reads 0                                                | 1      | PHY Speed Statusdefault = 0                                           |

|        | at way o found o                                                       | 0      | PHY Duplex Statusdefault = (                                          |

|        |                                                                        | U      | Duples Seuces delault                                                 |

| Offset 23 (17h) – False Carrier / SQE Counter (0000h). RO |

|-----------------------------------------------------------|

|                                                           |

| <u>Speed 100</u>                                          |

| <b>15-0</b> False Carrier Count default = 0               |

| Speed 10                                                  |

| 15-0 SQE Detect Countdefault = 0                          |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

| ffset 26 (1Ah) - PHY Test Configuration 1 (0012h) RV | Offset 27 (1Bh) – PHY Test Configuration 2 (C500h) RW |

|------------------------------------------------------|-------------------------------------------------------|

| 15 PHY Capability to Set Baseline Wande              | r 15 10 Squelch Signals Debounce                      |

| <b>Correction Circuit Correction Amount</b>          | 0 Disable                                             |

| 0 Disabledefaul                                      | lt 1 Enabledefault                                    |

| 1 Enable                                             | 14 10 Squelch Signals Go Idle State Debounce          |

| 14-9 Baseline Wander Correction Circuit Value        | 0 Disable                                             |

| 8 PHY Capability to Read Baseline Wande              | r 1 Enabledefault                                     |

| <b>Correction Circuit Correction Amount</b>          | 13 10 Squelch Signals Idle Condition Select def = 0   |

| 0 Disabledefaul                                      | lt 12 NLP Pulse Length                                |

| 1 Enable                                             | 0 100 nsdefault                                       |

|                                                      | 1 150 ns                                              |

| 7 Baseline Wander Upper Limit Overflow               | w 11 Force Transmit Data                              |

| IndicationLI                                         | H 0 Disabledefault                                    |

| 0 Disabledefaul                                      | lt 1 Enable                                           |

| 1 Enable                                             | 10 NLP Watchdog                                       |

| 6 Baseline Wander Lower Limit Overflow               | w 0 Disable                                           |

| IndicationLI                                         | H 1 Enable (10 will go Link Fail if too many          |

| 0 Disabledefaul                                      | TIET S TOUTH OF IN THE OF                             |

| 1 Enable                                             | Status)default                                        |

|                                                      | 9 Set Rx21-23 MIB Counters to FFFEh                   |

| 5-4 FTxD10, FTxData10En Clock Phase Selection        | 0 Disabledefault                                      |

| default = 01                                         | b 1 Enable Self Clearing                              |

|                                                      | 8 10 Stop Receive Data if Squelch Signals Go Idle     |

| 3 Drive Kill Pattern Mode                            | State                                                 |

| 0 Disabledefaul                                      |                                                       |

| 1 Enable                                             | 1 Enabledefault                                       |

|                                                      | 7 Drive Overshoot Pattern for 100 Characterization    |

| 2 Asynchronous Baseline Wander Correction            | 0 Disabledefault                                      |

| 0 Disabledefaul                                      | lt 1 Enable                                           |

| 1 Enable                                             | 6 Fast Drive NLP Pattern for 10 Characterization      |

| 1-0 Asynchronous Baseline Wander Correction Peal     |                                                       |

| Detection Threshold default = 10                     |                                                       |

|                                                      | 5 F Direct Drive (See Bits 0-4)                       |

|                                                      | 0 Disabledefault                                      |

1 Enable

(bit-5) is Set

5) is Set

3-0

Replacement Value for TXER if FDirectDrive

Replacement Value for TXD if FDirectDrive (bit-

| Offset 2 | 8 (1Ch) – PHY Test Configuration 3 (0208h)RW          | Offset 2                             | 29 (1Dh) – PHY Test Configuration 4 (0030h) RW                                                                                 |

|----------|-------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 15       | <b>Hold DPLL Phase Setting</b>                        | 15                                   | Hold Adeq Operation, Keep Current Equalizer                                                                                    |

|          | 0 Disabledefault                                      |                                      | Gain Setting                                                                                                                   |

|          | 1 Enable                                              |                                      | 0 Disabledefault                                                                                                               |

| 14-10    | <b>DPLL Clock Phase Setting</b> default = 0           |                                      | 1 Enable                                                                                                                       |

| 9-8      | <b>DPLL Low Pass Filter Bandwidth</b> default = 10b   | 14-9                                 | •                                                                                                                              |

| 7        | Output DPLL Recovered Clock Phase to PHY              | 8                                    | Adeq Can Output Gain Setting                                                                                                   |

|          | 0 Disabledefault                                      |                                      | 0 Disabledefault                                                                                                               |

|          | 1 Enable                                              |                                      | 1 Enable                                                                                                                       |

| 6        | PHY Set DPLL Phase Capability                         | 7                                    | PHY Can Set Adeq Gain Amount                                                                                                   |

|          | 0 Disabledefault                                      |                                      | 0 Disabledefault                                                                                                               |

| _        | 1 Enable                                              |                                      | 1 Enable                                                                                                                       |

| 5        | DPLL Loopback Mode                                    | 6-5                                  | Adeq Low Pass Filter Bandwidth default = 01b                                                                                   |

|          | 0 Disabledefault                                      | 4                                    | Adeq Test Buffers AOP1/AON1, AOP2/AON2                                                                                         |

|          | 1 Enable                                              |                                      | 0 Disable                                                                                                                      |

| 4        | Rd100, Rd10 Output to PHY  0 Disabledefault           | 2.2                                  | 1 Enable                                                                                                                       |

|          | 0 Disabledefault<br>1 Enable                          | 3-2                                  | Adeq Clock Setting for 100BaseT Adaptive                                                                                       |