## TCD6000

# 6 CHANNEL CLASS-T DIGITAL AUDIO PROCESSOR USING DIGITAL POWER PROCESSING<sup>™</sup> TECHNOLOGY

Technical Information – Preliminary

Revision 1.0 – September 2004

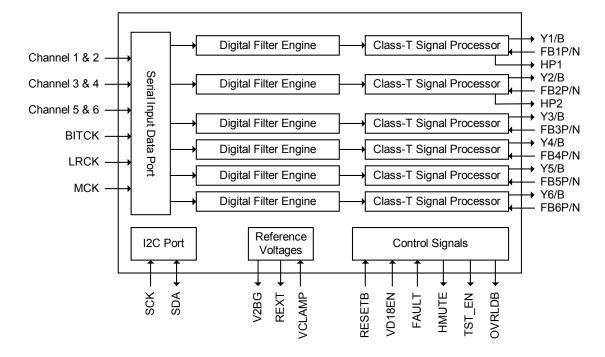

## **General Description**

The TCD6000 is a high-performance 6-channel digital audio amplifier processor. It receives 6 digital audio channels (3 pairs) and outputs 6 complementary single-bit digital data streams suitable for driving Tripath or other switching output stages.

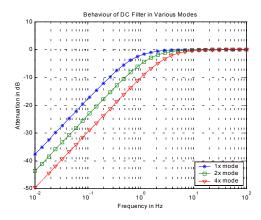

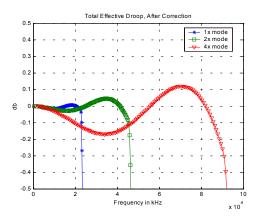

The TCD6000 accepts data at audio sample rates ranging from 32kHz to 192kHz and incorporates digital interpolation and sigma-delta conversion to produce streamed digital output signals. When combined with switching output stages, the TCD6000 allows the implementation of a complete digital audio system incorporating Class-T Digital Audio Amplification.

### Features

- Class-T architecture combining ultra-low distortion with high efficiency

- Inputs support I<sup>2</sup>S and other PCM audio formats

- Up to 24-bit resolution (16, 18, 20, and 24 bit)

- 104dB dynamic range

- THD+N less than 0.03%

- Input sampling rates up to 192kHz

- I<sup>2</sup>C compatible interface

- Stereo headphone amplifier

- Predictive Gain Control

- Digital volume control

- 128dB range

- 1/2 dB step size in 1/8 dB increments

- Zero crossing detection for click free transitions

- Optional mute mode leaves headphone amplifiers operating

- Automatic DC offset cancellation

- 130uV noise floor (PGC = 1/8, low post gain)

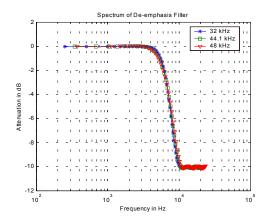

- Digital de-emphasis filtering for 32, 44.1 and 48kHz sampling rates

## **Absolute Maximum Ratings**

| SYMBOL             | PARAMETER                                                                | Min  | Max      | UNITS |

|--------------------|--------------------------------------------------------------------------|------|----------|-------|

| VD33               | 3.3V Digital Power Supply                                                | -0.3 | 4.0      | V     |

| VA33               | 3.3V Analog Power Supply                                                 | -0.3 | 4.0      | V     |

| VA50               | 5V Analog Power Supply                                                   | -0.3 | 6.0      | V     |

| Vlogic3            | Input Logic Level (DATAx, MCK, BITCLK, LRCLK, SCK,<br>SDA, RESET, ADDRx) | -0.3 | VD33+0.3 | V     |

| Vin5               | Input Level (VCLAMP, FBxx, FAULT)                                        | -0.3 | VD50+0.3 |       |

| ТА                 | Operating Free-air Temperature Range                                     | -40  | 85       | °C    |

| T <sub>STORE</sub> | Storage Temperature Range                                                | -55  | 150      | °C    |

| T <sub>JMAX</sub>  | Maximum Junction Temperature                                             |      | 150      | °C    |

| ESD <sub>HB</sub>  | ESD Susceptibility – Human Body Model (Note 2) All pins                  |      | 2000     | V     |

| ESD <sub>MM</sub>  | ESD Susceptibility – Machine Model (Note 3) All pins                     |      | 200      | V     |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

See the table below for Operating Conditions.

Note 2: Human body model, 100pF discharged through a 1.5K $\!\Omega$  resistor.

Note 3: Machine model, 220pF – 240pF discharged through all pins.

## Recommended Operating Conditions (Note 4)

| SYMBOL            | PARAMETER                   | MIN | TYP | MAX  | UNITS |

|-------------------|-----------------------------|-----|-----|------|-------|

| VA50              | 5V Analog Power Supply      | 4.5 | 5   | 5.5  | V     |

| VA33              | 3.3V Analog Power Supply    | 3.0 | 3.3 | 3.6  | V     |

| VD33              | 3.3V Digital Power Supply   | 3.0 | 3.3 | 3.6  | V     |

| V <sub>HI-3</sub> | Vlogic3 Input High          | 2.1 |     | VD33 | V     |

| V <sub>LO-3</sub> | Vlogic3 Input Low           | 0   |     | 0.8  | V     |

| T <sub>A</sub>    | Operating Temperature Range | -40 | 25  | 85   | С     |

Note 4: Recommended Operating Conditions indicate conditions for which the device is functional. See Digital, Analog, and Switching Characteristics for guaranteed specific performance limits.

## **Power and Thermal Characteristics**

$T_A$  = 25 °C. See Application/Test Circuit on page 8.

| SYMBOL          | PARAMETER                                           | CONDITIONS                                | MIN | TYP | MAX | UNITS |

|-----------------|-----------------------------------------------------|-------------------------------------------|-----|-----|-----|-------|

| PTOTAL          | Total Power Dissipation                             | VA50 = 5.0V<br>VA33 = 3.3V<br>VD33 = 3.3V |     | 880 |     | mW    |

| IA50            | VA50 Power Supply Current                           | VA50 = 5.0V                               |     | 65  | 90  | mA    |

| IA33            | VA33 Power Supply Current                           | VA33 = 3.3V                               |     | 50  |     | mA    |

| ID33            | VD33 Power Supply Current                           | VD33 = 3.3V                               |     | 20  |     | mA    |

| 133             | Combined VD33+VA33 Power Supply<br>Current (Note 5) | VD33 = 3.3V<br>VA33 = 3.3V                |     |     | 100 | mA    |

| θ <sub>JA</sub> | Junction-to-ambient Thermal Resistance (still air)  |                                           |     | 35° |     | C/W   |

Note 5: Separate IA33 and ID33 maximums are not tested.

## **Digital Characteristics**

| T <sub>A</sub> = 25 °C. Unless otherwise noted, the MCK frequency is 12.288 | 8. See Application/Test Circuit on page 8. |

|-----------------------------------------------------------------------------|--------------------------------------------|

|-----------------------------------------------------------------------------|--------------------------------------------|

| SYMBOL               | PARAMETER                      | CONDITIONS                           | MIN  | TYP | MAX  | UNITS |

|----------------------|--------------------------------|--------------------------------------|------|-----|------|-------|

| V <sub>IH33</sub>    | High-Level Input Voltage       | VD33 = 3.3V                          | 2.1  |     |      | V     |

| V <sub>IL33</sub>    | Low-Level Input Voltage        | VD33 = 3.3V                          |      |     | 0.8  | V     |

| FAULT <sub>IH5</sub> | FAULT High-Level Input Voltage | VA50 = 5.0V                          | 3.5  |     |      | V     |

| FAULT <sub>IL5</sub> | FAULT Low-Level Input Voltage  | VA50 = 5.0V                          |      |     | 0.8  | V     |

| FAULT <sub>OFF</sub> | FAULT Off Input Voltage        | VA50 = 5.0V                          | 2    |     | 3    | V     |

| V <sub>OH33</sub>    | High-Level Output Voltage      | VD33 = 3.0V, I <sub>OL</sub> = -50uA | 2.9  |     |      | V     |

|                      |                                | VD33 = 3.0V, I <sub>OL</sub> = -4mA  | 2.48 |     |      | V     |

| V <sub>OH5</sub>     | High-Level Output Voltage      | VA50 = 4.5V, I <sub>OL</sub> = -50uA | 4.4  |     |      | V     |

|                      |                                | VA50 = 4.5V, I <sub>OL</sub> = -8mA  | 3.8  |     |      | V     |

| V <sub>OL33</sub>    | Low-Level Output Voltage       | VD33 = 3.0V, I <sub>OL</sub> = 50uA  |      |     | 0.1  | V     |

|                      |                                | VD33 = 3.0V, I <sub>OL</sub> = 4mA   |      |     | 0.44 | V     |

| V <sub>OL5</sub>     | Low-Level Output Voltage       | VA50 = 4.5V, I <sub>OL</sub> = 50uA  |      |     | 0.1  | V     |

|                      |                                | VA50 = 4.5V, I <sub>OL</sub> = 8mA   |      |     | 0.44 | V     |

## **Performance Characteristics**

$T_A = 25$  °C. Unless otherwise noted, the power stage used for testing is the TP2150B, the supply voltage is VPP=|VNN|=28V, R<sub>L</sub> = 4 $\Omega$ , PGC = 1, post-gain = high, the MCK frequency is 12.288 MHz, fs = 48kHz, the input frequency is 1kHz, and the measurement bandwidth is 20kHz. See Application/Test Circuit on page 8.

| SYMBOL            | PARAMETER                                | CONDITIONS                                                                             | MIN | TYP               | MAX | UNITS          |

|-------------------|------------------------------------------|----------------------------------------------------------------------------------------|-----|-------------------|-----|----------------|

| P <sub>OUT</sub>  | Output Power<br>(continuous RMS/Channel) | THD+N = 0.1%<br>THD+N = 1.0%<br>THD+N = 10%                                            |     | 60<br>75<br>105   |     | W<br>W<br>W    |

| THD + N           | Total Harmonic Distortion Plus Noise     | P <sub>OUT</sub> = 20W/Channel                                                         |     | 0.03              |     | %              |

| IHF-IM            | IHF Intermodulation Distortion           | 19kHz, 20kHz, 1:1 (IHF),<br>P <sub>OUT</sub> = 10W/Channel                             |     | -80               |     | dB             |

| SNR               | Signal-to-Noise Ratio                    | PGC = 1, post-gain = high,<br>A Weighted,<br>P <sub>OUT</sub> = 100W/Channel           |     | 98                |     | dB             |

| CS                | Channel Separation                       | 0dBr = 10W                                                                             |     | 84                |     | dB             |

| η                 | Power Efficiency                         | Pout = 100W/Channel                                                                    |     | 87                |     | %              |

| Averror           | Channel to Channel Gain Error            | P <sub>OUT</sub> = 10W/Channel                                                         |     |                   | 0.2 | dB             |

| e <sub>NOUT</sub> | Output Noise Voltage<br>(A-Weighted)     | PGC = 1, post-gain = high<br>PGC = 1/8, post-gain = high<br>PGC = 1/8, post-gain = low |     | 260<br>150<br>130 |     | μV<br>μV<br>μV |

| VOFFSET           | Output Offset Voltage                    | After automatic DC calibration                                                         | -95 | ±40               | +95 | mV             |

## **Switching Characteristics**

$T_A$  = 25 °C. Unless otherwise noted, the MCK frequency is 12.288 MHz and the measurement bandwidth is 20kHz. See Application/Test Circuit on page 8.

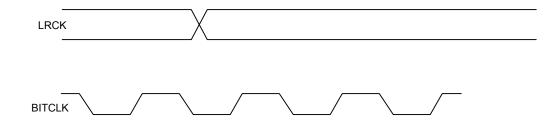

| SYMBOL                                                                 | PARAMETER                                                                                                                                                  | CONDITIONS | MIN                         | TYP                    | MAX         | UNITS                                  |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------|------------------------|-------------|----------------------------------------|

| fMCK                                                                   | Master Clock Timing<br>Frequency<br>Duty Cycle                                                                                                             |            | 8.192<br>40                 |                        | 24.56<br>60 | MHz<br>%                               |

| fLRCK                                                                  | Left-Right Clock Timing<br>1X Mode<br>2X Mode<br>4X Mode                                                                                                   |            | 32                          | 44.1<br>96<br>192      | 48          | KHz<br>KHz<br>kHz                      |

| tBITCK                                                                 | Serial Interface Timing<br>BITCK period<br>1X Mode<br>2X Mode<br>4X Mode                                                                                   |            | 488.2                       | 354.3<br>177.1<br>88.6 | 325.5       | ns<br>ns<br>ns                         |

| tSCK<br>tSCKL<br>tSCKH<br>tSDAset<br>tSDAhold<br>tSDA rise<br>tSDAfall | Control Interface Timing<br>SCK Period<br>SCK Pulse Width Low<br>SCK Pulse Width High<br>SDA Setup Time<br>SDA Hold Time<br>SDA Rise Time<br>SDA Fall Time |            | 200<br>80<br>80<br>40<br>40 |                        | 20<br>20    | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns |

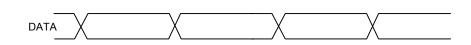

## **TCD6000 Pin Layout**

## **TCD6000 Pin Description**

| Pin      | Function  | Туре                               | Description                                                              |

|----------|-----------|------------------------------------|--------------------------------------------------------------------------|

| 1        | FB2P      | Input                              | Switching feedback                                                       |

| 2        | GA        | Ground                             | Analog Ground                                                            |

| 3        | FB2N      | Input                              | Switching feedback                                                       |

| 4        | NC        | Not connected internally           | must be kept floating                                                    |

| 5        | NC        | Not connected internally           | must be kept floating                                                    |

| 6        | NC        | Not connected internally           | must be kept floating                                                    |

| 7        | FB3N      | Input                              | Switching feedback                                                       |

| 8        | FB3P      | Input                              | Switching feedback                                                       |

| 9        | FAULT     | Input                              | 3-level digital input to detect power stage fault condition              |

| 10       | FB4N      | Input                              | Switching feedback                                                       |

| 11       | FB4P      | Input                              | Switching feedback                                                       |

| 12       | HMUTE     | 5V Logic Output                    | Digital output – indicates processor channels are muted                  |

| 13       | FB5N      | Input                              | Switching feedback                                                       |

| 14       | FB5P      | Input                              | Switching feedback                                                       |

| 15       | TST_EN    | 5V Logic Output                    | Digital output to put power stage in to test mode                        |

| 16       | FB6N      | Input                              | Switching feedback                                                       |

| 17       | FB6P      | Input                              | Switching feedback                                                       |

| 18       | NC        | Not connected internally           | must be kept floating                                                    |

| 19       | OVRLDB    | 5V Logic Output                    | Digital output – indicates that one or more channels are near saturation |

| 20       | Y1        | 5V Logic Output                    | Switching modulator output                                               |

| 21       | Y1B       | 5V Logic Output                    | Switching modulator output                                               |

| 22       | Y2        | 5V Logic Output                    | Switching modulator output                                               |

| 23       | Y2B       | 5V Logic Output                    | Switching modulator output                                               |

| 24       | NC        | Not connected internally           | must be kept floating                                                    |

| 25       | NC        | Not connected internally           | must be kept floating                                                    |

| 26       | NC        | Not connected internally           | must be kept floating                                                    |

| 27       | NC        | Not connected internally           | must be kept floating                                                    |

| 28       | NC        | Not connected internally           | must be kept floating                                                    |

| 29       | GA        | Ground                             | Analog Ground                                                            |

| 30<br>31 | Y3        | 5V Logic Output                    | Switching modulator output                                               |

| 31       | Y3B<br>Y4 | 5V Logic Output<br>5V Logic Output | Switching modulator output<br>Switching modulator output                 |

| 33       | Y4B       | 5V Logic Output                    | Switching modulator output                                               |

| 34       | VA50      | Power                              | 5V analog power supply                                                   |

| 35       | GA        | Ground                             | Analog ground                                                            |

| 36       | Y5        | 5V Logic Output                    | Switching modulator output                                               |

| 37       | Y5B       | 5V Logic Output                    | Switching modulator output                                               |

| 38       | Y6        | 5V Logic Output                    | Switching modulator output                                               |

| 39       | Y6B       | 5V Logic Output                    | Switching modulator output                                               |

| 40       | NC        | Not connected internally           | must be kept floating                                                    |

| 41       | NC        | Not connected internally           | must be kept floating                                                    |

| 42       | GA        | Ground                             | Analog ground                                                            |

| 43       | VA33      | Power                              | 3.3V analog power supply                                                 |

| 44       | VA33      | Power                              | 3.3V analog power supply                                                 |

| 45       | NC        | Not connected internally           | must be kept floating                                                    |

| 46       | GA        | Ground                             | Analog ground                                                            |

| 47       | GA        | Ground                             | Analog ground                                                            |

| 48       | GD        | Ground                             | Digital Ground                                                           |

| 49       | VD18CAP   | Output                             | Decoupling point for internal 1.8V regulator                             |

| 50       | VD33      | Power                              | 3.3V digital power supply                                                |

| 51       | TEST      | Float                              | Test pin – must be kept floating                                         |

| 52       | NC        | Not connected internally           | must be kept floating                                                    |

| 53       | NC        | Not connected internally           | must be kept floating                                                    |

| 54       | NC        | Not connected internally           | must be kept floating                                                    |

| 55       | NC        | Not connected internally           | must be kept floating                                                    |

| 56       | GA        | Power                              | Analog ground                                                            |

| 57       | GA        | Power                              | Analog ground                                                            |

| 58       | TEST      | Float                              | Test pin – must be kept floating                                         |

| 59       | TEST      | Float                              | Test pin – must be kept floating                                         |

| 60       | GD        | Ground                             | Digital ground                                                           |

| 61       | MCK       | 3.3V Logic Input                   | Master clock digital input                                               |

| 62       | SCK       | 3.3V Logic Input                   | I <sup>2</sup> C clock input                                             |

| 63       | SDA       | 3.3V Logic Input                   | I <sup>2</sup> C serial data input                                       |

#### Tripath Technology, Inc. – Preliminary Technical Information

| 64 DATA12 3.3V Logic Input PCM audio input for channels 1 and 2   65 DATA34 3.3V Logic Input PCM audio input for channels 3 and 4   66 DATA56 3.3V Logic Input PCM audio input for channels 5 and 6   67 BITCK 3.3V Logic Input PCM audio input for channels 5 and 6   68 LRCK 3.3V Logic Input PCM audio input for channels 5 and 6   69 VD18EN 3.3V Logic Input PCM audio input for channels 6   70 RESETB 3.3V Logic Input Test mode enable – must be kept grounded   71 TESTMODE 3.3V Logic Input Chip address select 2   73 TEST Float Test pin – must be kept floating   74 ADDR1 3.3V Logic Input Chip address select 1   75 GD Ground Digital ground   76 RA Nc toonnected internally must be kept floating   78 NC Not connected internally must be kept floating   78 NC Not connected internally must be kept floating   81 TEST                                                                                                                                                                                                                              |     |          |                          |                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|--------------------------|---------------------------------------------------------------------|

| 66 DATA56 3.3V Logic Input PCM audio input for channels 5 and 6   67 BITCK 3.3V Logic Input PCM audio bit clock input   68 LRCK 3.3V Logic Input PCM audio bit clock input   69 VD18EN 3.3V Logic Input PCM audio bit forking to clock input   69 VD18EN 3.3V Logic Input Reset input - resets internal registers   71 TESTMODE 3.3V Logic Input Test mode enable - must be kept grounded   72 ADDR2 3.3V Logic Input Chip address select 2   73 TEST Float Test pin - must be kept floating   74 ADDR1 3.3V Logic Input Chip address select 1   75 GD Ground Digital ground   76 GA Ground Analog ground   77 NC Not connected internally must be kept floating   78 NC Not connected internally must be kept floating   79 TEST Float Test pin - must be kept floating   81 TEST Float Test pin - must be ke                                                                                                                                                                                                                                                           | 64  | DATA12   | 3.3V Logic Input         | PCM audio input for channels 1 and 2                                |

| 67 BITCK 3.3V Logic Input PCM audio bit clock input   68 LRCK 3.3V Logic Input PCM audio left/right clock input   69 VD18EN 3.3V Logic Input 1.8V internal regulator enable   70 RESETB 3.3V Logic Input Test mode enable – must be kept grounded   71 TESTMODE 3.3V Logic Input Test mode enable – must be kept grounded   72 ADDR2 3.3V Logic Input Chip address select 2   73 TEST Float Test mode enable – must be kept floating   74 ADDR1 3.3V Logic Input Chip address select 1   75 GD Ground Digital ground   76 GA Ground Malog ground   77 NC Not connected internally must be kept floating   79 TEST Float Test pin – must be kept floating   80 TEST Float Test pin – must be kept floating   81 TEST Float Test pin – must be kept floating   82 VD33 Power 3.3V digital power supply                                                                                                                                                                                                                                                                     | 65  | DATA34   | 3.3V Logic Input         | PCM audio input for channels 3 and 4                                |

| 68 LRCK 3.3V Logic Input PCM audio left/right clock input   69 VD18EN 3.3V Logic Input 1.8V internal regulator enable   70 RESETB 3.3V Logic Input Resterinput – resets internal registers   71 TESTMODE 3.3V Logic Input Test mode enable – must be kept grounded   72 ADDR2 3.3V Logic Input Test mode enable – must be kept floating   74 ADDR1 3.3V Logic Input Chip address select 1   75 GD Ground Digital ground   76 GA Ground Analog ground   77 NC Not connected internally must be kept floating   79 TEST Float Test pin – must be kept floating   79 TEST Float Test pin – must be kept floating   80 TEST Float Test pin – must be kept floating   81 TEST Float Test pin – must be kept floating   82 VD33 Power 3.3V digital power supply   83 VD18CAP Output Decoupling point for internal 1.                                                                                                                                                                                                                                                           | 66  | DATA56   | 3.3V Logic Input         | PCM audio input for channels 5 and 6                                |

| 69 VD18EN 3.3V Logic Input 1.8V internal regulator enable   70 RESETB 3.3V Logic Input Reset input - resets internal registers   71 TESTMODE 3.3V Logic Input Test mode enable – must be kept grounded   72 ADDR2 3.3V Logic Input Chip address select 2   73 TEST Float Test pin – must be kept floating   74 ADDR1 3.3V Logic Input Chip address select 1   75 GD Ground Digital ground   76 GA Ground Mathing   79 TEST Float Test pin – must be kept floating   79 TEST Float Test pin – must be kept floating   80 TEST Float Test pin – must be kept floating   81 TEST Float Test pin – must be kept floating   82 VD33 Power 3.3V digital power supply   83 VD18CAP Output Decoupling point for internal 1.8V regulator   84 GD Ground Analog ground   85                                                                                                                                                                                                                                                                                                        | 67  | BITCK    | 3.3V Logic Input         | PCM audio bit clock input                                           |

| 70 RESETB 3.3V Logic Input Reset input – resets internal registers   71 TESTMODE 3.3V Logic Input Test mode enable – must be kept grounded   72 ADDR2 3.3V Logic Input Test mode enable – must be kept floating   74 ADDR1 3.3V Logic Input Test pin – must be kept floating   74 ADDR1 3.3V Logic Input Chip address select 1   75 GD Ground Digital ground   76 GA Ground Analog ground   77 NC Not connected internally must be kept floating   78 NC Not connected internally must be kept floating   79 TEST Float Test pin – must be kept floating   80 TEST Float Test pin – must be kept floating   81 TEST Float Test pin – must be kept floating   82 VD18CAP Output Decoupling point for internal 1.8V regulator   84 GD Ground Analog ground   85 GA Ground Analog ground                                                                                                                                                                                                                                                                                    | 68  | LRCK     | 3.3V Logic Input         | PCM audio left/right clock input                                    |

| 71TESTMODE3.3V Logic InputTest mode enable – must be kept grounded72ADDR23.3V Logic InputChip address select 273TESTFloatTest pin – must be kept floating74ADDR13.3V Logic InputChip address select 175GDGroundDigital ground76GAGroundAnalog ground77NCNot connected internallymust be kept floating78NCNot connected internallymust be kept floating79TESTFloatTest pin – must be kept floating80TESTFloatTest pin – must be kept floating81TESTFloatTest pin – must be kept floating82VD33Power3.3V digital power supply83VD18CAPOutputDecoupling point for internal 1.8V regulator84GDGroundAnalog ground85GAGroundAnalog ground86GAGroundAnalog ground87REXTOutputAnalog current reference input – requires 10K ohms +/- 1% to GA88V2BGFILTOutputReference Voltage89VA33Power3.3V analog power supply90GAGroundAnalog ground91NCNot connected internallymust be kept floating93V2BGOutputReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output chan                                                                 | 69  | VD18EN   | 3.3V Logic Input         | 1.8V internal regulator enable                                      |

| 72ADDR23.3V Logic InputChip address select 273TESTFloatTest pin – must be kept floating74ADDR13.3V Logic InputChip address select 175GDGroundDigital ground76GAGroundAnalog ground77NCNot connected internallymust be kept floating78NCNot connected internallymust be kept floating79TESTFloatTest pin – must be kept floating80TESTFloatTest pin – must be kept floating81TESTFloatTest pin – must be kept floating82VD33Power3.3V digital power supply83VD18CAPOutputDecoupling point for internal 1.8V regulator84GDGroundAnalog ground85GAGroundAnalog gurond86CAGroundAnalog gurond87REXTOutputAnalog current reference input – requires 10K ohms +/- 1% to GA88V2BGFILTOutputAnalog ground90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallymust be kept floating93V2BGOutputAnalog ground94HP1OutputReference Voltage95HP2OutputHeadphone amplifier output channel 196GAGroundAnalog ground97VA50Power <td>70</td> <td>RESETB</td> <td>3.3V Logic Input</td> <td>Reset input – resets internal registers</td>  | 70  | RESETB   | 3.3V Logic Input         | Reset input – resets internal registers                             |

| 73TESTFloatTest pin – must be kept floating74ADDR13.3V Logic InputChip address select 175GDGroundDigital ground76GAGroundAnalog ground77NCNot connected internallymust be kept floating78NCNot connected internallymust be kept floating79TESTFloatTest pin – must be kept floating80TESTFloatTest pin – must be kept floating81TESTFloatTest pin – must be kept floating82VD33Power3.3V digital power supply83VD18CAPOutputDecouping point for internal 1.8V regulator84GDGroundAnalog ground85GAGroundAnalog ground86GAGroundAnalog ground87REXTOutputReference Voltage89VA33Power3.3V analog ground90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallymust be kept floating93V2BGOutputReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50PowerSV analog power supply98FB1PSV Logic OutputSwitching feedback </td <td>71</td> <td>TESTMODE</td> <td>3.3V Logic Input</td> <td>Test mode enable – must be kept grounded</td> | 71  | TESTMODE | 3.3V Logic Input         | Test mode enable – must be kept grounded                            |

| 74ADDR13.3V Logic InputChip address select 175GDGroundDigital ground76GAGroundAnalog ground77NCNot connected internallymust be kept floating78NCNot connected internallymust be kept floating79TESTFloatTest pin – must be kept floating80TESTFloatTest pin – must be kept floating81TESTFloatTest pin – must be kept floating82VD33Power3.3V digital power supply83VD18CAPOutputDecoupling point for internal 1.8V regulator84GDGroundAnalog ground85GAGroundAnalog ground86GAGroundAnalog ground87REXTOutputAnalog current reference input – requires 10K ohms +/- 1% to GA88V2BGFILTOutputReference Voltage89VA33Power3.3V analog ground90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallymust be kept floating93V2BGOutputReference Voltage94HP1OutputReference Voltage95HP2OutputHeadphone amplifier output channel 196GAGroundAnalog ground97VA50PowerSvandog power supply98FB1P5V Logic OutputSwit                                                                                                              | 72  | ADDR2    | 3.3V Logic Input         | Chip address select 2                                               |

| 75GDGroundDigital ground76GAGroundAnalog ground77NCNot connected internallymust be kept floating78NCNot connected internallymust be kept floating79TESTFloatTest pin – must be kept floating80TESTFloatTest pin – must be kept floating81TESTFloatTest pin – must be kept floating82VD33Power3.3V digital power supply83VD18CAPOutputDecoupling point for internal 1.8V regulator84GDGroundDigital ground85GAGroundAnalog ground86GAGroundAnalog ground87REXTOutputAnalog current reference input – requires 10K ohms +/- 1% to GA88V2BGFILTOutputReference Voltage89VA33Power3.3V analog ground91NCNot connected internallymust be kept floating92NCNot connected internallymust be kept floating93V2BGOutputReference Voltage94HP1OutputReference Voltage95HP2OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Log                                                                                                     | 73  | TEST     | Float                    | Test pin – must be kept floating                                    |

| 76GAGroundAnalog ground77NCNot connected internallymust be kept floating78NCNot connected internallymust be kept floating79TESTFloatTest pin – must be kept floating80TESTFloatTest pin – must be kept floating81TESTFloatTest pin – must be kept floating82VD33Power3.3V digital power supply83VD18CAPOutputDecoupling point for internal 1.8V regulator84GDGroundDigital ground85GAGroundAnalog ground86GAGroundAnalog ground87REXTOutputAnalog ground88V2BGFILTOutputAnalog ground89VA33Power3.3V analog power supply90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallymust be kept floating93V2BGOutputReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                                                                                       | 74  | ADDR1    | 3.3V Logic Input         | Chip address select 1                                               |

| 77NCNot connected internallymust be kept floating78NCNot connected internallymust be kept floating79TESTFloatTest pin – must be kept floating80TESTFloatTest pin – must be kept floating81TESTFloatTest pin – must be kept floating82VD33Power3.3V digital power supply83VD18CAPOutputDecoupling point for internal 1.8V regulator84GDGroundDigital ground85GAGroundAnalog ground86GAGroundAnalog ground87REXTOutputAnalog current reference input – requires 10K ohms +/- 1% to GA88V2BGFILTOutputReference Voltage89VA33Power3.3V analog power supply90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallymust be kept floating93V2BGOutputReference Voltage94HP1OutputReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 196GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                            | 75  | GD       | Ground                   | Digital ground                                                      |

| 78NCNot connected internallymust be kept floating79TESTFloatTest pin – must be kept floating80TESTFloatTest pin – must be kept floating81TESTFloatTest pin – must be kept floating82VD33Power3.3V digital power supply83VD18CAPOutputDecoupling point for internal 1.8V regulator84GDGroundDigital ground85GAGroundAnalog ground86GAGroundAnalog ground87REXTOutputReference Voltage89VA33Power3.3V analog power supply90GAGroundAnalog ground91NCNot connected internally92NCNot connected internally93V2BGOutput94HP1Output95HP2Output96GAGround97VA50Power98FB1P5V Logic Output99FB1N5V Logic Output90SAGround91ND92NC93V2BG94HP195HP296GA99FB1N5V Logic OutputSwitching feedback99FB1N5V Logic Output90Switching feedback                                                                                                                                                                                                                                                                                                                                            | 76  | GA       | Ground                   | Analog ground                                                       |

| 79TESTFloatTest pin – must be kept floating80TESTFloatTest pin – must be kept floating81TESTFloatTest pin – must be kept floating82VD33Power3.3V digital power supply83VD18CAPOutputDecoupling point for internal 1.8V regulator84GDGroundAnalog ground85GAGroundAnalog ground86GAGroundAnalog ground87REXTOutputReference Voltage89VA33Power3.3V analog power supply90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallyReference Voltage94HP1OutputReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1PSV Logic OutputSwitching feedback99FB1NSV Logic OutputSwitching feedback                                                                                                                                                                                                                                                                                                               | 77  | NC       | Not connected internally | must be kept floating                                               |

| 80TESTFloatTest pin – must be kept floating81TESTFloatTest pin – must be kept floating82VD33Power3.3V digital power supply83VD18CAPOutputDecoupling point for internal 1.8V regulator84GDGroundDigital ground85GAGroundAnalog ground86GAGroundAnalog ground87REXTOutputAnalog current reference input – requires 10K ohms +/- 1% to GA88V2BGFILTOutputReference Voltage89VA33Power3.3V analog power supply90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallymust be kept floating93V2BGOutputReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                                                                                                                                                                                                     | 78  | NC       | Not connected internally | must be kept floating                                               |

| 81TESTFloatTest pin – must be kept floating82VD33Power3.3V digital power supply83VD18CAPOutputDecoupling point for internal 1.8V regulator84GDGroundDigital ground85GAGroundAnalog ground86GAGroundAnalog ground87REXTOutputAnalog current reference input – requires 10K ohms +/- 1% to GA88V2BGFILTOutputAnalog current reference Voltage89VA33Power3.3V analog power supply90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallymust be kept floating93V2BGOutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog power supply98FB1P5V Logic OutputSV analog power supply99FB1N5V Logic OutputSwitching feedback                                                                                                                                                                                                                                                                                                                                                    | 79  | TEST     | Float                    | Test pin – must be kept floating                                    |

| 82VD33Power3.3V digital power supply83VD18CAPOutputDecoupling point for internal 1.8V regulator84GDGroundDigital ground85GAGroundAnalog ground86GAGroundAnalog ground87REXTOutputAnalog current reference input – requires 10K ohms +/- 1% to GA88V2BGFILTOutputReference Voltage89VA33Power3.3V analog power supply90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallyReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                                                                                                                                                                                                                                                                                                                            | 80  | TEST     | Float                    | Test pin – must be kept floating                                    |

| 83VD18CAPOutputDecoupling point for internal 1.8V regulator84GDGroundDigital ground85GAGroundAnalog ground86GAGroundAnalog ground87REXTOutputAnalog current reference input – requires 10K ohms +/- 1% to GA88V2BGFILTOutputReference Voltage89VA33Power3.3V analog power supply90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallyReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                | 81  | TEST     | Float                    | Test pin – must be kept floating                                    |

| 84GDGroundDigital ground85GAGroundAnalog ground86GAGroundAnalog ground87REXTOutputAnalog current reference input – requires 10K ohms +/- 1% to GA88V2BGFILTOutputReference Voltage89VA33Power3.3V analog power supply90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallymust be kept floating93V2BGOutputReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 82  | VD33     | Power                    | 3.3V digital power supply                                           |

| 85GAGroundAnalog ground86GAGroundAnalog ground87REXTOutputAnalog current reference input – requires 10K ohms +/- 1% to GA88V2BGFILTOutputReference Voltage89VA33Power3.3V analog power supply90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallymust be kept floating93V2BGOutputReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 83  | VD18CAP  | Output                   | Decoupling point for internal 1.8V regulator                        |

| 86GAGroundAnalog ground87REXTOutputAnalog current reference input – requires 10K ohms +/- 1% to GA88V2BGFILTOutputReference Voltage89VA33Power3.3V analog power supply90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallymust be kept floating93V2BGOutputReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 84  | GD       | Ground                   | Digital ground                                                      |

| 87REXTOutputAnalog current reference input - requires 10K ohms +/- 1% to GA88V2BGFILTOutputReference Voltage89VA33Power3.3V analog power supply90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallymust be kept floating93V2BGOutputReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 85  | GA       | Ground                   | Analog ground                                                       |

| 88V2BGFILTOutputReference Voltage89VA33Power3.3V analog power supply90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallymust be kept floating93V2BGOutputReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 86  |          | Ground                   |                                                                     |

| 88V2BGFILTOutputReference Voltage89VA33Power3.3V analog power supply90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallymust be kept floating93V2BGOutputReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 87  | REXT     | Output                   | Analog current reference input – requires 10K ohms +/- 1% to GA     |

| 90GAGroundAnalog ground91NCNot connected internallymust be kept floating92NCNot connected internallymust be kept floating93V2BGOutputReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 88  | V2BGFILT | Output                   | Reference Voltage                                                   |

| 91NCNot connected internallymust be kept floating92NCNot connected internallymust be kept floating93V2BGOutputReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 89  | VA33     | Power                    | 3.3V analog power supply                                            |

| 92NCNot connected internallymust be kept floating93V2BGOutputReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 90  | GA       | Ground                   | Analog ground                                                       |

| 93V2BGOutputReference Voltage94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 91  | NC       | Not connected internally | must be kept floating                                               |

| 94HP1OutputHeadphone amplifier output channel 195HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 92  | NC       | Not connected internally | must be kept floating                                               |

| 95HP2OutputHeadphone amplifier output channel 296GAGroundAnalog ground97VA50Power5V analog power supply98FB1P5V Logic OutputSwitching feedback99FB1N5V Logic OutputSwitching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | V2BG     | Output                   |                                                                     |

| 96 GA Ground Analog ground   97 VA50 Power 5V analog power supply   98 FB1P 5V Logic Output Switching feedback   99 FB1N 5V Logic Output Switching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 94  | HP1      | Output                   | Headphone amplifier output channel 1                                |

| 97 VA50 Power 5V analog power supply   98 FB1P 5V Logic Output Switching feedback   99 FB1N 5V Logic Output Switching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |          | Output                   | Headphone amplifier output channel 2                                |

| 98 FB1P 5V Logic Output Switching feedback   99 FB1N 5V Logic Output Switching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 96  | GA       | Ground                   | Analog ground                                                       |

| 99 FB1N 5V Logic Output Switching feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -   |          |                          |                                                                     |

| ······································                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | FB1P     | 5V Logic Output          | Switching feedback                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 99  | FB1N     | 5V Logic Output          | Switching feedback                                                  |

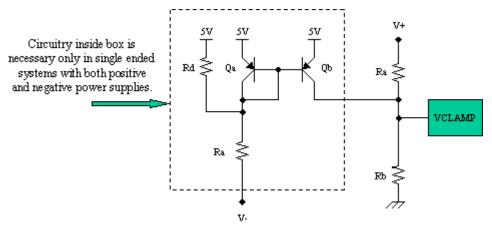

| 100 VCLAMP Input Soft clamp threshold voltage input to control audio signal clipping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 100 | VCLAMP   | Input                    | Soft clamp threshold voltage input to control audio signal clipping |

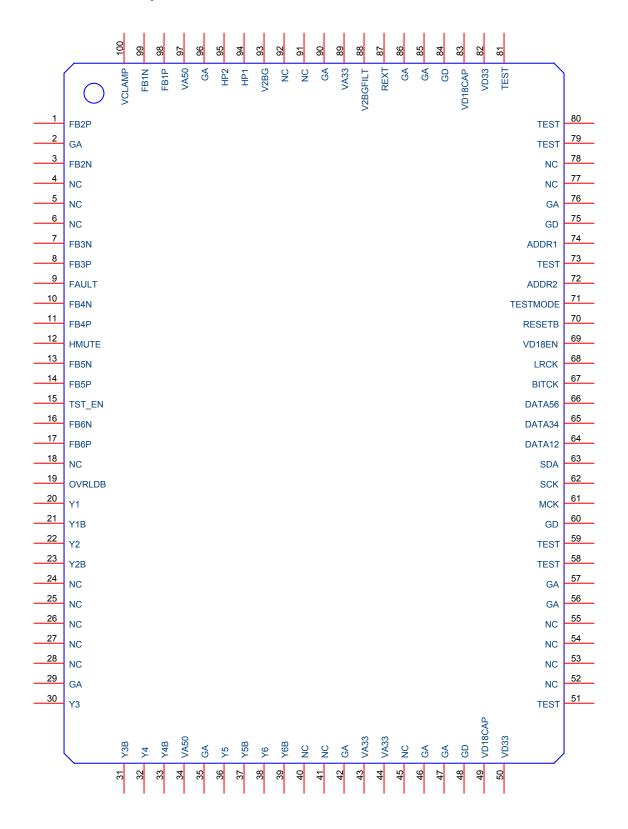

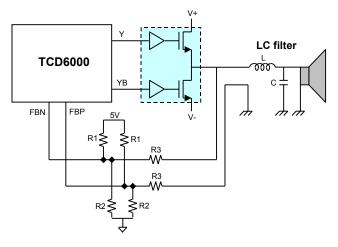

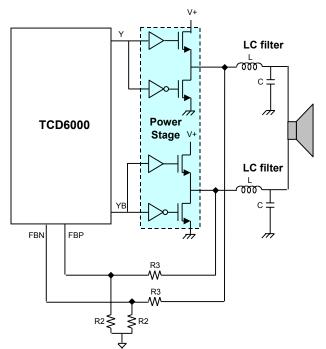

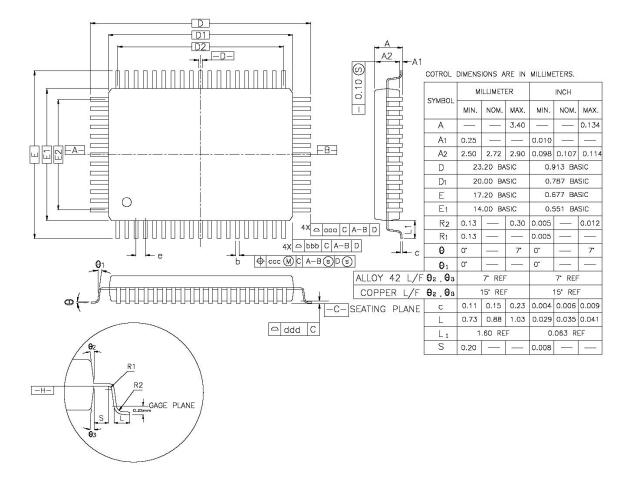

#### 5V 3.3V VA50 Cs \_\_0.1uF Cs =0.1uF 50 VD33 GA 49 VD18CAP Cs 0.1uF 5∨ 60 GD 97 VA50 3.3V Cs 0.1uF Cs 0.1uF 82 VD33 96 GA 83 VD18CAP Cs 0.1uF Y1 Y1B 21 POWER STAGE AND 75 GD FB1P FB1N FEEDBACK 99 48 GD Y2 Y2B 84 GD 3.3V POWER STAGE AND FEEDBACK FB2P FB2N 56 GA Rp Rr Y3 Y3B 3.3V 69 POWER STAGE VD18EN AND FEEDBACK FB3P FB3N 2-WIRE 62 63 SCK SDA CONTROL Y4 Y4B 33 POWER STAGE AND 74 72 ADDR1 ADDR2 ADDRESS FB4P FB4N 10 FEEDBACK 61 мск Y5 68 67 LRCK BITCK Y5B POWER STAGE PCM AUDIO SOURCE AND FB5P FB5N 64 65 FEEDBACK DATA12 13 DATA34 DATA56 66 Y6 Y6B 39 RESET POWER STAGE 70 RESETB AND FEEDBACK FB6P FB6N 3.3V 16 43 ך 100u;10V ± Cs VA33 **\_**0.1uF 46 GA 94 HP1 3.3V 95 HP2 89 VA33 100u;10V Ch 10 86 10 GA 5V 5V 0.1uF 0.1uF Rd 88 V2BGFILT Cv2bg 0.1uF QE QA Ra $\overline{\uparrow}$ 100 VCLAMP 3.3V Cs 0.1uF I+ 85 GA 0.1uF Rb Ra OVRLDB TST\_EN HMUTE 12 44 VA33 VNN FAULT DETECT FAULT 47 GA V2BG Cv2bg 0.1uF 87 71 TEST TEST TEST TEST TEST TEST TEST TESTMODE REXT ĉ 888888 Rext 10K 1% 29 29 29 29 69999 Connect ground planes at a single location near TCD6000.

## **TCD6000 Connection Diagram**

#### **TCD6000 Operation Overview**

#### POWER SUPPLY

The TCD6000 requires both 3.3V and 5V supplies. Pins labeled VD33 correspond to the digital power networks, and pins labeled VA33 and VA50 correspond to the analog power networks. All should be separately decoupled to their respective grounds.

All TCD6000 logic inputs are 3.3V unless otherwise specified.

#### VD18EN

VD18EN is a logic input that enables the internal 1.8V regulator. It should be tied to VD33.

#### REXT

The REXT pin should be connected to ground through an external  $10K\Omega$ . This connection is used by the TCD6000 as a current reference. The  $10K\Omega$  resistor must have an accuracy of +/- 1%.

#### V2BG and V2BGFILT

The V2BG and V2BGFILT pin should each be AC coupled to GA with a 0.1uF capacitor.

#### RESETB

When pulled low, the RESETB pin will force all control registers from sub-address 00h to 6Fh and 80h to EFh to their default state. Registers from sub-address 70h to 7Fh and F0h to FFh remain unchanged.

#### FAULT

The TCD6000 has no fault detection circuitry of its own. Over/under voltage, over current, and over temperature fault detection are expected to be done externally. However, a FAULT input has been provided as an alternate "mute" input. The default (non-muted) state for FAULT is "floating". The pin will self-bias to approximately 2.5V. If FAULT is taken to either 5V or 0V the TCD6000 will go in to hard mute. If FLD (register 3Ah bit D2) is set to '1', the TCD6000 will automatically un-mute after FAULT is released (forced or floated back to 2.5V). If FLD is cleared to '0', the TCD6000 will remain latched in this FAULT-based muted condition until the FAULT pin is released and FLC (register 3Ah bit D1) undergoes a '0' to '1' transition.

#### AUTOMATIC DC OFFSET CALIBRATION

When the TCD6000 comes out of hard mute (register 2Ch bit D1 transitions from '1' to '0') an automatic DC offset calibration sequence is started. During this sequence, the TCD6000 calibrates itself and its external components to minimize DC offset at the speaker outputs that can be caused by process variations and component tolerance.

The automatic DC offset calibration sequence takes a maximum of 1 second if the PGC is disabled and 4 seconds if the PGC is enabled. The additional time is required because each different amplifier gain level may require a different calibration level. Therefore, each of the four PGC levels will require calibration upon un-muting.

Automatic DC offset calibration produces 10 bit offset values for each channel that are stored in internal registers. When Automatic DC offset calibration is enabled, the 10 bit values that are in use can be read in the Calibration Readback registers (registers 02h – 09h). When the PGC is enabled, four different values are stored for each channel. The values that are seen in the Calibration Readback registers will change as the PGC Setting changes.

#### PREDICTIVE GAIN CONTROL

The Predictive Gain Control (PGC) automatically sets one of four different pre-gain levels depending on the Channel Volume level (registers 25h – 2Ah). The PGC allows less gain to be used for lower volume levels. This results in greater digital resolution and lower noise floor. When PGC is enabled (register 3Dh bit D7 is set to '1'), PGC settings are changed automatically by the Channel Volume. When PGC is disabled, the system's pre-gain level is always set to full gain.

| Channel Volume Range | PGC Setting |

|----------------------|-------------|

| FFh – F4h            | Full Gain   |

| F3h – E8h            | 1/2 Gain    |

| E7h – DCh            | 1/4 Gain    |

| DBh – 00h            | 1/8 Gain    |

#### **POST-GAIN**

When the GNn control bits are cleared to '0', the TCD6000 operates in low post-gain mode. In this mode, the noise floor is lowered but the system may not be able to obtain the maximum power output from the power stage. When the GNn control bits are set to '1', the TCD6000 operates in high post-gain mode. In this mode, gain is increased by 25% (about 2dB). The system will now be able to obtain the maximum power output from the noise floor will have increased accordingly.

The user may use low post-gain at low volume levels to take advantage of the lower noise floor and use high post-gain at higher volume levels to take advantage of the full range of the power stage. Precautions must be taken while changing post-gain to prevent DC offset. The automatic DC offset cancellation settings will have been affected by changes in post-gain. To avoid this problem, the software that is controlling the TCD6000 through the I<sup>2</sup>C port should store DC calibration values for each post-gain setting and swap between them as in the following procedure:

- 1. Set post-gain to low and channel volumes to 00h.

- 2. Un-mute.

- 3. Wait for calibration to complete.

- Read values in the "Calibration Readback" registers and write them to the "Calibration Bank" registers.

- 5. Mute.

- 6. Set post-gain to high and channel volumes to 00h.

- 7. Un-mute.

Now the calibration bank contains the DC calibration values for low post-gain and the TCD6000 has stored the DC calibration values for high post-gain in its internal registers. When the CFn bits (register 2Fh bits D5..D0) are set to '1', the values stored in the Calibration Bank are used. When the CFn bits are cleared to '0', the internal registers that hold the automatic DC calibration values for high post-gain are used. If the PGC is enabled, the software should only switch between low and high post-gain modes when the PGC is in 1/8 Gain mode. This is because the values stored in the Calibration Bank will only be valid for the PGC mode that was in effect when the channel volumes were set to 00h and automatic DC calibration took place.

Special care should be taken when using this scheme to prevent events from interfering with DC calibration. FAULT should be latched so that a proper calibration can take place during un-mute. Clocks should be kept synchronized to prevent Sync Reset.

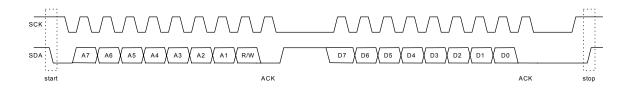

#### I<sup>2</sup>C INTERFACE

The  $I^2C$  interface is a simple bi-directional bus interface for allowing a microcontroller to read and write control registers in the TCD6000. Every component hooked up to the  $I^2C$  bus has its own unique address whether it is a CPU, memory or some other complex function chip. Each of these chips can act as a receiver and/or transmitter depending on its functionality. The TCD6000 acts as a slave while a microcontroller would act as a master.

The TCD6000 device address is 80h, 82h, 84h, or 86h depending on the state of the ADDRn pins. The TCD6000 constantly monitors the I<sup>2</sup>C data input and waits until its device address appears before writing into or reading from its control registers. The 8<sup>th</sup> bit of the address determines whether the master is reading

or writing. When the last bit is HIGH, the master is reading from a register on the slave. When the last bit is LOW, the master is writing to a register on the slave.

| ADDR2 | ADDR1 | TCD6000 write | TCD6000 read |

|-------|-------|---------------|--------------|

|       |       | address       | address      |

| 0     | 0     | 80h           | 81h          |

| 0     | 1     | 82h           | 83h          |

| 1     | 0     | 84h           | 85h          |

| 1     | 1     | 86h           | 87h          |

The I<sup>2</sup>C interface consists of a serial data input (SDA) and a clock input (SCK) and is capable of both reading and writing. Both SCK and SDA are bidirectional lines connected to VD33 via a pull-up resistor. When the bus is free both lines are HIGH.

The SCK clock frequency is typically less than 400 kHz. Data is transmitted serially in groups of 8 bits, followed by an acknowledge bit. The data on the SDA line is expected to be stable while SCK is HIGH.

A START condition is defined as a HIGH to LOW transition on the data line while the SCL line is held HIGH. After this has been transmitted by the master, the bus is considered busy. The next byte of data transmitted after the start condition contains the address of the slave in the first 7 bits and the eighth bit tells whether the master is receiving data from the slave or transmitting data to the slave. When an address is sent, each device in the system compares the first seven bits after a start condition with its address. If they match, the device considers itself addressed by the master. Data transfer with acknowledge is obligatory. The transmitter must release the SDA line during the acknowledge pulse. The receiver must then pull the data line LOW so that it remains stable low during the HIGH period of the acknowledge clock pulse. A receiver which has been addressed is obliged to generate an acknowledge after each byte of data has been received. The receiver can hold the SCK line LOW after an acknowledge to force the transmitter to wait until the receiver is ready to accept another byte.

When addressed as a slave, the following protocol must be adhered to, once a slave acknowledge has been returned, an 8-bit sub-address will be transmitted. If the LSB of the slave address was '1', a repeated START condition will have to be issued after the address byte; if the LSB is '0' the master will transmit to the slave with direction unchanged.

When the master writes data to the slave, the following events occur:

- 0. SDA and SCK are both HIGH.

- 1. A start condition is generated when the master pulls SDA LOW.

- 2. The master begins toggling SCK and transmits the slave's device address on SDA with a 0 in the LSB (ex. 80h).

- 3. On the ninth SCK pulse, the master releases SDA and the slave acknowledges by pulling SDA LOW.

- 4. The slave holds SCK low until it is ready to receive the next byte.

- 5. The slave releases SCK and the master begins toggling SCK and transmits the control register address on SDA.

- 6. On the ninth SCK pulse, the master releases SDA and the slave acknowledges by pulling SDA LOW.

- 7. The slave holds SCK low until it is ready to receive the next byte.

- 8. The slave releases SCK and the master begins toggling SCK and transmits the data byte on SDA.

- 9. On the ninth SCK pulse, the master releases SDA and the slave acknowledges by pulling SDA LOW.

- 10. The slave holds SCK low until it is ready to receive the next byte.

- 11. To transmit additional data bytes, repeat steps 8 through 10.

- A stop condition is generated when SCK is released and SDA goes HIGH while SCK is still high.

When the master reads data from the slave, the following events occur:

- 0. SDA and SCK are both HIGH.

- 1. A start condition is generated when the master pulls SDA LOW.

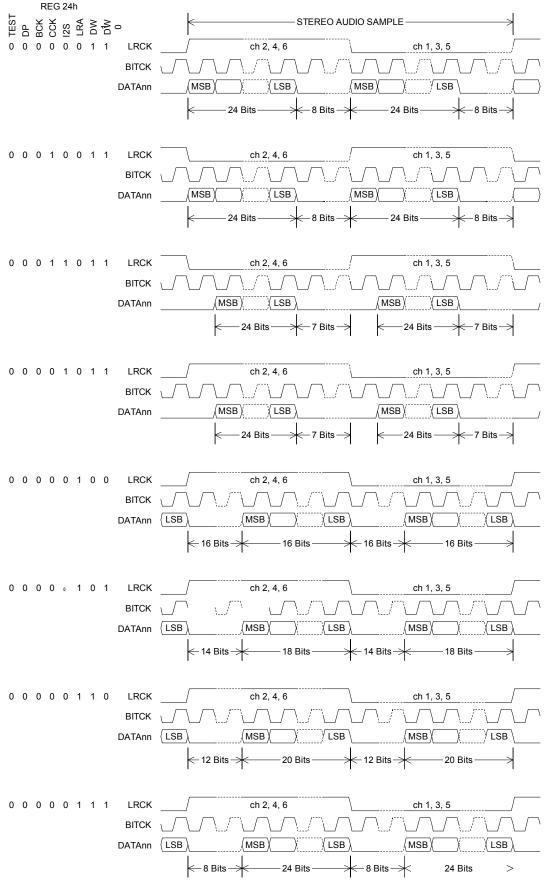

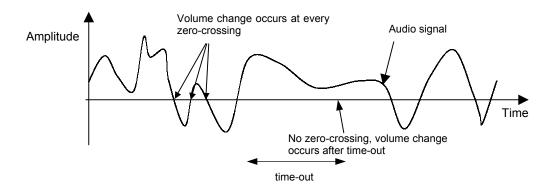

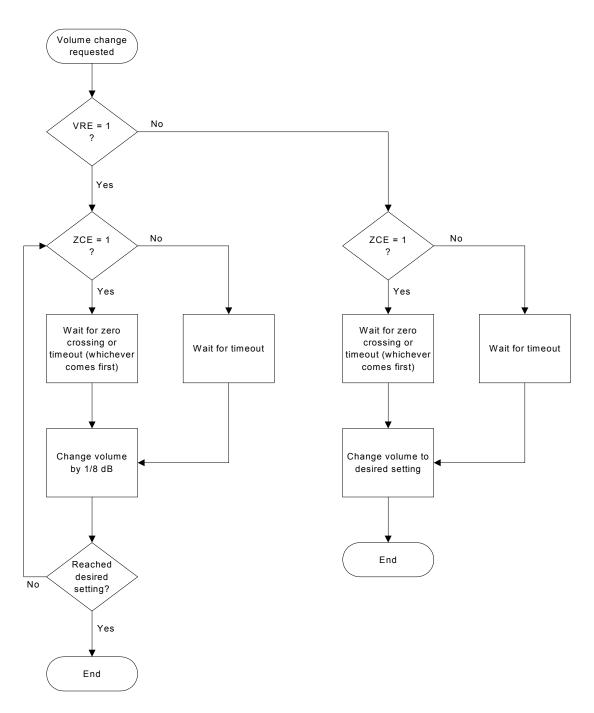

- 2. The master begins toggling SCK and transmits the slave's device address on SDA with a 1 in the LSB (ex. 81h).