## Product Preview 1:10 LVCMOS Fanout Buffer

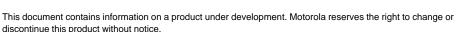

The MPC9120 is a 1:10 LVCMOS fanout buffer targeted to support Intel based Pentium II<sup>™</sup> microprocessor chip sets. The device features 10 low skew outputs optimized to drive the clock inputs of standard unbuffered SO–DIMM SDRAM modules. Standard unbuffered SO–DIMM SDRAM modules require two clocks per module allowing for the device to drive up to four modules. The output buffers have been optimized to drive the load presented by the SDRAM module.

The MPC9120 provides output shut off capabilities via an I<sup>2</sup>C serial port for applications which plan to use fewer than four modules and desire to minimize the power dissipation of the chip. Every output clock can be individually enabled/disabled through fields in the I<sup>2</sup>C control registers. After power up the default state is all outputs enabled. In applications where this default state is acceptable the I<sup>2</sup>C ports need not be exercised.

- Supports Intel Pentium<sup>™</sup> and Pentium II Processor Architectures

- 10 Skew Controlled 3.3V Compatible SDRAM Clocks

- I<sup>2</sup>C Serial Bus Interface

- Extensive Output Enable Control Capability

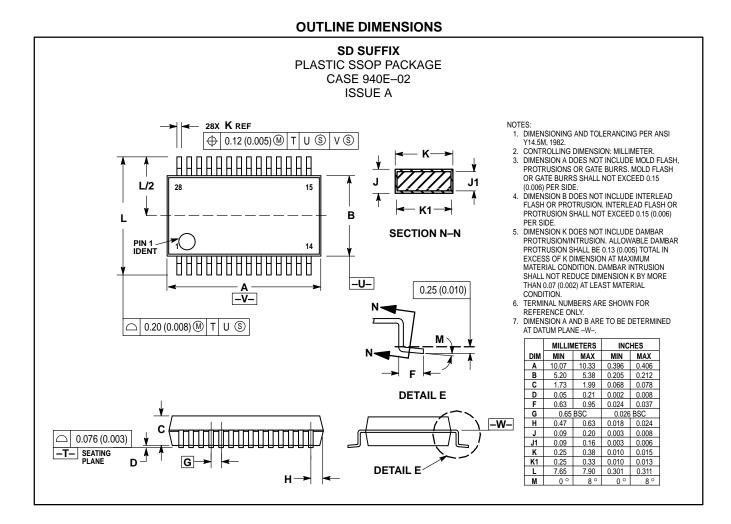

- Space Efficient 28–Lead SSOP Package

- Operating Temperature Range of 0°C to 70°C

- 3.3V ± 5% Power Supply

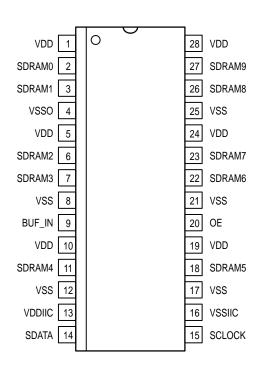

Figure 1. 28-Lead Pinout (Top View)

# 1:10 LVCMOS **FANOUT BUFFER** SD SUFFIX 28-LEAD PLASTIC SSOP PACKAGE CASE 940E-02

MPC9120

#### **FUNCTION TABLE**

| OE | V1, V2    |

|----|-----------|

| 0  | High–Z    |

| 1  | 1x BUF IN |

discontinue this product without notice.

12/97

## Table 1. Pin Descriptions

| Pin Name | I/O | Function                                                                                                                               |

|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------|

| BUF_IN   | l   | 3.3V CMOS clock input                                                                                                                  |

| SDRAM0:9 | 0   | 3.3V CMOS SDRAM clock outputs                                                                                                          |

| SDATA    | I/O | Serial data for configuration control                                                                                                  |

| SCLK     | I   | Serial clock input for configuration control. The state of the SDATA input is clocked into the device on the rising edge of this clock |

| OE       | I   | A Low forces all outputs into High–Z state                                                                                             |

| VDD      | -   | 3.3V power supply connection                                                                                                           |

| VSS      | -   | Ground connection which should be connected directly to the ground plane                                                               |

## I<sup>2</sup>C Interface

The device has an I<sup>2</sup>C serial bus interface consisting of a serial clock input (SCLK) and a data line (SDATA). The clock driver acts as a slave receiver on the I<sup>2</sup>C bus with a standard data transfer rate of up to 100 kbit/s. The MPC9120 is a 'write only' device which will not respond to general call requests from the bus master. The I<sup>2</sup>C interface transfers data in byte length packets except for the start, stop and acknowledge bits. The clock driver supports block writes consisting of the following elements.

- 1) Start Bit

- 2) Address

- 3) Acknowledge Bit

- 4) Command Code

- 5) Acknowledge Bit

- 6) Byte Count

- 7) Acknowledge Bit

- 8) Data Fields (see Table 2)

- 9) Acknowledge Bit

- 10) Stop Bit

### Table 2. Serial Data Fields

After each byte, the clock driver pulls down the data line to acknowledge the transfer. The clock driver holds SDATA low during the high state of SCLK. The 7-bit address of the clock driver is:

| A7 | A6                                | A5 | A4 | A3 | A2 | A1 | R/W |  |  |  |

|----|-----------------------------------|----|----|----|----|----|-----|--|--|--|

| 1  | 1                                 | 0  | 1  | 0  | 0  | 1  | 0   |  |  |  |

|    | Note: A7 is the first address bit |    |    |    |    |    |     |  |  |  |

The 'Command Code' should be set to all '0's and the 'Byte Count' can range from 1 to 3. The data fields are transferred sequentially in ascending order starting with Byte 0 - Configuration Function.

The MPC9120 is compliant with the DC/AC characteristics of a "Standard-Mode" I<sup>2</sup>C bus device. The logic thresholds are dependent on the 3.3V supply. For additional information on the I<sup>2</sup>C bus, refer to the document, 3114 – "The I<sup>2</sup>C-bus and how to use it (including specifications)" available from Philips Semiconductors:

http://www.semiconductors.philips.com

| Byte | Function    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

|------|-------------|----------|----------|----------|----------|----------|----------|----------|----------|

|      | SDRAM0:3    | Not Used | Not Used | Not Used | Not Used | SDRAM3   | SDRAM2   | SDRAM1   | SDRAM0   |

| 0    | Package Pin | N/A      | N/A      | N/A      | N/A      | 7        | 6        | 3        | 2        |

| 4    | SDRAM6:9    | SDRAM9   | SDRAM8   | SDRAM7   | SDRAM6   | Not Used | Not Used | Not Used | Not Used |

| I    | Package Pin | 27       | 26       | 23       | 22       | N/A      | N/A      | N/A      | N/A      |

|      | SDRAM4:5    | SDRAM5   | SDRAM4   | Not Used |

| 2    | Package Pin | 18       | 11       | N/A      | N/A      | N/A      | N/A      | N/A      | N/A      |

1. Not Used bits fields are "Don't Care" conditions.

2. When a bit field is programmed with a "1" (enable), the clock is active. A "0" (disable) means the clock is inactive.

#### **MAXIMUM RATINGS\***

| Symbol           | Parameter                         | Min  | Max | Unit |

|------------------|-----------------------------------|------|-----|------|

| VDD              | 3.3V Core Supply Voltage          | -0.5 | 4.6 | V    |

| T <sub>stg</sub> | Storage Temperature Range         | -65  | 150 | °C   |

| VIH              | 3.3V Input High Voltage (Note 3.) | -0.5 | 4.6 | V    |

| VIL              | 3.3V Input Low Voltage            | -0.5 |     | V    |

| ESD              | ESD Input Protection              | 2000 |     | V    |

\* Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions.

3. VIH should not exceed VDD level.

| Symbol          | Characteristic           |                                                | Min  | Тур | Max             | Unit | Condition                      |

|-----------------|--------------------------|------------------------------------------------|------|-----|-----------------|------|--------------------------------|

| IDD             | Supply Current for VDD   | No Clock Mode<br>Active 66MHz<br>Active 100MHz |      |     | 3<br>230<br>360 | mA   | BUF_IN = VSS or VDD            |

| VIL             | Input Low Voltage        |                                                | -0.3 |     | 0.8             | V    |                                |

| VIH             | Input High Voltage       |                                                | 2.0  |     | VDD+0.3         | V    |                                |

| ۱ <sub>IL</sub> | Input Leakage Current    |                                                | -5.0 |     | 5               | μΑ   | 0 < V <sub>IN</sub> < VCC/VCCI |

| VOL             | 3.3V Output Low Voltage  |                                                |      |     | 0.40            | V    | I <sub>OL</sub> = 1mA          |

| VOH             | 3.3V Output High Voltage |                                                | 2.4  |     |                 | V    | I <sub>OH</sub> = -1.0mA       |

| Cl              | Input Capacitance        |                                                |      | TBD |                 | pF   | Except XTL_In, XTL_Out         |

| LI              | Input Inductance         |                                                |      | TBD |                 | nH   | Except XTL_In, XTL_Out         |

## **DC CHARACTERISTICS** (VDD = $3.3V \pm 5\%$ ; GND = 0.0V; T<sub>A</sub> = 0 to +70°C; Unless Otherwise Specified)

## AC CHARACTERISTICS (VDD = $3.3V \pm 5\%$ ; GND = 0.0V; T<sub>A</sub> = 0 to +70°C; Unless Otherwise Specified)

| Symbol                                            | Characteristic                |                 | Min          | Тур | Max          | Unit | Condition         |

|---------------------------------------------------|-------------------------------|-----------------|--------------|-----|--------------|------|-------------------|

| SDRAM Clo                                         | ock Outputs (SDRAM0:17)       |                 |              |     |              |      |                   |

| <sup>t</sup> sk                                   | Output Clock Skew             |                 |              |     | 250          | ps   | Note 4.           |

| dt                                                | Output Duty Cycle             |                 | 45           |     | 55           | %    | Note 5.           |

| t <sub>p</sub>                                    | Clock Period                  | 66MHz<br>100MHz | 15.0<br>10.0 |     | 15.5<br>10.5 | ns   | Note 4.           |

| t∨IH                                              | High Time                     | 66MHz<br>100MHz | 5.6<br>3.3   |     |              | ns   | Measured at 2.4V  |

| t∨IL                                              | Low Time                      | 66MHz<br>100MHz | 5.3<br>3.1   |     |              | ns   | Measured at 0.4V  |

| t <sub>rise</sub>                                 | Rise Time                     |                 | 1.5          |     | 4.0          | V/ns | From 0.4V to 2.4V |

| <sup>t</sup> fall                                 | Fall Time                     |                 | 1.5          |     | 4.0          | V/ns | From 2.4V to 0.4V |

| <sup>t</sup> PLH                                  | Low to High Propagation Delay |                 | 1.0          |     | 5.0          | ns   |                   |

| <sup>t</sup> PHL                                  | High to Low Propagation Delay |                 | 1.0          |     | 5.0          | ns   |                   |

| <sup>t</sup> PZL <sup>,</sup><br><sup>t</sup> PZH | Enable Delay                  |                 | 1.0          |     | 8.0          | ns   |                   |

| <sup>t</sup> PLZ,<br><sup>t</sup> PHZ             | Disable Delay                 |                 | 1.0          |     | 8.0          | ns   |                   |

4. Measured on the rising edge of the clock at 1.5V.

5. Input slew rate >1V/ns.

## **APPLICATIONS INFORMATION**

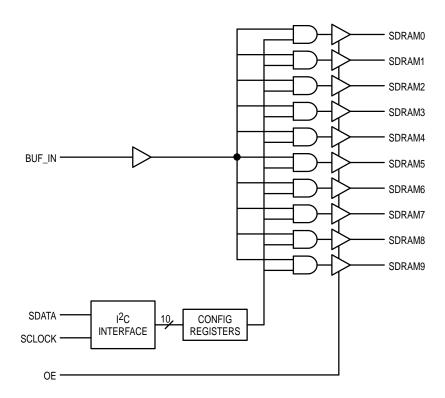

### **Output Series Termination**

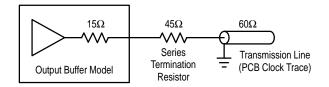

With typical MPC9120 edge rates of 1.5V/ns, a PCB trace becomes a transmission line when it is over 1–inch in length. This transmission line needs some sort of termination scheme to ensure good signal integrity at the load (device receiving clock signal). Most motherboards use the practice of *series termination*. In series termination, a series termination resistor (external resistor) is added in series with the driver device output, as shown in Figure 3, series termination resistor value is chosen so that its value, added to the output impedance of the driver, is equal to the PCB trace impedance, or in other words,  $R_{TH} = R_S + Z_L$ . The series termination resistor must be located close to the device output.

Typical system PCB trace impedance is 50–70 $\Omega$ , which is low enough to produce sufficient signal rise and fall time at the load capacitance presented by a standard CMOS input. Figure 4 illustrates proper series termination of the 15 $\Omega$ MPC9120 output driving a 60 $\Omega$  transmission line.

Figure 3. Clock Output Series Termination

Figure 4. Clock Output Series Termination

|                | Pull–Up                    |              |              |   |                | Pull-                      | Down         |              |

|----------------|----------------------------|--------------|--------------|---|----------------|----------------------------|--------------|--------------|

| Voltage<br>(V) | l <mark>min</mark><br>(mA) | ltyp<br>(mA) | Imax<br>(mA) |   | Voltage<br>(V) | l <mark>min</mark><br>(mA) | ltyp<br>(mA) | Imax<br>(mA) |

| 0              | -72                        | -116         | -198         | 1 | 0              | 0                          | 0            | 0            |

| 1.000          | -72                        | -116         | -198         | 1 | 0.400          | 23                         | 34           | 53           |

| 1.400          | -68                        | -110         | -188         | 1 | 0.650          | 35                         | 52           | 83           |

| 1.500          | -67                        | -107         | -184         | 1 | 0.850          | 43                         | 65           | 104          |

| 1.650          | -64                        | -103         | -177         | 1 | 1.000          | 49                         | 74           | 118          |

| 1.800          | -60                        | -98          | -170         | 1 | 1.400          | 61                         | 93           | 152          |

| 2.000          | -54                        | -90          | -157         | 1 | 1.500          | 64                         | 98           | 159          |

| 2.400          | -39                        | -69          | -126         | 1 | 1.650          | 67                         | 103          | 168          |

| 2.600          | -30                        | -56          | -107         | 1 | 1.800          | 70                         | 108          | 177          |

| 3.135          | 0                          | -15          | -46          | 1 | 1.950          | 72                         | 112          | 184          |

| 3.300          | _                          | 0            | -23          | 1 | 3.315          | 72                         | 112          | 204          |

| 3.465          | _                          | _            | 0            | 1 | 3.600          | _                          | 112          | 204          |

Figure 5. Typical Output V/I Characteristics for MPC9120

Pentium and Pentium II are trademarks of Intel Corp.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and **(A)** are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employeer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1–303–675–2140 or 1–800–441–2447

#### Customer Focus Center: 1-800-521-6274

Mfax™: RMFAX0@email.sps.mot.com

- TOUCHTONE 1–602–244–6609

Motorola Fax Back System

- US & Canada ONLY 1–800–774–1848

- http://sps.motorola.com/mfax/

$\Diamond$

HOME PAGE: http://motorola.com/sps/

Mfax is a trademark of Motorola, Inc.

JAPAN: Nippon Motorola Ltd.: SPD, Strategic Planning Office, 141, 4–32–1 Nishi–Gotanda, Shagawa–ku, Tokyo, Japan. 03–5487–8488

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298