### **Freescale Semiconductor**

Advance Information

Document Number: MCIMX31 Rev. 1.4, 04/2006

# MCIMX31 and MCIMX31L

# i.MX31 and i.MX31L

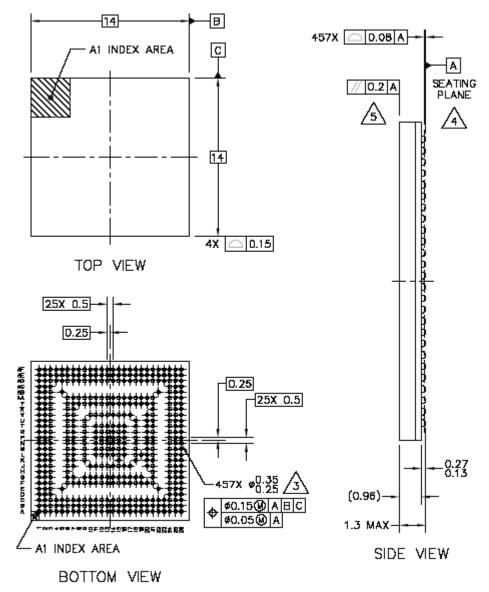

Multimedia Applications Processors Package Information Plastic Package Case 1581-01 14 x 14 mm, 0.5 P

| Ordering Information |                                |            |  |  |  |  |  |

|----------------------|--------------------------------|------------|--|--|--|--|--|

| Device               | Operating<br>Temperature Range | Package    |  |  |  |  |  |

| MCIMX31VKN5          | 0°C to +70°C                   | MAPBGA-457 |  |  |  |  |  |

| MCIMX31LVKN5         | 0°C to +70°C                   | MAPBGA-457 |  |  |  |  |  |

## 1 Introduction

The i.MX31 (MCIMX31) and i.MX31L (MCIMX31L) are multimedia applications processors that represent the next step in low-power, high-performance application processors. Unless otherwise specified, the material in this data sheet is applicable to both the i.MX31 and i.MX31L processors.

Based on an ARM11<sup>™</sup> microprocessor core, the i.MX31 and i.MX31L provide the performance with low power consumption required by modern digital devices such as:

- Feature-rich cellular phones

- Portable media players and mobile gaming machines

- Personal digital assistants (PDAs) and Wireless PDAs

- Portable DVD players

- Digital cameras

The i.MX31 and i.MX31L take advantage of the ARM1136JF-S<sup>TM</sup> core running at typical speeds of 532 MHz, and is optimized for minimal power

#### Contents

| 1 | Introduction1                                 |

|---|-----------------------------------------------|

|   | 1.1 Features                                  |

|   | 1.2 Block Diagram 2                           |

| 2 | Functional Description and Application        |

|   | Information                                   |

|   | 2.1 ARM11 Microprocessor Core 3               |

|   | 2.2 Module Inventory 5                        |

|   | 2.3 Module Descriptions 8                     |

| 3 | Signal Descriptions 23                        |

|   | 3.1 i.MX31 and i.MX31L I/O Pad Signal         |

|   | Settings 23                                   |

| 4 | Electrical Characteristics                    |

|   | 4.1 i.MX31 and i.MX31L                        |

|   | Chip-Level Conditions                         |

|   | 4.2 Supply Power-Up Requirements and          |

|   | Restrictions 65                               |

|   | 4.3 Module-Level Electrical Specifications 66 |

| 5 | Package Information and Pinout 152            |

|   | 5.1 MAPBGA Production Package                 |

|   | 457 14 x 14 mm, 0.5 P 153                     |

| 6 | Product Documentation 167                     |

|   | 6.1 Revision History 167                      |

This document contains information on a new product. Specifications and information herein are subject to change without notice.

© Freescale Semiconductor, Inc., 2005, 2006. All rights reserved.

Preliminary

#### Introduction

consumption using the most advanced techniques for power saving (DPTC, DVFS, power gating, clock gating). With 90 nm technology and dual-Vt transistors (two threshold voltages), the i.MX31 and i.MX31L provide the optimal performance versus leakage current balance.

The performance of the i.MX31 and i.MX31L is boosted by a multi-level cache system, and features peripheral devices such as an MPEG-4 Hardware Encoder (VGA, 30 fps), an Autonomous Image Processing Unit, a Vector Floating Point (VFP11) co-processor, and a RISC-based SDMA controller.

The i.MX31 and i.MX31L support connections to various types of external memories, such as 266 MHz DDR, NAND Flash, NOR Flash, SDRAM, and SRAM. The i.MX31 and i.MX31L can be connected to a variety of external devices using technology, such as high-speed USB2.0 OTG, ATA, MMC/SDIO, and compact flash.

### 1.1 Features

The i.MX31 and i.MX31L are designed for the high-tier and mid-tier smartphone markets. They provide low-power solutions for high-performance demanding multimedia and graphics applications.

The i.MX31 and i.MX31L are built around the ARM11 MCU core and implemented in the 90 nm technology.

The systems include the following features:

- Multimedia and floating-point hardware acceleration supporting:

- MPEG-4 real-time encode of up to VGA at 30 fps

- MPEG-4 real-time video post-processing of up to VGA at 30 fps

- Video conference call of up to QCIF-30 fps (decoder in software), 128 kbps

- Video streaming (playback) of up to VGA-30 fps, 384 kbps

- 3D graphics and other applications acceleration with the ARM<sup>®</sup> tightly-coupled Vector Floating Point co-processor

- On-the-fly video processing that reduces system memory load (for example, the power-efficient viewfinder application with no involvement of either the memory system or the ARM CPU)

- Advanced power management

- Dynamic voltage and frequency scaling

- Multiple clock and power domains

- Independent gating of power domains

- Multiple communication and expansion ports including a fast parallel interface to an external graphic accelerator (supporting major graphic accelerator vendors)

### 1.2 Block Diagram

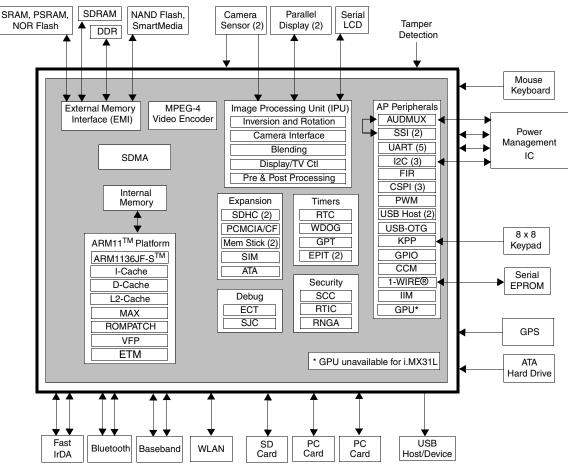

Figure 1 shows the i.MX31 and i.MX31L simplified interface block diagram.

Figure 1. i.MX31/i.MX31L Simplified Interface Block Diagram

Table 1 provides additional details on the i.MX31 and i.MX31L orderable parts.

Table 1. Orderable Part Details

| Device       | Operating Temp.<br>Range (T <sub>A</sub> ) | Package                                  | RoHS<br>Compliant | Pb-Free | MSL<br>Level | Solder<br>Temp. |

|--------------|--------------------------------------------|------------------------------------------|-------------------|---------|--------------|-----------------|

| MCIMX31VKN5  | −0°C to +70°C                              | 457-lead MAPBGA<br>0.5 mm, 14 mm x 14 mm | Yes               | Yes     | 3            | 260°C           |

| MCIMX31LVKN5 | −0°C to +70°C                              | 457-lead MAPBGA<br>0.5 mm, 14 mm x 14 mm | Yes               | Yes     | 3            | 260°C           |

# 2 Functional Description and Application Information

### 2.1 ARM11 Microprocessor Core

The CPU of the i.MX31 and i.MX31L is the ARM1136JF-S core based on the ARM v6 architecture. It supports the ARM Thumb<sup>®</sup> instruction sets, features Jazelle<sup>®</sup> technology (which enables direct execution of Java byte codes), and a range of SIMD DSP instructions that operate on 16-bit or 8-bit data values in 32-bit registers.

The ARM1136JF-S processor core features:

- Integer unit with integral EmbeddedICE<sup>™</sup> logic

- Eight-stage pipeline

- Branch prediction with return stack

- Low-interrupt latency

- Instruction and data memory management units (MMUs), managed using micro TLB structures backed by a unified main TLB

- Instruction and data L1 caches, including a non-blocking data cache with Hit-Under-Miss

- Virtually indexed/physically addressed L1 caches

- 64-bit interface to both L1 caches

- Write buffer (bypassable)

- High-speed Advanced Micro Bus Architecture (AMBA)<sup>TM</sup> L2 interface

- Vector Floating Point co-processor (VFP) for 3D graphics and other floating-point applications hardware acceleration

- $ETM^{TM}$  and JTAG-based debug support

### 2.1.1 Performance

ARM1136JF-S operating frequency in C90LP process:

• 532 MHz (4 × 133 MHz) (wcs)

#### 2.1.2 Memory System

The ARM1136JF-S complex includes 16 KB Instruction and 16 KB Data L1 caches. It connects to the i.MX31 and i.MX31L L2 unified cache through 64-bit instruction (read-only), 64-bit data read/write (bi-directional), and 64-bit data write interfaces.

The embedded 16K SRAM can be used for audio streaming data to avoid external memory accesses for the Low Power Audio Playback, for Security, or for other applications. There is also a 32-KB ROM for bootstrap code and other frequently-used code and data.

A ROM patch module provides the ability to patch the internal ROM. It can also initiate an external boot by overriding the boot reset sequence by a jump to a configurable address.

Table 2 shows information about the i.MX31 and i.MX31L core in tabular form.

| Core                | Core                | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Integrated Memory                                                                                                                                               |

|---------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acronym             | Name                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Includes                                                                                                                                                        |

| ARM11 or<br>ARM1136 | ARM1136<br>Platform | The ARM1136 <sup>™</sup> Platform consists of the ARM1136JF-S core, the ETM real-time debug modules, a 6 x 5 multi-layer AHB crossbar switch (MAX), and a Vector Floating Processor (VFP).<br>The i.MX31/i.MX31L provide a high-performance ARM11 microprocessor core and highly integrated system functions. The ARM Application Processor (AP) and other subsystems address the needs of the personal, wireless, and portable product market with integrated peripherals, advanced processor core, and power management capabilities. | <ul> <li>16 Kbyte<br/>Instruction Cache</li> <li>16 Kbyte Data<br/>Cache</li> <li>128 Kbyte L2<br/>Cache</li> <li>32 Kbyte ROM</li> <li>16 Kbyte RAM</li> </ul> |

#### Table 2. i.MX31/i.MX31L Core

### 2.2 Module Inventory

Table 3 shows an alphabetical listing of the modules in the multimedia applications processor. A cross-reference is provided directly to each module description for more information.

| Block<br>Mnemonic | Block Name                                                                                                                               | Functional<br>Grouping     | Brief Description3                                                                                                                                                                                                                                          | Section/<br>Page |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 1-Wire®           | 1-Wire Interface                                                                                                                         | Connectivity<br>Peripheral | The 1-Wire module provides bi-directional communication between<br>the ARM11 core and the Add-Only-Memory EPROM (DS2502).<br>The 1-Kbit EPROM is used to hold information about battery and<br>communicates with the ARM11 platform using the IP interface. | 2.3.1/8          |

| ATA               | Advanced<br>Technology (AT)<br>Attachment                                                                                                | Connectivity<br>Peripheral | The ATA block is an AT attachment host interface. It is designed to interface with IDE hard disc drives and ATAPI optical disc drives.                                                                                                                      | 2.3.2/8          |

| AUDMUX            | Digital Audio<br>Multiplexer                                                                                                             | Multimedia<br>Peripheral   | The AUDMUX interconnections allow multiple, simultaneous audio/voice/data flows between the ports in point-to-point or point-to-multipoint configurations.                                                                                                  | 2.3.3/9          |

| ССМ               | Clock Control<br>Module                                                                                                                  | Clock                      | The CCM provides clock, reset, and power management control for the i.MX31 and i.MX31L.                                                                                                                                                                     | 2.3.4/9          |

| CSPI              | Configurable<br>Serial Peripheral<br>Interface (x 3)                                                                                     | Connectivity<br>Peripheral | The CSPI is equipped with data FIFOs and is a master/slave configurable serial peripheral interface module, capable of interfacing to both SPI master and slave devices.                                                                                    | 2.3.5/10         |

| ECT               | Embedded<br>Cross Trigger                                                                                                                | Debug                      | The ECT is composed of three CTIs (Cross Trigger Interface) and one CTM (Cross Trigger Matrix—key in the multi-core and multi-IP debug strategy.                                                                                                            | 2.3.6/10         |

| EMI               | MI External<br>Memory<br>Interface Memory<br>Interface (EMI)<br>NAND Flash Controller (NFC)<br>Wireless External Interface Module (WEIM) |                            | 2.3.7/11                                                                                                                                                                                                                                                    |                  |

| EPIT              | Enhanced<br>Periodic<br>Interrupt Timer                                                                                                  | Timer<br>Peripheral        | The EPIT is a 32-bit "set and forget" timer which starts counting<br>after the EPIT is enabled by software. It is capable of providing<br>precise interrupts at regular intervals with minimal processor<br>intervention.                                   | 2.3.8/12         |

#### Table 3. Digital and Analog Modules

| Block<br>Mnemonic | Block Name                                   | Functional<br>Grouping     | Brief Description3                                                                                                                                                                                                                                                                                  | Section/<br>Page |

|-------------------|----------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| FIR               | Fast InfraRed<br>Interface                   | Connectivity<br>Peripheral | This FIR is capable of establishing a 0.576 Mbit/s, 1.152 Mbit/s or 4 Mbit/s half duplex link via a LED and IR detector. It supports 0.576 Mbit/s, 1.152 Mbit/s medium infrared (MIR) physical layer protocol and 4Mbit/s fast infrared (FIR) physical layer protocol defined by IrDA, version 1.4. | 2.3.9/12         |

| GPIO              | General<br>Purpose I/O<br>Module             | Pins                       | The GPIO provides 32 bits of bidirectional, general purpose I/O.<br>This peripheral provides dedicated general-purpose pins that can<br>be configured as either inputs or outputs.                                                                                                                  | 2.3.10/12        |

| GPT               | General<br>Purpose Timer                     | Timer<br>Peripheral        | The GPT is a multipurpose module used to measure intervals or generate periodic output.                                                                                                                                                                                                             | 2.3.11/12        |

| GPU               | Graphics<br>Processing Unit                  | Multimedia<br>Peripheral   | The GPU provides hardware acceleration for 2D and 3D graphics algorithms.                                                                                                                                                                                                                           | 2.3.12/13        |

| 12C               | Inter IC<br>Communication                    | Connectivity<br>Peripheral | The I2C provides serial interface for controlling the Sensor Interface<br>and other external devices. Data rates of up to 100 Kbits/s are<br>supported.                                                                                                                                             | 2.3.13/13        |

| IIM               | IC Identification<br>Module                  | Security                   | The IIM provides an interface for reading—and in some cases, programming, and overriding identification and control information stored in on-chip fuse elements.                                                                                                                                    | 2.3.14/13        |

| IPU               | Image<br>Processing Unit                     | Multimedia<br>Peripheral   | The IPU supports video and graphics processing functions in the i.MX31 and i.MX31L and interfaces to video, still image sensors, and displays.                                                                                                                                                      | 2.3.15/14        |

| KPP               | Keypad Port                                  | Connectivity<br>Peripheral | The KPP is used for key pad matrix scanning or as a general purpose I/O. This peripheral simplifies the software task of scanning a keypad matrix.                                                                                                                                                  | 2.3.16/15        |

| MPEG-4            | MPEG-4 Video<br>Encoder                      | Multimedia<br>Peripherals  | The MPEG-4 encoder accelerates video compression, following the MPEG-4 standard                                                                                                                                                                                                                     | 2.3.17/15        |

| PCMCIA            | РСМ                                          | Connectivity<br>Peripheral | The PCMCIA Host Adapter provides the control logic for PCMCIA socket interfaces.                                                                                                                                                                                                                    | 2.3.19/16        |

| PWM               | Pulse-Width<br>Modulator                     | Timer<br>Peripheral        | The PWM has a 16-bit counter and is optimized to generate sound from stored sample audio images. It can also generate tones.                                                                                                                                                                        | 2.3.20/16        |

| RNGA              | Random<br>Number<br>Generator<br>Accelerator | Security                   | The RNGA module is a digital integrated circuit capable of generating 32-bit random numbers. It is designed to comply with FIPS-140 standards for randomness and non-determinism.                                                                                                                   | 2.3.21/16        |

| RTC               | Real Time Clock                              | Timer<br>Peripheral        | The RTC module provides a current stamp of seconds, minutes, hours, and days. Alarm and timer functions are also available for programming. The RTC support dates from the year 1980 to 2050.                                                                                                       | 2.3.22/16        |

| RTIC              | Run-Time<br>Integrity<br>Checkers            | Security                   | The RTIC ensures the integrity of the peripheral memory contents and assists with boot authentication.                                                                                                                                                                                              | 2.3.23/17        |

#### Table 3. Digital and Analog Modules (continued)

| Block<br>Mnemonic Block Name Functional<br>Grouping |                                                                               |                                 | Brief Description3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Section/<br>Page |

|-----------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| SCC                                                 | Security<br>Controller<br>Module                                              | Security                        | The SCC is a hardware component composed of two blocks—the<br>Secure RAM module, and the Security Monitor. The Secure RAM<br>provides a way of securely storing sensitive information. The<br>Security Monitor implements the security policy, checking algorithm<br>sequencing, and controlling the Secure State.                                                                                                                                                                                                                                                                                                                                                    | 2.3.24/17        |

| SDHC                                                | Secured Digital<br>Host Controller                                            | Connectivity<br>Peripheral      | The SDHC controls the MMC (MultiMediaCard), SD (Secure Digital) memory, and I/O cards by sending commands to cards and performing data accesses to and from the cards.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.3.25/18        |

| SDMA                                                | SDMA                                                                          | System<br>Control<br>Peripheral | The SDMA controller maximizes the system's performance by relieving the ARM core of the task of bulk data transfer from memory to memory or between memory and on-chip peripherals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.3.26/18        |

| SIM                                                 | Subscriber<br>Identification<br>Module                                        | Connectivity<br>Peripheral      | The SIM interfaces to an external Subscriber Identification Card. It<br>is an asynchronous serial interface adapted for Smart Card<br>communication for e-commerce applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.3.27/20        |

| SJC                                                 | Secure JTAG<br>Controller                                                     | Debug                           | The SJC provides debug and test control with maximum security<br>and provides a flexible architecture for future derivatives or future<br>multi-cores architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.3.28/20        |

| SSI                                                 | Synchronous<br>Serial Interface                                               | Multimedia<br>Peripheral        | The SSI is a full-duplex, serial port that allows the chip to<br>communicate with a variety of serial devices, such as standard<br>codecs, Digital Signal Processors (DSPs), microprocessors,<br>peripherals, and popular industry audio codecs that implement the<br>inter-IC sound bus standard (I2S) and Intel AC97 standard.                                                                                                                                                                                                                                                                                                                                      | 2.3.29/20        |

| UART                                                | Universal<br>Asynchronous<br>Receiver/Trans<br>mitter                         | Connectivity<br>Peripheral      | The UART provides serial communication capability with external devices through an RS-232 cable or through use of external circuitry that converts infrared signals to electrical signals (for reception) or transforms electrical signals to signals that drive an infrared LED (for transmission) to provide low speed IrDA compatibility.                                                                                                                                                                                                                                                                                                                          | 2.3.30/21        |

| USB                                                 | Universal Serial<br>Bus—<br>2 Host<br>Controllers and<br>1 OTG<br>(On-The-Go) | Connectivity<br>Peripherals     | <ul> <li>USB Host 1 is designed to support transceiverless connection to the on-board peripherals in Low Speed and Full Speed mode, and connection to the ULPI (UTMI+ Low-Pin Count) and Legacy Full Speed transceivers.</li> <li>USB Host 2 is designed to support transceiverless connection to the Cellular Modem Baseband Processor.</li> <li>The USB-OTG controller offers HS/FS/LS capabilities in Host mode and HS/FS in device mode. In Host mode, the controller supports direct connection of a FS/LS device (without external hub). In device (bypass) mode, the OTG port functions as gateway between the Host 1 Port and the OTG transceiver.</li> </ul> | 2.3.31/21        |

| WDOG                                                | Watchdog Timer<br>Module                                                      | Timer<br>Peripheral             | The WDOG module protects against system failures by providing a method for the system to recover from unexpected events or programming errors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.3.32/23        |

#### Table 3. Digital and Analog Modules (continued)

### 2.3 Module Descriptions

This section provides a brief text description of all the modules included in the i.MX31 and i.MX31L, arranged in alphabetical order.

### 2.3.1 1-Wire

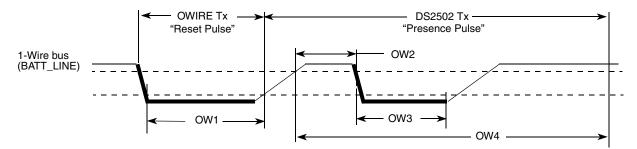

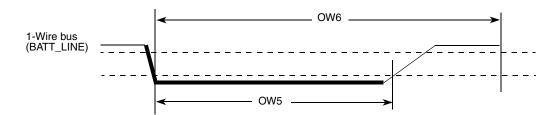

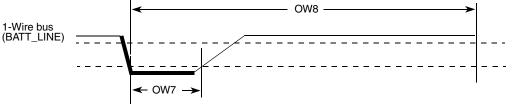

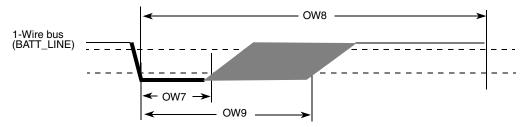

The 1-Wire module provides bi-directional communication between the ARM11 core and the Add-Only-Memory EPROM (DS2502). The 1-Kbit EPROM is used to hold information about battery and communicates with the ARM11 platform using the IP interface. The ARM11 (through the 1-Wire interface) acts as the bus master and the DS2502 device is the slave. The 1-Wire peripheral does not trigger interrupts; hence it is necessary for the ARM11 to poll of the 1-Wire to manage the module. The 1-Wire uses an external pin(to connect to the DS2502. Timing requirements are met in hardware with the help of a 1 MHz clock. The clock divider generates a 1 MHz clock that is used as time reference by the state machine. Timing requirements are crucial for proper operation, and the 1-Wire state machine and the internal clock provide the necessary signal. The clock must configured to approximately 1 MHz. You can then set the 1-Wire register to send and receive bits over the 1-Wire bus.

### 2.3.2 Advanced Technology Attachment (ATA)

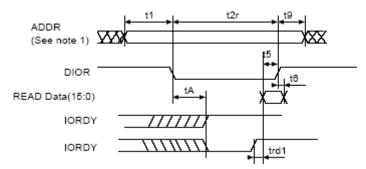

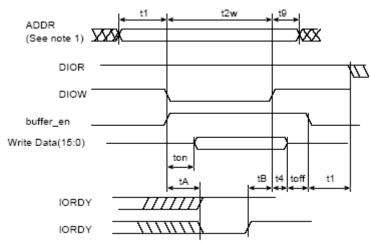

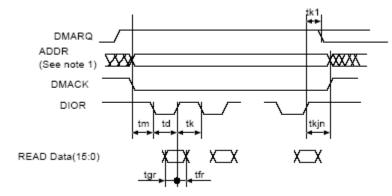

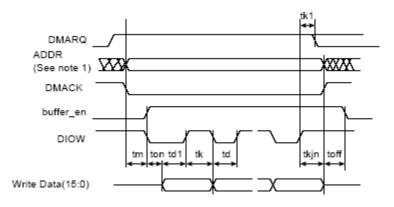

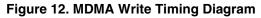

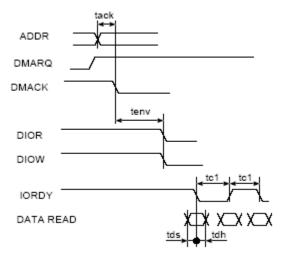

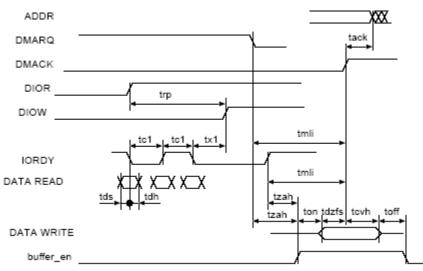

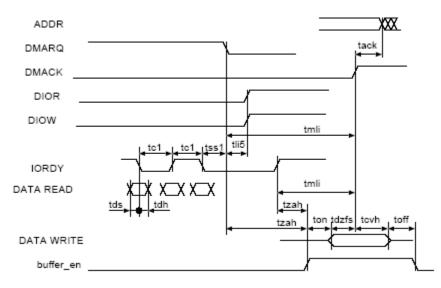

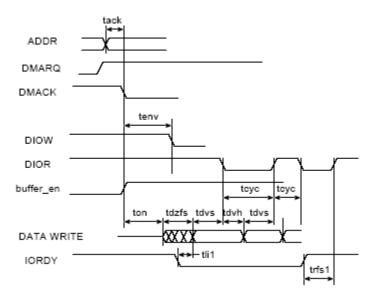

The ATA block provides an AT attachment host interface for the i.MX31 and i.MX31L. Its main use is to provide an interface with IDE hard disc drives and ATAPI optical disc drives. It interfaces with the ATA device using industry standard ATA signals. The ATA interface is compliant to the ATA standard, and supports following ATA standard protocols:

- PIO modes 0, 1, 2, 3, and 4

- Multiword DMA modes 0, 1, and 2

- Ultra DMA modes 0, 1, 2, 3, and 4 with a bus clock of 50 MHz or higher

- Ultra DMA mode 5 with bus clock of 80 MHz or higher

The ATA interface has two busses connected to it. The CPU bus provides communication with the ARM11 host processor and the DMA bus provides communication between the ATA module and the host DMA unit. All internal ATA registers are visible from both busses, allowing enhanced DMA access to program the interface.

There are basically two protocols that can be active at the same time on the ATA bus. The first and simplest protocol (PIO mode access) can be started at any time by either the ARM11 or the host-enhanced DMA to the ATA bus. The PIO mode is a slow protocol, mainly intended to be used to program an ATA disc drive, but also possible to use to transfer data to/from the disc drive.

The second protocol is the DMA mode access. DMA mode is started by the ATA interface after receiving a DMA request from the drive, and only if the ATA interface has been programmed to accept the DMA request. In DMA mode, either multiword DMA or ultra DMA protocol is used on the ATA bus. All transfers between FIFO and host IP or DMA IP bus are zero wait states transfer, so high speed transfer between FIFO and DMA/host bus is possible.

### 2.3.3 Digital Audio Mux (AUDMUX)

The AUDMUX provides programmable interconnecting for voice, audio, and synchronous data routing between host serial interfaces (i.e. SSI, SAP) and peripheral serial interfaces (i.e. audio and voice codecs). The AUDMUX allows audio system connectivity to be modified through programming (as opposed to altering the design of the system into which the chip is designed). The design of the AUDMUX allows multiple simultaneous audio/voice/data flows between the ports in point-to-point or point-to-multipoint configurations.

Included in the AUDMUX are two types of interfaces. The internal ports connect to the processor serial interfaces and external ports connect to off-chip audio devices and serial interfaces of other processors. A desired connectivity is achieved by configuring the appropriate internal and external ports.

The module includes full 6-wire SSI interfaces for asynchronous receive and transmit as well as a configurable 4-wire (synchronous) or 6-wire (asynchronous) peripheral interface The AUDMUX allows each host interface to be connected to any other host or peripheral interface in a point-to-point or point-to-multipoint (network mode).

### 2.3.4 Clock Control Module (CCM)

The CCM controls the system frequency, distributes clocks to various parts of the chip, controls the reset mechanism of the chip, and provides an advanced low-power management capability of the i.MX31 and i.MX31L.

The CCM utilizes multiple clock sources to generate the clock signals in the i.MX31 and i.MX31L. The external low frequency clock (CKIL) can use either a 32 kHz, 32.768 kHz or a 38.4 kHz crystal as its source. For applications that require a high frequency clock source the CCM has a CKIH pin to which an external high frequency clock can be connected.

The CCM provides a large number of clock outputs used to supply clocks to the MCU and the peripherals. The i.MX31 and i.MX31L are partitioned into two asynchronous clock domains: MCU and USB, as there are different functionality and frequency requirements from these clocks. The main clock of the MCU clock domain is mcu\_main\_clk and is generated by MCU clock switch unit. The MCU clock domain is partitioned into four synchronous clocks and two sub-domains. The main clock of this domain is called mcu\_main\_clk, and it is the output of the MCU clock switch unit. The main clock of the USB clock domain is usb\_main\_clk and is generated by the USB clock switch unit.

Another part of the CCM is the low-power clock gating (LPCG). The LPCG block distributes clocks to all modules from the subdomain clocks and gates off clocks in low-power mode. Clock gating for each module is carried out based on the specific low-power mode and the relevant bits in the MCGR register.

The power management portion of the i.MX31 and i.MX31L is controlled by the CCM. To this end, the i.MX31 and i.MX31L are partitioned into four power domains. The i.MX31 and i.MX31L support a versatile definition of power modes, including power and clock domains status and applied power techniques. The power modes are Run, Wait, Doze, State Retention, Deep Sleep, and Hibernate. The CCM supports several power management techniques that reduce active and static power consumption:

• Dynamic Voltage Frequency Scaling (DVFS) reduces active power consumption by scaling voltage and frequency accordingly to required MIPs.

- Dynamic Process Temperature Compensation (DPTC) reduces active power consumption by adjusting supply voltage accordingly specific process cases, the manner in which the chip was fabricated, and the ambient temperature.

- State Retention Voltage (SRV) reduces static power consumption by decreasing supply voltage to minimum State Retention level. Chip is not functional in this mode.

- Active Well Bias (AWB) reduces static power consumption by applying back bias on transistors. AWB can be applied on ARM11P. ARM11P is not functional when AWB is applied.

- L2 Cache Power Gating—Reduces static power consumption by eliminating L2 Cache leakage.

- ARM11P Power Gating—Reduces static power consumption by eliminating ARM11P leakage.

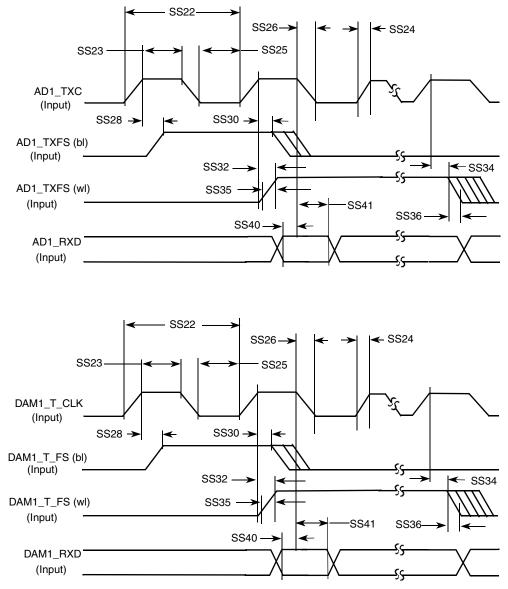

### 2.3.5 Configurable Serial Peripheral Interface (CSPI)

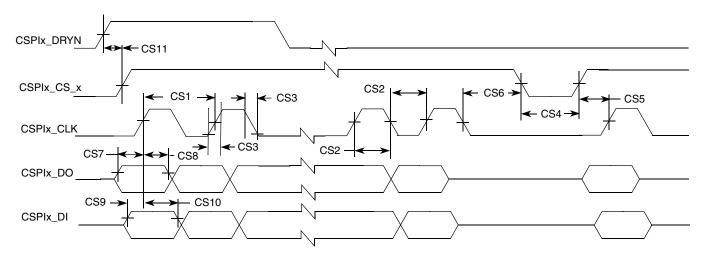

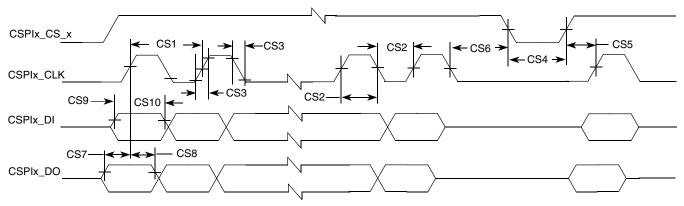

The CSPI is used for fast data communication with fewer software interrupts. There are three identical CSPI modules in the i.MX31 and i.MX31L that provide full-duplex synchronous serial interface. It is master/slave configurable and includes four chip selects to support multiple peripherals. In addition, the transfer continuation function of the CSPI allows unlimited length data transfers using 32-bit wide by 8 entry FIFO for both TX and RX data DMA support. The CSPI is equipped with data FIFOs and is a master/slave configurable serial peripheral interface module, capable of interfacing to both SPI master and slave devices. The CSPI Ready (SPI\_RDY) and Chip Select (SS) control signals enable fast data communication with fewer software interrupts. When the CSPI module is configured as a master, it uses a serial link to transfer data between the CSPI and an external device. A chip-enable signal and a clock signal are used to transfer data between these two devices. When the CSPI module is configured as a slave, the user can configure the CSPI Control register to match the external SPI master's timing.

### 2.3.6 Embedded Cross Trigger (ECT)

The ECT scheme is based on the ECT debugging hardware from ARM Ltd. The ECT is composed of three CTIs (Cross Trigger Interface) and one CTM (Cross Trigger Matrix). The ECT is key in the multi-core and multi-IP debug strategy. The outcome is a SW-controlled debug signal matrix that receives many signals from various sources (i.e. cores and peripherals) and propagates/routes them to the different debug resources of the SoC. As seen in previous sections, those debug resources can include profiling capabilities, real-time trace (trace enabled or disabled), triggers, SOC level multiplexing, and debug interrupts.

The main advantages of using the ECT are that it provides a standardized debug scheme, in line with ARM RealView debugger, simplifies integration with ARM debug tools. Another advantage is that within a single debug domain, all the IPs can share the same debug resources and there is no need to duplicates counters or real-time trace resources. One trace port can be used with one tool to track the activity of the core and its peripherals. Since ECT should only be used during debug sessions, it is off (disabled) by default.

### 2.3.7 External Memory Interface (EMI)

The EMI controls all memory accesses external to the i.MX31 and i.MX31L (read/write/erase/program) from all the masters in the system. This is done by using two port interfaces MPG (AHB 32 bit) and MPG64 (AHB 64 bit) toward different external memories.

The EMI includes interface elements, and controllers of external memories, as shown in the list below:

- M3IF—Multi Master Memory Interface.

- ESDCTL/MDDRC—Enhanced SDRAM/MDDR memory controller.

- PCMCIA—PCMCIA memory controller.

- NFC—NAND Flash memory controller.

- WEIM—SRAM/PSRAM/FLASH memory controller.

All accesses via the EMI are arbitrated by the Multi Master Memory Interface (M3IF) and controlled by the respective memory controller. The M3IF - ESDCTL/MDDRC interface is designed to reduce access latency by generating multiple accesses through the dedicated ESDCTL/MDDRC arbitration (MAB) module, which controls the access towards/from the Enhanced SDRAM/MDDR memory controller. For the other memory interfaces (PCMCIA, NFC, WEIM), the M3IF only arbitrates and forwards the masters requests received through the Master Port Gasket (MPG/MPG64) interface.

**The M3IF - Multi Master Memory Interface** controls memory accesses (read/write/erase/program) from one or more masters through different port interfaces toward different external memory controllers. The masters arrive from the ARM Platform, the SDMA, the MPEG-4 encoder, or the IPU. The controllers are: ESDCTL/MDDRC, PCMCIA, NANDFLASH and WEIM. The interface between the M3IF and the controllers can be divided into two different types: M3IF-ESDCTL, and M3IF-all others. For the other port interfaces, the M3IF arbitrates and forwards the masters' requests received through the Master Port Gasket (MPG) interfaces and the M3IF arbitration (M3A) module toward the respective memory controller.

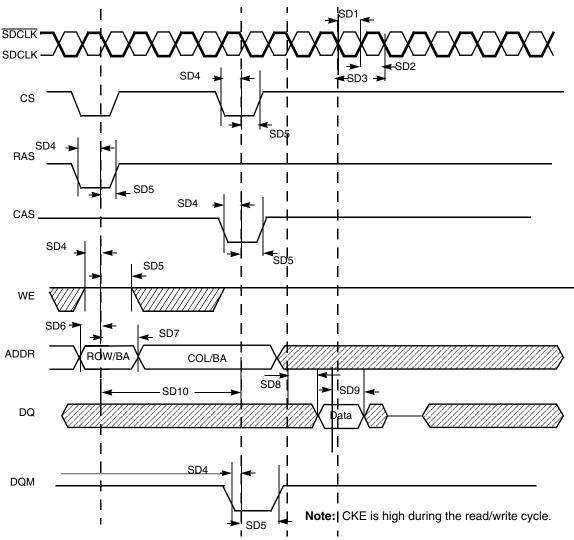

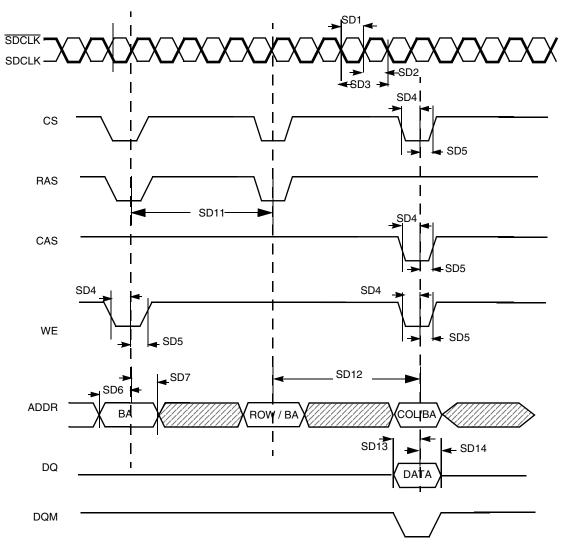

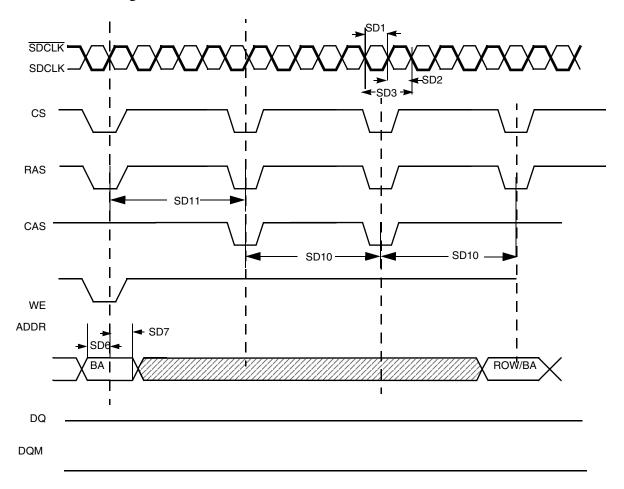

**The Enhanced SDRAM Controller** consists of 10 major blocks, including the SDRAM command state machine controller, bank register (page and bank address comparators), Row/Column Address Multiplexer & decoder, configuration registers, refresh request sequencer, command sequencer, size logic (splitting access), data path (data aligner/multiplexer), MDDR interface, and the Power Down timer. Since up to two SDRAMs can be connected to the ESDCTL, and each SDRAM has 4 banks, there are a total of 8 bank controllers. The bank controllers can also be used as comparators for timing parameters.

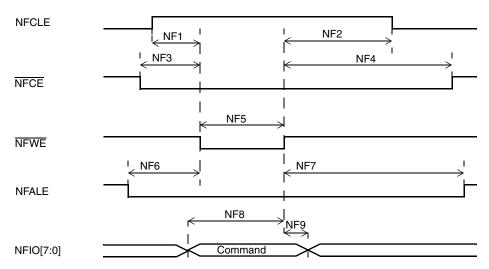

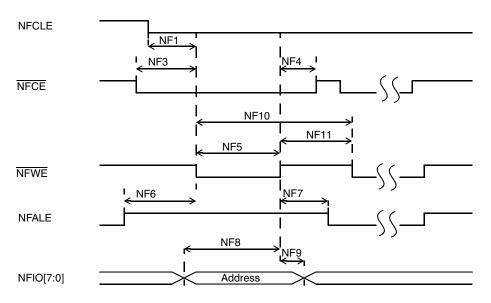

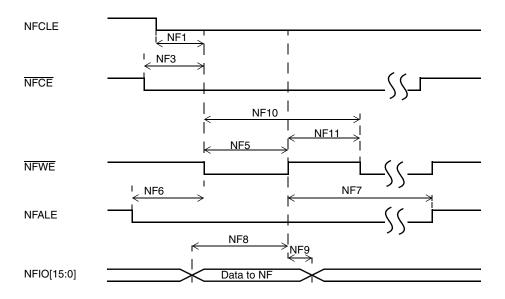

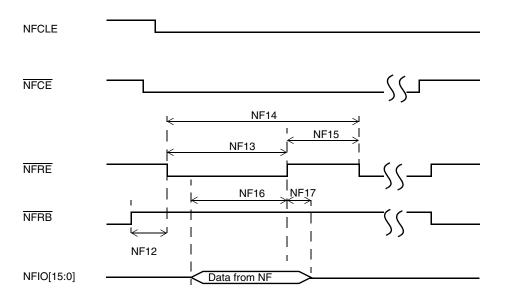

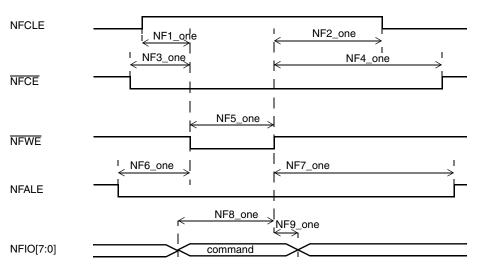

**The NAND Flash Controller (NFC)** interfaces standard NAND Flash devices to the i.MX31 and i.MX31L and hides the complexities of accessing the NAND Flash. It provides a glueless interface to both 8-bits and 16-bits NAND Flash parts with page sizes of 512 Bytes or 2 Kilobytes. It addressing scheme allows it to accesses flash devices of almost limitless capacities. The 2 kilobyte RAM buffer of the NAND Flash is used as the boot RAM during a cold reset (if the i.MX31 and i.MX31L are configured for a boot to be carried out from the NAND Flash device). After the boot procedure completes, the RAM is available as buffer RAM. In addition, the NAND Flash controller provides an X16 bit and X32 bit interface to the AHB bus on the chip side, and an X8/X16 interface to the NAND Flash device on the external side.

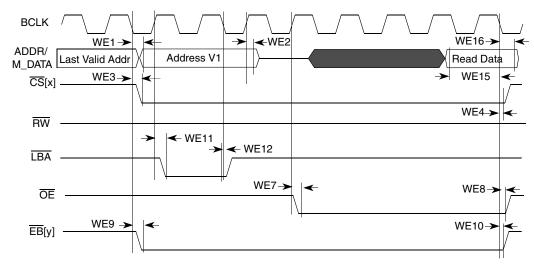

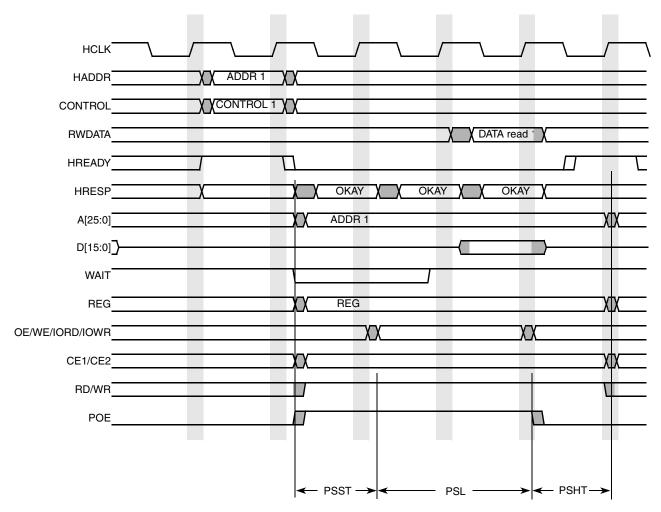

The Wireless External Interface Module (WEIM) handles the interface to devices external to chip, including generation of chip selects, clocks and controls for external peripherals and memory. It provides asynchronous and synchronous access to devices with SRAM-like interface. The WEIM includes six chip

selects for external devices, with two CS signals covering a range of 128Mbytes, and the other four each covering a range of 32Mbytes. The 128 Mbyte range can be increased to 256Mbytes when combined with combining the two signals. The WEIM offers selectable protection for each chip select as well as programmable data port size. There is a programmable wait-state generator for each chip select and support for Big Endian and Little Endian modes of operation per access.

### 2.3.8 Enhanced Periodic Interrupt Timer (EPIT)

The EPIT is a 32-bit "set and forget" timer which starts counting after the EPIT is enabled by software and can generate an interrupt generation when counter reaches the Compare value. It is capable of providing precise interrupts at regular intervals with minimal processor intervention. The EPIT is based on a 32-bit down counter with selectable clock. It also has a 12-bit prescaler for division of input clock frequency. The counter value can be programmed on the fly and can also be programmed to be active in both low power and debug modes.

### 2.3.9 Fast InfraRed Interface (FIR)

The Fast InfraRed Interface module (FIR) is capable of establishing a 0.576 Mbit/s, 1.152 Mbit/s or 4 Mbit/s half duplex link via a LED and IR detector. It supports 0.576 Mbit/s, 1.152 Mbit/s Medium InfraRed (MIR) physical layer protocol and 4Mbit/s Fast InfraRed (FIR) physical layer protocol defined by IrDA, version 1.4. In addition, the Serial InfraRed (SIR) protocol, which supports data rate 115.2kbps or lower, is implemented in UART module. The FIR interface signals are multiplexed with the UART counterpart signals via GPIO configuration for a complete InfraRed Interface supporting SIR, MIR and FIR modes.

### 2.3.10 General Purpose I/O Module (GPIO)

The general-purpose input/output (GPIO) peripheral provides dedicated general-purpose pins that can be configured as either inputs or outputs. When configured as an output, you can write to an internal register to control the state driven on the output pin. When configured as an input, you can detect the state of the input by reading the state of an internal register. The GPIO includes all of the general purpose input/output logic necessary to drive a specific data to the pad and control the direction of the pad using registers in the GPIO module. The ARM11 is able to sample the status of the corresponding pads by reading the appropriate status register. The GPIO supports up to 32 interrupts and has the ability to identify interrupt edges as well as generate three active high interrupts.

### 2.3.11 General Purpose Timer (GPT)

The General purpose timer (GPT) has a 32 bit up-counter. The timer counter value can be captured in a register using an event on an external pin. The capture trigger can be programmed to be a rising or/and falling edge. The GPT can also generate an event on ipp\_do\_cmpout pins and an interrupt when the timer reaches a programmed value. It has a 12-bit prescaler providing a programmable clock frequency derived from multiple clock sources. The GPT has one 32 bit up-counter with clock source selection, including external clock, two input capture channels with programmable trigger edge, and three output compare channels with programmable output mode. The GPT can perform a forced compare and can configured to

be programmed to be active in low power and debug modes Interrupt generation can be programmed for capture, compare, rollover events and the timers offers both restart or free-run modes of operation.

### 2.3.12 Graphics Processing Unit (GPU)

The GPU provides hardware acceleration for 2D and 3D graphics algorithms. The quality is sufficient for running desk-top quality interactive graphics applications on displays whose resolution is equivalent to VGA (and above) and whose color representation is up to 32 bits per pixel. The i.MX31 and i.MX31L's GPU is built around an ARM MBX R-S graphics accelerator.

The GPU operates on 3D scene data (sent as batches of triangles) that are transformed and lit by the VGP. Triangles are written directly to the TA on a First In First Out (FIFO) basis so that the CPU is not stalled. In addition, the SDMA can be used to perform batch transfers with very low CPU involvement. The TA performs advanced culling on triangle data by writing the tiled non-culled triangles to the external memory. The event manager uses SmartBuffer technology for control. As a result, any level of scene complexity is handled in a fixed display list buffer size. The HSR engine reads the tiled data and implements per-pixel HSR with full Z-accuracy. The resulting visible pixels are textured and shaded in Internal True Color (ITC, 24 bit per pixel) before rendering the final image for display buffer.

#### NOTE

The GPU is not available on the i.MX31L.

### 2.3.13 Inter IC Communication (I<sup>2</sup>C)

I<sup>2</sup>C is a two-wire, bidirectional serial bus that provides a simple, efficient method of data exchange, minimizing the interconnection between devices. This bus is suitable for applications requiring occasional communications over a short distance between many devices. The flexible I<sup>2</sup>C allows additional devices to be connected to the bus for expansion and system development.

The I<sup>2</sup>C operates up to 400 kbps but it depends on the pad loading and timing (for pad requirement details please refer to Philips I<sup>2</sup>C Bus Specification, Version 2.1). The I<sup>2</sup>C system is a true multiple-master bus including arbitration and collision detection that prevents data corruption if multiple devices attempt to control the bus simultaneously. This feature supports complex applications with multiprocessor control and can be used for rapid testing and alignment of end products through external connections to an assembly-line computer.

### 2.3.14 IC Identification Module (IIM)

The IIM provides an interface for reading and in some cases programming and/or overriding identification and control information stored in on-chip fuse elements. The module supports laser fuses (L-Fuses) or electrically-programmable poly fuses (e-Fuses) or both kinds.

The IIM also provides a set of volatile software-accessible signals which can be used for software control of hardware elements, not requiring non-volatility. The IIM provides the primary user-visible mechanism for interfacing with on-chip fuse elements. Among the uses for the fuses are unique chip identifiers, mask revision numbers, cryptographic keys, and various control signals requiring permanent non-volatility. The IIM also provides up to 28 volatile control signals and a means to generate a second 168-bit SCC key.

The IIM consists of a master controller, a software fuse value shadow cache, and a set of registers to hold the values of signals visible outside the module. Up to eight arrays of fuses (L-Fuses and/or e-Fuses) are associated with the IIM, but are instantiated outside it.

The IIM is accessible via an 8-bit IP bus interface. An 8-bit interface is used because it matches the natural width of the fuse arrays. All registers are 32-bit aligned, to allow the module to be instantiated on IP buses supporting only 32-bit peripherals. A subset of fuses, as well as the software-controlled volatile signals, are capable of driving top-level nets within the SoC. These signals are hereinafter referred to as Hardware-Visible Signals, or HW-Visible Signals. These signals are intended for feature enablement and disablement and similar uses within the device.

Laser fuses can only be blown during chip manufacturing (at the wafer level). The e-Fuses may be blown under software or JTAG control during IC final test, at the customer factory or in the field. They include a mechanism to inhibit further blowing of fuses (write-protect), to support secure computing environments. The fuse values may also be overridden by software without modifying the fuse element. Similar to the write-protect functionality, the override functionality can also be permanently disabled. Fuse banks may also be scan-inhibited on a per-bank basis to prevent reading and programming of fuses through the JTAG interface.

### 2.3.15 Image Processing Unit (IPU)

The IPU is designed to support video and graphics processing functions in the i.MX31 and i.MX31L and to interface to video/still image sensors and displays. The IPU can capture image data from a camera sensor or from a TV decoder. The captured image can be sent to preprocessing or stored in an external system memory for additional processing on the ARM11 platform. Preprocessing of data can be programmed from the sensor or from the external system memory. There are two preprocessing includes determined by the data destination - an encoder or a display (viewfinder mode). Preprocessing includes downsizing with independent integer horizontal and vertical ratios, resizing with independent fractional horizontal and vertical ratios, color space conversion, combining a video plane with a graphics plane (blending on graphics on top of video plane),

Data postprocessing from the external system memory. The MCU can invoke a number of postprocessing channels sequentially by re-programming the IPU after finish of previous channel frame processing. Postprocessing includes downsizing with independent integer horizontal and vertical ratios, resizing with independent fractional horizontal and vertical ratios, color space conversion and combining a video plane with a graphics plane (blending on graphics on top of video plane). It also provides 90 degree rotation, up/down and left/right flipping of the image. Post-filtering of data from the system memory with support of the MPEG-4 (both deblocking and deringing) and H.264 post-filtering algorithms.

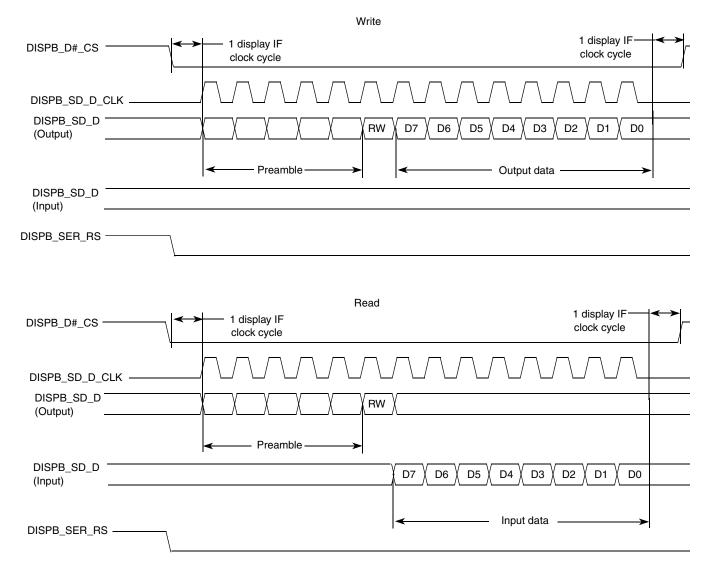

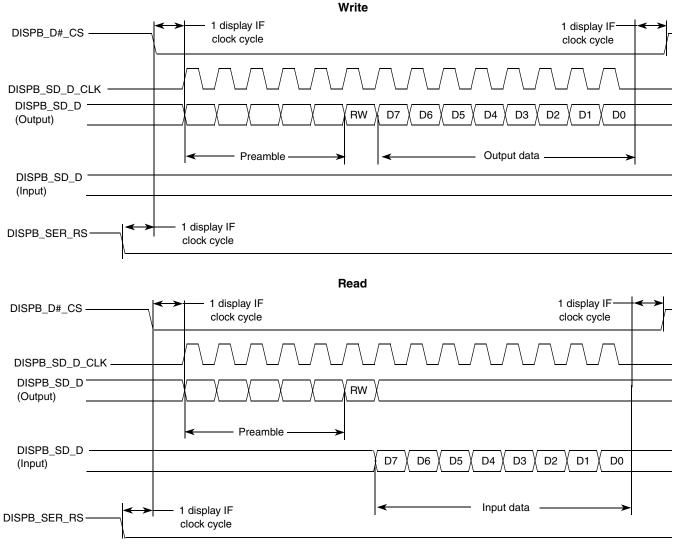

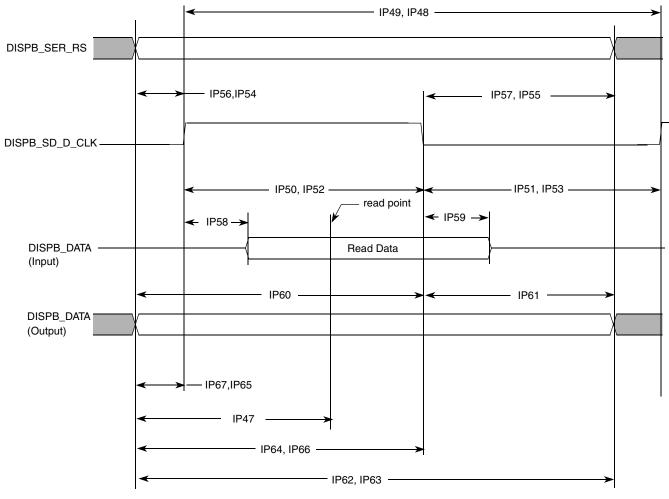

The IPU provides for the display of video and graphics on a synchronous (dump or memoryless) display by displaying video and graphics on an asynchronous (smart) display. There are two mechanisms to support smart display or graphic accelerator functionality: interleaving data and commands from a command buffer prepared by the MCU or automatic commands generation according to a prepared template. The data can be sent to the smart display from the system memory, internal IPU processing modules or directly from the MCU or the system DMA controller.

### 2.3.16 Keypad Port (KPP)

The Keypad Port is designed to interface with keypad matrix with 2-contact or 3-point contact keys. The Keypad Port is designed to simplify the software task of scanning a keypad matrix. With appropriate software support, the KPP is capable of detecting, debouncing and decoding one or multiple keys pressed simultaneously in the keypad. The KPP supports up to 8 x 8 external key pad matrix. Its port pins can be used as general purpose I/O. Using an open drain design the KPP includes glitch suppression circuit design, multiple keys, long key, and standby key detection.

### 2.3.17 MPEG-4 Video Encoder (MPEG-4)

The MPEG-4 encoder in the i.MX31 and i.MX31L accelerates video compression, in compliance with the MPEG-4 standard. The encoder provides several levels of compression formats including MPEG-4 simple profile (all levels) and H.263 baseline. The encoder can encode at a pixel rate up to VGA @ 30 fps and compressed bit-rates up to 4 Mbps. The MPEG-4 encoder provides what is essentially the complete video processing chain, generating a Huffman-coded stream with the exception of the formation of the final MPEG-4 stream which is the only burden put on the ARM11 processor. Additional processing provided by the MPEG-4 encoder includes picture smoothening (low-pass filter) and camera movement stabilization. Support for enhanced conference call format in the form of additional information inserted within the MPEG stream, used by a MPEG-4 decoder to improve performance.

### 2.3.18 Memory Stick Host Controller (MSHC)

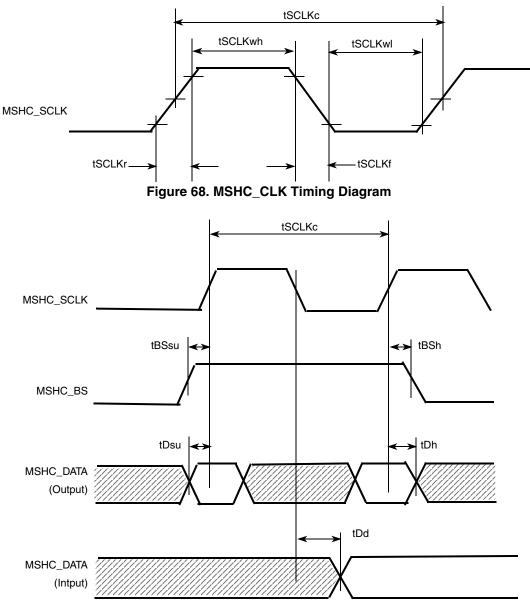

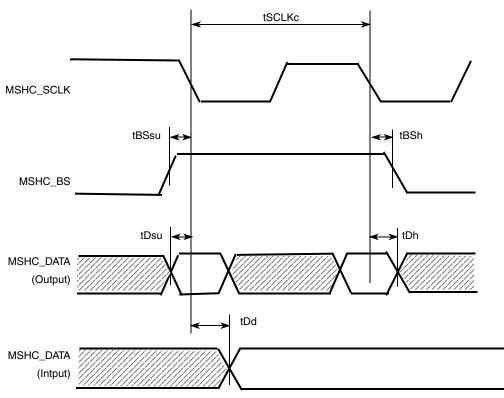

The MSHC is located between the AIPS and the Sony Memory Stick and provides support for data transfers between the i.MX31/i.MX31L and the Memory Stick (MS). The memory stick host controller consists of two sub modules; the MSHC gasket and the Sony Memory Stick Host Controller (SMSC). The SMSC module, which is the actual memory stick host controller, is compatible with Sony Memory Stick Ver 1.x and Memory Stick PRO. The gasket connects the AIPS IP bus to the SMSC interface to allow communication and data transfers via the IP Bus.

The MSHC gasket uses a reduced IP Bus interface that supports the IP bus read/write transfers that include a back-to-back read or write {mshc\_rd\_wr\_data,back\_to\_back\_rw, back\_to\_back\_complex}. DMA transfers also take place via the IP Bus interface.{mshc\_sdma}.

A transfer can be initiated by the SDMA or the host (through AIPS) in response to an MSHC DMA request or interrupt. The SMSC has two SDMA address modes—a single address mode and a dual address mode.

The MSHC is set to dual address mode for transfers with the SDMA. In dual address mode, when the MSHC requests a transfer with the DMA request (XDRQ), the SDMA will initiate a transfer to the MSHC.

#### NOTE

All details regarding the operation of the SMSC module can be found separately in "*Memory Stick/Memory Stick PRO Host Controller IP Specification 1.3*".

### 2.3.19 PCMCIA Host Adapter (PCMCIA)

The PCMCIA Host Adapter provides the control logic for PCMCIA socket interfaces, and requires some additional external analog power switching logic and buffering. The PCMCIA host adapter module is fully compliant with the PCMCIA standard release 2.1 (PC Card -16) and supports one PCMCIA socket. The adapter supports hot-insertion, card detection and removal, CompactFlash<sup>®</sup>, and ATA emulation in TrueIDE mode. The PCMCIA maps to common memory space, attribute memory space and I/O space. Each space can be up to 64Mbyte in size. As part of the EMI complex the PCMCIA shares its pins with the WEIM, SDRAMC, and NFC.

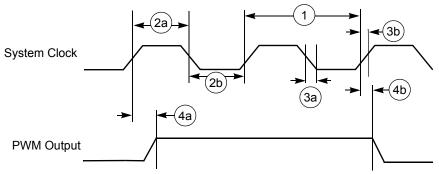

### 2.3.20 Pulse-Width Accelerator (PWM)

The PWM has a 16-bit counter and is optimized to generate sounds from stored sample audio images and it can also generate tones. It uses 16-bit resolution and a 4x16 data FIFO to generate sound. The following features characterize the PWM. the 16-bit up-counter has a source selectable clock with 4 x 16 FIFO to minimize interrupt overhead. Clock in frequency is controlled by a12-bit prescaler for division of clock. Capable of sound and melody generation the PWM has an active high or active low configurable output and can be programmed to be active in low power and debug modes. The PWM can be programmed to generate interrupts at compare and rollover events.

### 2.3.21 Random Number Generator Accelerator (RNGA)

The RNGA module is a digital integrated circuit capable of generating 32-bit random numbers. The RNGA is designed to comply with FIPS-140 standards for randomness and non-determinism. The random bits are generated by clocking shift registers with clocks derived from ring oscillators. The configuration of the shift registers ensures statistically good data (that is, data that looks random). The oscillators with their unknown frequencies provide the required entropy needed to create random data.

It is important to note that there is no known cryptographic proof showing that this is a secure method of generating random data. In fact, there may be an attack against the random number generator described in this document if its output is used directly in a cryptographic application (the attack is based on the linearity of the internal shift registers). Due to lack of a secure method and the potential for attacks, Freescale Semiconductor recommends that the random data produced by this module be used as an input seed to a NIST approved (based on DES or SHA-1) or cryptographically secure (RSA Generator or BBS Generator) random number generation algorithm. It is also recommended that other sources of entropy be used along with the RNGA to generate the seed to the pseudo-random algorithm. But this is optional. The more random sources combined to create the seed the better.

The RNGA uses a 32-bit IP Bus slave interface and contains a  $16 \times 32$  FIFO. It provides a Secure mode or operations as well as a power saving mode

### 2.3.22 Real Time Clock (RTC)

The RTC module maintains the system clock, provides stopwatch, alarm, and interrupt functions, and supports the following features.

• Full clock—days, hours, minutes, seconds

- Minute countdown timer with interrupt

- Programmable daily alarm with interrupt

- Sampling timer with interrupt

- Once-per-day, once-per-hour, once-per-minute, and once-per-second interrupts

- Operation at 32.768 kHz, 32 kHz, or 38.4 kHz (determined by reference clock crystal)

The prescaler converts the incoming crystal reference clock to a 1 Hz signal which is used to increment the seconds, minutes, hours, and days TOD counters. The alarm functions, when enabled, generate RTC interrupts when the TOD settings reach programmed values. The sampling timer generates fixed-frequency interrupts, and the minute stopwatch allows for efficient interrupts on very small boundaries.

### 2.3.23 Run-Time Integrity Checker (RTIC)

The RTIC is one of the security components in the i.MX31 and i.MX31L. Its purpose is to ensure the integrity of the peripheral memory contents and assist with boot authentication. The RTIC has the ability to verify the memory contents during system boot and during run-time execution. If the memory contents at runtime fail to match the hash signature, an error in the security monitor is triggered.

The RTIC provides SHA-1 message authentication and receives input via the DMA (AMBA-AHB Lite bus master) interface. It uses segmented data gathering to support non-contiguous data blocks in memory (up to two segments per block) and works during and with High Assurance Boot (HAB) process. It provides Secure-scan DFT security and support for up to four independent memory blocks. The RTIC has both a programmable DMA bus duty cycle timer and its own watchdog timer.

The RTIC operates in two primary modes: One time hash mode and continuous hash mode.

The One time hash mode is used during HAB for code authentication or one time integrity checking during which it stores the hash result internally and signals the ARM11 using an interrupt. In Continuous hash mode the RTIC is used continuously to verify integrity of memory contents by checking re-generated hash against internally stored values and interrupts host only if error occurs.

#### 2.3.24 Security Controller Module (SCC)

Security and security services, in an embedded or data processing platform, refer to the i.MX31 and i.MX31L processor's ability to provide mandatory and optional information protection services. Information in this context refers to all embedded data, both program store and data load. Therefore, a secure platform is intended to protect information/data from unauthorized access in the form of inspection (read), modification (write) or execution (use). Security assurance refers to the degree of confidence that security claims are actually met and is therefore associated with the resources available to, and the integrity of, a given security design.

The SCC is a hardware security component composed of two subblocks, the Secure RAM and the Security Monitor Overall its primary functionality is associated with establishing a centralized security state controller and hardware security state with a hardware configured, unalterable security policy. It also provides an uninterruptedly hardware mechanism to detect and respond to threat detection signals

(specifically platform test access signals). It also serves as a device unique data protection/encryption resource to enable off chip storage of security sensitive data and an internal storage resource which automatically and irrevocably destroys plain text security sensitive data upon threat detection.

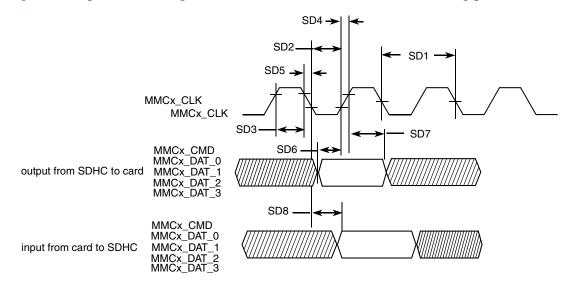

### 2.3.25 Secure Digital Host Controller (SDHC)

The MultiMediaCard (MMC), is a universal low cost data storage and communication media that is designed to cover a wide area of applications as electronic toys, organizers, PDAs and smart phones etc. The MMC communication is based on an advanced 7 pin serial bus designed to operate in a low voltage range. The Secure Digital Card (SD), is an evolution of MMC technology, with two additional pins in the form factor. It is specifically designed to meet the security, capacity, performance, and environment requirement inherent in newly emerging audio and video consumer electronic devices. The physical form factor, pin assignment and data transfer protocol are forward compatible with the MultiMediaCard with some additions. Under SD, it can be categorized into Memory and I/O. The memory card invokes a copyright protection mechanism that complies with the security of the SDMI standard. It will be faster and provide the capability for a higher memory capacity. The I/O card provides high-speed data I/O with low power consumption for mobile electronic devices.

The SDHC controls the MMC, SD memory, and I/O cards by sending commands to cards and performing data accesses to/from the cards. The Multimedia Card/Secure Digital Host module (MMC/SD) integrates both MMC support along with SD memory and I/O functions. The SDHC is fully compatible with the MMC System Specification Version 3.0 as well as compatible with the SD Memory Card Specification 1.0, and SD I/O Specification 1.0 with 1/4 channel(s). The maximum data rate in 4-bit mode is 100 Mbps. The SDHC uses a built-in programmable frequency counter for SDHC bus and provides a maskable hardware interrupt for SDIO Interrupt, Internal status & FIFO status and it has a 32x16-bit data FIFO buffer built-in.

### 2.3.26 SDMA

The SDMA architecture offers highly-competitive DMA Controller features combined with software-based virtual-DMA flexibility. Furthermore, it enables data transfers between peripheral I/O devices and internal/external memories.

The Smart Direct Memory Access (SDMA) controller is a critical piece of hardware in a highly integrated IC like a 3G Baseband chip or a Multimedia SoC. It helps maximizing system performance by off-loading the CPU in dynamic data routing. It contains a custom RISC core along with its RAM, ROM, the three DMA units, the CRC unit, and the scheduler.

The SDMA is used to execute short routines that perform DMA transfers; these routines or programs are called scripts hereafter. The Instruction-Set is composed of single cycle instructions with the exception of Load/Store instructions to the internal memory (RAM, ROM and memory mapped registers), to the registers of the DMA and CRC units, and Branch instructions that may require several cycles to execute. The SDMA core is interfaced to its own memory via the SDMA System Bus. The SDMA System Bus supports a 32-bit data path and a 16-bit address bus. DMA units are interfaced to the CORE via the Functional Unit Bus and use dedicated registers to perform DMA transfers.

The SDMA memory is constituted of a ROM and a RAM. The ROM contains startup scripts (for example, boot code) and other common utilities which are referenced by the scripts that reside in the RAM. The internal RAM is divided into a context area and a script area.

Every transfer channel requires one context area to keep the contents of all the CORE and units registers while it is inactive. Channel scripts are downloaded into the internal RAM by the SDMA using a dedicated channel that is started during the boot sequence. Downloads are invoked using command and pointers provided by the MCU or DSP. Every channel contains a corresponding channel script that is located in RAM and/or ROM; and it can be reconfigured independently on an "as needed" basis. This permits a wide range of SDMA functionality while using the lowest internal memory footprint possible. Channel scripts can be stored in an external, large capacity, FLASH memory and downloaded when needed. The SDMA can be configured with any mixture of scripts to enable an endless combination of supported services.

The scheduler is responsible for monitoring and detecting DMA requests, mapping them to channels and mapping individual channels to a pre-configured priority. At any point in time, the scheduler will present the highest priority channel requiring service to the SDMA core. A special SDMA core instruction is used to "conditionally yield" the current channel being executed to an eligible channel that requires service. If, and only if, an eligible channel is pending will the current execution of a channel be pre-empted. There are two "yield" instructions that differently determine the eligible channels: in the first version, eligible channels with a strictly higher priority than the current channel priority; in the second version ("yieldage"), eligible channels are pending channels are pending service through its 32 DMA request inputs. After a request is detected, the scheduler determines the channel(s) that is (are) triggered by this request and marks it (them) as pending in the "Channel Pending (EP)" register. The priorities of all the pending channels are combined and continuously evaluated in order to update the highest pending priority. The channel pending flag is cleared by the channel script when the transfer has completed.

The MCU Control module contains the control registers which are used to configure the 32 individual channels. There are 32 Channel Enable Registers: every register is used to map one DMA request to any desired combination of channels. The 32 Priority Registers are used to assign a programmable 1-of-7 level priority to every possible channel. This module also contains all other control registers that can be accessed by the MCU.

The DSP Control module, when available, contains a restricted set of registers that enable the DSP to control the channels that have been allocated by the MCU approximately the same set of registers as the MCU Control module. The SDMA is either owned by the MCU or the DSP, never by both at the same time for security reasons. The master (MCU or DSP) that owns the SDMA is able to allocate channels to the other master; the latter that is not controlling the SDMA has a limited access to its control registers.

The 32 DMA requests that are connected to the scheduler come from a variety of sources. The "receive register full" and "transmit register empty" signals that are found in UART and USB ports are typical examples of DMA requests that can be connected to the SDMA. These requests can be used to trigger a specific SDMA channel, or several channels. This feature can be used to realize a "just-in-time" data exchange between the two processors to relax the requirement to meet critical deadlines.

The embedded nature of the SDMA requires on-chip debug capability to assure product quality and reliability and to realize the full performance capabilities of the core. The OnCE compatible debug port

includes support for setting breakpoints, Single-Step & Trace and register dump capability. In addition, all memory locations are accessible from the debug port.

### 2.3.27 Subscriber Identification Module (SIM)

The SIM Interface Module (SIM) is designed to facilitate communication to SIM cards or Eurochip pre-paid phone cards. The SIM module has two ports that can be used to interface with the various cards. The interface with the MCU is via a 16-bit connection, The SIM module I/O interface can be operated in one of three modes of operation.

**Two wire interface.** In this mode both the IC pin RX and IC pin TX are used to interface to the smartcard. This is activated by resetting the 3volt bit in the port control register to a "0".

**External one wire interface**. In this mode the IC pins RX and TX are tied together external to the IC and routed to the smartcard. The 3volt bit in the port control register is reset to a "0" and the OD bit in the OD\_CONFIG register is set to a "1". For this interface to work properly the IC pin (RX-TX) must be pulled high by a resistor. The value should be selected small enough to give a fast enough rise time.

**Internal one wire interface.** In this mode the IC pin TX is routed to the smartcard. The receive pin RX is connected to the TX pin internal to the IC. The 3volt bit in the port control register is reset to a "1" and the OD bit in the OD\_CONFIG register is set to a "1". For this interface to work properly the IC pin TX must be pulled high by a resistor. The value should be selected small enough to give a fast enough rise time.

### 2.3.28 Secure JTAG Controller (SJC)

The IEEE1149.1 JTAG test access port (TAP) supports IEEE1149.1 v2001 standard features, access to OnCE and ICE of each Core, debug features to improve controllability and absorbability of the Cores for debug purposes, manufacturing test features (special test modes, PLL bypass, memory BIST and Burn-in...). The SJC provides debug and test control with the maximum security and provide a flexible architecture for future derivatives or future multi-cores architecture (how to add-remove a Core, software and hardware implications). JTAG pins can be muxed to the PCS bus connectors.

The SJC operates at maximum 1/8 the slowest frequency of the accessed OnCE/ICE. For example in normal operation (no core in low-power mode), this frequency will be 1/8 of the SDMA frequency if this core is present in the TDI-TDO chain (serially connected with other cores or standalone). User needs also to take into account the 25MHz frequency limitation on the CE bus.

In addition, secure JTAG options are provided to protect debug resources from attacks by unauthorized users. The secure JTAG design prevents the debug architecture from compromising security.

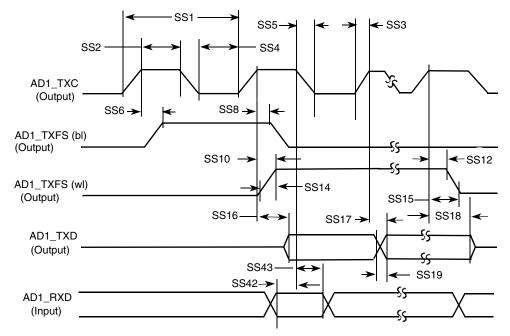

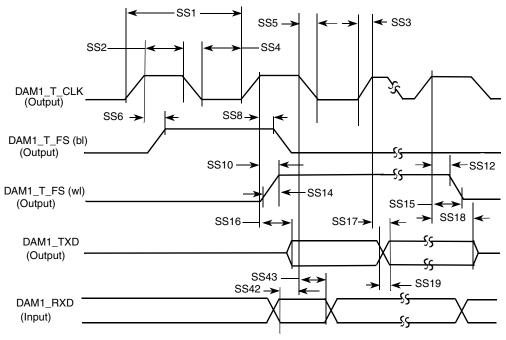

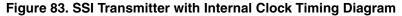

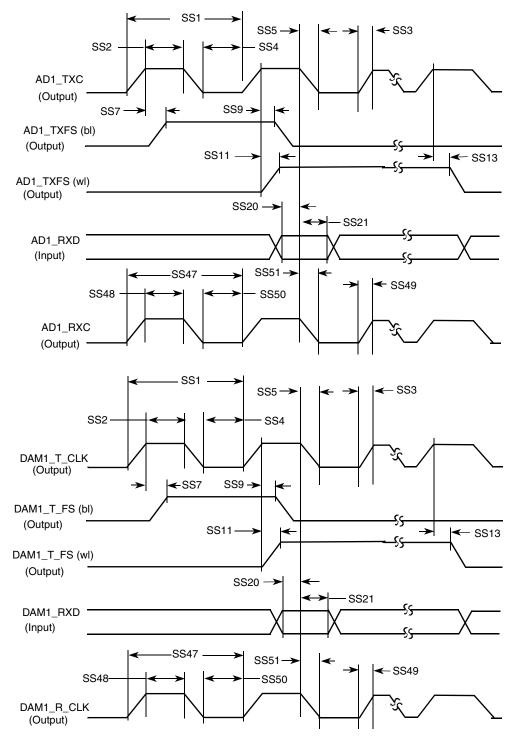

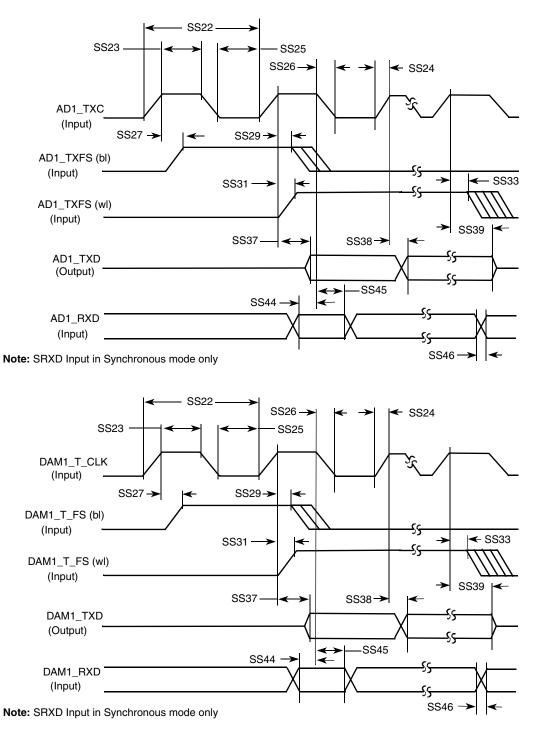

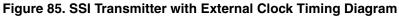

### 2.3.29 Synchronous Serial Interface (SSI)

The SSI is a full-duplex, serial port that allows the chip to communicate with a variety of serial devices. These serial devices can be standard codecs, Digital Signal Processors (DSPs), microprocessors, peripherals, and popular industry audio codecs that implement the inter-IC sound bus standard (I2S) and Intel AC97 standard.

SSI is typically used to transfer samples in a periodic manner. The SSI consists of independent transmitter and receiver sections with independent clock generation and frame synchronization.

The SSI contains independent (asynchronous) or shared (synchronous) transmit and receive sections with separate or shared internal/external clocks and frame syncs, operating in Master or Slave mode. The SSI can work in normal mode operation using frame sync and in Network mode operation allowing multiple devices to share the port with as many as thirty-two time slots. The SSI provides 2 sets of Transmit and Receive FIFOs. Each of the four FIFOs is 8x24 bits. The two sets of Tx/Rx FIFOs can be used in Network mode to provide 2 independent channels for transmission and reception. It also has programmable data interface modes such like I2S, LSB, MSB aligned and programmable word lengths. Other program options include frame sync and clock generation and programmable I2S modes (Master, Slave or Normal). Oversampling clock, ccm\_ssi\_clk available as output from SRCK in I2S Master mode.

In addition to AC97 support the SSI has completely separate clock and frame sync selections for the receive and transmit sections. In AC97 standard, the clock is taken from an external source and frame sync is generated internally. the SSI also has a programmable internal clock divider and Time Slot Mask Registers for reduced CPU overhead (for Tx and Rx both).

### 2.3.30 Universal Asynchronous Receiver/Transmitter (UART)

The i.MX31 and i.MX31L contain five UART modules, Each UART module is capable of standard RS-232 non-return-to-zero (NRZ) encoding format and IrDA-compatible infrared modes. The UART provides serial communication capability with external devices through an RS-232 cable or through use of external circuitry that converts infrared signals to electrical signals (for reception) or transforms electrical signals to signals that drive an infrared LED (for transmission) to provide low speed IrDA compatibility.

The UART transmits and receives characters containing either 7 or 8 bits (program selectable). To transmit, data is written from the IP data bus (Sky-Blue line interface) to a 32-byte transmitter FIFO (TxFIFO). This data is passed to the shift register and shifted serially out on the transmitter pin (TXD). To receive, data is received serially from the receiver pin (RXD) and stored in a 32-half-words-deep receiver FIFO (RxFIFO). The received data is retrieved from the RxFIFO on the IP data bus. The RxFIFO and TxFIFO generate maskable interrupts as well as DMA Requests when the data level in each of the FIFO reaches a programmed threshold level.

The UART generates baud rates based on a dedicated input clock and its programmable divisor. The UART also contains programmable auto baud detection circuitry to receive 1 or 2 stop bits as well as odd, even, or no parity. The receiver detects framing errors, idle conditions, BREAK characters, parity errors, and overrun errors.

### 2.3.31 Universal Serial Bus (USB)

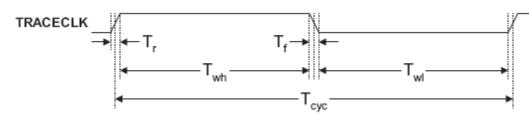

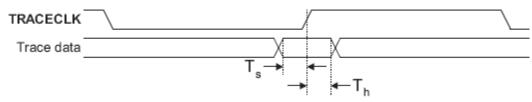

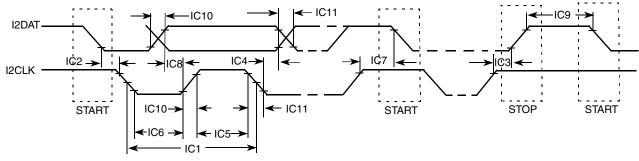

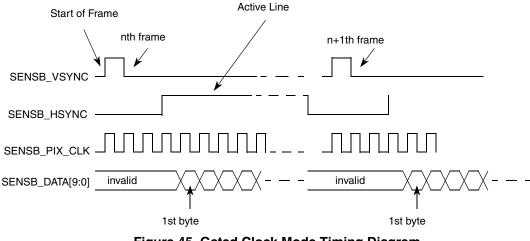

The i.MX31 and i.MX31L provides three USB ports. The USB module provides high performance USB On-The-Go (OTG) functionality, compliant with the USB 2.0 specification, the OTG supplement and the ULPI 1.0 Low Pin Count specification. The module consists of 3 independent USB cores, each controlling 1 USB port.