# **IDT79RC32334 and IDT79RC32332 Integrated Communications** Processors

(Y Revision)

# **RISCore™ 32300 Family**

# MM. Data She at the second sec **User Reference Manual**

June 2002

2975 Stender Way, Santa Clara, California 95054 Telephone: (800) 345-7015 • TWX: 910-338-2070 • FAX: (408) 330-1748 Printed in U.S.A. ©2001 Integrated Device Technology, Inc.

#### GENERAL DISCLAIMER

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

#### CODE DISCLAIMER

Code examples provided by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of the code examples below is completely at your own risk. IDT MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND CONCERNING THE NONINFRINGEMENT, QUALITY, SAFETY OR SUITABILITY OF THE CODE, EITHER EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICU-LAR PURPOSE, OR NON-INFRINGEMENT. FURTHER, IDT MAKES NO REPRESENTATIONS OR WARRANTIES AS TO THE TRUTH, ACCURACY OR COMPLETENESS OF ANY STATEMENTS, INFORMATION OR MATERIALS CONCERNING CODE EXAMPLES CONTAINED IN ANY IDT PUBLICATION OR PUBLIC DISCLOSURE OR THAT IS CONTAINED ON ANY IDT INTERNET SITE. IN NO EVENT WILL IDT BE LIABLE FOR ANY DIRECT, CONSEQUENTIAL, INCIDENTAL, INDIRECT, PUNITIVE OR SPECIAL DAMAGES, HOWEVER THEY MAY ARISE, AND EVEN IF IDT HAS BEEN PREVIOUSLY ADVISED ABOUT THE POSSIBILITY OF SUCH DAMAGES. The code examples also may be subject to United States export control laws and may be subject to the export or import laws of other countries and it is your responsibility to comply with any applicable laws or regulations.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

The IDT logo, Dualsync, Dualasnyc and ZBT are registered trademarks of Integrated Device Technology, Inc. IDT, QDR, RisController, RISCore, RC3041, RC3051, RC3052, RC3052, RC30541, RC32134, RC32332, RC32334, RC32355, RC32364, RC36100, RC4700, RC4640, RC64145, RC4650, RC5000, RC64474, RC64475, SARAM, Smart ZBT, SuperSync, SwitchStar, Terasync, Teraclock, are trademarks of Integrated Device Technology, Inc.

Powering What's Next and Enabling A Digitally Connected World are service marks of Integrated Device Technology, Inc. Q, QSI, SynchroSwitch and Turboclock are registered trademarks of Quality Semiconductor, a wholly-owned subsidiary of Integrated Device Technology, Inc.

#### Introduction

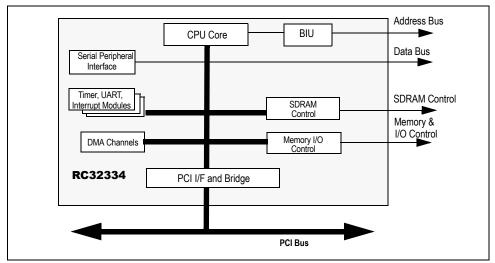

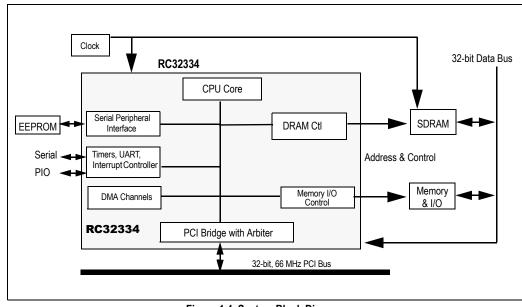

This user reference manual includes hardware and software information on the RC32334 (Y revision)<sup>1</sup>, a high performance integrated processor that combines a high performance 32-bit CPU core with system logic to provide direct connection to boot memory, main memory, I/O, and PCI. It also includes on-chip peripherals such as DMA channels, reset circuitry, interrupts, timers, and UARTs.

This is also the user reference manual for the RC32332 (Y revision) integrated processor. The information herein generally refers explicitly only to the RC32334 but is applicable to the RC32332 unless noted otherwise. Differences between the RC32334 and the RC32332 are identified in Appendix G.

#### **Additional Information**

Information not included in this manual such as mechanicals, package pin-outs, and electrical characteristics can be found in the data sheet for this device, which is available from the IDT website (www.idt.com) as well as through your local IDT sales representative.

#### **Content Summary**

Chapter 1, "RC32334 Device Overview," provides a complete introduction to the performance capabilities of the RC32334. Included in this chapter is a summary of features for the device as well as a system block diagram and internal register maps.

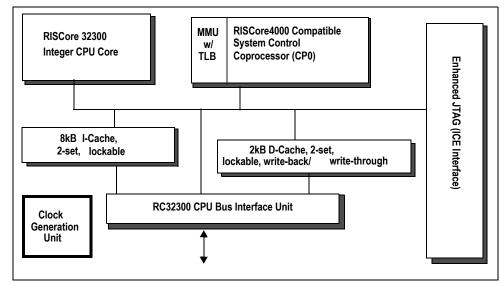

Chapter 2, "RC32300 CPU Core," describes the features of the RC32300 CPU core.

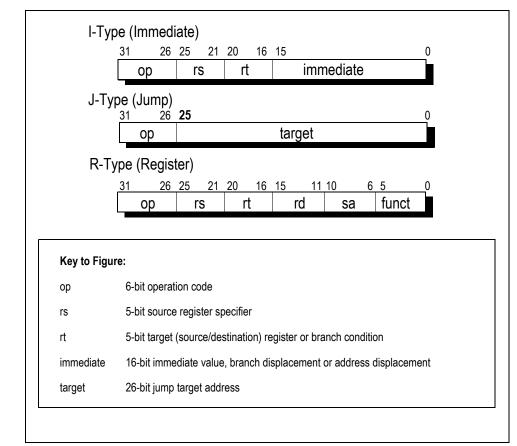

Chapter 3, "CPU Instruction Set Overview," presents a general overview on the three CPU instruction formats as well as the computational instructions of the MIPS architecture. Instruction set summary tables are also provided.

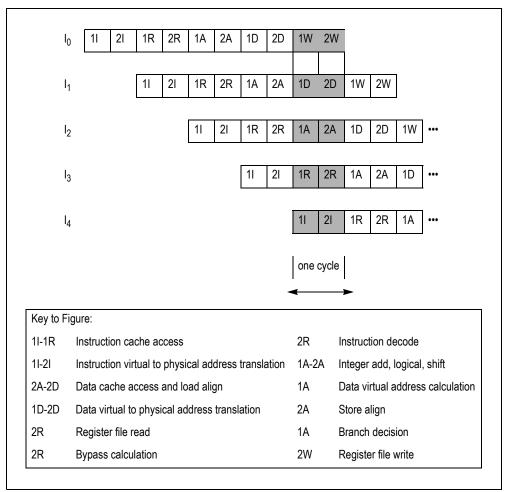

**Chapter 4, "CPU Pipeline Architecture,"** discusses pipeline features as well as interlock and exception handling of the device's RISCore<sup>™</sup> 32300.

**Chapter 5, "Memory Management,"** contains a discussion on the virtual-to-physical address translation technique, TLB management, and operation modes for the RC32334. Register formats and field description tables are also provided in this chapter.

**Chapter 6, "CPU Exception Processing,"** defines and describes the various exception types and handling processes for the RC32334. Also provided in this chapter are the CPO register formats, their field descriptions, and general exception handling flowcharts.

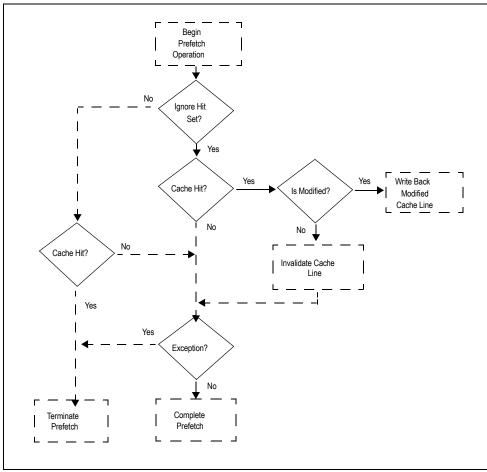

Chapter 7, "Cache Organization, Operation, and Coherency," includes a general discussion on the operation of cache as well as the more specific cache attributes of the RC32334. Flowcharts and various diagrams are provided to clarify the concepts discussed in this chapter.

Chapter 8, "RC32334 Internal Bus," presents a general overview of the RC32334's internal bus that provides a connection to internal peripherals and controllers.

Chapter 9, "External Local Bus Interface," presents a general overview of the RC32334's system bus that provides an easy connection to main memory and to peripherals.

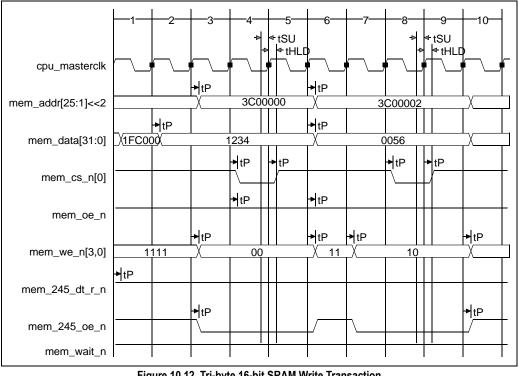

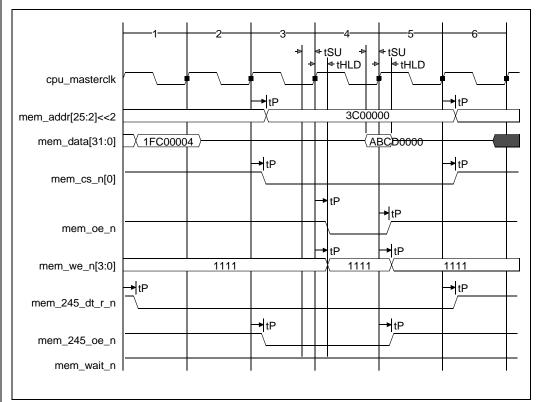

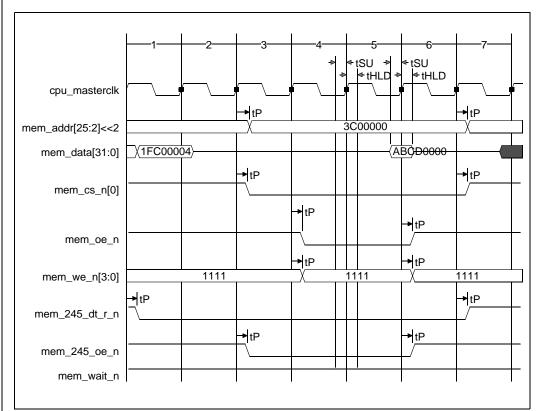

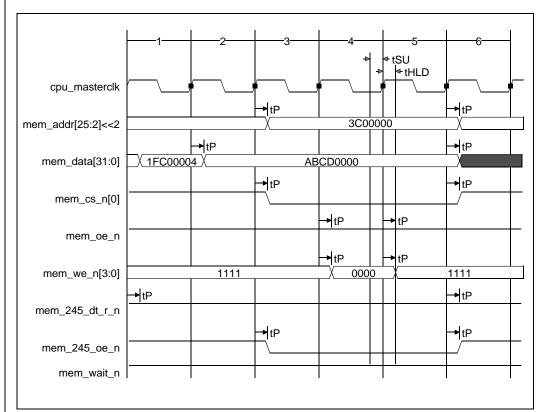

**Chapter 10, "Memory Controller,"** provides a functional overview on the CPU core, DMA or PCI bridge generated transactions. A block diagram, register maps, signal description table, and timing diagrams for various read and write operations are also included.

<sup>&</sup>lt;sup>1.</sup> For information on an earlier user manual that covers the Z revision, contact your IDT sales representative.

read and write transactions.

#### **Notes**

**Content Summary**

Chapter 12, "PCI Interface Controller," contains descriptions of the PCI host/satellite modes and master/target operations supported in the RC32334. Register maps and register field definitions are included.

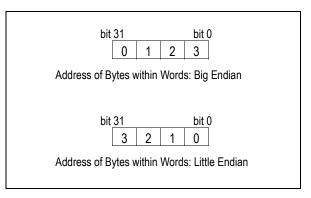

**Chapter 13**, "**DMA Controllers**," includes descriptions on the four general purpose DMA channels and the transfer operations supported. Byte swapping between big- and little-endian is also discussed and includes examples.

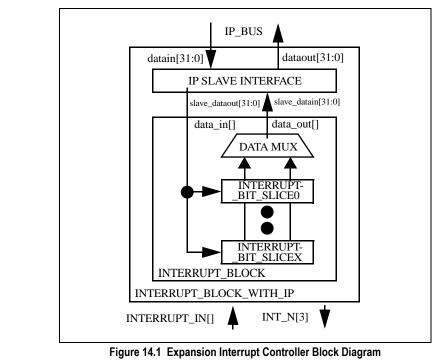

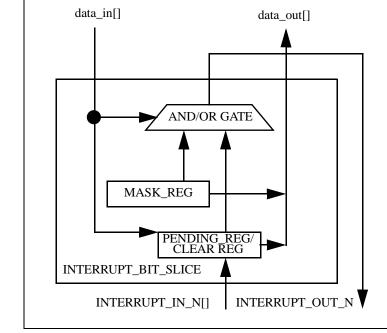

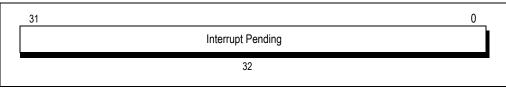

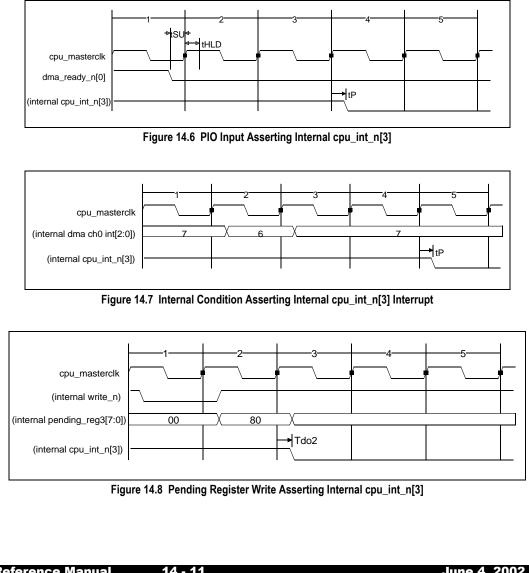

Chapter 14, "Expansion Interrupt Controller," provides a functional and operational overview on this controller. This chapter includes a block diagram, signal definitions and register mapping tables for each of the 14 groups supported.

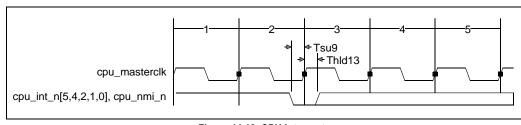

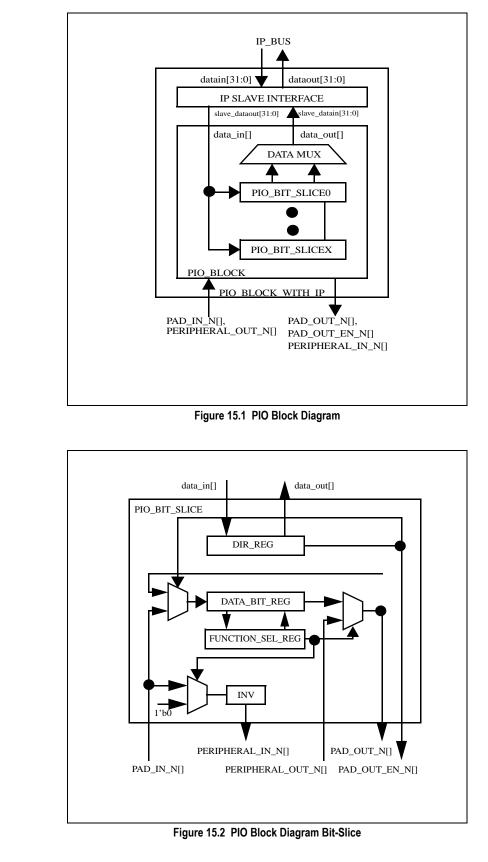

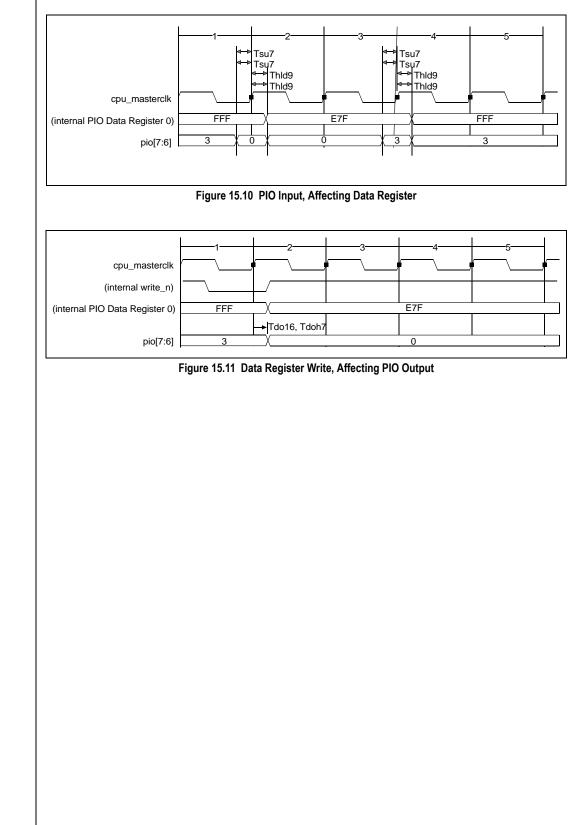

Chapter 15, "Programmable I/O (PIO) Controller," provides the signal descriptions, register mapping and programming information on the software programmable options of the RC32334's 15 peripheral pins.

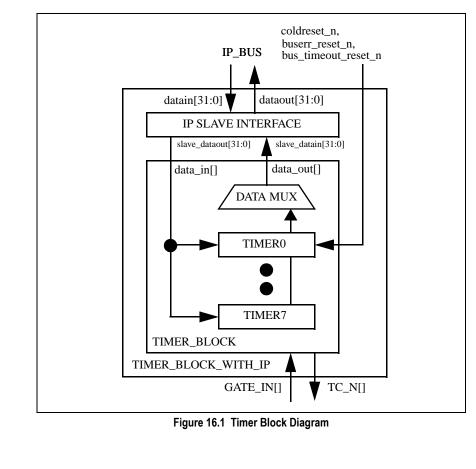

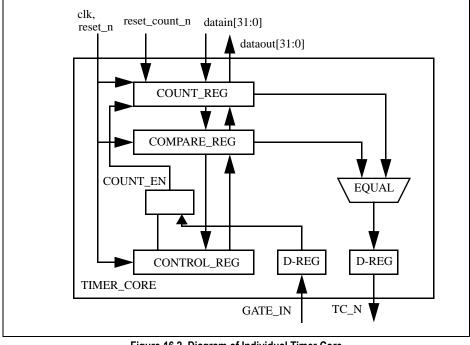

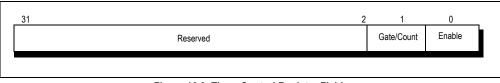

**Chapter 16, "Timer Controller,"** provides a user overview on the functions of the RC32334's nine onchip timers. A block diagram, signal definitions and register maps are included.

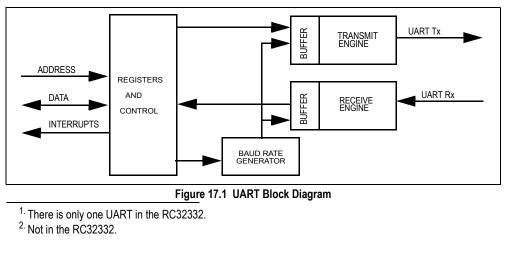

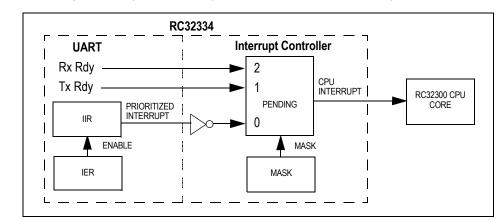

Chapter 17, "UART Controller," describes the operation of the two 16550 compatible UARTs available on the RC32334. Register maps and descriptions are included.

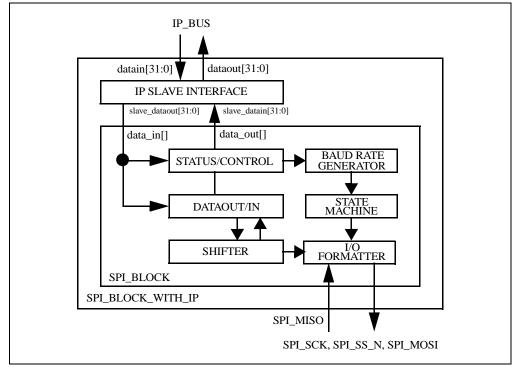

Chapter 18, "Serial Peripheral Interface," describes the properties and operations of this interface to low-cost serial peripherals.

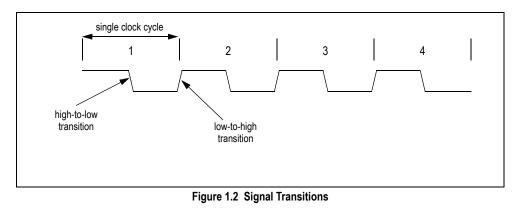

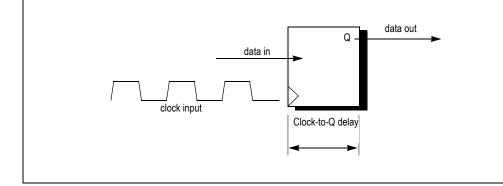

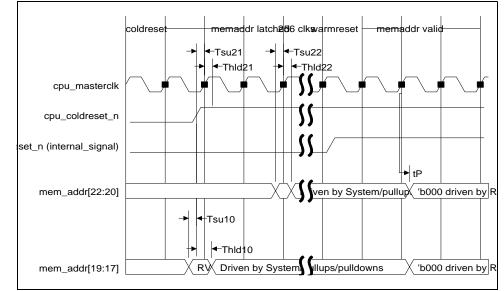

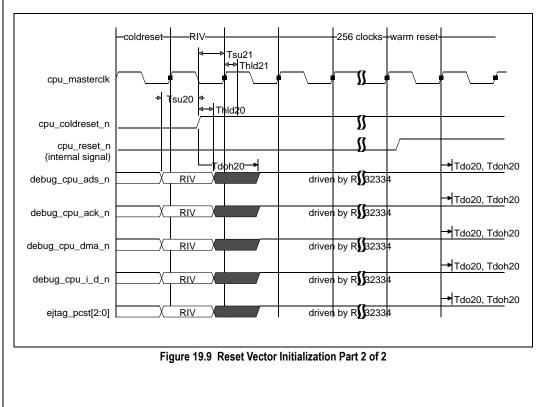

Chapter 19, "Clocking, Reset, and Initialization," provides a description of the clock signals that are used on the RC32334 processor and includes a discussion on the basic system clocks and system timing parameters. This chapter also provides a brief explanation on the power reduction modes for this device and a description of the RC32334 initialization and reset registers.

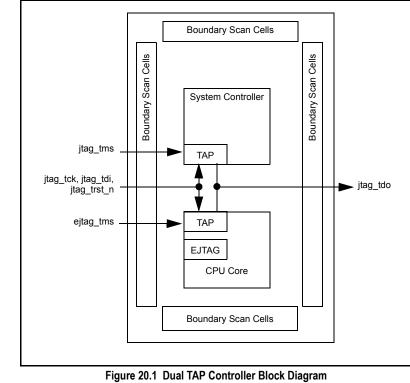

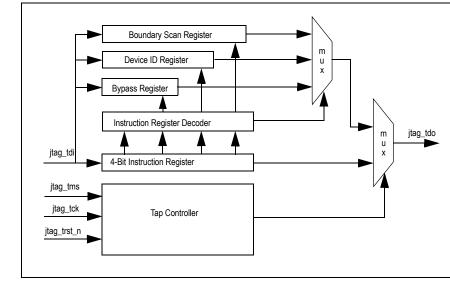

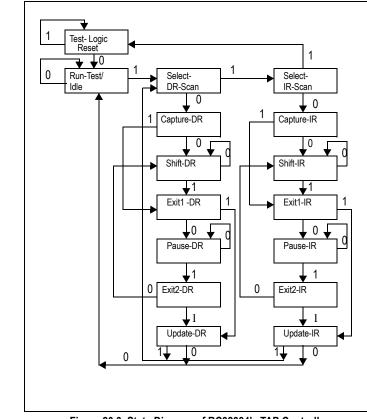

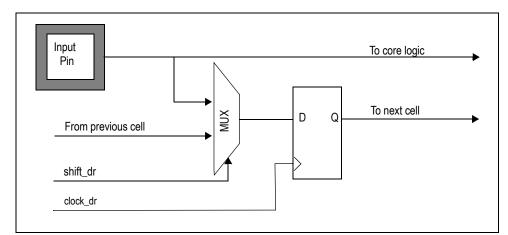

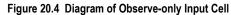

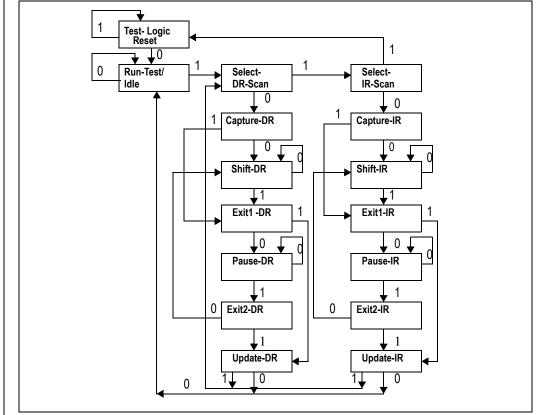

Chapter 20, "JTAG Boundary Scan," introduces the standard JTAG interface used for board-level debugging. A description on the Test Access Port (TAP) interface and TAP controller state assignments is also included.

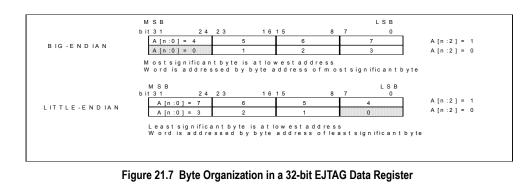

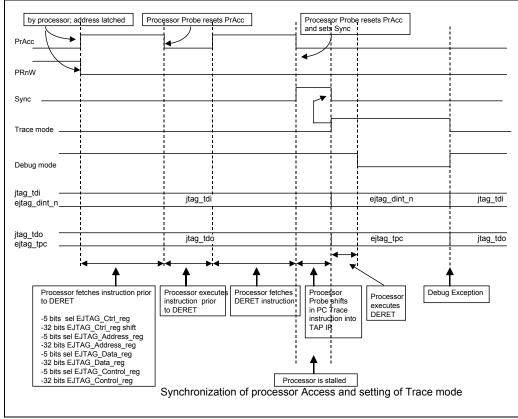

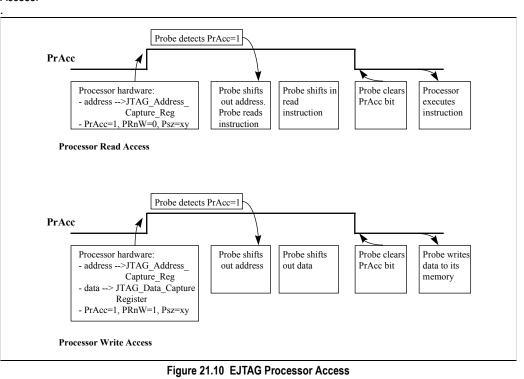

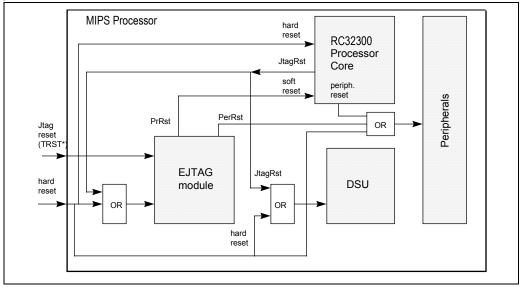

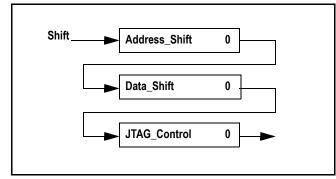

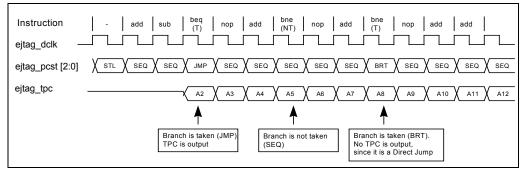

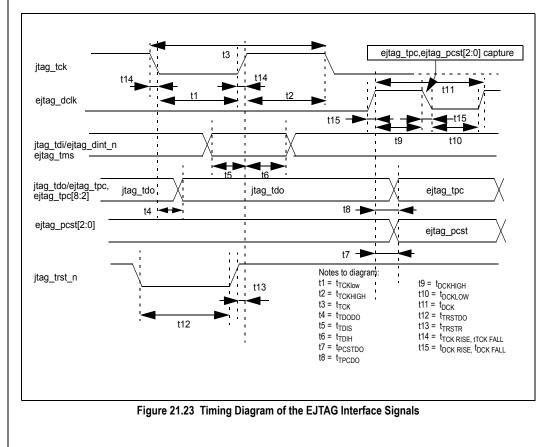

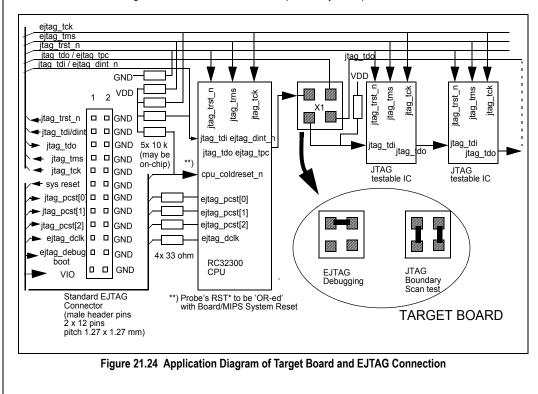

Chapter 21, "EJTAG (In-circuit Emulator) Interface," describes the Debug Support Unit (DSU). It covers the debug instructions added to the MIPS II ISA instruction set as well as support functions and registers for debugging.

Appendix A, "RC32300 CPU Core Enhancements to MIPS II ISA," discusses in detail architectural enhancements to the MIPS II ISA.

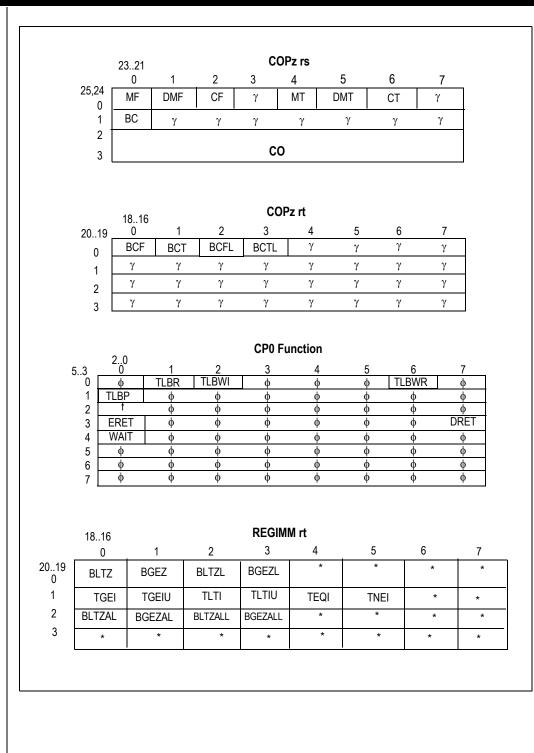

Appendix B, "Opcode Map," provides an opcode map.

Appendix C, "The Timing of Cache Operations," provides a table for primary data cache operations and a table for primary instruction cache operations, as well as caveats about cache operations.

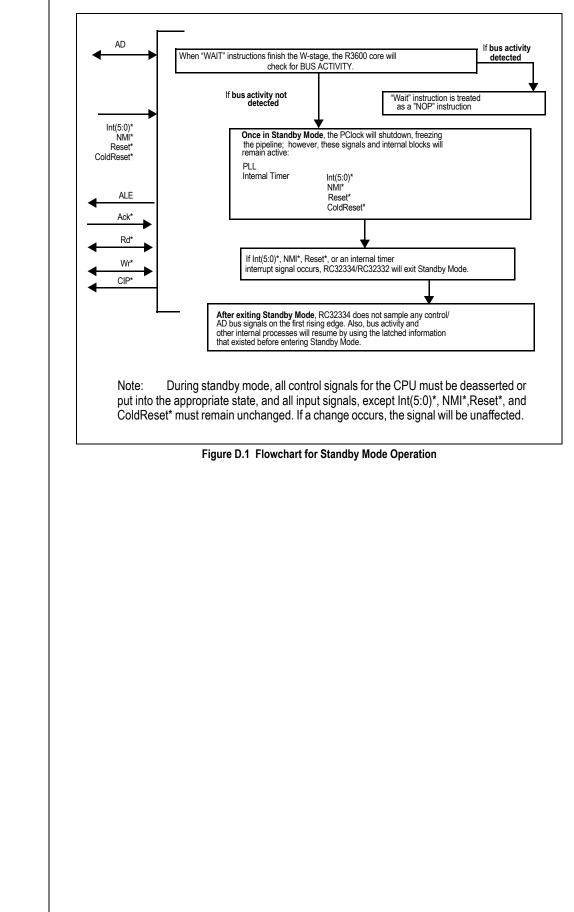

Appendix D, "RC32334/RC32332 Standby Mode Operation," discusses power reduction, in particular, the "Wait" instruction and the standby mode that follows this instruction.

Appendix E, "Coprocessor 0 Hazards," identifies the RC32334 CP0 hazards.

Appendix F, "Integer Multiply Scheduling," discusses integer multiply performance, defines instructions, and summarizes integer multiply and divide performance.

Appendix G, "RC32332 Differences," identifies the differences between the RC32334 and the RC32332.

#### **Revision History**

November 15, 2000: Initial publication.

**February 5, 2001**: In Chapter 12, separated PCI CPU Memory and I/O Space 1 Base Register section into two sections, one dealing with CPU Memory and the other with CPU I/O, and changed bit description to reflect CPU I/O Base uses [23:20] instead of [31:28].

**February 26, 2001**: Changed alternate function for uart\_tx[0] from PIO[3] to PIO[1] in Table 1.2 and G.4. In Chapter 15, clarified that timer\_tc\_n[0] is not present in the RC32332 and added a reference in the Signal Definitions section to Tables G.2 and G.3. In Appendix G, added two tables (G.2 and G.3) to highlight the differences in PIO pin name assignments between the RC32334 and RC32332.

**April 2, 2001**: Made the following changes in Chapter 18: added system clock formula under Serial Peripheral Clock Register section; removed "active" from description for bit 2 in table 18.4; changed SPSE register to SPSR register in Table 18.6; in Master Programming Example, item 1, changed formula in parentheses to 3.7 MHz (67/ [(8+1) \* 2]); in Master Programming Example, item 2, changed formula in parentheses to 3.7 / 2 = 1.85 MHz.

**May 17, 2001**: Table 17.6, "Interrupt Identity Register Fields and Descriptions," has been revised to show that for bits 3:1 (Current Interrupt field) the value 111 has the same status and priority level as the value 011. Also, in Table 11.2, under SDRAM Organization column, 2nd category from the bottom, the data now reads "2 Mb x 16 x 4 banks" instead of "4 Mb x 16 x 4 banks." Finally, in Table 11.6, for bit 28 (SDRAM Bank Size field), the value descriptions now omit any reference to 16M-bit and 64M-bit. These references were confusing because the RC32334 and RC32332 devices also support 128M-bit SDRAMs.

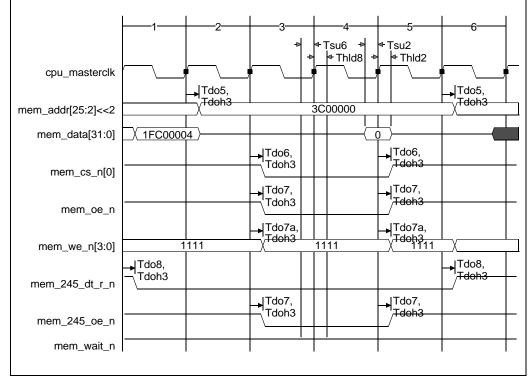

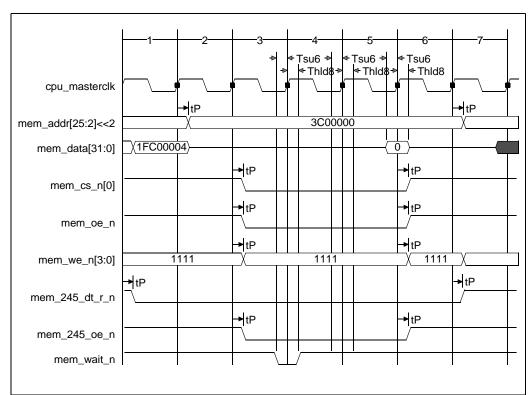

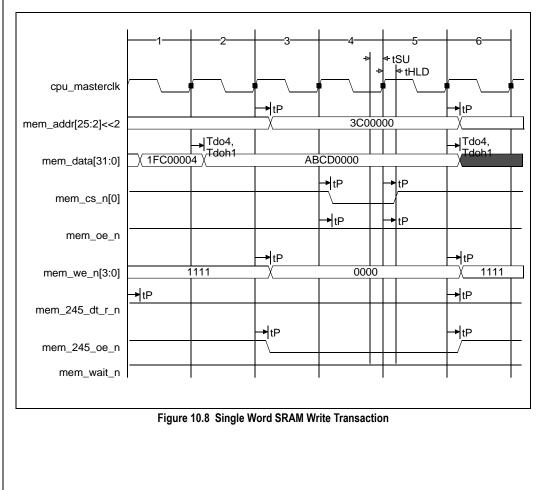

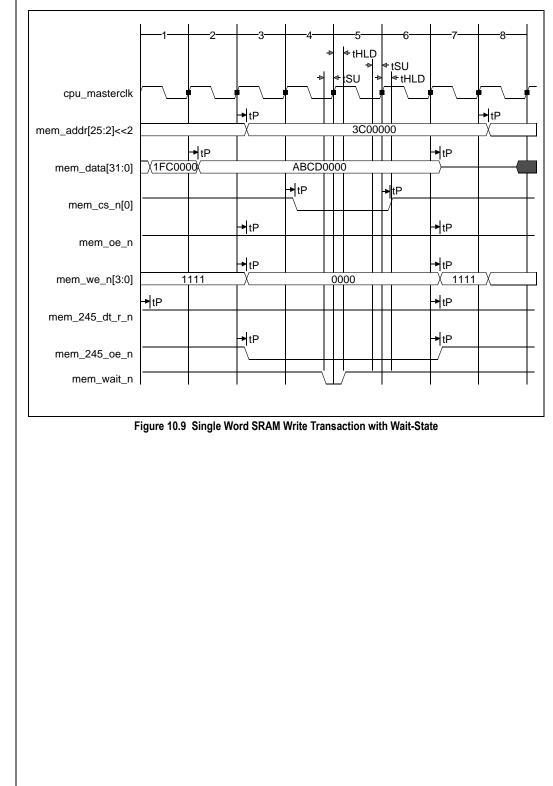

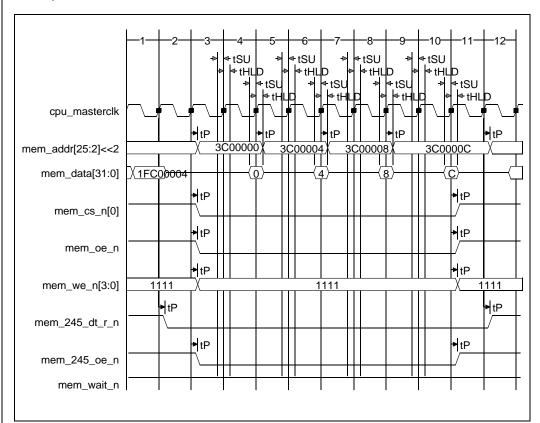

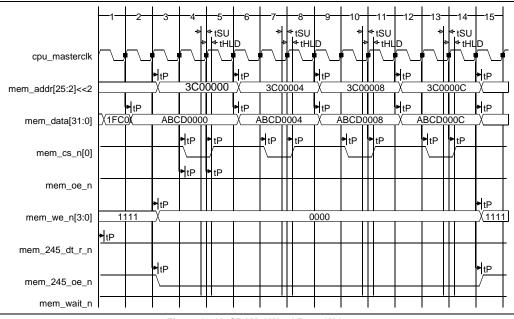

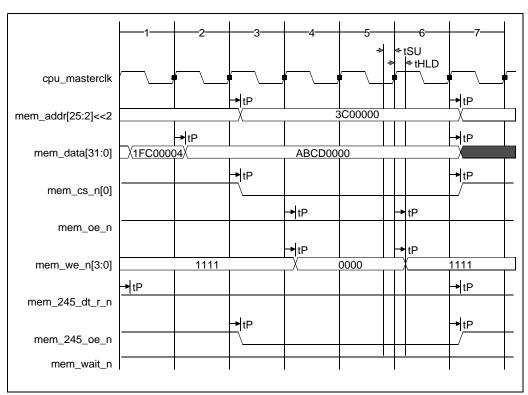

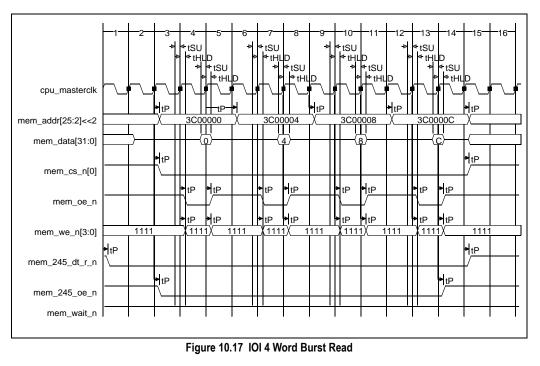

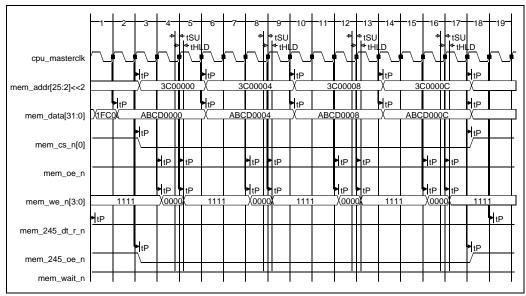

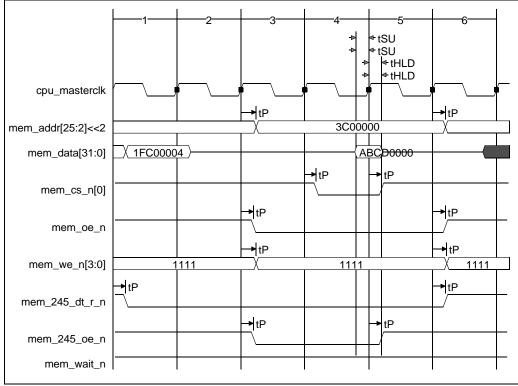

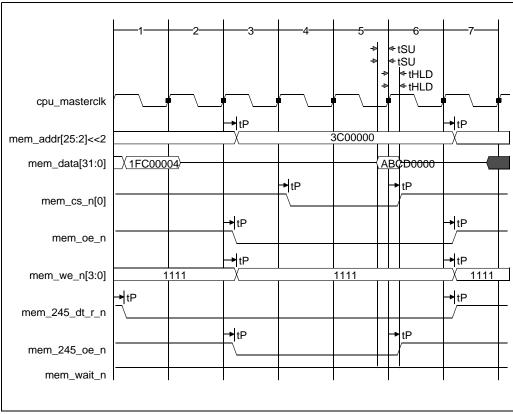

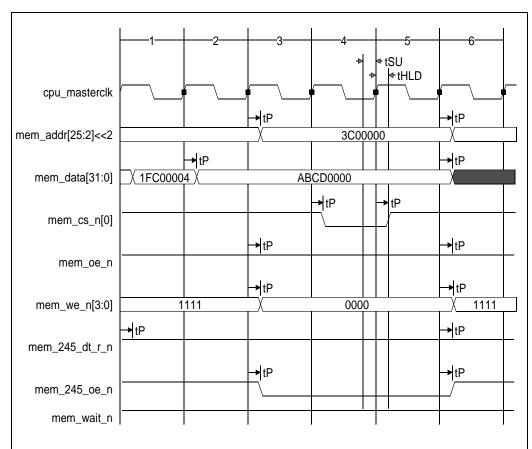

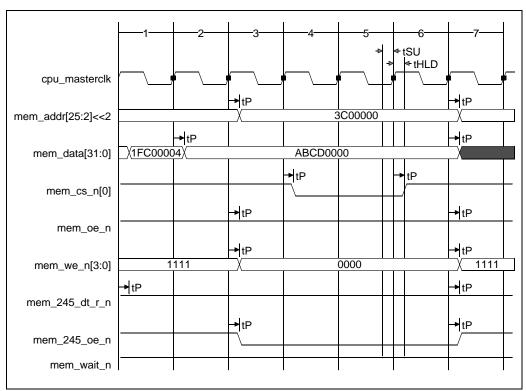

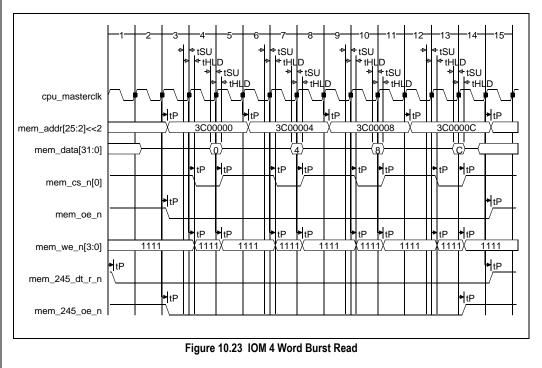

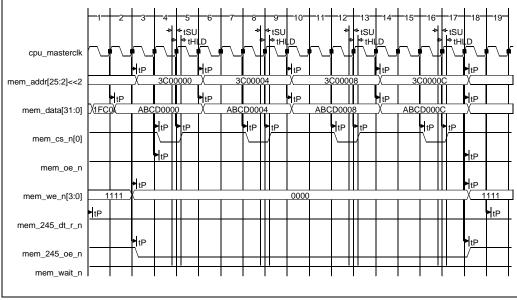

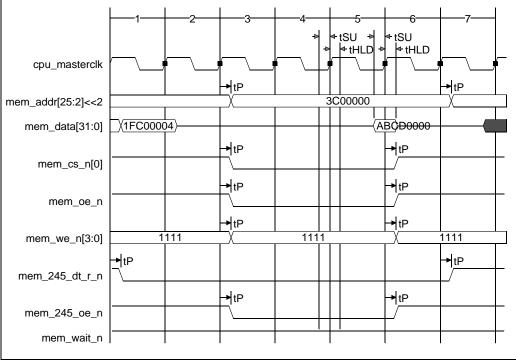

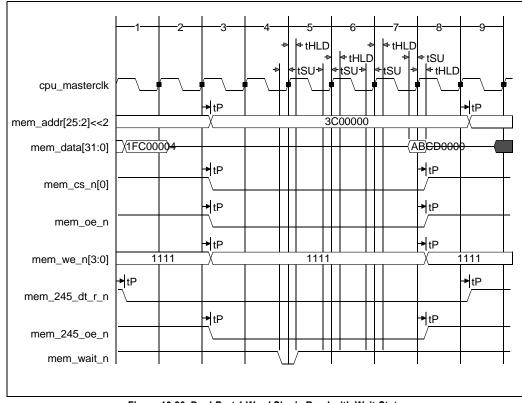

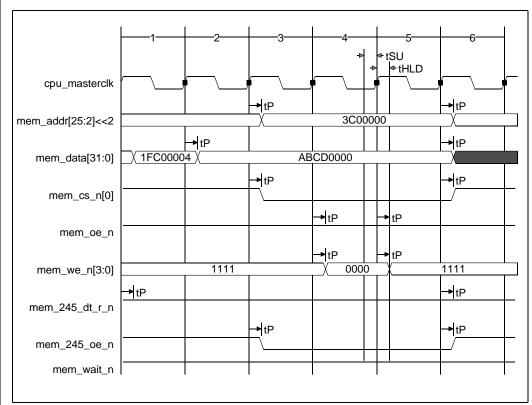

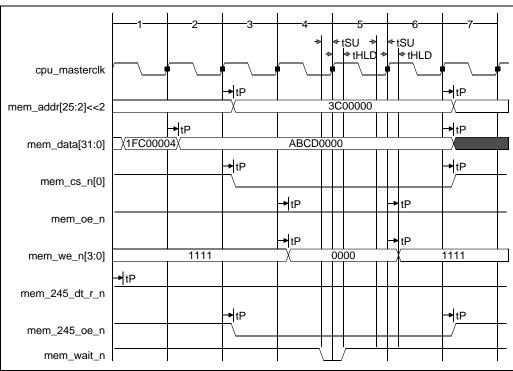

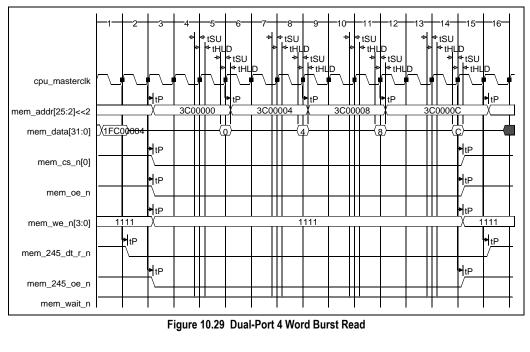

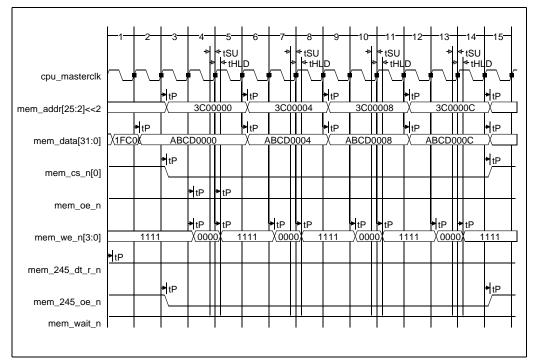

July 26, 2001: In Chapter 10, the bit address for mem\_addr[25:2] was changed from 40000 to 3C00000 in Figures 10.6 through 10.30.

June 4, 2002: Made the following changes based on the introduction of Y silicon: Chapter 8, Internal Bus—changes in bit 7 description in Table 8.12, changes in Table 8.13. Chapter 11, SDRAM Controller—added more SDRAM address multiplexing and control registers (SDRAM Secondary Control), changes to Tables 11.1 and 11.2, changes in SDRAM Initialization section. Chapter 12, PCI Interface—added CPU to PCI and PCI to CPU mapping diagrams, new Memory/IO Space Base register and PCI Memory/IO Base Address registers, Target FIFOs are 16 words deep, added PCI Target Control Register and New Feature sections, added additional fields in PCI Arbitration Register (Table 12.15), added 2 new base address registers, revised Tables 12.1, 12.7, and 12.12, changed Reset for System Identification Number from 00h to 01h (Table 12.24). Chapter 13, DMA Controllers—added New Feature Configuration register, added SDRAM to PCI Arbitration Algorithm field, and revised function description for interrupt\_n[3] and n[4] pins in Table 13.3. PIO chapter—added New Feature Register. Clocking, Reset and Initialization chapter—revised description in first row of Table 19.1.

## **Table of Contents**

Notes

#### About This Manual

| Introduction       | Í |

|--------------------|---|

| Content Summary    | i |

| Revision Historyii | i |

#### 1 RC32334 Device Overview

| Verview                                                  |      |

|----------------------------------------------------------|------|

| Foreword                                                 | 1-1  |

| Introduction                                             | 1-1  |

| Block Diagram                                            | 1-1  |

| Documentation Conventions and Definitions                |      |

| Signal Terminology                                       |      |

| List of Features                                         | 1-3  |

| System Block Diagram                                     | 1-4  |

| System Overview                                          | 1-4  |

| Pin Description Table — RC32334                          | 1-6  |

| Pin Description Table — RC32332                          | 1-13 |

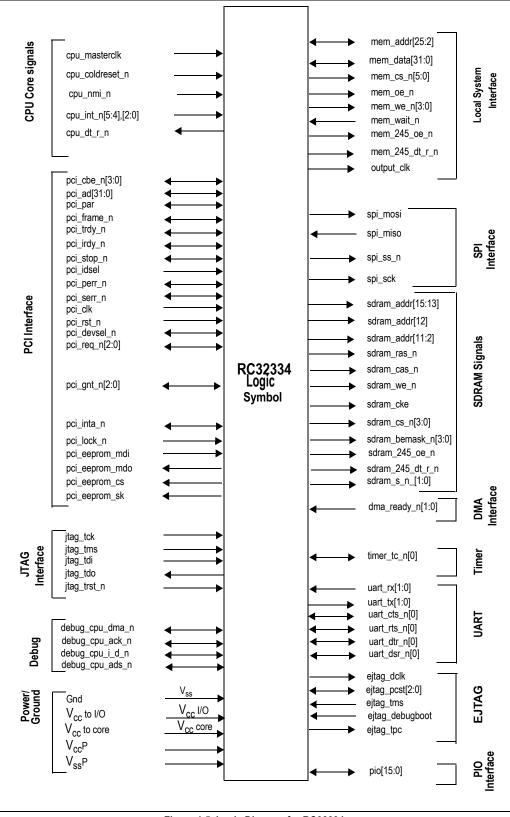

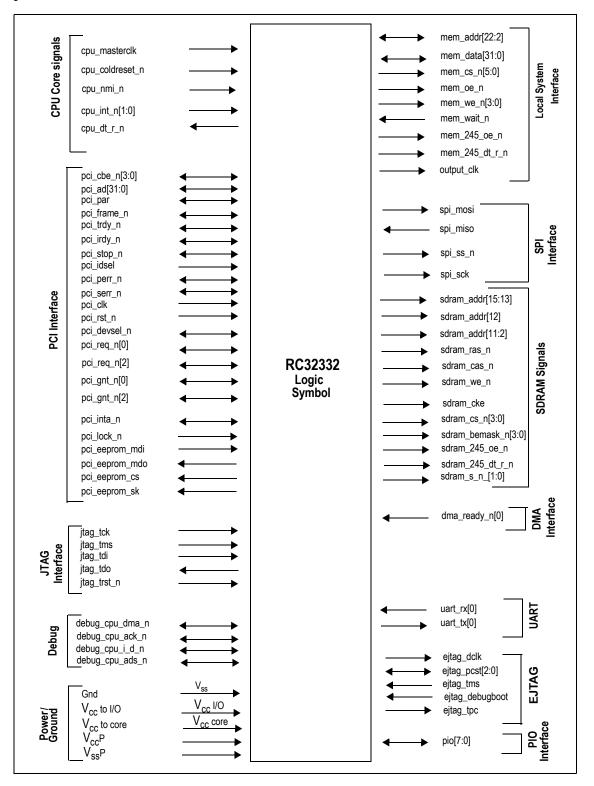

| Logic Diagram — RC32334                                  | 1-19 |

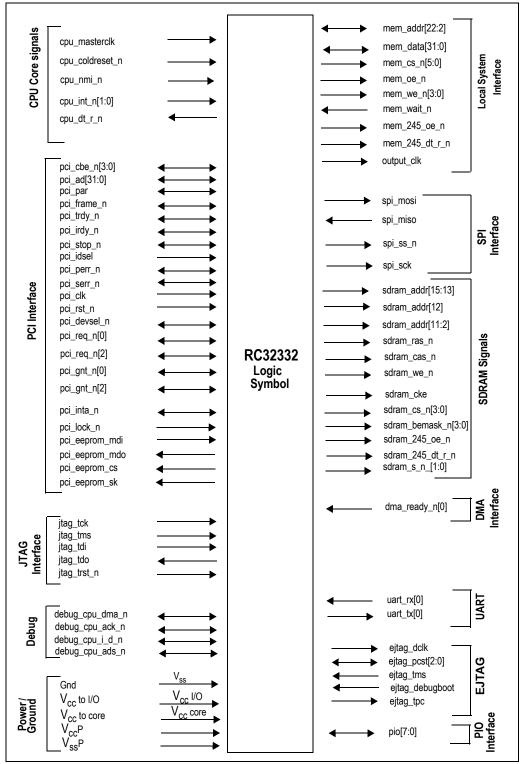

| Logic Diagram — RC32332                                  | 1-20 |

| Typical RC32334 Memory Map                               | 1-21 |

| RC32334 Internal Register Map Addresses and              |      |

| Definitions                                              | 1-21 |

| BIU Control Registers                                    |      |

| Base Address and Base Mask Registers                     |      |

| Memory Control Registers                                 |      |

| DRAM Memory Controller Registers                         |      |

| Expansion Interrupt Registers                            |      |

| Programmable I/O Registers<br>Timer Controller Registers |      |

| UART Control Registers                                   |      |

| Serial Peripheral Interface Registers                    |      |

| DMA Control Registers                                    |      |

| PCI Interface Control Registers                          |      |

#### 2 RC32300 CPU Core

| Introduction              | 2-1 |

|---------------------------|-----|

| Performance Overview      | 2-1 |

| RC32300 CPU Core Features | 2-1 |

| RC32300 CPU Overview      | 2-2 |

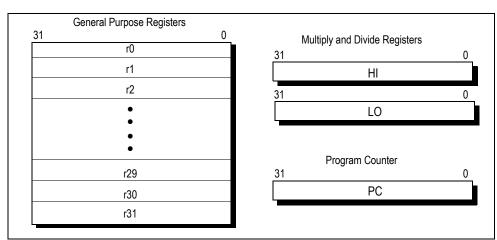

| CPU Registers             | 2-2 |

| Configuration             | 2-3 |

| CP0 Considerations        | 2-4 |

| 2-4 |

|-----|

| 2-4 |

| 2-4 |

| 2-4 |

|     |

#### 3 CPU Instruction Set Overview

| Introduction                                      | 3-1 |

|---------------------------------------------------|-----|

| CPU Instruction Formats                           | 3-1 |

| Load and Store Instructions (I-type)              | 3-2 |

| Scheduling a Load Delay Slot                      |     |

| Defining Access Types                             | 3-2 |

| Computational Instructions (R-type and I-type)    | 3-3 |

| Operations with 32-bit Operands                   | 3-3 |

| Cycle Timing for Multiply and Divide Instructions | 3-3 |

| Jump & Branch Instructions (J-type and R-type)    |     |

| Overview of Jump Instructions                     | 3-3 |

| Overview of Branch Instructions                   | 3-4 |

| Special Instructions (R-type)                     | 3-4 |

| Exception Instructions                            | 3-4 |

| Coprocessor Instructions (I-type)                 | 3-4 |

| Summary of CPU Supported Instruction Sets         | 3-4 |

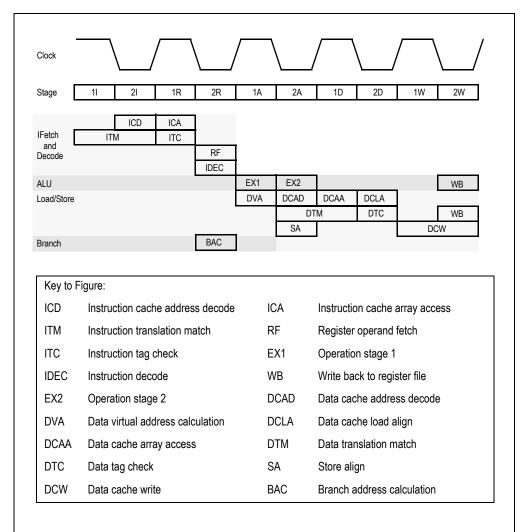

#### 4 CPU Pipeline Architecture

| Introduction                      | 4-1 |

|-----------------------------------|-----|

| CPU Pipeline Stages               | 4-1 |

| 1I - Instruction Fetch, Phase One | 4-2 |

| 2I - Instruction Fetch, Phase Two | 4-2 |

| 1R - Register Fetch, Phase One    | 4-2 |

| 2R - Register Fetch, Phase Two    | 4-2 |

| 1A - Execution, Phase One         | 4-2 |

| 2A - Execution, Phase Two         | 4-2 |

| 1D - Data Fetch, Phase One        |     |

| 2D - Data Fetch, Phase Two        |     |

| 1W - Write Back, Phase One        |     |

| 2W - Write Back, Phase Two        | 4-3 |

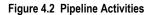

| Branch Delay                      | 4-3 |

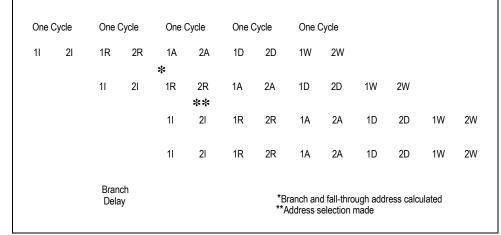

| Load Delay                        | 4-4 |

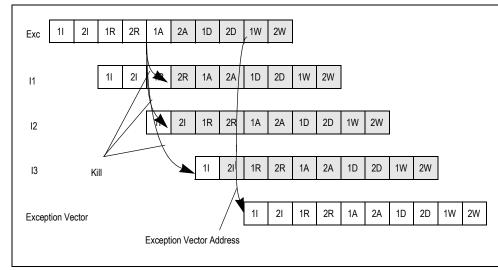

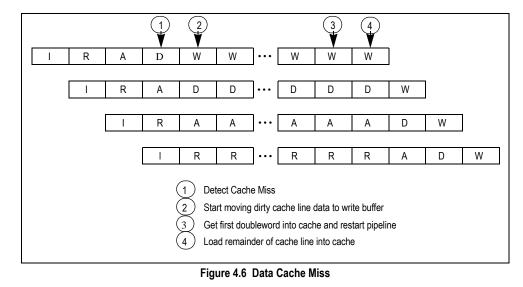

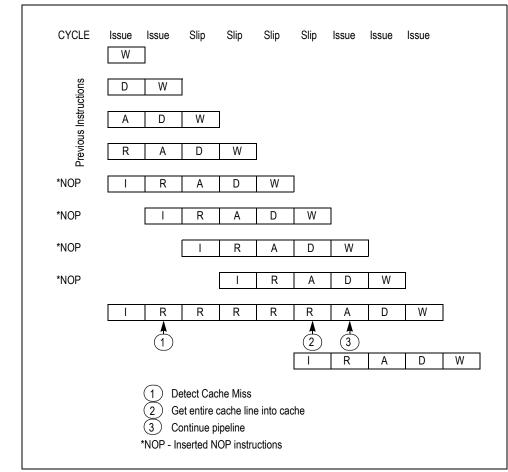

| Interlock and Exception Handling  | 4-4 |

| Exception Conditions              |     |

| Stall Conditions                  | 4-5 |

| Slip Conditions                   | 4-6 |

#### 5 Memory Management

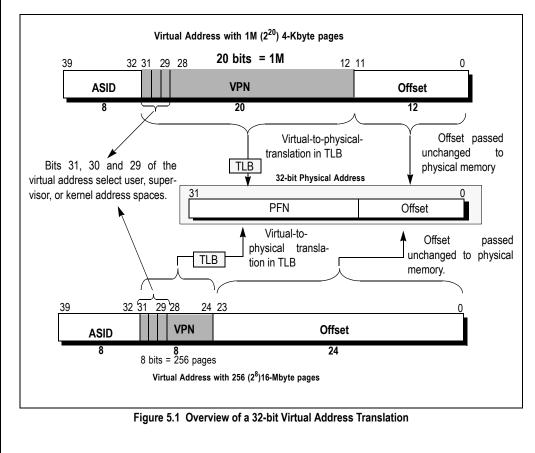

| Introduction                            | 5-1 |

|-----------------------------------------|-----|

| Virtual-to-Physical Address Translation | 5-1 |

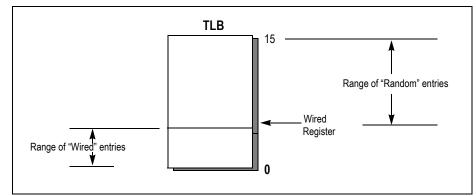

| TLB Management                          | 5-2 |

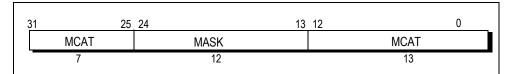

|   | MMU Register Descriptions                                 | 5-3 |

|---|-----------------------------------------------------------|-----|

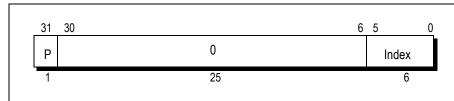

|   | Index Register (0)                                        | 5-3 |

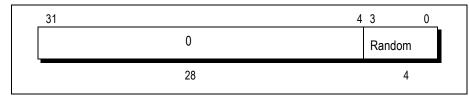

|   | Random Register (1)                                       | 5-4 |

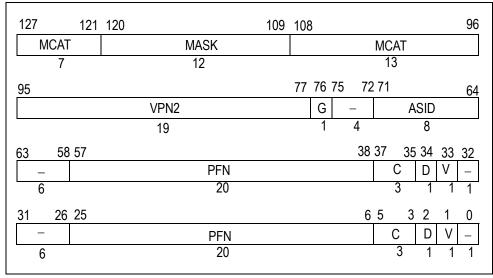

|   | EntryLo0 (2), and EntryLo1 (3) Registers                  |     |

|   | Context Register (4)                                      |     |

|   | PageMask Register (5)                                     | 5-6 |

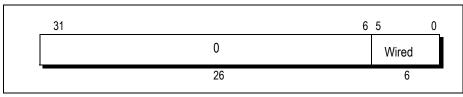

|   | Wired Register (6)                                        |     |

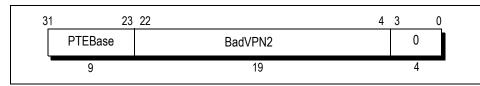

|   | Bad Virtual Address Register (BadVAddr) (8)               | 5-7 |

|   | EntryHi Register (10)                                     | 5-8 |

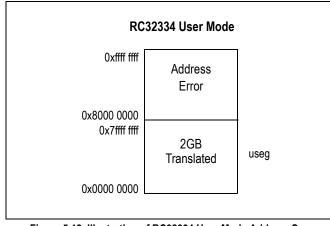

|   | Kernel/User Operating Modes and Addressing                | 5-8 |

|   | User Mode                                                 | 5-8 |

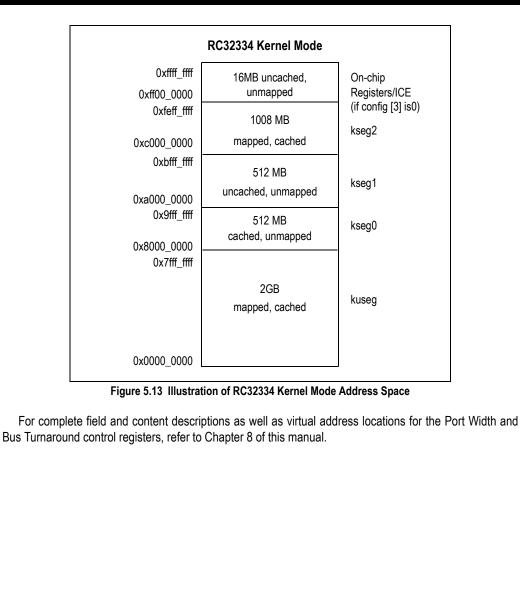

|   | Kernel Mode                                               | 5-9 |

| 6 | CPU Exception Processing                                  |     |

| U |                                                           | 6.4 |

|   | Introduction                                              |     |

|   | Exception Processing Registers                            |     |

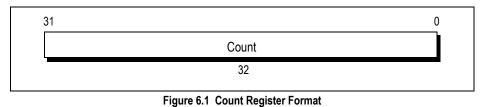

|   | Count Register (9)                                        |     |

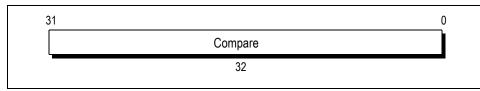

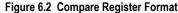

|   | Compare Register (11)                                     |     |

|   | Status Register (12)                                      |     |

|   | Status Register Modes and Access States                   |     |

|   | Cause Register (13)                                       |     |

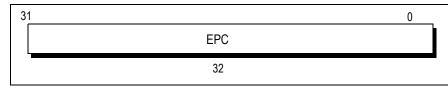

|   | Exception Program Counter (EPC) Register (14)             |     |

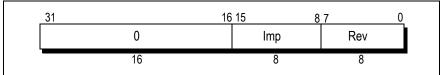

|   | Processor Revision Identifier (PRId) Register (15)        |     |

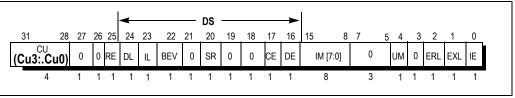

|   | Config Register (16)                                      |     |

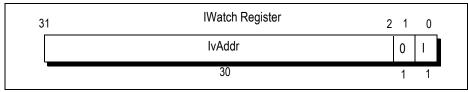

|   | IWatch Register (18)                                      |     |

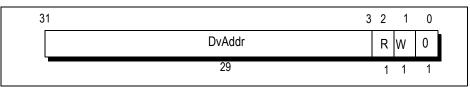

|   | DWatch Register (19)                                      |     |

|   | Debug Exception Program Counter (DebugEPC) Register (23)  |     |

|   | Debug Register (24)                                       |     |

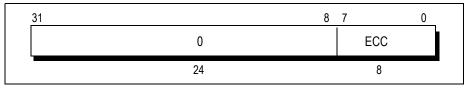

|   | Error Checking and Correcting (ECC) Register (26)         |     |

|   | Cache Error (CacheErr) Register (27)                      |     |

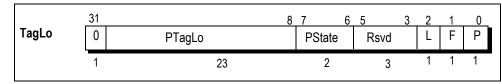

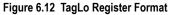

|   | TagLo Register (28)                                       |     |

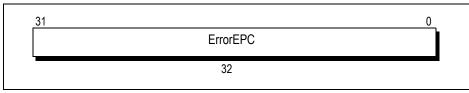

|   | Error Exception Program Counter (Error EPC) Register (30) |     |

|   | Processor Exceptions                                      |     |

|   | Exception Types                                           |     |

|   | General Exception Process                                 |     |

|   | Priority of Exceptions                                    |     |

|   | Exception Vector Locations                                |     |

|   | Reset Exception                                           |     |

|   | Debug Exception                                           |     |

|   | Soft Reset Exception                                      |     |

|   | Nonmaskable Interrupt (NMI) Exception                     |     |

|   | Address Error Exception                                   |     |

|   | TLB Exceptions                                            |     |

|   | TLB Refill Exception                                      |     |

|   | TLB Invalid Exception                                     |     |

|   | TLB Modified Exception                                    |     |

|   |                                                           |     |

|   | Bus Error Exception                                       |     |

|   | Integer Overflow Exception                                |     |

|   | Trap Exception                                            |     |

|   | System Call Exception                                   | 6-20       |

|---|---------------------------------------------------------|------------|

|   | Breakpoint Exception                                    |            |

|   | Reserved Instruction Exception                          |            |

|   | Coprocessor Unusable Exception                          |            |

|   | Interrupt Exception                                     | 6-21       |

|   | DWatch Exception                                        | 6-22       |

|   | IWatch Exception                                        | 6-22       |

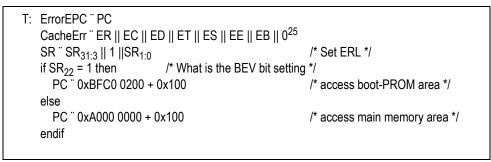

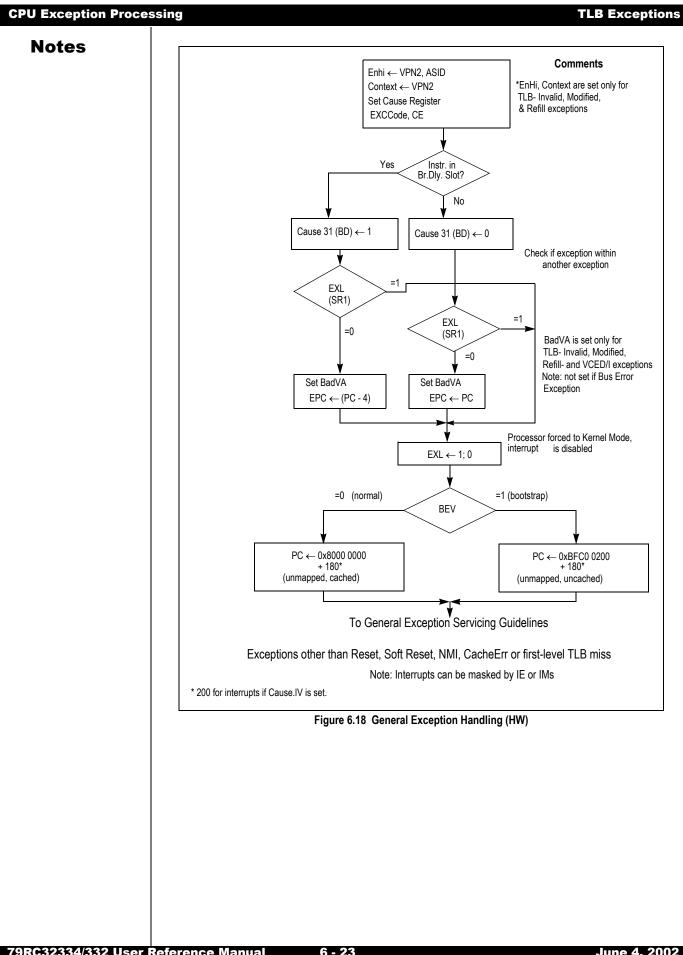

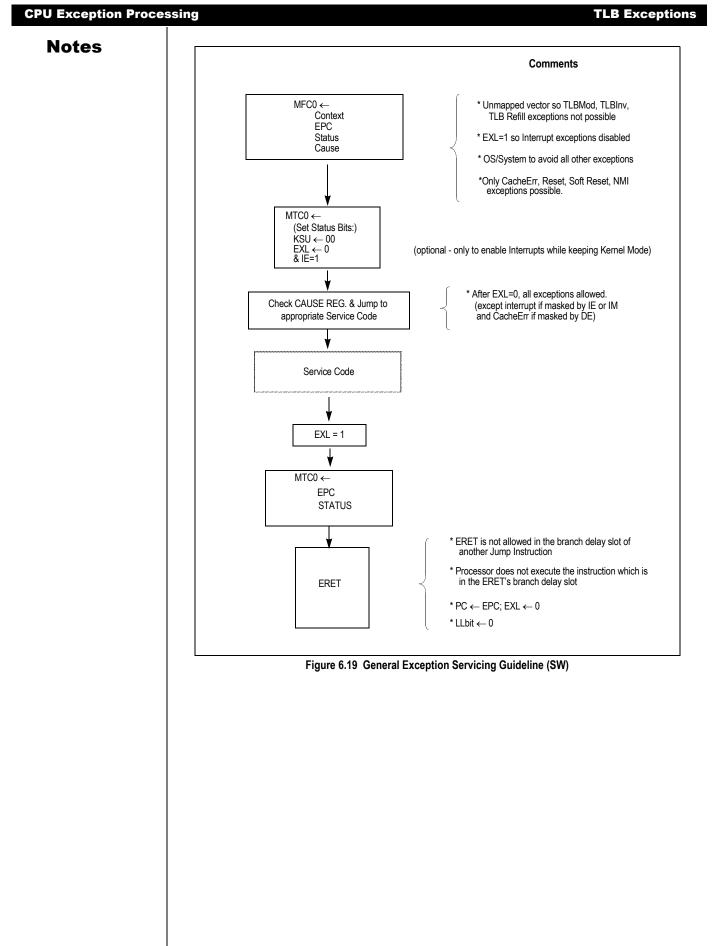

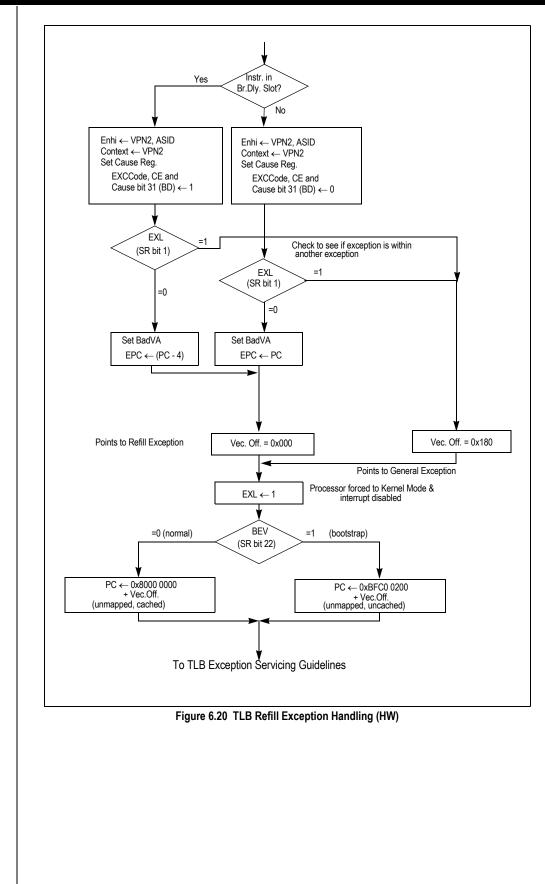

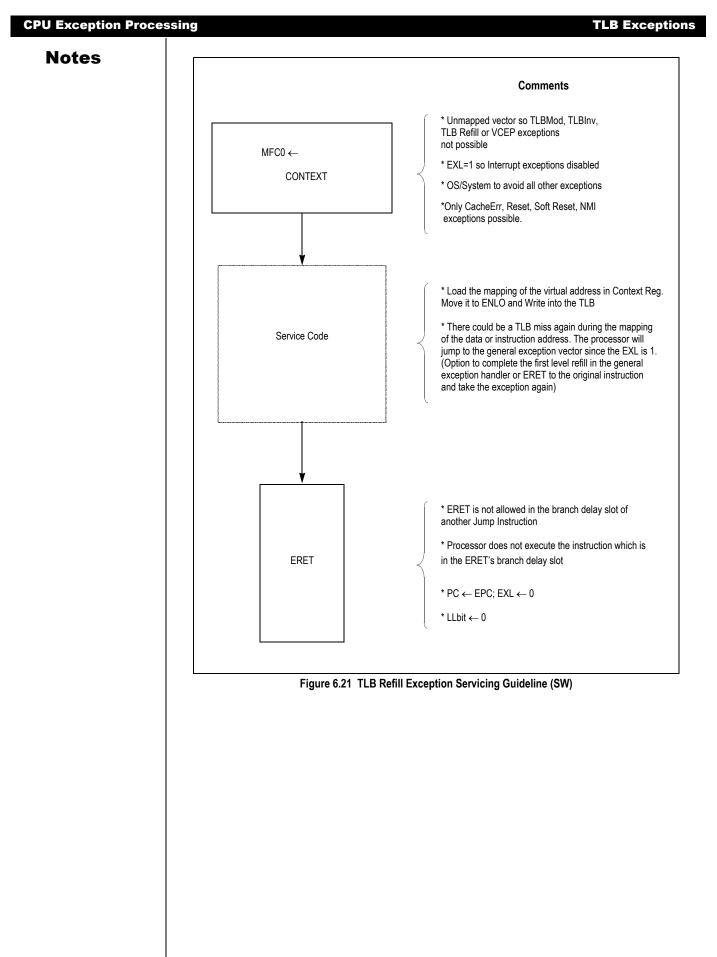

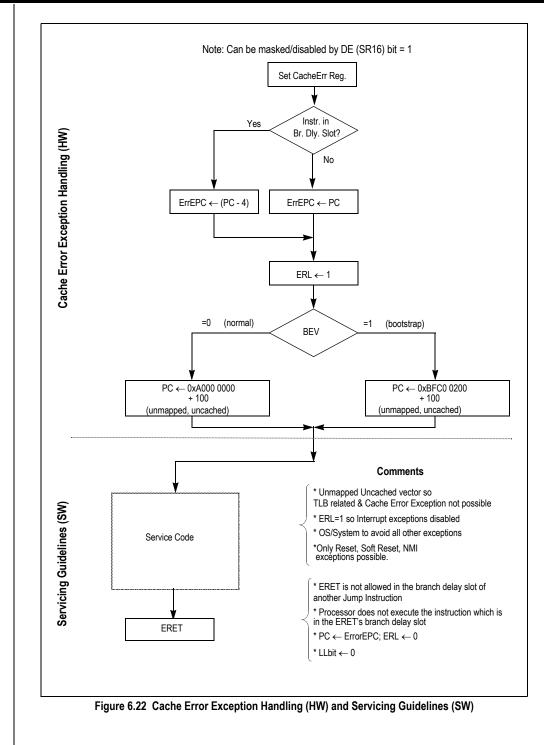

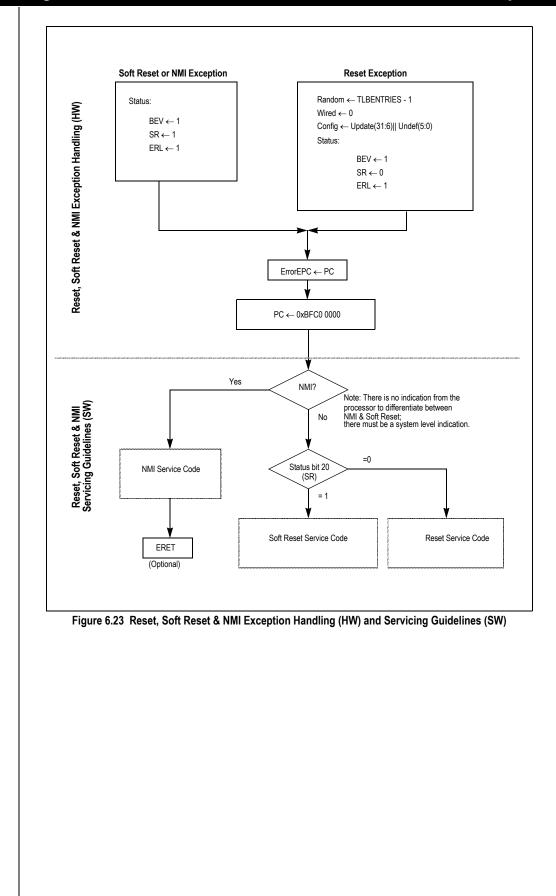

|   | Exception Handling and Servicing Flowcharts             | 6-22       |

| 7 | Cache Organization,<br>Operation, and Coherency         |            |

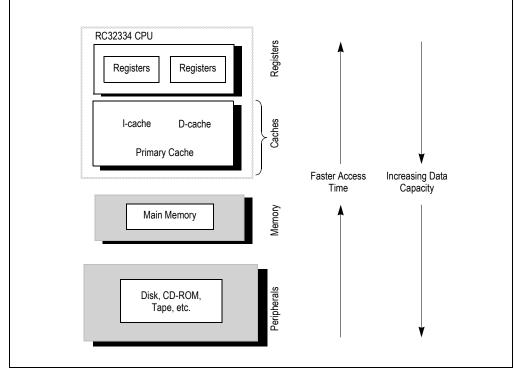

|   | Introduction                                            | 7-1        |

|   | Cache Operation Overview                                | 7-1        |

|   | RC32334 Cache Description                               | 7-2        |

|   | RC32334 Cache Attributes                                | 7-2        |

|   | Cache Organization and Accessibility                    | 7-2        |

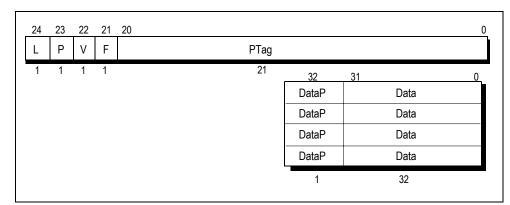

|   | Organization of the Primary Instruction Cache (I-Cache) | 7-2        |

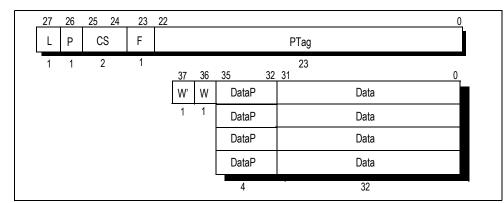

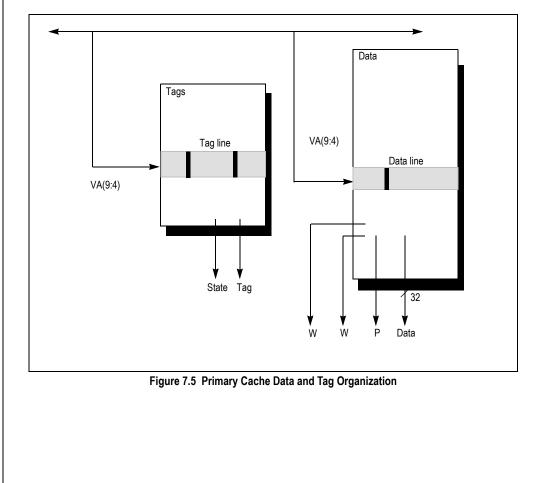

|   | Organization of the Primary Data Cache (D-Cache)        | 7-3        |

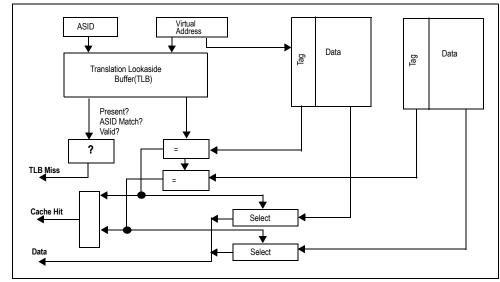

|   | Accessing the Primary Caches                            | 7-5        |

|   | Primary Cache States                                    | 7-6        |

|   | Primary Cache States                                    | 7-6        |

|   | Cache Line Ownership                                    | 7-6        |

|   | Cache Write Policy                                      | 7-7        |

|   | Store Buffer                                            | 7-7        |

|   | Cache Replacement Policy                                | 7-7        |

|   | Cache Initialization                                    | 7-8        |

|   | Cache Locking                                           | 7-8        |

|   | When to use Cache Locking                               | 7-8        |

|   | Example: Data Cache Locking                             | 7-8        |

|   | Example: Instruction Cache Locking                      | 7-9        |

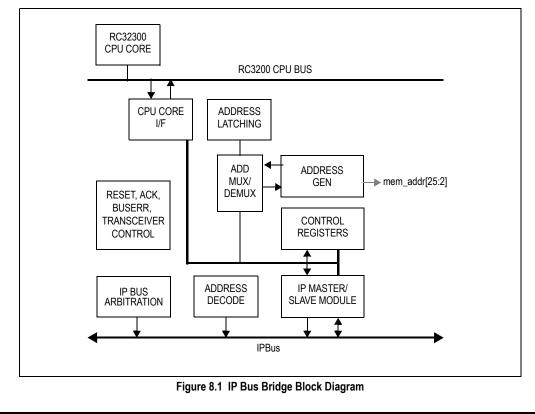

| 0 | RC32334 Internal Bus                                    |            |

| 0 |                                                         | <b>0</b> 4 |

|   |                                                         |            |

|   | List of Features for RC32300 CPU Bus                    |            |

|   | Block Diagram                                           |            |

|   | Functional Overview                                     | 8-2        |

|   | Address Module                                          |            |

|   | Address Incrementer                                     | 8-2        |

|   | Address MUX                                             |            |

|   | Address Decode                                          |            |

|   | Data Module                                             |            |

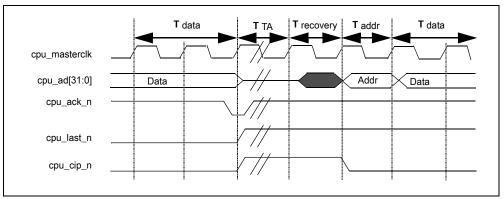

|   | CPU Read/Write Operations                               | 8-3        |

|   | DMA Read/Write Operations                               |            |

|   | Arbitration                                             | 8-4        |

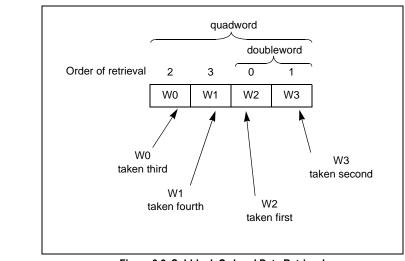

|   | Memory Port Sizing                                      | 8-4        |

|   | Bus Turnaround (BTA) Register                           | 8-4        |

|   | Watchdog Timer                                          | 8-5        |

| Bus Time-Out Counters                                                  | 8-5  |

|------------------------------------------------------------------------|------|

| Bus Error Timers                                                       | 8-5  |

| Register Descriptions                                                  | 8-5  |

| Interface Control Registers                                            | 8-6  |

| CPU Port-Width Control Register: Virtual Address 0xFFFF_E200           | 8-6  |

| CPU Bus Turnaround (BTA) Control Register: Virtual Address 0xFFF_E204  | 8-8  |

| CPU Bus Error Address Register (Read Only): Virtual Address 0xFFF_E208 | 8-9  |

| BTA Control Register                                                   | 8-9  |

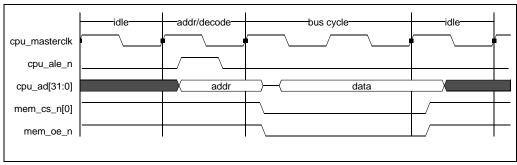

| Address Latch Timing Register                                          | 8-11 |

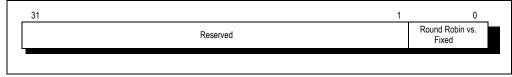

| Arbitration Register                                                   | 8-12 |

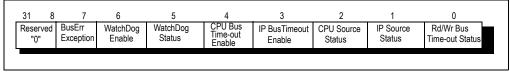

| BusError Control Register                                              | 8-12 |

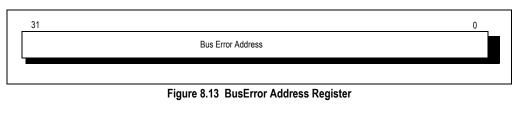

| BusError Address Register                                              | 8-12 |

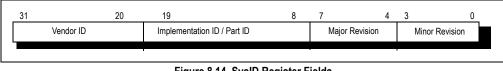

| SysID Register                                                         | 8-14 |

|                                                                        |      |

#### 9 External Local Bus Interface

| Introduction                  | 9-1 |

|-------------------------------|-----|

| Operation                     | 9-1 |

| Variable Port-Width Interface | 9-2 |

| Debug Signals                 | 9-4 |

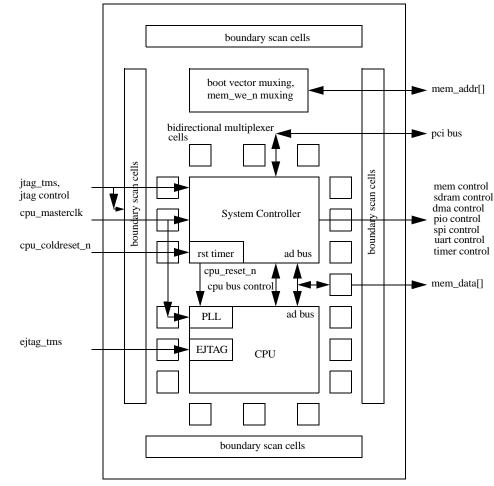

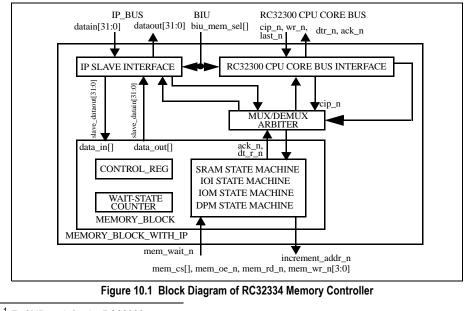

#### 10 Memory Controller

| Introduction                                        | . 10-1 |

|-----------------------------------------------------|--------|

| List of Features                                    | .10-1  |

| Block Diagram                                       | .10-1  |

| Functional Overview                                 | .10-2  |

| Memory Controller Operation                         | . 10-2 |

| Integrated Processor Generated Transactions         |        |

| DMA Controller or PCI Bridge Generated Transactions |        |

| Chip Selects                                        |        |

| Transceiver Control Interface                       |        |

| Using 8- or 16-bit Boot PROMs                       | . 10-3 |

| Wait-State Generator (WSG)                          | . 10-4 |

| Address Decoding                                    | .10-4  |

| Memory Type and Port-Width Size Support             | . 10-5 |

| Port-Width Size                                     | . 10-6 |

| I/O Width Support                                   | . 10-7 |

| Programmable Wait-State Generator                   | . 10-7 |

| External Wait-State Behavior                        | . 10-7 |

| Bus Error Recovery                                  | . 10-8 |

| Signal Descriptions                                 | .10-8  |

| Register Definitions                                | . 10-9 |

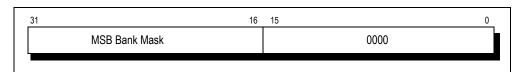

| Memory MSB Base Address Register for Banks 1:0      | 10-10  |

| Memory MSB Bank Mask Registers for Banks 1:0        | 10-10  |

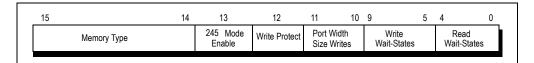

| Memory Control Register for Banks 5:0               | 10-11  |

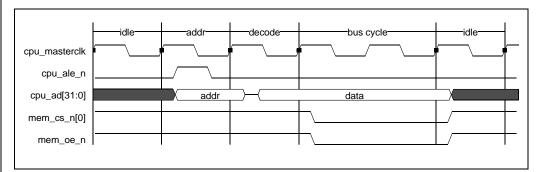

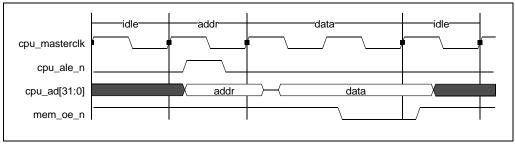

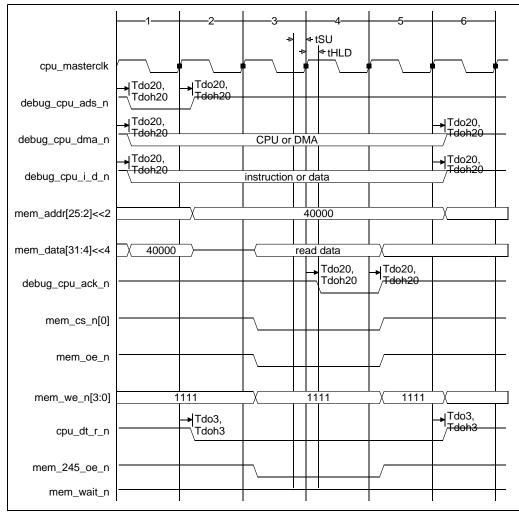

| Timing Diagrams                                     | 0.40   |

#### 11 Synchronous DRAM Controller

| Introduction                              | 11-1  |

|-------------------------------------------|-------|

| Features                                  | 11-1  |

| SDRAM Enhancements in Y Silicon Revision  | 11-1  |

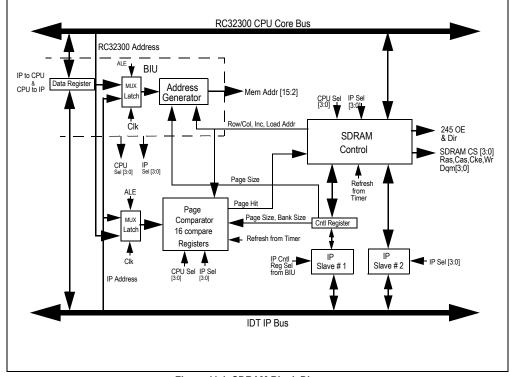

| Block Diagram                             | 11-3  |

| Functional Overview                       | 11-3  |

| Base Address Decoding                     | 11-7  |

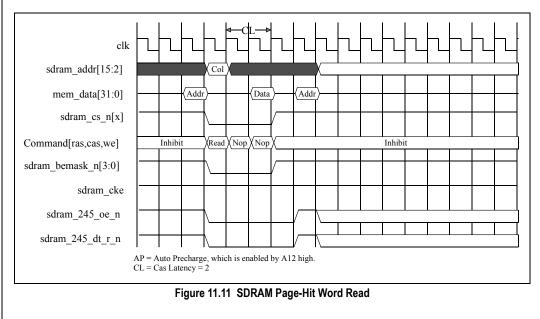

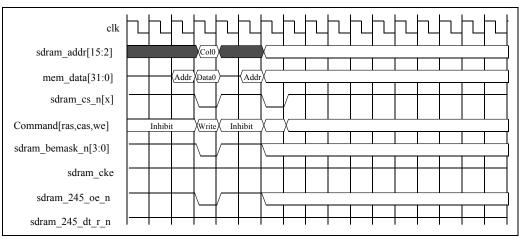

| Page Row Comparators                      | 11-7  |

| Burst Support                             | 11-7  |

| RAS/CAS Address MUX                       | 11-8  |

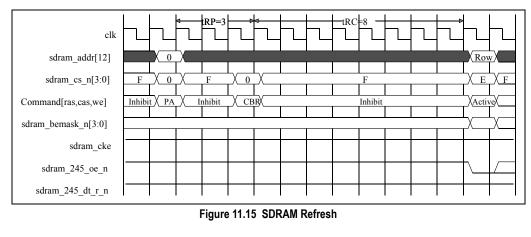

| Refresh Timer                             | 11-8  |

| Error Recovery                            | 11-8  |

| SDRAM Initialization                      | 11-8  |

| Register Definitions                      | 11-9  |

| SDRAM Control Registers                   | 11-10 |

| SDRAM Primary Control Register            |       |

| SDRAM Secondary Control Register          | 11-13 |

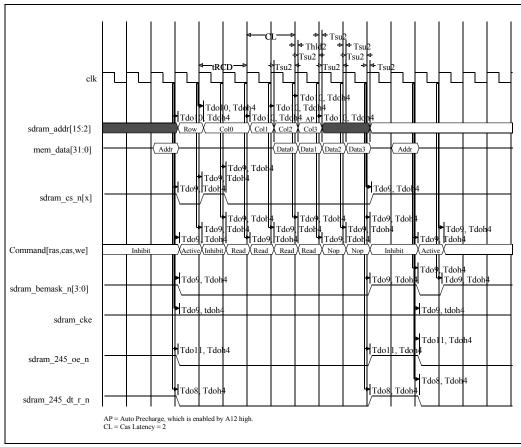

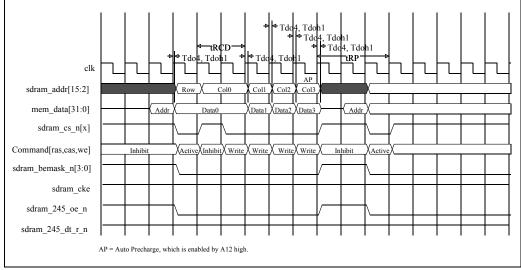

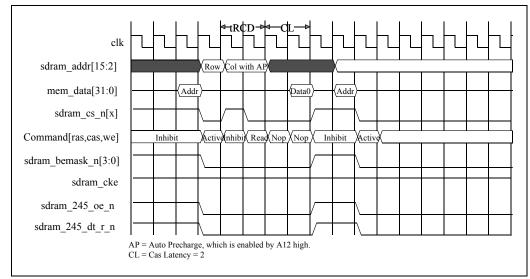

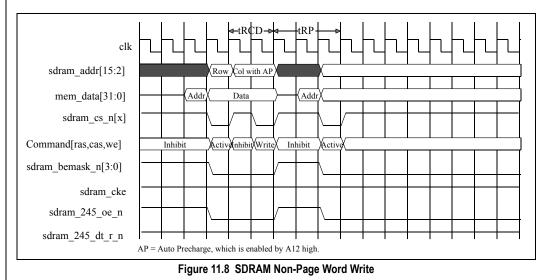

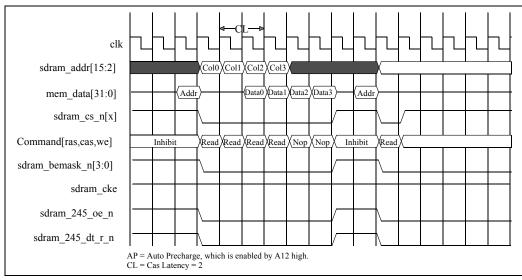

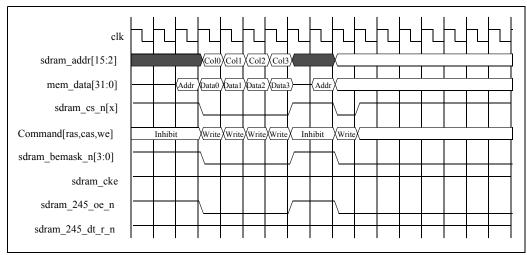

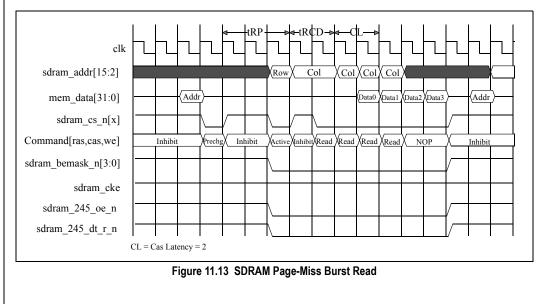

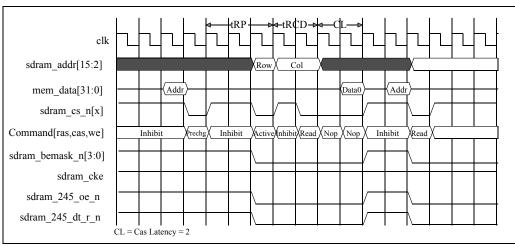

| Timing Diagrams                           | 11-15 |

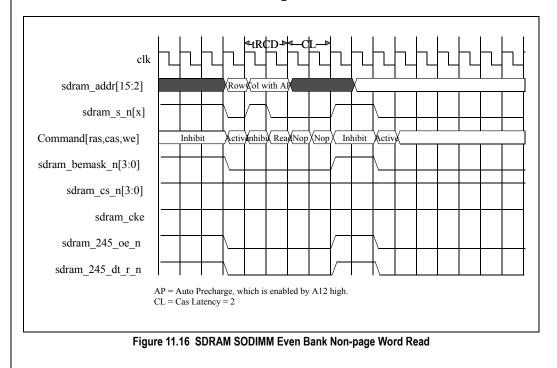

| SODIMM                                    | 11-21 |

| SODIMM Configuration                      | 11-21 |

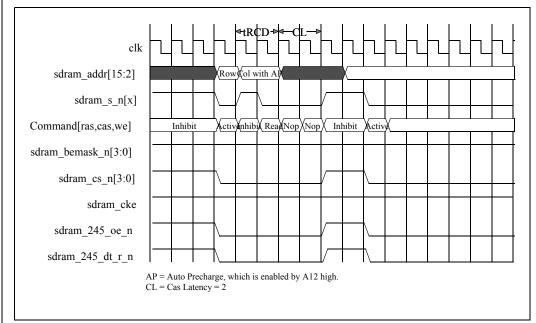

| SDRAM SODIMM Even Bank Non-Page Word Read | 11-21 |

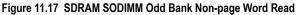

| SDRAM SODIMM Odd Bank Non-Page Word Read  | 11-22 |

| SDRAM SODIMM Refresh                      | 11-23 |

| output_clk Usage                          | 11-23 |

|                                           |       |

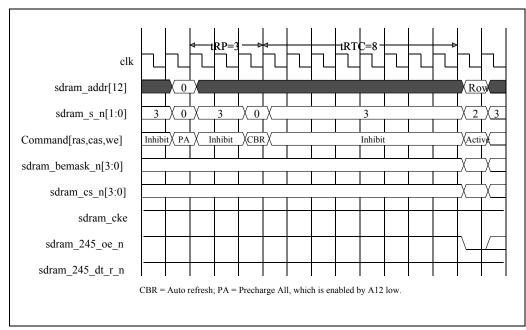

#### 12 PCI Interface Controller

| Introduction                                     |       |

|--------------------------------------------------|-------|

| Features                                         |       |

| PCI Interface Enhancements in Y Silicon Revision |       |

| Functional Overview                              |       |

| Memory Mapping                                   |       |

| RC32334 PCI Bus Target Operation                 |       |

| RC32334 PCI Bus Master Operation                 |       |

| RC32334 PCI Bus Target Operation                 |       |

| PCI Satellite Mode                               |       |

| PCI Commands Supported                           |       |

| PCI Configuration Register Access                |       |

| PCI Polling Error Handling                       |       |

| PCI Interrupts                                   | 12-11 |

| Signal Definitions                               |       |

| Register Definitions                             |       |

| PCI Controller Interrupt Pending Register 11     |       |

| CPU to PCI Mailbox Interrupt Pending Register 12 |       |

| PCI to CPU Mailbox Interrupt Pending Register 13 |       |

| PCI Memory Space [1,2,3] Base Register           |       |

| PCI I/O Base Register                            |       |

| New Feature Register                             |       |

|                                                  |       |

| Notes | PCI Target Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10163 | PCI Arbitration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | PCI to CPU Memory/IO Space [1,2,3,4] Base Registers                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | PCI Configuration Address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | PCI Configuration Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | RC32334 PCI Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

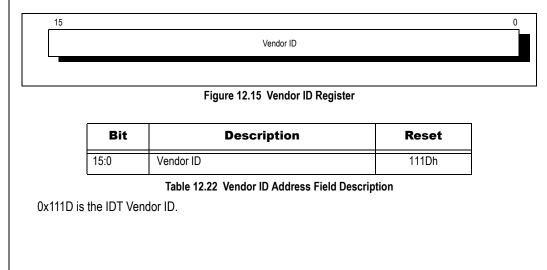

|       | Vendor ID Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

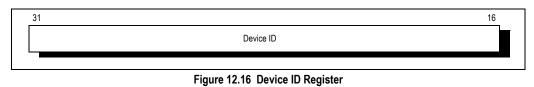

|       | Device ID Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | PCI Command Register                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | PCI Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

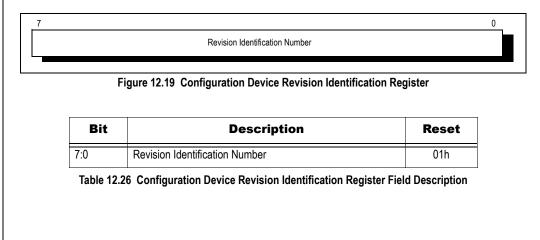

|       | Device Revision Identification Register                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Class Code Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Cacheline Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

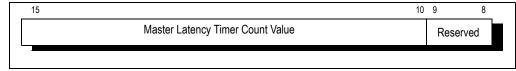

|       | Master Latency Timer Register                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

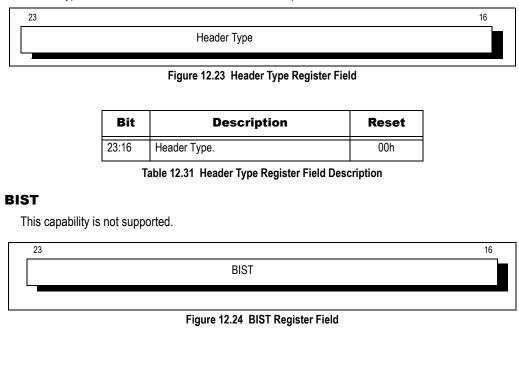

|       | Header Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | BIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | PCI Memory/IO Base Address [1,2,3,4] Registers                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Subsystem Vendor ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Subsystem ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Interrupt Line Register                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Interrupt Pin Register                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | MIN_GNT Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | MAX_LAT Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | TRDY Timeout Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Retry Timeout Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 13 DMA Controllers                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Introduction<br>List of Features                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | Introduction<br>List of Features<br>DMA Enhancements in Y Silicon Revision                                                                                                                                                                                                                                                                                                                                                                                                         | 13<br>13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | Introduction<br>List of Features                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13<br>13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | Introduction<br>List of Features<br>DMA Enhancements in Y Silicon Revision                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

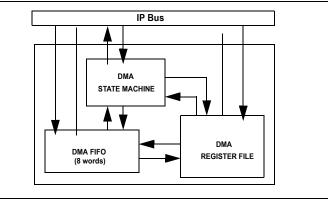

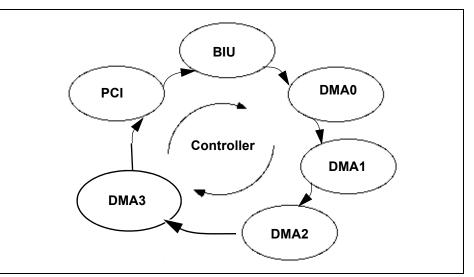

|       | Introduction<br>List of Features<br>DMA Enhancements in Y Silicon Revision<br>Block Diagram                                                                                                                                                                                                                                                                                                                                                                                        | 13<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | Introduction<br>List of Features<br>DMA Enhancements in Y Silicon Revision<br>Block Diagram<br>DMA Operations                                                                                                                                                                                                                                                                                                                                                                      | 13<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | Introduction<br>List of Features<br>DMA Enhancements in Y Silicon Revision<br>Block Diagram<br>DMA Operations<br>Endianness Swapping.                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Introduction<br>List of Features<br>DMA Enhancements in Y Silicon Revision<br>Block Diagram<br>DMA Operations<br>Endianness Swapping.<br>DMA Transfer Modes.                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

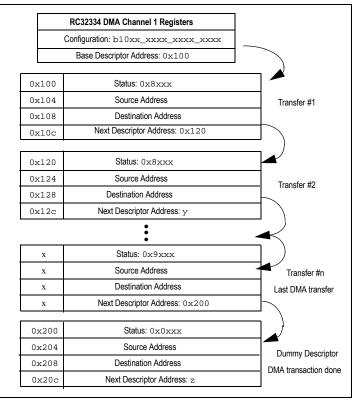

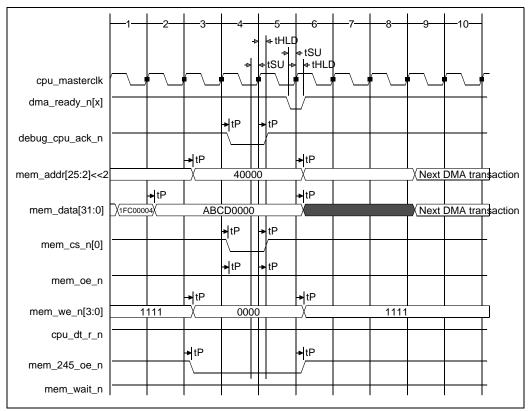

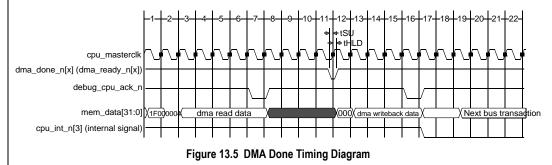

|       | Introduction<br>List of Features<br>DMA Enhancements in Y Silicon Revision<br>Block Diagram<br>DMA Operations<br>Endianness Swapping<br>DMA Transfer Modes<br>DMA Transfer Operations                                                                                                                                                                                                                                                                                              | 13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | Introduction<br>List of Features<br>DMA Enhancements in Y Silicon Revision<br>Block Diagram<br>DMA Operations<br>Endianness Swapping<br>DMA Transfer Modes<br>DMA Transfer Operations<br>Last Partial Word Transfers                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Introduction<br>List of Features<br>DMA Enhancements in Y Silicon Revision<br>Block Diagram<br>DMA Operations<br>Endianness Swapping<br>DMA Transfer Modes<br>DMA Transfer Operations<br>Last Partial Word Transfers<br>Transfer Restrictions                                                                                                                                                                                                                                      | 13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Introduction<br>List of Features<br>DMA Enhancements in Y Silicon Revision<br>Block Diagram<br>DMA Operations<br>Endianness Swapping.<br>DMA Transfer Modes<br>DMA Transfer Modes<br>Last Partial Word Transfers<br>Transfer Restrictions<br>DMA Arbitration Methods<br>DMA Access                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

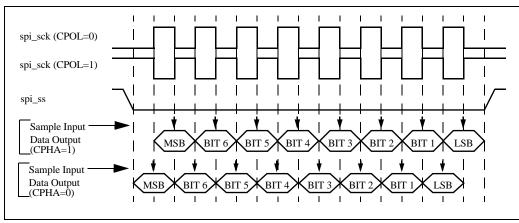

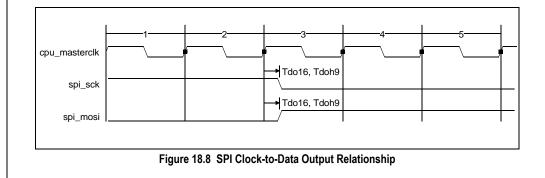

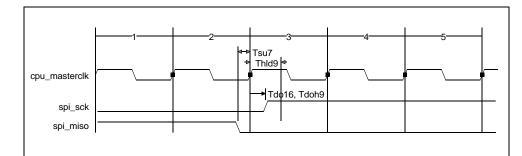

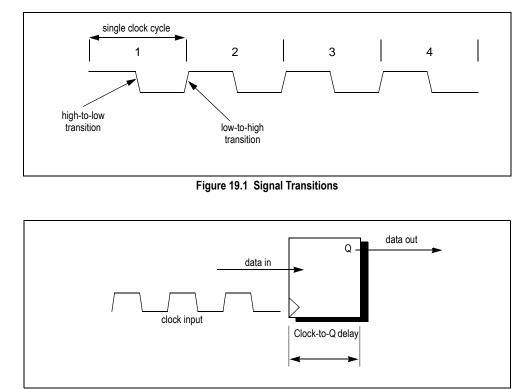

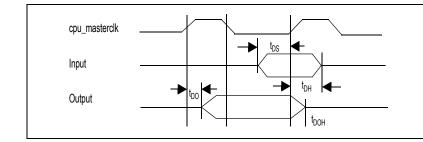

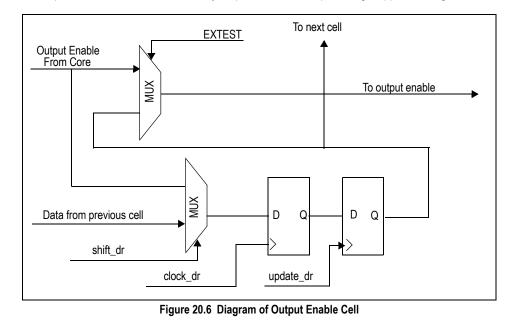

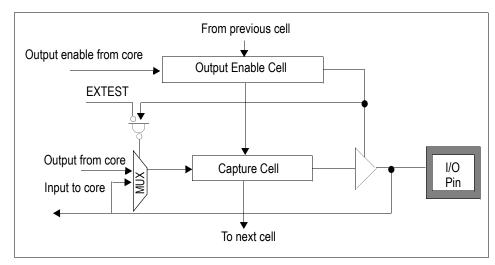

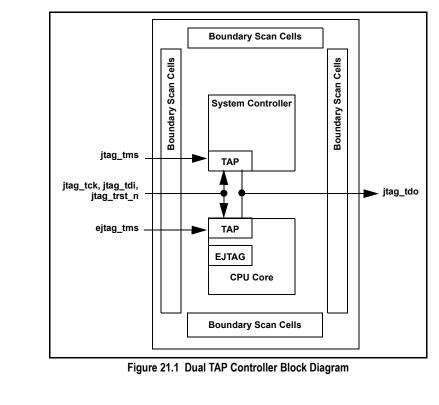

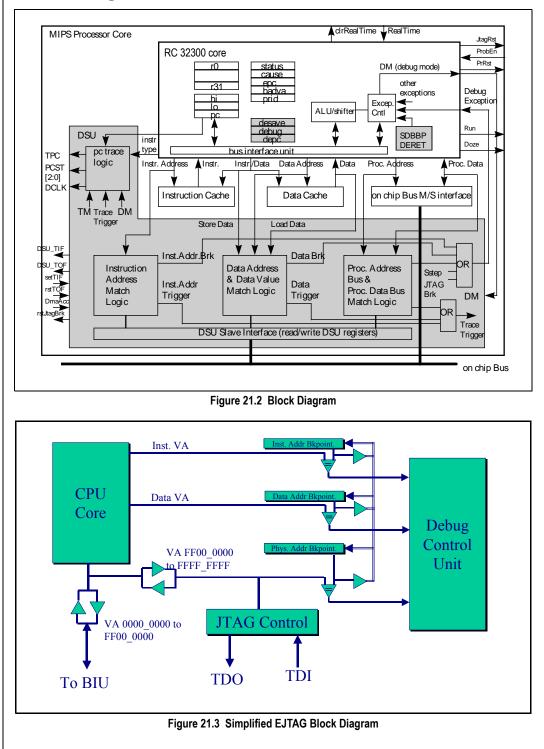

|       | Introduction<br>List of Features                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>13<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |