# HD153130F Color Palette with Three Eight-Bit DAC **Channels for High-Resolution CRTs**

# **HITACHI**

**Preliminary** Rev. 0 Dec. 1991

The HD153130 stores color information and converts digital pixel data to analog color output signals. Fabricated using Hitachi's Hi-BiCMOS process, it includes high-speed logic, high-speed SRAM, and high-precision eight-bit D/A converters on a single chip. Color signals can be output at a maximum dot rate of 135 MHz, enabling non-interlaced display of color graphics on a high-resolution CRT with up to 1280 bits × 1024 rasters.

The input section includes a pixel data multiplexer, so that pixel data can be input in parallel at 1/4 or 1/2 the dot rate. The palette RAM stores 256 words  $\times$  24 bits. The digital-to-analog converter section has three high-precision eight-bit D/A converter channels. Up to 256 out of 16.77 million colors can be displayed simultaneously.

Comparators built into the analog output section can be used to check that a monitor is connected and to discriminate between monochrome and color monitors.

#### **Features**

- On-chip eight-bit D/A converters: three channels.

- Maximum operating frequency: 110 or 135 MHz.

- Can simultaneously display 256 out of 16.77 million colors.

- Read mask function for display control.

- Interface conforms to VGATM graphics standard.

- Composite signal can include the blanking and sync signals needed for CRT control.

- 4:1 or 2:1 input multiplexer; pixel data can be input at standard TTL level.

- Variable black level (0 or 7.5 IRE units)

- D/A converter output specifications conform to

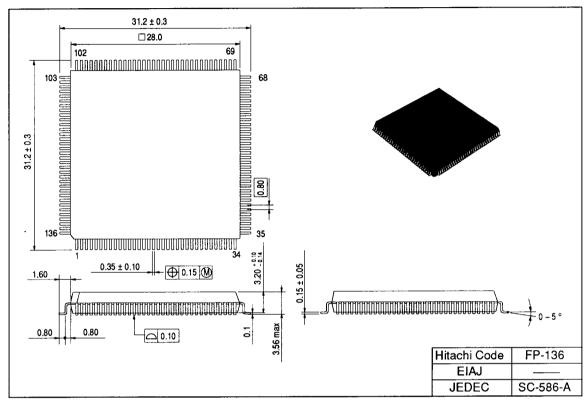

- Compact surface-mountable 136-lead QFP package.

### **Ordering Information**

| Ordering Information         | Maximum Clock Rate           | Package             |       |

|------------------------------|------------------------------|---------------------|-------|

| Product Number<br>HD153130F  | 110 MHz                      | 136-pin plastic QFP | ~     |

| HD153130F-135                | 135 MHz                      |                     | cOl.  |

| Note: VGA is a registered to | rademark of IBM Corporation. | atash               | eethu |

| Hitachi<br>semiconductor     |                              | MMM Days            | 1     |

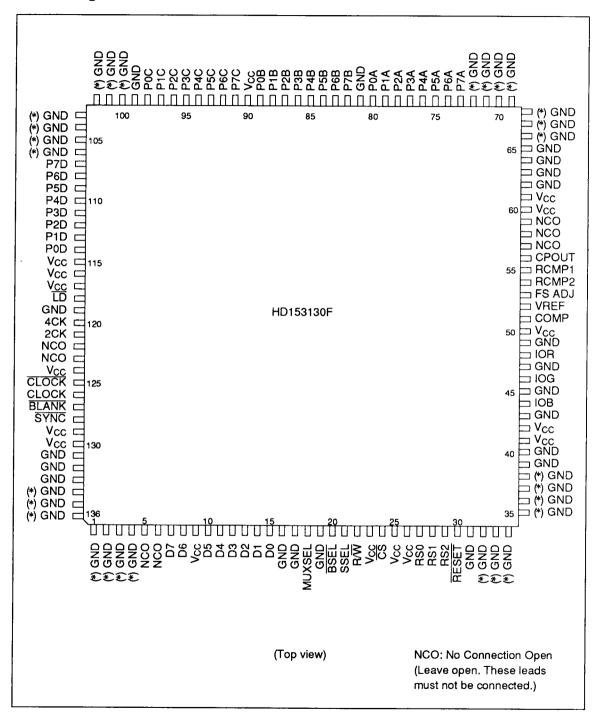

#### Pin Arrangement

# **Pin Description**

| Pin No.          | Symbol        | Function                                                                                                                                                                                              |  |  |  |  |

|------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7 to 8, 10 to 15 | D7 to D0      | Data input/output lines for reading and writing the CLT and registers. D7 is the MSB; D0 is the LSB.                                                                                                  |  |  |  |  |

| 73 to80          | P7A to P0A    | Input lines for pixel data addressing the CLT. P7A is the MSB; P0A is the LSB.                                                                                                                        |  |  |  |  |

| 82 to 89         | P7B to P0B    | Input lines for pixel data addressing the CLT. P7B is the MSB; P0B is the LSB.                                                                                                                        |  |  |  |  |

| 91 to 98         | P7C to P0C    | Input lines for pixel data addressing the CLT. P7C is the MSB; P0C is the LSB.                                                                                                                        |  |  |  |  |

| 107 to 114       | P7D to P0D    | Input lines for pixel data addressing the CLT. P7D is the MSB; P0D is the LSB.                                                                                                                        |  |  |  |  |

| 24               | <del>CS</del> | Chip select line for reading and writing the CLT and registers.                                                                                                                                       |  |  |  |  |

| 22               | R/W           | Mode select line for reading and writing the CLT and registers. $R/\overline{W}$ is valid when $\overline{CS} = 0$ , $R/\overline{W} = 1$ selects read mode. $R/\overline{W} = 0$ selects write mode. |  |  |  |  |

| 29 to 27         | RS2 to RS0    | Register select lines for reading and writing the CLT and registers.                                                                                                                                  |  |  |  |  |

| 118              | <u>LD</u>     | Strobe input line for pixel data and the SYNC and BLANK signals. The LD frequency should be 1/2 the clock frequency (2:1 multiplexing) or 1/4 the clock frequency (4:1 multiplexing).                 |  |  |  |  |

| 126, 125         | CLOCK, CLOCK  | Clock input lines. Two opposite-phase inputs are required.  Operations from pixel data input to analog output are clocked by these inputs.                                                            |  |  |  |  |

| 127              | BLANK         | Forces the analog signals from the DACs to the blanking level.                                                                                                                                        |  |  |  |  |

| 128              | SYNC          | SYNC signal input line. If SSEL = 1, when SYNC = 0 sync level is included in the green-channel DAC analog output. If the SYNC line is not used, leave it unconnected or pull it up to the 1 level.    |  |  |  |  |

| 20               | BSEL          | Selects composite or non-composite blanking level for the DAC output. BSEL = 0 selects composite; BSEL = 1 selects non-composite.                                                                     |  |  |  |  |

| 21               | SSEL          | Selects composite or non-composite sync level for the DAC output. SSEL = 1 selects composite; SSEL = 0 selects non-composite.                                                                         |  |  |  |  |

| 48               | IOR           | Analog output line for the red-channel DAC.                                                                                                                                                           |  |  |  |  |

| 46               | IOG           | Analog output line for the green-channel DAC.                                                                                                                                                         |  |  |  |  |

| 44               | IOB           | Analog output line for the blue-channel DAC.                                                                                                                                                          |  |  |  |  |

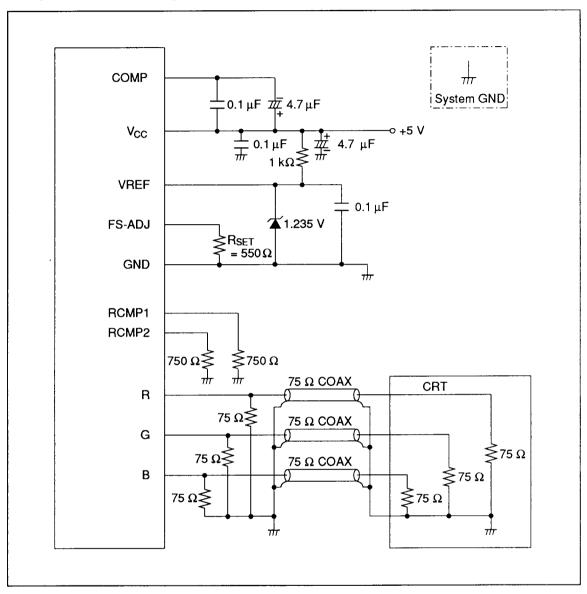

| 51               | COMP          | For connection of phase-compensating capacitors. Insert a 0.1- $\mu F$ (ceramic) and 4.7- $\mu F$ (electrolytic) capacitor between this lead and ground.                                              |  |  |  |  |

| 52               | VREF          | DAC reference level input line. See the sample connection diagram for external components.                                                                                                            |  |  |  |  |

| 53               | FS ADJ        | Connect a resistor (R <sub>SET</sub> ) for adjusting the DAC output level. Normally R <sub>SET</sub> should be about 550 $\Omega$ .                                                                   |  |  |  |  |

# **Pin Description (cont)**

| Pin No.                                                                         | Symbol          | Function                                                                                                                                                                              |

|---------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55, 54                                                                          | RCMP1, RCMP2    | Lines for generating comparator reference voltages: RCMP1 is for the red and blue comparators; RCMP2 is for the green comparator. Normally, connect resistors of about 750 $\Omega$ . |

| 56                                                                              | CPOUT           | Comparator result output line. Results of comparing the RGB output voltages with the reference voltages are output on this line as a digital signal.                                  |

| 120, 121                                                                        | 4CK, 2CK        | Output lines for clock signals obtained by dividing the dot clock frequency by four (4CK) and two (2CK).                                                                              |

| 18                                                                              | MUXSEL          | Selects the input multiplex mode. MUXSEL = 1 selects 2:1. MUXSEL = 0 selects 4:1.                                                                                                     |

| 30                                                                              | RESET           | Resets internal registers, flip-flops, etc. Reset is performed when RESET = 0.                                                                                                        |

| 9, 23, 25, 26, 41, 42,<br>50, 60, 61, 90,<br>115 to 117, 124, 129,<br>130       | V <sub>CC</sub> | Power supply voltage lines                                                                                                                                                            |

| 16, 17, 19, 31, 39, 40,<br>43, 45, 47, 49, 62 to 65,<br>81, 99, 119, 131 to 133 |                 | Ground lines                                                                                                                                                                          |

| 1 to 4, 32 to 38,<br>66 to 72, 100 to 106<br>134 to 136                         | (*)GND          | Ground lines for heat dissipation                                                                                                                                                     |

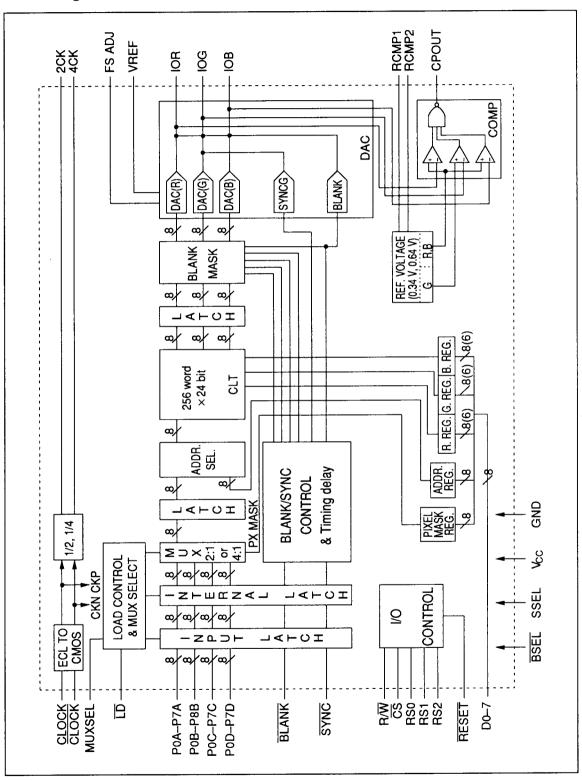

### **Block Diagram**

#### **Functional Description**

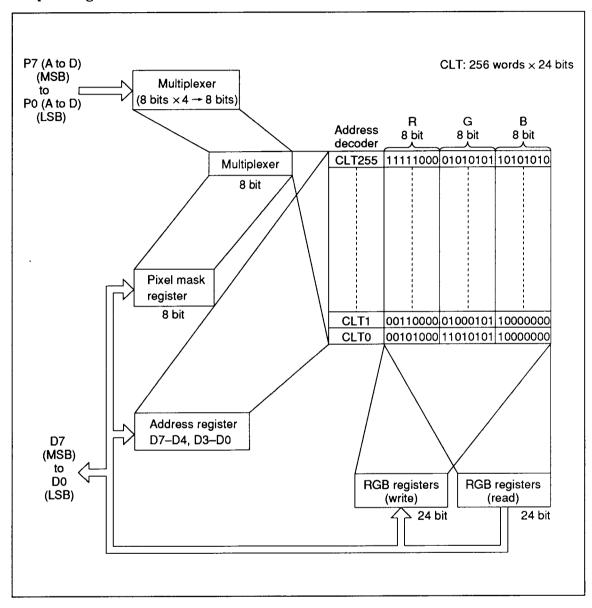

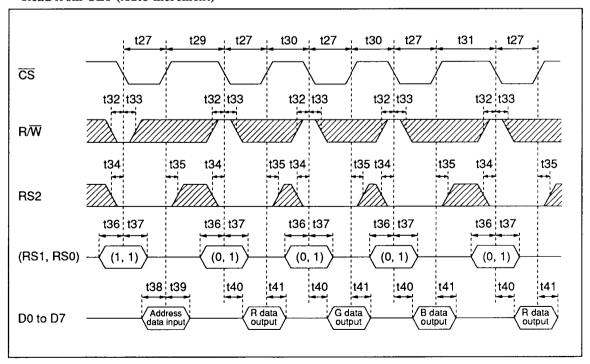

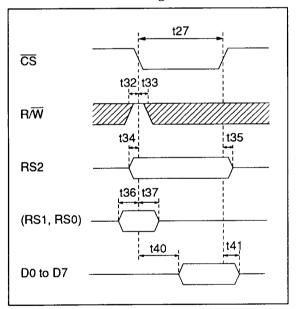

#### MPU Access to CLT and Registers

The CLT (Color Lookup Table) and registers are accessed using the  $\overline{CS}$ , R/W, RS2 to RS0, and D7 to D0 signals. RS2 to RS0 select the palette or register as indicated in table 1.

- Write to CLT: Figure 1 shows the timing for auto-increment writing data to the CLT. The write procedure is as follows:

- Write address information in the address register.

- Input data on D0 to D7 in the order of red, green, blue. All 24 bits (or 18 bits) are written together to the CLT after inputting of the blue data.

- After the data are written, the address is automatically incremented by 1. Continue inputting data in the order of red, green, blue.

- Read from CLT: Figure 2 shows the timing for auto-increment reading data from the CLT. The read procedure is as follows:

- Write address information in the address register.

- Data are read from the specified address in the order of red, green, blue.

- After the blue data have been read, the address is automatically incremented by 1, so the red, green, and blue data at the next address can be read.

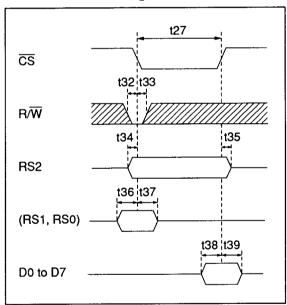

- Register Write: To write data in registers, input the data on D0 to D7 as shown in figure 5.

- Register Read: Data are read from registers via D0 to D7. See the timing diagram in figure 6.

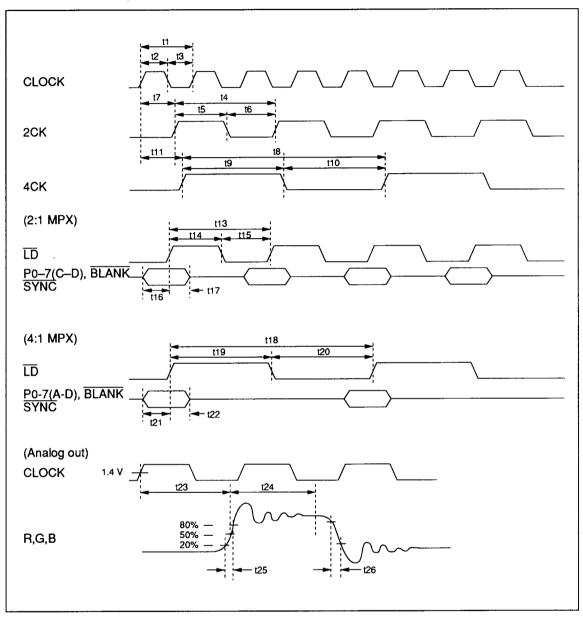

#### **Pixel Data Input Control**

• Pixel Data Input: Pixel data are input on lines P7 (A to D) to P0 (A to D). The data should be inputted at 1/4 or 1/2 the video output dot rate. The input data are multiplexed internally in A-to-D order (P7A-P0A, P7B-P0B, P7C-P0C, then P7D-P0D) and the CLT is accessed to obtain video output at the dot rate.

In 2:1 multiplexing, only P7C to P0C and P7D to P0D are used.

- Pixel Mask Function: An on-chip pixel mask register enables arbitrary bits to be masked in the pixel data input on P7 (A to D) to P0 (A to D). Masked bits are held to 0. Table 2 lists the signal names of the pixel mask register. Table 3 indicates how bits are masked.

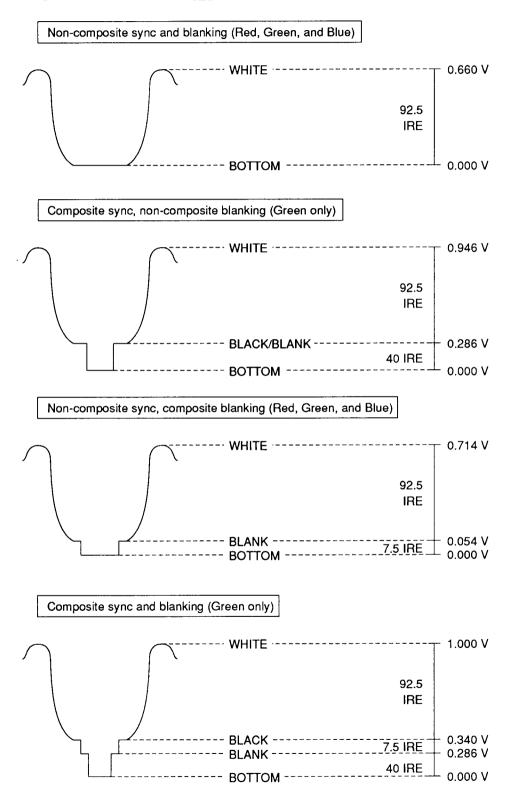

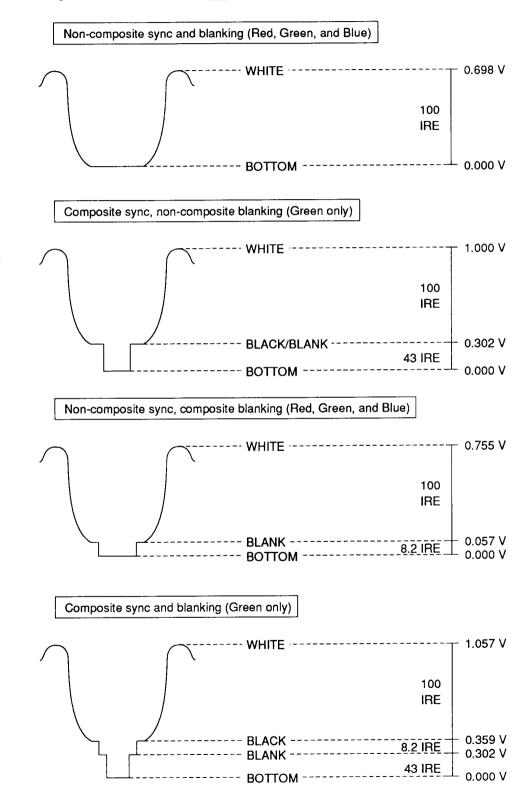

- Video Output Control Signals: The BLANK, SYNC, BSEL, and SSEL input signals can be used to have either composite or non-composite sync and blanking levels supplied to the red, green, and blue video output lines. For details, see table 4.

Table 1 Address Mapping

| RS2 | RS1 | RS0 | Selected Palette or Register |

|-----|-----|-----|------------------------------|

| 0   | 0   | 0   | Address register (write)     |

| 0   | 0   | 1   | CLT (0 to 255)               |

| 0   | 1   | 0   | Pixel mask register          |

| 0   | 1   | 1   | Address register (read)      |

| 1   | 0   | 0   | 8-bit/6-bit control register |

| 1   | 0   | 1   | Reserved                     |

| 1   | 1   | 0   | Reserved                     |

| 1   | 1   | 1   | Reserved                     |

#### 8-Bit and 6-Bit Modes

An on-chip register can be used to set the bit width of the red, green, and blue DA converters to eight or six bits. BC5 = 1 selects eight bits. BC5 = 0 selects six bits. (See table 2.)

#### Video Output and Connection Check Function

Red, green, and blue output comparators and reference current sources that generate reference levels for the comparators are integrated onto the chip. These can be used to have a test program implement software checks of interconnections to a graphics board, coaxial cables, and the CRT. The reference levels of the comparators can be adjusted by the resistances connected to the RCMP1 and RCMP2 lines. The reference level supplied to the comparators (Vcref) is related to the external resistance values (Rcmp1, Rcmp2) as follows:

#### **Double Termination Mode**

Non-composite sync (red, green and bluechannels)

Vcref (mV) =

$$0.458$$

(mA) × Rcmp1 ( $\Omega$ ) (Rcmp2)

• Composite sync

Vcref (mV) = 0.458 (mA)

$$\times$$

Rcmp1 ( $\Omega$ ) [red and blue channels]

Vcref (mV) =

$$0.860$$

(mA) × Rcmp2 ( $\Omega$ ) [green channel]

Table 2 Register Signal Names

|                      | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|----------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Pixel mask register  | PM7 | PM6 | PM5 | PM4 | РМЗ | PM2 | PM1 | PM0 |

| 8-bit/6-bit register |     | _   | BC5 | _   |     |     | _   | _   |

**Table 3 Pixel Mask Function**

|     | Pixel Mask Function       |

|-----|---------------------------|

| PM7 | Bit 7 masked when PM7 = 0 |

| РМ6 | Bit 6 masked when PM6 = 0 |

| PM5 | Bit 5 masked when PM5 = 0 |

| PM4 | Bit 4 masked when PM4 = 0 |

| РМЗ | Bit 3 masked when PM3 = 0 |

| PM2 | Bit 2 masked when PM2 = 0 |

| PM1 | Bit 1 masked when PM1 = 0 |

| PM0 | Bit 0 masked when PM0 = 0 |

### Map of Registers and CLT

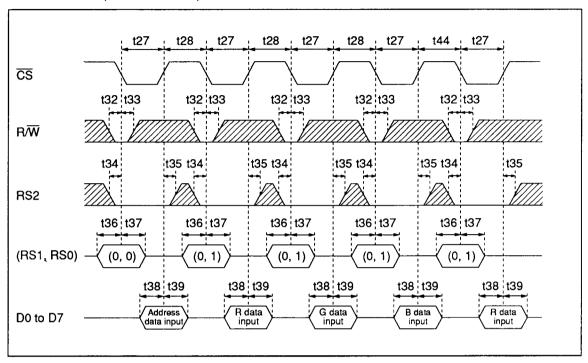

#### • Write to CLT (Auto-increment)

Figure 1

#### • Read from CLT (Auto-increment)

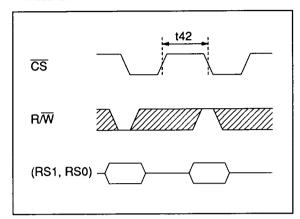

#### · Read after Write

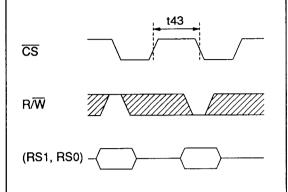

· Write after Read

Figure 3

Figure 4

### • Write to CLT and Register

• Read from CLT and Register

Figure 5

Figure 6

#### **MPU Interface**

| Item                     | Symbol | Min    | Тур     | Max         | Unit | Test Conditions |

|--------------------------|--------|--------|---------|-------------|------|-----------------|

| CS signal low time       | t27    | 50     | _       | _           | ns   |                 |

| CS signal high time (1)  | t28    | t1 × 4 |         |             | ns   |                 |

| CS signal high time (2)  | t29    | t1 × 7 |         |             | ns   |                 |

| CS signal high time (3)  | t30    | t1 × 4 |         |             | ns   |                 |

| CS signal high time (4)  | t31    | t1 × 7 |         |             | ns   | t1: clock cycle |

| CS signal high time (5)  | t42    | t1 × 7 |         |             | ns   |                 |

| CS signal high time (6)  | t43    | t1 × 7 |         | <del></del> | ns   |                 |

| CS signal high time (7)  | t44    | t1 × 7 | <u></u> |             | ns   |                 |

| R/W setup time to CS     | t32    | 10     |         |             | ns   |                 |

| R/W hold time to CS      | t33    | 10     |         | _           | ns   |                 |

| RS2 setup time to CS     | t34    | 10     |         | _           | ns   | Not tested      |

| RS2 hold time to CS      | t35    | 10     |         |             | ns   |                 |

| RS0-RS1 setup time to CS | t36    | 10     |         |             | ns   |                 |

| RS0-RS1 hold time to CS  | t37    | 10     |         |             | ns   |                 |

| D0-D7 setup time to CS   | t38    | 10     | _       | _           | ns   |                 |

| D0-D7 hold time to CS    | t39    | 10     |         | _           | ns   |                 |

| Data output delay time   | t40    | 5      | _       | 40          | ns   |                 |

| Data output hold time    | t41    | 5      | _       |             | ns   |                 |

# Absolute Maximum Ratings ( $T_a = 25^{\circ}C$ )

| Item                           | Symbol           | Min  | Тур | Max   | Unit |

|--------------------------------|------------------|------|-----|-------|------|

| Supply voltage                 | V <sub>CC</sub>  |      |     | 7.0   | ٧    |

| TTL input voltage              | V <sub>IT</sub>  | -0.5 |     | 5.5   | ٧    |

| ECL input voltage              | V <sub>IE</sub>  | -0.5 |     | 5.5   | ٧    |

| Voltage across ECL input lines | DVIE             | 0    |     | 2.0   | ٧    |

| Storage temperature            | T <sub>str</sub> | -55  |     | 150   | °C   |

| DAC output current             | loa              | 0    |     | -28.0 | mA   |

| Operating temperature Note     | T <sub>opr</sub> | 0    |     | 70    | °C   |

Note: Ambient temperature prior to operation of the HD153130.

# Electrical Characteristics ( $T_a = 0$ to +70°C, $V_{CC} = 5$ V $\pm 5\%$ unless otherwise specified)

### **DC** Characteristics

### **Analog Output**

| Item                           | Symbol | Min        | Тур | Max         | Unit | Test Conditions     |

|--------------------------------|--------|------------|-----|-------------|------|---------------------|

| Resolution                     |        | 8          | 8   | 8           | Bit  | $R_L = 37.5 \Omega$ |

| Integral linearity error       | ILE    | -1         |     | 1           | LSB  | $V_{CC} = 5 V$      |

| Differential linearity error   | DLE    | -1         | _   | 1           | LSB  | $T_a = 25$ °C       |

| Full-scale error               |        | <b>-</b> 5 | _   | 5           | %    |                     |

| Output voltage                 |        |            | 1   | <del></del> | ٧    |                     |

| Output matching characteristic |        |            |     | 5           | %    |                     |

#### **Digital Input**

| Item                                | Symbol           | Min         | Тур | Max | Unit | Test Conditions          |

|-------------------------------------|------------------|-------------|-----|-----|------|--------------------------|

| TTL high input voltage              | V <sub>IHT</sub> | 2.2         |     | 5.5 | ٧    |                          |

| TTL low input voltage               | V <sub>ILT</sub> | -0.3        |     | 0.7 | ٧    |                          |

| ECL high input voltage              | V <sub>IHE</sub> | 4           | _   | 5   | ٧    |                          |

| ECL low input voltage               | V <sub>ILE</sub> | 0           | _   | 3.4 | ٧    |                          |

| Voltage across ECL input lines      | DV <sub>IE</sub> | 0.7         | _   | 1.7 | ٧    |                          |

| TTL high input current (VI = 2.2 V) | Інт              | -0.3        |     | 20  | μΑ   | V <sub>CC</sub> = 5.25 V |

| TTL low input current (VI = 0.7 V)  | I <sub>ILT</sub> | -0.3        |     | -20 | μΑ   |                          |

| ECL high input current (VI = 4.0 V) | I <sub>IHE</sub> | -50         | _   | 50  | μΑ   |                          |

| ECL low input current (VI = 3.4 V)  | I <sub>ILE</sub> | <b>-</b> 50 | _   | 50  | μА   |                          |

# **Recommended Operating Conditions**

| Item                   | Symbol           | Min  | Тур  | Max      | Unit |

|------------------------|------------------|------|------|----------|------|

| Power supply voltage   | V <sub>CC</sub>  | 4.75 | 5.0  | 5.25     | V    |

| TTL high input voltage | V <sub>IHT</sub> | 2.4  | _    | $V_{CC}$ | V    |

| TTL low input voltage  | V <sub>ILT</sub> | 0    |      | 0.5      | V    |

| ECL high input voltage | V <sub>IHE</sub> | 4.4  |      | $v_{cc}$ | V    |

| ECL low input voltage  | V <sub>ILE</sub> | 0    |      | 3.1      | V    |

| DAC output resistance  | RL               | 37.5 |      | 75       | Ω    |

| Reference voltage      | $V_{REF}$        | _    | 1.20 | _        | V    |

| Reference resistance   | V <sub>EXT</sub> | _    | 542  |          | Ω    |

| Operating temperature  | Ta               | 0    | 25   | 50       | °C   |

# **AC Characteristics**

#### **Pixel Data**

|                  |        | HD15 | 3130 | F-110 | HD153130F-135 |              | 130F-135 |      |                                    |

|------------------|--------|------|------|-------|---------------|--------------|----------|------|------------------------------------|

| Item             | Symbol | Min  | Тур  | Max   | Min           | Тур          | Max      | Unit | Test Conditions                    |

| Clock frequency  | fmax   | 20   |      | 110   | 20            | <del>-</del> | 135      | MHz  |                                    |

| Clock cycle time | t1     | 9.1  | _    |       | 7.4           |              | _        | ns   |                                    |

| Clock high time  | t2     | 3.6  |      |       | 3             | _            |          | ns   | Not tested                         |

| Clock low time   | t3     | 3.6  |      | _     | 3             | _            |          | ns   | Not tested                         |

| 2CK frequency    | f2max  | 10   | _    | 55    | 10            | _            | 67.5     | MHz  |                                    |

| 2CK cycle time   | t4     | 18.2 |      | _     | 14.8          | _            | _        | ns   |                                    |

| 2CK high time    | t5     | 7.3  | _    | _     | 5.9           |              |          | ns   | Not tested                         |

| 2CK low time     | t6     | 7.3  |      |       | 5.9           | _            | _        | ns   | Not tested                         |

| 2CK delay time   | t7     | _    | 7    | _     | _             | 7            |          | ns   | C <sub>L</sub> = 15 pF             |

| 2CK duty         |        | 30   | 50   | 70    | 30            | 50           | 70       | %    | C <sub>L</sub> = 15 pF, not tested |

| 4Ck frequency    | f4max  | 5    | _    | 27.5  | 5             | _            | 33.75    | MHz  |                                    |

| 4CK cycle time   | t8     | 36.4 | _    |       | 29.6          | _            |          | ns   |                                    |

| 4CK high time    | t9     | 14.5 | _    | _     | 11.8          |              |          | ns   | Not tested                         |

| 4CK low time     | t10    | 14.5 | _    | _     | 11.8          | _            |          | ns   | Not tested                         |

| 4CK delay time   | t11    | _    | 7    | _     |               | 7            | _        | ns   | C <sub>L</sub> = 15 pF             |

| 4CK duty         |        | 30   | 50   | 70    | 30            | 50           | 70       | %    | C <sub>L</sub> = 15 pF, not tested |

### • 2:1 multiplex

|                        |        | HD153130F-110 |     |     | HD153130F-135 |     |     |      |                         |

|------------------------|--------|---------------|-----|-----|---------------|-----|-----|------|-------------------------|

| Item                   | Symbol | Min           | Тур | Мах | Min           | Тур | Max | Unit | Test Conditions         |

| LD cycle time          | t13    | 18.2          |     | _   | 14.8          | _   | _   | ns   |                         |

| LD high time           | t14    | 5             |     | _   | 5             |     |     | ns   | Not tested              |

| LD low time            | t15    | 5             | _   |     | 5             | _   |     | ns   | Not tested              |

| Data setup time to LD  | t16    | 4             |     |     | 4             | _   | _   | ns   | TESTER SPEC: t16 = 5 ns |

| Data hold time from LD | t17    | 3             |     |     | 3             |     | _   | ns   | TESTER SPEC: t17 = 4 ns |

### • 4:1 multiplex

|                        | Symbol | HD153130F-110 |     |     | HD153130F-135 |     |             |      |                         |

|------------------------|--------|---------------|-----|-----|---------------|-----|-------------|------|-------------------------|

| Item                   |        | Min           | Тур | Max | Min           | Тур | Max         | Unit | Test Conditions         |

| LD cycle time          | t18    | 36.4          |     |     | 29.6          | _   | _           | ns   |                         |

| LD high time           | t19    | 10            | _   | _   | 10            | _   | <del></del> | ns   | Not tested              |

| LD low time            | t20    | 10            | _   |     | 10            | _   | _           | ns   | Not tested              |

| Data setup time to LD  | t21    | 4             | _   | _   | 4             | _   | _           | ns   | TESTER SPEC: t21 = 5 ns |

| Data hold time from LD | t22    | 3             | _   | _   | 3             | _   | _           | ns   | TESTER SPEC: t22 = 4 ns |

### • Analog output

|                          | Symbol | HD153130F-110 |     |     | HD153130F-135 |     |     |      |                        |

|--------------------------|--------|---------------|-----|-----|---------------|-----|-----|------|------------------------|

| Item                     |        | Min           | Тур | Max | Min           | Тур | Max | Unit | Test Conditions        |

| Analog output delay time | t23    | _             | 20  |     | _             | 20  | _   | ns   | C <sub>L</sub> = 15 pF |

| Settling time            | t24    | _             | 5   | _   | _             | 5   |     | ns   | ±1 LSB/FSR, not tested |

| Analog output rise time  | t25    | _             | 1.5 |     | _             | 1.5 | _   | ns   | 20% to 80%, not tested |

| Analog output fall time  | t26    |               | 1.5 |     |               | 1.5 | _   | ns   | 80% to 20%, not tested |

| Analog output skew       |        |               | 0.5 | _   |               | 0.5 |     | ns   | Not tested             |

# **Pixel Data Timing**

**Table 4 Video Output Modes**

| BLANK | SYNC | BSEL | SSEL | R         | G               | В         |

|-------|------|------|------|-----------|-----------------|-----------|

| Н     | Н    | Н    | Н    | color (1) | color (3)       | color (1) |

| Н     | Н    | Н    | L    | color (1) | color (1)       | color (1) |

| Н     | Н    | L    | Н    | color (2) | color (4)       | color (2) |

| Н     | Н    | L    | L    | color (2) | color (2)       | color (2) |

| ×     | L    | ×    | ×    | воттом    | воттом          | воттом    |

| L     | Н    | Н    | Н    | воттом    | BLACK/BLANK (*) | воттом    |

| L     | Н    | Н    | L    | воттом    | воттом          | воттом    |

| L     | Н    | L    | Н    | воттом    | BLACK/BLANK (*) | воттом    |

| L     | Н    | L    | L    | воттом    | воттом          | воттом    |

Notes: x: Don't care

color (1) Normal color level

color (2) Composite blanking level

color (3) Composite sync level

color (4) Composite blanking and sync levels

BLACK/BLANK (\*) Composite sync level

### Video Output Waveforms (1) ( $R_{SET} = 550 \Omega$ )

### Video Output Waveforms (2) ( $R_{SET} = 529 \Omega$ )

### **Sample Connection Diagram**

### **Package Dimensions**

Unit: mm

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

#### Hitachi, Ltd.

Semiconductor & IC Div.

Karukozaka MN Bldg., 2-1, Ageba-cho, Shinjuku-ku, Tokyo 162, Japan

Tel: Tokyo (03) 3266-9376 Fax: (03) 3235-2375

#### For further information write to:

Hitachi America, Ltd. Semiconductor & IC Div. 2000 Sierra Point Parkway Brisbane, CA. 94005-1819

Tel: 415-589-8300 Fax: 415-583-4207 Hitachi Europe GmbH Electronic Components Div. Central Europe Headquarters Hans-Pinsel-Straße 10A 8013 Haar bei München F. R. Germany Tei: 089-46140 Fax: 089-463068 Hitachi Europe Ltd.

Electronic Components Div.

Northern Europe Headquarters

Wihtebrook Park

Lower Cookham Road

Maidenhead

Berkshire SL6 8YA

United Kingdom

Tel: 0628-585000

Tel: 0628-585000 Fax: 0628-778322 Hitachi Asia (Hong Kong) Ltd. Unit 706, North Tower, World Finance Centre, Harbour City, Canton Road Tsimshatsui, Kowloon Hong Kong Tel: 852-7359218 Fax: 852-7306071

030516 V\_R