# mos integrated circuit $\mu PD7004C$

## 10-BIT CMOS SUCCESSIVE APPROXIMATION A/D CONVERTER

30E D

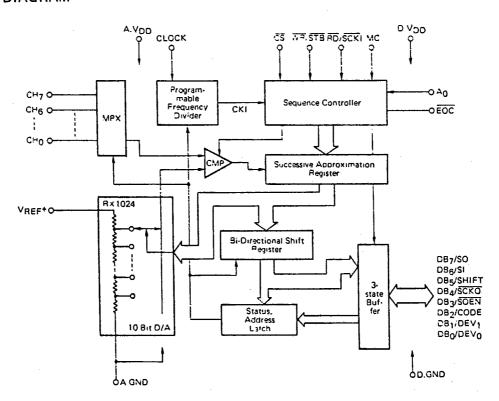

The μPD7004 is a 10-bit monolithic CMOS analog-to-digital converter using the Successive Approximation Register (SAR) technique. The μPD7004 incorporates an 8-channel multiplexed analog input and full microprocessor interface to achieve a high degree of versatility. The designer has a choice of either serial or parallel output and interface to 8080 type microprocessors or advanced signal processors like the μPD7720.

#### **FEATURES**

- 8-channel multiplexed analog input

- Serial or parallel interface

- 10-bit resolution

- Linearity: 1 LSB MAX. (Ta = 25 °C)

- Conversion time: 10 μs (f<sub>CLK</sub> = 1 MHz)

- Input voltage range 0 to VREF

- Temperature range from -40 to +85 °C

- Operates from single +5 volt supply (5 V ±10 %)

#### **BLOCK DIAGRAM**

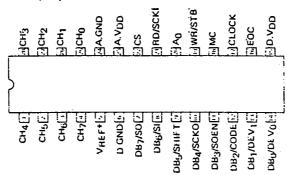

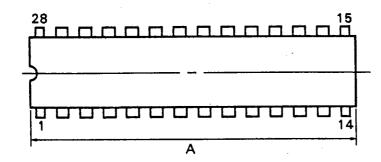

#### CONNECTION DIAGRAM (Top View)

#### PIN IDENTIFICATION

| Pin No. | <u> </u>                          | <u> </u> | Parallel mode                | ļ<br>ī        | Serial mode                           |  |  |  |  |

|---------|-----------------------------------|----------|------------------------------|---------------|---------------------------------------|--|--|--|--|

| rin No. | i Sumbol                          | 1/0      | Function                     | 1/0           | Function                              |  |  |  |  |

| 1       | CH <sub>4</sub>                   |          | Ar                           | nalog input ( | og input CH4                          |  |  |  |  |

| 2       | CH <sub>5</sub>                   |          | Analog input CH <sub>5</sub> |               |                                       |  |  |  |  |

| 3       | CH <sub>6</sub>                   |          | Ar                           | nalog input ( | CH <sub>6</sub>                       |  |  |  |  |

| 4       | CH <sub>7</sub>                   |          | Ar                           | nalog input ( | CH <sub>7</sub>                       |  |  |  |  |

| 5       | VREF+                             |          | Positive r                   | reference vol | Itage input                           |  |  |  |  |

| 6       | D.GND                             |          | Dig                          | ital Ground   | Note                                  |  |  |  |  |

| 7       | BD7/SO                            | Output   | Data bus (MSB)               | Output        | Serial output                         |  |  |  |  |

| 8       | DB <sub>6</sub> /SI               | Output   | Data bus (2nd)               | Input         | Serial input                          |  |  |  |  |

| 9       | DB <sub>5</sub> /SHIFT            | Output   | Data bus (3rd)               | Input         | First-bit select (LSB/MSB)            |  |  |  |  |

| 10      | DB <sub>4</sub> /SCKO             | Output   | Data bus (4th)               | 1/0           | Serial clock output                   |  |  |  |  |

| 11      | DB3/SOEN                          | Output   | Data bus (5th)               | 1/0           | Serial-out enable                     |  |  |  |  |

| 12      | D82/CODE                          | 1/0      | Data bus (6th)               | Input         | Code select                           |  |  |  |  |

| 13      | DB1/DEV1                          | 1/0      | Data bus (7th)               | Input         | Division ratio set                    |  |  |  |  |

| 14      | DB <sub>0</sub> /DEV <sub>0</sub> | 1/0      | Data bus (LSB)               | Input         | Division ratio set                    |  |  |  |  |

| 15      | D.V <sub>DD</sub>                 |          | Digital Power Supply Note    |               |                                       |  |  |  |  |

| 16      | EOC                               | Output   | End-of-conv                  | version signa | i (Active low)                        |  |  |  |  |

| 17      | CLOCK                             | Input    | Clock                        | signal input  | terminal                              |  |  |  |  |

| 18      | MC                                | Input    | Mode sele                    | ct (H=Parall  | el, L=Serial)                         |  |  |  |  |

| 19      | WR/STB                            | Input    | Write signal input           | Input         | Address-write strobe signal           |  |  |  |  |

| 20      | A <sub>0</sub>                    | Input    | Control address input        | Input         | Internal/external serial clock select |  |  |  |  |

| 21      | AD/SCKI                           | Input    | Read signal input            | Input         | Serial clock input                    |  |  |  |  |

| 22      | CS                                | Input    | C                            | hip select si | gnal                                  |  |  |  |  |

| 23      | A.V <sub>DD</sub>                 | :        | Analo                        | g Power Sup   | oply Note                             |  |  |  |  |

| 24      | · A.GND                           |          | An                           | alog Ground   | i Note                                |  |  |  |  |

| 25      | CH <sub>0</sub>                   | :        | A                            | nalog input   | CH <sub>0</sub>                       |  |  |  |  |

| 26      | CH <sub>1</sub>                   |          | A                            | nalog input   | CH <sub>1</sub>                       |  |  |  |  |

| 27      | CH <sub>2</sub>                   | Ţ        | A                            | nalog input   | CH <sub>2</sub>                       |  |  |  |  |

| 28      | CH <sub>3</sub>                   | !        | A                            | nalog input   | CH <sub>3</sub>                       |  |  |  |  |

Note: Connect to Digital Ground (D.GND) with Analog Ground (A.GND) externally.

Connect to Digital Power Supply (D.V\_DD) with Analog Power Supply (A.V\_DD) externally.

#### ABSOLUTE MAXIMUM RATINGS (T. = 25 °C)

Supply Voltage

$V_{DD}$

-0.3 to +7.0

Input Voltage

٧ı

-0.3 to  $V_{\mathrm{DD}}$  + 0.3

Reference Voltage Operating Temperature, Topt

$V_{\mathsf{REF}}$

-0.3 to  $V_{DD} + 0.3$

°C

Storage Temperature

$T_{\text{stg}}$

-40 to +85 -65 to +125

°C

### RECOMMENDED OPERATING CONDITIONS (Ta = -40 to +85 °C)

| Parameter                                      | Symbol          | MIN.   | TYP.        | MAX.         | Unit | Test Condition                                                          |

|------------------------------------------------|-----------------|--------|-------------|--------------|------|-------------------------------------------------------------------------|

| Supply Voltage                                 | V <sub>DD</sub> | 4.5    | 5.0         | 5.5          | ٧    |                                                                         |

| Reference Voltage                              | VREF            | 4.0    |             | مم۷          | ٧    |                                                                         |

| Analogue Input Voltage                         | VI              | 0.0    |             | VREF         | ٧    |                                                                         |

| High-level Input Voltage                       | VIH             | 2.4    |             |              | ٧    |                                                                         |

| Low-level Input Voltage                        | VIL             |        |             | 0.8          | ٧    |                                                                         |

| Clock Frequency                                | fcĸ             | 0.4    |             | 8.8          | MHz  |                                                                         |

| Internal Clock Frequency                       | fcKI            | 0.4    | 1.0         | 1.1          | MHz  | fCKI = fCK X Division ratio                                             |

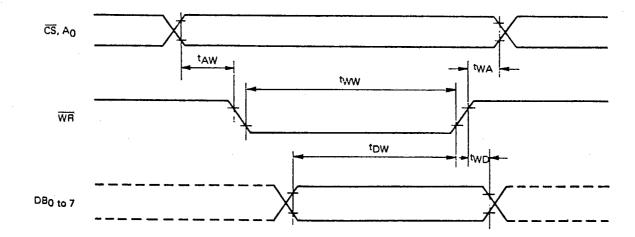

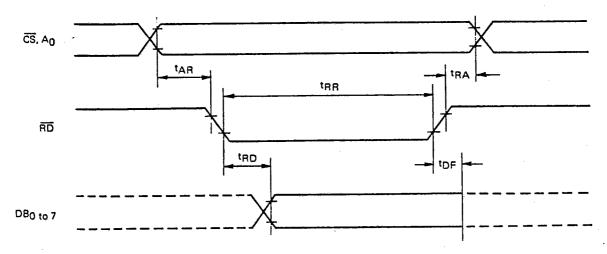

| Parallel Mode (MC = High)                      |                 | •      |             |              | ·    | <u> </u>                                                                |

| Address Setup Time                             | taw             | 20     |             |              | ns.  | $\overline{CS} \downarrow$ , $A_0 \rightarrow \overline{WR} \downarrow$ |

|                                                | <sup>t</sup> AR | 20     | !           |              | ns   | CS + , A <sub>0</sub> → RD +                                            |

| Address Hold Time                              | tWA             | 10     |             |              | ns   | WR t → CS t , A <sub>0</sub>                                            |

|                                                | tRA             | 10     |             | ļ            | ns   | RD t → CS t, A <sub>0</sub>                                             |

| WR Signal Pulse Width                          | tww             | 200    |             |              | ns   |                                                                         |

| RD Signal Pulse Width                          | ter             | 200    |             |              | ns   |                                                                         |

| Data Setup Time                                | tow             | 100    |             |              | ns   | DB → WR t                                                               |

| Data Hold Time                                 | two             | 20     |             |              | ns   | WR t → DB                                                               |

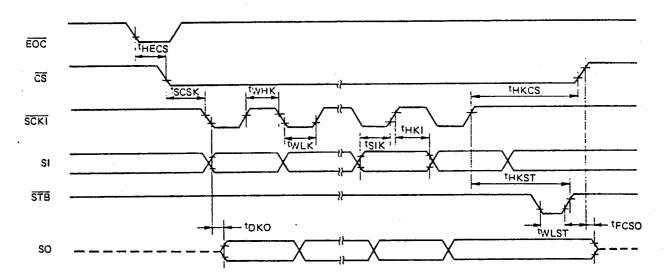

| Serial Mode 1 (MC = Low, A <sub>0</sub> = Low; | External Seria  | Clock) | <del></del> | <del>.</del> | ·    |                                                                         |

| EOC Hold Time                                  | tHECS           | 0      |             |              | μs   | EOC ↓ → CS ↓                                                            |

| CS Setup Time                                  | tscsk           | 1      |             |              | μs   | CS + → SCKI + (*)                                                       |

| Serial Input Setup Time                        | tsik            | 150    |             |              | ns   | SI → SCKI †                                                             |

| Serial Input Hold Time                         | tHKI            | 100    |             |              | ns   | SCKI ↑ → SI                                                             |

| Low-level Serial Clock Pulse Width             | tWLK            | 400    |             |              | ПS   |                                                                         |

| High-level Serial Clock Pulse Width            | twhk            | 400    |             |              | ns   |                                                                         |

| Strobe Pulse Width                             | tWLST           | 200    |             |              | ns   |                                                                         |

| Strobe Hold Time                               | tHKST           | 200    |             |              | ns   | SCKI t - STB t                                                          |

| Chip Select Hold Time                          | tHKCS           | 100    | <u> </u>    |              | ns   | SCKI ↑ → CS ↑                                                           |

<sup>\*</sup> fCKI = 1 MHz

t ... Rising edge

<sup>↓ ...</sup> Falling edge

## CONVERSION CHARACTERISTICS (T<sub>a</sub> = 25 °C, $V_{DD}$ = $V_{REF}$ = 5.0 ±0.5 V, $f_{CKI}$ = 1 MHz)

| Parameter                          | Symbol   | MIN. | TYP.         | MAX. | Unit   | Test Condition                 |

|------------------------------------|----------|------|--------------|------|--------|--------------------------------|

| Resolution                         |          | 10   | 10           | 10   | Bit    | T <sub>a</sub> = -40 to +85 °C |

| Total Unajusted Error              | NL       |      |              | ±1.0 | LSB    |                                |

| Total Unajusted Error              |          |      | !            | ±2.0 | LSB    | T <sub>a</sub> = -40 to +85 °C |

| Zero Scale Error                   |          |      | <del> </del> | ±0.5 | LSB    |                                |

| Zero Scale Temperature Coefficient |          |      | 2            |      | ppm/°C | T <sub>a</sub> = -40 to +85 °C |

| Full Scale Error                   |          | 1    |              | ±0.5 | LSB    |                                |

| Full Scale Temperature Coefficient | <u> </u> |      | 2            |      | ppm/°C | T <sub>a</sub> = -40 to +85 °C |

| Conversion Time                    | TCONV    | 96   | Τ            | 104  | • μ\$  | Parallel Mode, Serial Mode 1   |

| Conversion Time                    | TCONV    | 104  | 104          | 104  | μs     | Serial Mode 2                  |

## DC CHARACTERISTICS ( $V_{DD} = V_{REF} = 5.0 \pm 0.5 \text{ V}$ , $T_a = -40 \text{ to } +85 \,^{\circ}\text{C}$ , $f_{CKI} = 1 \text{ MHz}$ )

| Parameter                       | Symbol              | MIN. | TYP. | MAX. | Unit | Test Condition                                                                         |

|---------------------------------|---------------------|------|------|------|------|----------------------------------------------------------------------------------------|

| High-level Output Voltage       | Voн                 | 3.5  |      |      | ٧    | I <sub>O</sub> = -1.6 mA                                                               |

| Low-level Output Voltage        | VOL                 |      |      | 0.4  | V    | I <sub>O</sub> = 1.6 mA                                                                |

| Digital Input Leakage Current   | מו                  | !    |      | ±10  | μА   | V <sub>I</sub> = 0 to V <sub>DD</sub>                                                  |

| Floating Output Leakage Current | ¹FO                 |      | :    | ±10  | μА   | V <sub>0</sub> = 0 to V <sub>DD</sub>                                                  |

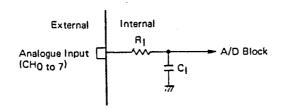

| Analog Input Resistance (DC)    | R <sub>I</sub> (DC) | -    | 2    | i    | MΩ   | V <sub>I</sub> = 0 to V <sub>DD</sub>                                                  |

|                                 | RI                  | 1    | : 10 | i    | kΩ   | : The analogue input impedance is equiva-<br>lent to the series circuit between RI and |

| (*)                             | CI                  |      | 100  | 1    | pF   | CI.                                                                                    |

| Reference Input Resistance      | RREF                | 5    | ;    | 50   | kΩ   |                                                                                        |

| Power Consumption               | Pd                  |      | 5    | 15   | : mW | :                                                                                      |

#### • Equivalent Circuit

Charge or discharge current flows at the internal multiplexer switching timing. Therefore, connect a capacitor (>0.01  $\mu$ F) to the analog input terminal in case the external is high.

## AC CHARACTERISTICS ( $V_{DD} = V_{REF} = 5 \pm 0.5 \text{ V}$ , $T_a = -40 \text{ to } +85 \,^{\circ}\text{C}$ , $f_{CK1} = 1 \text{ MHz}$ )

| Parameter                           | Symbol | MIN. | TYP.   | MAX. | Unit       | Test Condition                          |

|-------------------------------------|--------|------|--------|------|------------|-----------------------------------------|

| Output Delay Time                   | tRD    |      | :      | 150  | ns         | RD ↓ → DB (Parallel Mode)               |

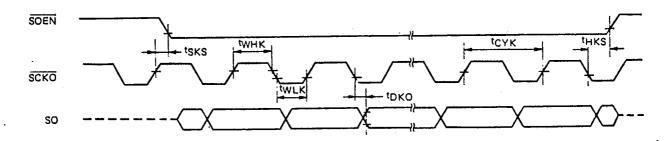

|                                     | tDKO   |      | 1      | 250  | ns         | SCKI ↓ , SCKO ↓ → SO (Serial Mode 1, 2) |

| Output Floating Delay Time          | tDF    |      |        | 100  | ns         | RD ↑ → DB Floating (Parallel Mode)      |

|                                     | tFCSO  |      | i      | 150  | ns         | CS t → SO Floating (Serial Mode 1)      |

| Serial-out Enable Delay Time        | tsks   | 40   |        | 200  | ns .       | SCKO ↑ → SOEN ↓ (Serial Mode 2)         |

| Serial-out Enable Delay Time        | tHKS   | 0    |        | 200  | ns         | SCKO ↓ → SOEN ↑ (Serial Mode 2)         |

| Serial Clock Output Cycle           | tCYK   |      | 1/fcKI |      | ns.        | (Serial Mode 2)                         |

| High-level Serial Clock Pulse Width | tWHK   | 400  | !      | i    | ns         | (Serial Mode 2)                         |

| Low-level Serial Clock Pulse Width  | WLK    | 400  |        |      | n <b>s</b> | (Serial Mode 2)                         |

| Serial Clock Rise Time              | trsc   |      | 20     |      | ns-        | (Serial Mode 2)                         |

| Serial Clock Fall Time              | tfsc   |      | 20     |      | ns         | (Serial Mode 2)                         |

t ... Rising edge

↓ ... Falling edge

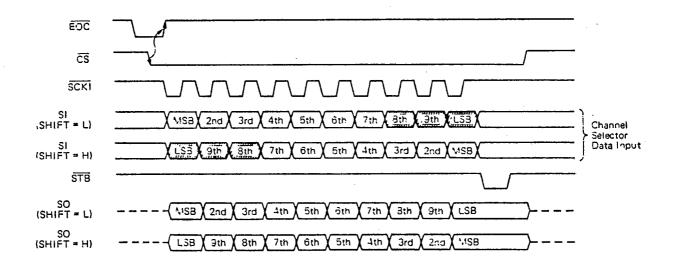

#### TIMING CHART

#### 1. Parallel Mode

#### (1) Write Mode

#### 2. Serial Mode 1

#### 3. Serial Mode 2

#### INTERNAL BLOCK OPERATION

#### 1. Sequence Controller

The sequence controller controls the operation of the comparator, internal sequence of the successive approximation register, and the 3-state buffers.

The A/D conversion starts in the parallel mode when the MPX address is written, and in the serial mode when the  $\overline{\text{CS}}$  signal changes to the high level.

When the A/D conversion is terminated, the sequence controller issues an end-of-conversion signal (EOC) to notify this to the external environment.

#### 2. Successive Approximation Register

The successive approximation register sends signals to the decoder of the 10-bit D/A according to the control signals from the sequence controller and then decides to set or reset the signals for the decoder, starting with the MSB, with the help of the results from the comparator.

#### 3. Bi Directional Shift Resister

This is the register into which the contents of the successive approximation register are entered. It outputs the converted data via 3-state buffers when in the parallel mode.

In serial mode 1, it outputs the converted data from the SO terminal when the SIKI signal falls and the CS signal is low, and fetches serial data (MPX address selector data) from the SI terminal when the SCKI signal rises.

In serial mode 2, 10-bit converted data accompanied by 6-bit high data is output from the SO terminal synchronously from the falling edge of the SCKO signal.

#### 4. Status, Address Latch

The status and address latch are 3-bit registers to latch the clock division selector ratio data, code selector data of the conversion data, and selector data for the MPX address.

It reads the data entered from the data buses (DB<sub>0 to 7</sub>) in the parallel mode. In serial mode, it latches the division ratio selector data and code selector data specified by the multi-function terminals (DB<sub>0</sub>/DEV<sub>0</sub>, DB<sub>1</sub>/DEV<sub>1</sub>, DB<sub>2</sub>/CODE) and also the MPX address selector data entered through the SI terminal.

However, that the MPX address is fixed at CH<sub>7</sub> and cannot be selected in serial mode 2.

#### 5. Programmable Frequency Divider

The programmable frequency divider designates clock signals entered from the external circuit to one of the ratios 1/1, 1/2, 1/4, and 1/8.

#### **OPERATING MODE**

The µPD7004, serving as an interface circuit with the microcomputer, supports two kinds of serial modes and a parallel mode.

30E D

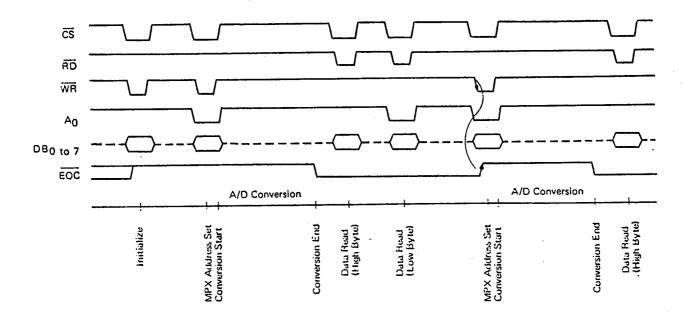

#### 1. Parallel Mode

The parallel mode allows a direct connection to the microprocessor data buses. Shown below is an example of the basic sequence;

The initialization designates the clock signal division ratio for the clock signal entered from the external environment and the conversion data code (2's complement/binary). Normally, initialization is performed to initialize the peripheral circuits of the microcomputer. After initialization, the data entered is held until the next initialization. Writing the MPX address into the µPD7004 (WR signal) after the initialization makes the A/D conversion start from the rising edge of WR signal.

The A/D conversion requires fcki (internal clock: fck X division ratio) to be 96 to 104 cycles. The EOC signal changes to the low level when the A/D conversion is complete to notify this to the external environment. The 10-bit converted data is read out from the µPD7004 eight bits at a time. The low byte has valid data in its two high-order bits, followed by six "0"s in the rest (DB5 to DB0).

Resetting the MPX address starts the next A/D conversion, changing the EOC signal to the high level at the falling edge of WR signal.

|    | Control terminal |    | Omanusian      | Serves as a data bus terminal |                                         |  |  |  |  |

|----|------------------|----|----------------|-------------------------------|-----------------------------------------|--|--|--|--|

| ĊŜ | WR               | RD | A <sub>0</sub> | Operation                     | Salace as a nara nn's faithiller        |  |  |  |  |

| н  | ` x              | х  | X              | No Operation                  | High-impedance State                    |  |  |  |  |

| L  | Н                | Н  | X              | No Operation                  | High-Impedance State                    |  |  |  |  |

| L  | L                | Н  | Н              | Initialize                    | Code Select, Clock Division Ratio Input |  |  |  |  |

| L  | L                | Н  | L              | Address Set                   | Analogue Channel Select Data Input      |  |  |  |  |

| L  | н                | L, | Н              | High-byte Read                | : High-byte Data Output                 |  |  |  |  |

| L  | Н                | L  | L              | Low-byte Read                 | Low-byte Data Output                    |  |  |  |  |

| L  | L                | L  | ×              | Inhibit                       | -                                       |  |  |  |  |

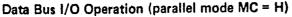

#### (1) initialize

In the parallel mode, the initialization data for the clock division ratio and the A/D conversion data code are written into the  $\mu$ PD7004 through data buses.

T-51-10-10

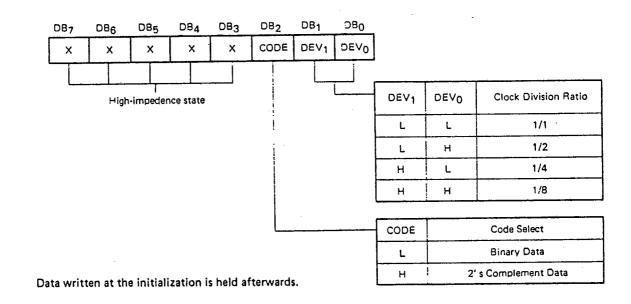

#### (2) Address set

The selector data for the analog channel is written into the  $\mu$ PD7004.

#### (3) High-byte/low-byte read

The A/D conversion data is read from the  $\mu$ PD7004.

|           | 087 | D8 <sub>6</sub> | DB <sub>5</sub> | OB <sub>4</sub> | овз | DB <sub>2</sub> | DB <sub>1</sub> | DB <sub>O</sub> |

|-----------|-----|-----------------|-----------------|-----------------|-----|-----------------|-----------------|-----------------|

| High-byte | MSB | 2ND             | 3RD             | 4TH             | 5TH | 6ТН             | 7TH             | , 8TH           |

| Low-byte  | 9TH | LSB             | L               | L               | L   | L               | L               | : L             |

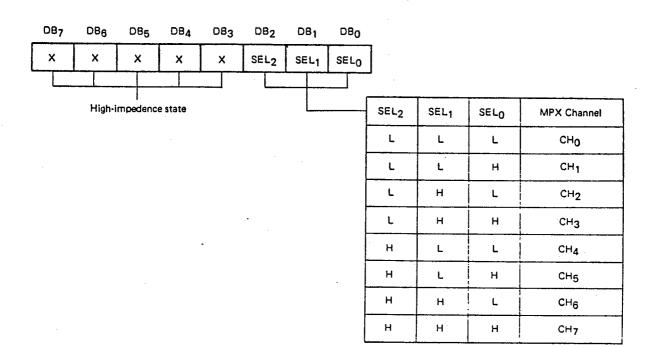

#### EXAMPLE OF THE PARALLEL MODE INTERFACE

Fig. 1 shows an example of connecting the  $\mu$ PD7004C to the  $\mu$ PD780C system. As shown in the example, the parallel mode can handle connections using such basic interface circuits as microcomputer peripheral LSIs.

In this example, the  $\mu$ PD780C is employed as a CPU. It is also possible to have other 8-bit CPUs connected in the same logic design, with some timing management by the wait cycle.

Fig. 1  $\mu$ PD780C/ $\mu$ PD7004C connection

- \*1 Can be used for interrupt request signals to the CPU.

- \*2 Can apply a clock to the CPU. (up to 8 MHz)

#### 2. Seriai Mode

The serial mode includes serial mode 1 and serial mode 2. Described below are the functions of terminals operating in each mode.

## SERIAL I/O OPERATION (Serial Mode 1, 2, MC = L)

| Symbol | Pin No. |             | Serial Mode 1<br>(External Serial Clock, A <sub>0</sub> = L)                                                                          | (1                                                                                                                                                     | Serial<br>Signal Processo           | Mode 2<br>or Mode, | A <sub>0</sub> = 1 | 4)     |       |  |  |

|--------|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------|--------------------|--------|-------|--|--|

| Oy     |         | 1/0         | Function                                                                                                                              | I/O Function                                                                                                                                           |                                     |                    |                    |        |       |  |  |

| so     | 7       | Output      | Serial output (three state). Data are output at the falling edge of SCKI or SCKO.                                                     |                                                                                                                                                        |                                     |                    |                    |        | ·     |  |  |

| SI     | 8       | Input       | Serial Input. Data read at the rising edge of SCKI or SCKO.                                                                           | ·                                                                                                                                                      |                                     |                    |                    |        |       |  |  |

| SHIFT  | 9       | Input       | Shift Select (H: LSB first, L: MSB first                                                                                              | t)                                                                                                                                                     |                                     |                    |                    |        |       |  |  |

| SCKO   | 10      | <del></del> | Connect to GND                                                                                                                        | Output                                                                                                                                                 | Serial Cloc                         | k Outpu            | t (= In            | ternal | Clock |  |  |

| SOEN   | 11      |             | Connect to GND                                                                                                                        | Output                                                                                                                                                 | Serial Output Enable (= Active Low) |                    |                    |        |       |  |  |

| CODE   | 12      | Input       | Code Select (H = 2' s complement, L =                                                                                                 | Binary)                                                                                                                                                |                                     |                    |                    |        |       |  |  |

| DEV 1  | 13      | Input       | Division Ratio Setting                                                                                                                | DEV <sub>1</sub>                                                                                                                                       |                                     | L                  | L                  | Н      | Н     |  |  |

| DEV 0  | 14      | Input       | <del></del>                                                                                                                           | DEV <sub>0</sub>                                                                                                                                       |                                     | L                  | н                  | L      | H     |  |  |

|        | •       |             |                                                                                                                                       | Division F                                                                                                                                             | Ratio                               | 1/1                | 1/2                | 1/4    | 1/8   |  |  |

| STB    | 19      | Input       | Address strobe Input MPX addresses are latched at the rising edge of STB Input.                                                       | Input                                                                                                                                                  | Connect to GND                      |                    |                    |        |       |  |  |

| SCKI   | 21      | Input       | SCKI controls the shift operation of I/O interface shift register. Data are output at the falling edge, and input at the rising edge. | :                                                                                                                                                      | Connect to VDD                      |                    |                    |        |       |  |  |

| ĊŜ     | 22      | Input       | Chip select signal input. Low level of CS resets the internal sequence, and I/O interface is enabled.                                 | Input Internal sequence reset signal input.  Sequence controller are reset at the low level of CS, and A/D conversion starts at the rising edge of CS. |                                     |                    |                    |        | the   |  |  |

Notes: 1. In serial mode 1, the following signals are strobed by the  $\overline{\text{CS}}$  signal. Therefore, the input signals are ignored and the output terminals become high impedance when  $\overline{\text{CS}}$  = HIGH.

Input Terminal: SI, STB, SCKI

Output Terminal: SO

2. In serial mode 2, the internal sequence reset signal (CS) specifies CH7.

#### 2.1 Serial Mode 1

Serial mode 1 supports the serial data I/O when the  $\overline{CS}$  signal is at the low level, outputs the serial data from the falling edge of the serial clock signal ( $\overline{SCKI}$ ) entered from the external circuit, and fetches the serial input data at the rising edge of the  $\overline{SCKI}$  signal.

If the MSB-first data is specified (SHIFT = L), the last three bits of the 10-bit serial input data for the MPX address selection contain valid data. If the LSB-first data is specified (SHIFT = H), the first three bits of the 10-bit data for the MPX address selection contain valid data. This MPX address data latch in the  $\mu$ PD7004C is implemented when at the rising edge of the  $\overline{STB}$  signal. The latch can also be achieved at the rising edge the  $\overline{CS}$  signal, if the  $\overline{STB}$  signal is fixed at the low level.

The A/D conversion starts from the rising edge of  $\overline{CS}$  signal. The  $\overline{EOC}$  signal changes to the low level at the end of the conversion to notify this to the external environment. The time required for the A/D conversion is the same as that required in the parallel mode. The  $\overline{EOC}$  signal changes to the high level from the falling edge of  $\overline{CS}$  signal.

The A/D conversion is repeatedly operated when the  $\overline{\text{CS}}$  signal stays in the high-level and the  $\overline{\text{EOC}}$  signal remains in the low-level.

#### Serial Mode 1 Timing Chart

The 3 low-order bits of the serial input data serve as channel selection data.

| 8th     | L               | L               | L.              | L               | н               | н               | H               | Н               |

|---------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 9th     | L               | L               | Н               | н               | L               | L               | Н               | Н               |

| LSB     | L               | Н               | L               | Н               | L               | Н               | L               | Н               |

| Channel | CH <sub>0</sub> | CH <sub>1</sub> | CH <sub>2</sub> | CH <sub>3</sub> | CH <sub>4</sub> | CH <sub>5</sub> | CH <sub>6</sub> | CH <sub>7</sub> |

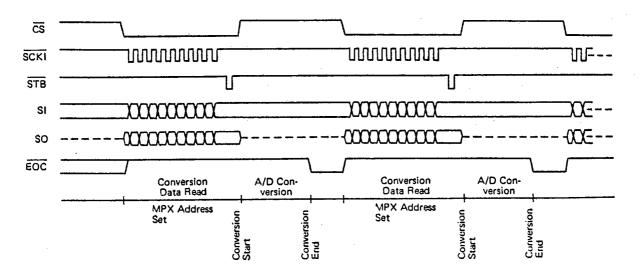

#### Serial Mode 1 Sequence Timing Chart

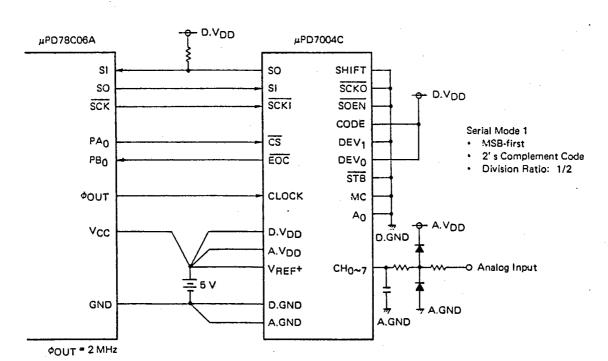

#### Example of the Interface with the $\mu$ PD78C06A

Fig. 2 shows an example of the interface with the  $\mu$ PD78C06A

Fig. 2 μPD7004C/μPD78C06A connection

$\mu$ PD78C06A contains a serial interface circuit and handles 8-bit data transfer. Therefore, the  $\mu$ PD78C06A operates 8-bit data transfer twice to handle the  $\mu$ PD7004C's 10-bit serial data transfer. The timing of the data transfer is shown in Fig. 3.

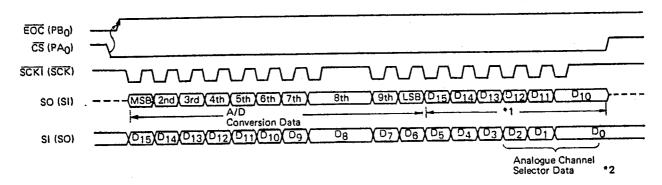

Fig. 3 Timing in serial mode 1 (connection with  $\mu PD78C06A$ )

\*1 The data entered through the SI terminal is output from SO.

\*2 Channel selector data is latched at the rising edge of the CS signal when the STB signal is fixed at the low level.

Channel selector data

| D <sub>2</sub> | L               | L               | L               | L ·             | Н               | Н               | Н               | Н               |

|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| D <sub>1</sub> | L               | L               | н               | Н               | L               | L               | Н               | H               |

| D <sub>0</sub> | L               | Н               | L               | Н               | L               | Н               | L               | Н               |

| Channel        | CH <sub>0</sub> | CH <sub>1</sub> | CH <sub>2</sub> | CH <sub>3</sub> | CH <sub>4</sub> | CH <sub>5</sub> | CH <sub>6</sub> | CH <sub>7</sub> |

#### 2.2 Serial Mode 2

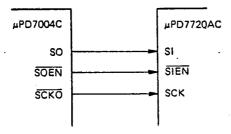

Serial mode 2 allows direct connection to the serial interface of the signal processor µPD7720AC.

Shown on the right is an example of connecting principal terminals between the  $\mu$ PD7004C and  $\mu$ PD7720AC. Serial mode 2 differs from the other two modes. This mode cannot specify the MPX address to the  $\mu$ PD7004C since the address is fixed at CH<sub>7</sub>.

Although the data through the A/D conversion consists of 10 bits, it is followed by six bits of high data when it is output as serial data.

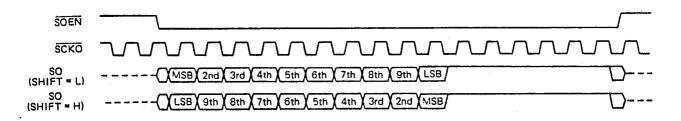

These six bits of high data always follow the converted data for MSB-first or LSB-first. (Refer to the Serial Mode 2 Timing Chart.)

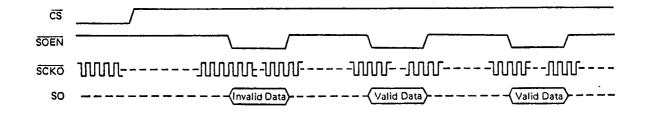

The A/D conversion sequence starts upon the initialization. The initialization is operated by holding the  $\overline{CS}$  signal at the low level for more than eight clock cycles. The A/D conversion starts when the  $\overline{CS}$  signal changes to the high-level. The A/D conversion requires 104 clock pulses (f<sub>CKI</sub>).

The EOC signal, as in the other modes, changes to the low level to notify the end of the conversion to the external environment. The EOC signal remains at the low level until the initialization is implemented.

The data converted and output immediately after the initialization is invalid. Valid data is available from the second output. This is because the MPX address is fixed at  $CH_7$  for the converted data output after the initialization. The A/D conversion and the converted data output are repeatedly operated while the  $\overline{CS}$  signal is in the high level. (Refer to the Serial Mode 2 Sequence Timing Chart.)

#### Serial Mode 2 Timing Chart

#### Serial Mode 2 Sequence Timing Chart

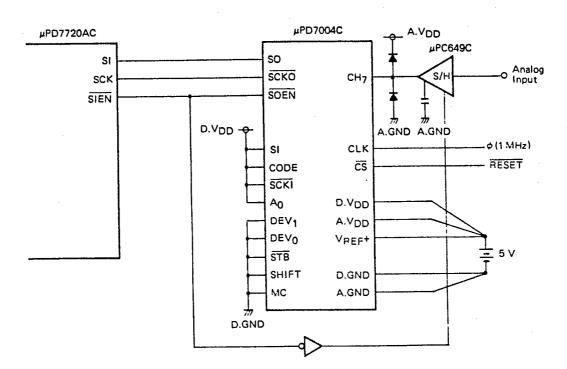

#### INTERFACE IN SERIAL MODE 2

In serial mode 2 direct connection can be made to the digital signal processor (µPD7720AC) and A/D conversion, unlike the parallel mode and serial mode 1, is operated in a periodic cycle.

Signals in the interface, unlike with serial mode 1, are controlled by the  $\mu PD7004C$ . Fig. 4 shows an example of connecting the  $\mu PD7004C$  to the  $\mu PD7720AC$ .

Fig. 4 µPD7004C/µPD7720AC connection

As shown in Fig. 4, it is possible to interface with only three kinds of signal connection lines in serial mode 2. A/D conversion is operated every 104  $\mu$ s cycle (where clock = 1 MHz). The converted data is output synchronously with the SOEN signal.

The  $\mu$ PD7720AC's serial interface operates 16-bit data transfer, while the converted data consists of 10 bits. Therefore, 6 bits of high data automatically follow the 10 bits of converted data.

In the example above, the external sample & hold circuit (µPC649C) is used and the whole operation is operated as a kind of pipe-line processing. The SOEN signal supplies valid data three cycles after the reset cancellation, and then supplies converted data every 104  $\mu s$  after this.

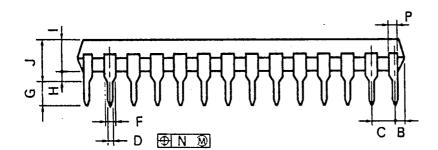

#### PACKAGE DIMENSIONS

## 28PIN PLASTIC DIP (400 mil)

P28C-100-400

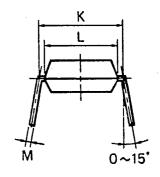

#### NOTES

- 1) Each lead centerline is located within 0.25 mm (0.01 inch) of its true position (T.P.) at maximum material condition.

- 2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS           | INCHES        |  |  |  |  |

|------|-----------------------|---------------|--|--|--|--|

| Α !  | 35.56 MAX.            | 1.400 MAX.    |  |  |  |  |

| В !  | 1.27 MAX.             | 0.050 MAX.    |  |  |  |  |

| С    | 2.54 (T.P.)           | 0.100 (T.P.)  |  |  |  |  |

| D    | 0.50 <sup>±0</sup> 10 | 0.020 = 8 8 5 |  |  |  |  |

| F    | 1.1 MIN.              | 0.043 MIN.    |  |  |  |  |

| G    | 3.5 *0 3              | 0.138 *0 012  |  |  |  |  |

| Н    | 0.51 MIN.             | 0.020 MIN.    |  |  |  |  |

| ı    | 4.31 MAX.             | 0.170 MAX.    |  |  |  |  |

| J    | 5.72 MAX.             | 0.226 MAX.    |  |  |  |  |

| К    | 10.16 (T.P.)          | 0.400 (T.P.)  |  |  |  |  |

| L    | 8.6                   | 0.339         |  |  |  |  |

| М    | 0.25 -0 05            | 0.010 -8 883  |  |  |  |  |

| N    | 0.25                  | 0.01          |  |  |  |  |

| Р    | 0.9 MIN.              | 0.035 MIN.    |  |  |  |  |