# Advanced Micro Devices

# Am486® DX4 3-Volt Processor

High-Performance, Clock-Selectable, 3.3 V, 32-Bit Microprocessor

#### DISTINCTIVE CHARACTERISTICS

## ■ Operating voltage range 3.3 V ± 0.3 V

- 120-MHz operating frequency uses a 40-MHz external bus

- 100-MHz operating frequency uses a 33-MHz external bus

- Wide range of chipsets and support available through the AMD FusionPC<sup>SM</sup> Program

#### ■ High Integration On-Chip

- 8-Kbyte code and data cache

- Floating-point unit

- Paged, virtual memory management

#### **■** High-Performance Design

- Frequent instructions execute in one clock

- 105.6-Million bytes/second burst bus at 33 MHz

- 128-Million bytes/second burst bus at 40 MHz

- 0.5-micron CMOS process technology

- Dynamic bus sizing for 8, 16, and 32-bit buses

#### ■ Complete 32-Bit Architecture

- Address and data buses

- All registers

- 8, 16, and 32-bit data types

### Multiprocessor Support

- Multiprocessor instructions

- Cache consistency protocols

- Support for second-level cache

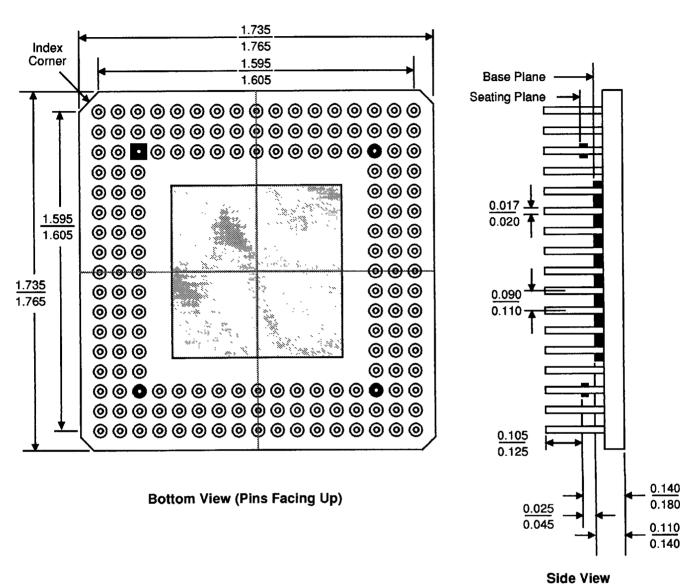

#### ■ Standard 168-Pin PGA Package

# ■ Supports Environmental Protection Agency's (EPA) "Energy Star" program

- Energy management capability provides excellent base for energy-efficient design

- Works with a variety of energy efficient, power managed devices

#### **GENERAL DESCRIPTION**

The Am486DX4 microprocessor is a high-performance 486 desktop solution that provides optimal price/performance for high-end 486 power-managed systems. The Am486DX4 CPU offers superior local bus graphics performance for Microsoft® Windows®.

Using AMD's speed-multiplying technology, the Am486DX4 CPU and cache operate two to three times faster than the external memory bus. It is manufactured using AMD's new 3.3-V CMOS process technology to consume about 2.6 watts of power at 100 MHz or 3.2 watts at 120 MHz. This 3.3-V technology provides superior solutions for low-power EPA's Energy Star Green PCs and portables.

The Am486DX4 processor operates with a 1X clock input. This 1X clock simplifies system design by reducing the clock frequency required by external devices. The 1X clock also reduces RF emission and simplifies clock generation. The input signal is doubled or tripled internally to achieve the maximum 2X or 3X operating frequency. The phases of the core clock are controlled by an internal Phase Lock Loop (PLL) circuit.

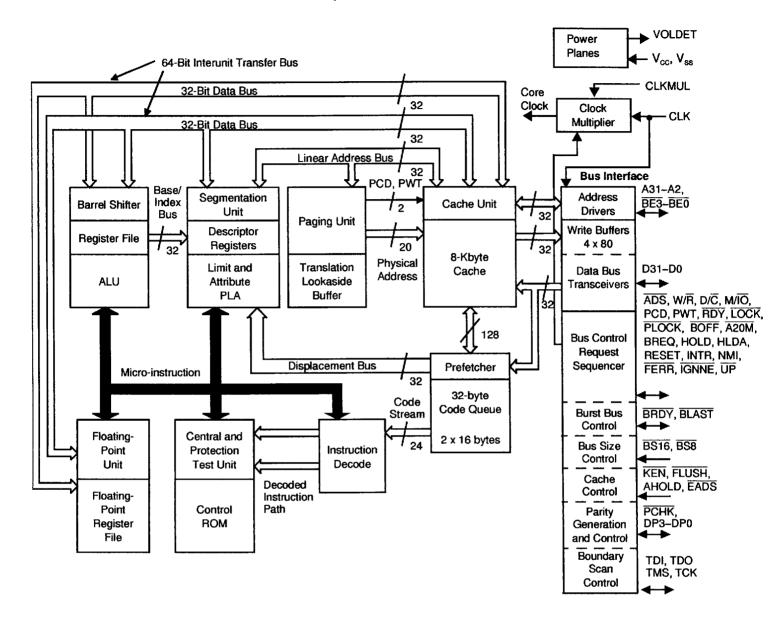

#### **BLOCK DIAGRAM**

#### Am486 CPU Pipelined 32-Bit Microarchitecture

19160C-001

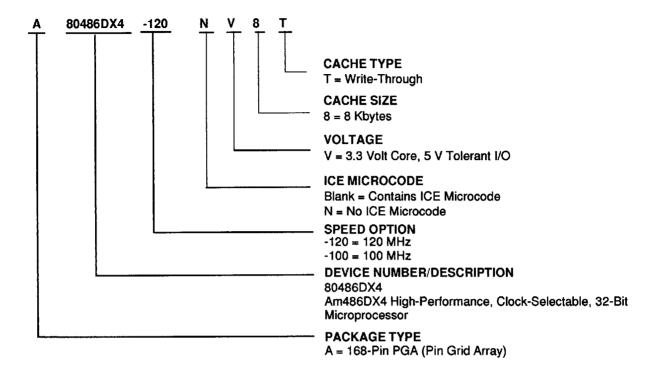

### **ORDERING INFORMATION**

### **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

| Valid Combinations |          |                      |  |  |  |  |

|--------------------|----------|----------------------|--|--|--|--|

| A                  | 80486DX4 | -120NV8T<br>-100NV8T |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

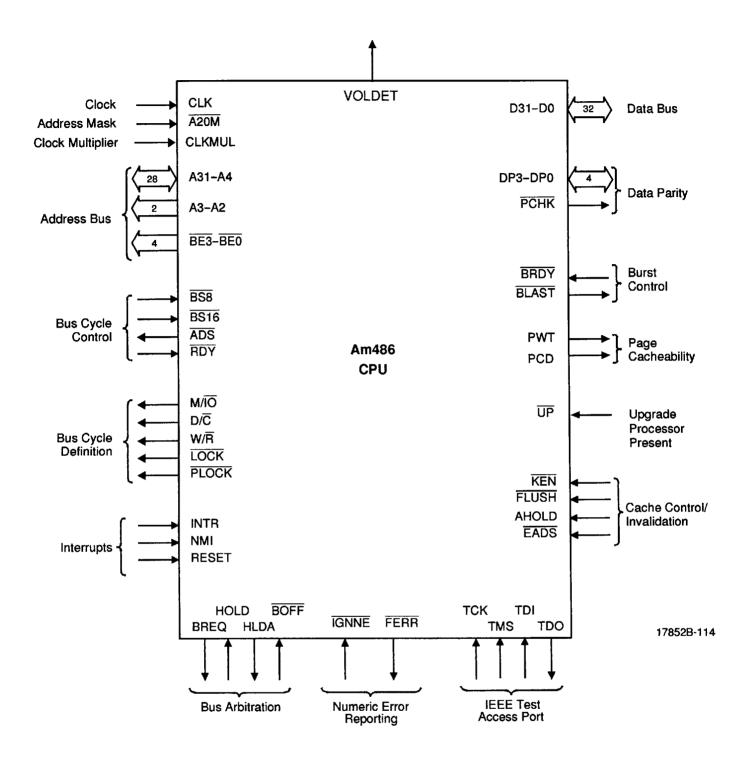

# **CONNECTION DIAGRAMS**

# Am486DX4 CPU Pin Side View

# 168-Pin PGA (Pin Grid Array) Package

|   | 1               | 2               | 3                     | 4               | 5               | 6                     | 7                     | 8                                | 9               | 10                    | 11                                | 12                    | 13       | 14                                | 15         | 16                           | 17                                |   |

|---|-----------------|-----------------|-----------------------|-----------------|-----------------|-----------------------|-----------------------|----------------------------------|-----------------|-----------------------|-----------------------------------|-----------------------|----------|-----------------------------------|------------|------------------------------|-----------------------------------|---|

| s | A27<br>O        | A26             | A23 \                 | VOLDE.          | T A14           | $\overset{v_{ss}}{O}$ | A12<br>O              | ${\overset{v_{\mathrm{ss}}}{O}}$ | v <sub>ss</sub> | $\overset{v_{SS}}{O}$ | ${\stackrel{v_{\mathrm{SS}}}{O}}$ | $\overset{v_{SS}}{O}$ | A10<br>O | ${\stackrel{v_{\mathrm{ss}}}{O}}$ | A6<br>O    | A4<br>O                      | ADS<br>O                          | s |

| R | A28<br>O        | A25             | $\overset{v_{cc}}{O}$ | v <sub>ss</sub> | A18             | $^{v_{cc}}$           | A15                   | $^{v_{cc}}$                      | $^{v_{cc}}$     | $^{v_{cc}}$           | $^{v_{cc}}$                       | A11<br>O              | 88<br>O  | $\overset{v_\infty}{O}$           | A3 Ē       | O                            | NC<br>O                           | R |

| Q | A31             | v <sub>ss</sub> | A17                   | A19             | A21             | A24<br>O              | A22<br>O              | A20                              | A16             | A13                   | A9                                | A5<br>O               | A7<br>O  | A2<br>O                           | BREQ 1     | 0                            | 0                                 | Q |

| Р | 00              | A29             | A30<br>O              |                 |                 |                       |                       |                                  |                 |                       |                                   |                       |          |                                   | HLDA<br>O  | V <sub>CC</sub><br>O<br>M/IO | V <sub>SS</sub><br>O              | Р |

| N | O<br>O          | O<br>O          | OP0                   |                 |                 |                       |                       |                                  |                 |                       |                                   |                       |          |                                   | O          | 0                            | W/R                               | N |

| м | v <sub>ss</sub> | v <sub>cc</sub> | D4<br>O               |                 |                 |                       |                       |                                  |                 |                       |                                   |                       |          |                                   | D/C        | $^{v_{cc}}$                  | v <sub>ss</sub>                   | М |

| L | v <sub>ss</sub> | D6              | D7<br><b>O</b>        |                 |                 |                       |                       |                                  |                 |                       |                                   |                       |          |                                   | PWT        | v <sub>cc</sub>              | v <sub>ss</sub>                   | L |

| к | v <sub>ss</sub> | $O_{cc}$        | D14                   |                 |                 |                       |                       |                                  |                 |                       |                                   |                       |          |                                   | BE0        | v <sub>cc</sub>              | v <sub>ss</sub>                   | к |

| J | O               | D5<br>O         | D16                   |                 |                 |                       |                       |                                  |                 |                       |                                   |                       |          |                                   | BE2        | BE1                          | PCD                               | J |

| н | v <sub>ss</sub> | O<br>D3         | DP2                   |                 |                 |                       |                       |                                  |                 |                       |                                   |                       |          |                                   | BRDY       | $^{v_{cc}}$                  | v <sub>ss</sub>                   | н |

| G | v <sub>ss</sub> | v <sub>cc</sub> | D12                   |                 |                 |                       |                       |                                  |                 |                       |                                   |                       |          |                                   | NC<br>O    | $^{v_{cc}}$                  | ${\stackrel{v_{\mathtt{SS}}}{O}}$ | G |

| F | DP1             | D8<br>O         | D15                   |                 |                 |                       |                       |                                  |                 |                       |                                   |                       |          |                                   | KEN        | RDY                          | BE3                               | F |

| E | v <sub>ss</sub> | $V_{cc}$        | D10                   |                 |                 |                       |                       |                                  |                 |                       |                                   |                       |          |                                   | HOLD       | v <sub>cc</sub>              | v <sub>ss</sub><br>O              | E |

| D | O<br>D9         | D13             | D17                   |                 |                 |                       |                       |                                  |                 |                       |                                   |                       |          |                                   | A20M       | BS8                          | BOFF                              | D |

| С | D11<br>O        | D18             | CLK<br>O              | v <sub>cc</sub> | v <sub>cc</sub> | D27                   | D26                   | D28                              | D30             | NC<br>O               | UP<br>O                           | NC<br>O               | NC<br>O  | FERR                              | FLUSH      | RESE                         | T BS16                            | С |

| В | D19             | D21             | v <sub>ss</sub>       | v <sub>ss</sub> | v <sub>ss</sub> | D25                   | $\overset{v_{cc}}{O}$ | D31                              | $^{v_{cc}}$     | NC<br>O               | o<br>O                            | NC (                  | CLKMU    | L TMS                             | О          | TDO<br>O                     | EADS                              | В |

| A | D20             | D22             | TCK<br>O              | D23             | DP3             | D24                   | v <sub>ss</sub>       | D29                              | v <sub>ss</sub> | NC<br>O               | v <sub>ss</sub>                   | NC<br>O               | NC<br>O  | O                                 | IGNNE<br>O | INTR<br>O                    | AHOLD<br>O                        | А |

|   | 1               | 2               | 3                     | 4               | 5               | 6                     | 7                     | 8                                | 9               | 10                    | 11                                | 12                    | 13       | 14                                | 15         | 16                           | 17                                | ] |

**Note:** NC = No connect. To guarantee functionality with future revisions, these pins must not be connected.

19160c-002

# **CONNECTION DIAGRAMS**

# Am486DX4 CPU Top Side View

# 168-Pin PGA (Pin Grid Array) Package

|   | 17                   | 16              | 15        | 14                       | 13             | 12                   | 11                      | 10              | 9               | 8                    | 7               | 6               | 5               | 4               | 3               | 2               | 1                                 | _ |

|---|----------------------|-----------------|-----------|--------------------------|----------------|----------------------|-------------------------|-----------------|-----------------|----------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------------------------|---|

| S | ADS<br>O             | A4<br>O         | A6<br>O   | ${\stackrel{v_{SS}}{O}}$ | A10            | v <sub>ss</sub><br>Ö | ${\overset{v_{SS}}{O}}$ | v <sub>ss</sub> | v <sub>ss</sub> | v <sub>ss</sub><br>O | A12             | v <sub>ss</sub> | A14 \<br>O      | OLDE1           | A23             | A26             | A27                               | s |

| R | NC<br>O              | BLAS            | T A3      | v <sub>cc</sub>          | 8A<br><b>O</b> | A11<br>O             | v <sub>cc</sub>         | v <sub>cc</sub> | v <sub>cc</sub> | v <sub>cc</sub>      | A15             | v <sub>cc</sub> | A18<br>O        | v <sub>ss</sub> | v <sub>cc</sub> | A25             | A28                               | R |

| Q | PCHK                 | PLOCH           | ₹ BREQ    | A2<br>O                  | A7<br>O        | A5<br>O              | A9<br>()                | A13             | A16             | A20                  | A22             | A24<br>O        | A21             | A19             | A17<br>O        | v <sub>ss</sub> | A31                               | Q |

| Р | V <sub>SS</sub>      | v <sub>cc</sub> | HLDA<br>O |                          |                |                      |                         |                 |                 |                      |                 |                 |                 |                 | A30             | A29             | D0<br>O                           | Р |

| N | w/R                  | M/ĪŌ            | LOCK      |                          |                |                      |                         |                 |                 |                      |                 |                 |                 |                 | DP0             | D1<br>O         | D2<br>O                           | N |

| М | v <sub>ss</sub>      | $^{v_{cc}}$     | D/C       |                          |                |                      |                         |                 |                 |                      |                 |                 |                 |                 | D4<br>O         | v <sub>cc</sub> | ${\stackrel{v_{SS}}{O}}$          | М |

| L | v <sub>ss</sub><br>O | $^{v_{cc}}$     | PWT       |                          |                |                      |                         |                 |                 |                      |                 |                 |                 |                 | D7<br>O         | D6              | ${\stackrel{v_{\mathrm{SS}}}{O}}$ | L |

| K | v <sub>ss</sub><br>O | v <sub>cc</sub> | BE0       |                          |                |                      |                         |                 |                 |                      |                 |                 |                 |                 | D14<br>O        | v <sub>cc</sub> | v <sub>ss</sub><br>O              | к |

| j | PCD                  | BE1             | BE2       |                          |                |                      |                         |                 |                 |                      |                 |                 |                 |                 | D16             | D5<br>O         | INC<br>O                          | J |

| Н | V <sub>SS</sub>      | 0               | BRDY      |                          |                |                      |                         |                 |                 |                      |                 |                 |                 |                 | DP2             | O<br>D3         | v <sub>ss</sub><br>O              | Н |

| G | V <sub>SS</sub>      | v <sub>cc</sub> | NC<br>O   |                          |                |                      |                         |                 |                 |                      |                 |                 |                 |                 | D12             | v <sub>cc</sub> | v <sub>ss</sub>                   | G |

| F | BE3                  | RDY             | KEN       |                          |                |                      |                         |                 |                 |                      |                 |                 |                 |                 | D15             | D8              | DP1                               | F |

| Ε | V <sub>ss</sub><br>O | 0               | HOLD      |                          |                |                      |                         |                 |                 |                      |                 |                 |                 |                 | D10             | v <sub>cc</sub> | ${\stackrel{v_{\mathrm{ss}}}{O}}$ | E |

| D | BOFF                 | 0               | A20M      |                          |                |                      |                         |                 |                 |                      |                 |                 |                 |                 | D17             | D13             | O<br>D9                           | D |

| С | 0                    | 0               | FLUSH     | 0                        | 0              | NC<br>O              | O<br>O                  | NC<br>O         | O<br>D30        | D28                  | D26             | D27             | v <sub>cc</sub> | v <sub>cc</sub> | CLK             | D18             | D11                               | С |

| В | EADS<br>O            | 0               | O         | 0                        | CLKMU          | 0                    | v <sub>cc</sub>         | NC<br>O         | o<br>O          | D31                  | v <sub>cc</sub> | D25             | V <sub>ss</sub> | V <sub>SS</sub> | v <sub>ss</sub> | D21             | D19                               | В |

| Α | AHOLD<br>O           | INTR<br>O       | GNNE      | O                        | NC<br>O        | NC<br>O              | v <sub>ss</sub>         | NC<br>O         | V <sub>SS</sub> | D29                  | v <sub>ss</sub> | D24             | O<br>DP3        | D23             | TCK<br>O        | D22             | D20                               | A |

|   | 17                   | 16              | 15        | 14                       | 13             | 12                   | 11                      | 10              | 9               | 8                    | 7               | 6               | 5               | 4               | 3               | 2               | 1                                 |   |

19160c-003

Note:

NC = No connect. To guarantee functionality with future revisions, these pins must not be connected.

# **PIN DESIGNATIONS (Functional Grouping)**

| Add         | iress      | Da          | ıta        | Con         | trol         | Te          | est        | INC/NC     | V <sub>cc</sub> | ٧,           |

|-------------|------------|-------------|------------|-------------|--------------|-------------|------------|------------|-----------------|--------------|

| Pin<br>Name | Pin<br>No. | Pin<br>Name | Pin<br>No. | Pin<br>Name | Pin<br>No.   | Pin<br>Name | Pin<br>No. | Pin<br>No. | Pin<br>No.      | Pin<br>No.   |

| A2          | Q-14       | D0          | P-1        | A20M        | D-15         | тск         | A-3        | A-10       | B-7             | A-7          |

| A3          | R-15       | D1          | N-2        | ADS         | S-17         | TDI         | A-14       | A-12       | B-9             | A-9          |

| A4          | S-16       | D2          | N-1        | AHOLD       | A-17         | TDO         | B-16       | A-13       | B-11            | A-11         |

| A5          | Q-12       | D3          | H-2        | BE0         | K-15         | TMS         | B-14       | B-10       | C-4             | B-3          |

| A6          | S-15       | D4          | M-3        | BE1         | J-16         |             |            | B-12       | C-5             | B-4          |

| A7          | Q-13       | D5          | J-2        | BE2         | J-15         |             |            | C-10       | E-2             | B-5          |

| A8          | R-13       | D6          | L-2        | BE3         | F-17         |             |            | C-12       | E-16            | E-1          |

| A9          | Q-11       | D7          | L-3        | BLAST       | R-16         |             |            | C-13       | G-2             | E-17         |

| A10         | S-13       | D8          | F-2        | BOFF        | D-17         |             |            | G-15       | G-16            | G-1          |

| A11         | R-12       | D9          | D-1        | BRDY        | H-15         |             |            | J-1        | H-16            | G-17         |

| A12         | S-7        | D10         | E-3        | BREQ        | Q-15         |             |            | R-17       | K-2             | H-1          |

| A13         | Q-10       | D11         | C-1        | BS8         | D-16         |             |            |            | K-16            | H-17         |

| A14         | S-5        | D12         | G-3        | BS16        | C-17         |             |            |            | L-16            | K-1          |

| A15         | R-7        | D13         | D-2        | CLK         | C-3          | 1           |            |            | M-2             | K-17         |

| A16         | Q-9        | D14         | K-3        | CLKMUL      | B-13         | 1           |            |            | M-16            | L-1          |

| A17         | Q-3        | D15         | F-3        | D/C         | M-15         |             |            |            | P-16            | L-17         |

| A18         | R-5        | D16         | J-3        | DP0         | N-3          |             |            |            | R-3             | M-1          |

| A19         | Q-4        | D17         | D-3        | DP1         | F-1          |             |            |            | R-6             | M-17         |

| A20         | Q-8        | D18         | C-2        | DP2         | H-3          |             |            |            | R-8             | P-17         |

| A21         | Q-5        | D19         | B-1        | DP3         | A-5          |             |            |            | R-9             | Q-2          |

| A22         | Q-7        | D20         | A-1        | EADS        | B-17         |             |            |            | R-10            | R-4          |

| A23         | S-3        | D21         | B-2        | FERR        | C-14         |             |            |            | R-11            | S-6          |

| A24         | Q-6        | D22         | A-2        | FLUSH       | C-15         | 1           |            |            | R-14            | S-8          |

| A25         | R-2        | D23         | A-4        | HLDA        | P-15         | ļ           |            |            | 1               | S-9          |

| A26         | S-2        | D24         | A-6        | HOLD        | E-15         |             |            |            | ļ               | S-10<br>S-11 |

| A27         | S-1        | D25         | B-6        | IGNNE       | A-15<br>A-16 |             |            |            | 1               | S-11         |

| A28         | R-1<br>P-2 | D26<br>D27  | C-7<br>C-6 | INTR<br>KEN | F-15         |             |            |            |                 | S-12         |

| A29<br>A30  | P-2<br>P-3 |             | C-8        | LOCK        | N-15         |             |            |            |                 | 3-14         |

| A30         | P-3<br>Q-1 | D28<br>D29  | A-8        | M/IO        | N-15<br>N-16 |             |            |            |                 | }            |

| Mai         | Q-1        | D30         | C-9        | NMI         | B-15         |             |            |            | 1               |              |

|             |            | D30         | B-8        | PCD         | J-17         | ł           |            |            |                 |              |

|             |            | 551         | D-0        | PCHK        | Q-17         |             |            | -          |                 |              |

| ł           |            |             |            | PLOCK       | Q-16         |             |            |            |                 | 1            |

|             |            |             |            | PWT         | L-15         |             |            |            |                 |              |

|             |            |             |            | RDY         | F-16         |             |            |            |                 | -            |

|             |            |             |            | RESET       | C-16         |             |            |            | Į               | 1            |

|             |            |             |            | UP          | C-11         |             |            |            | 1               |              |

|             |            | ļ           |            | VOLDET      | S-4          |             |            |            |                 |              |

|             |            |             |            | W/R         | N-17         |             |            | }          |                 | 1            |

### Notes:

INC = Internal No Connect (J-1).

NC = No Connect (A-10, A-12, A-13, B-10, B-12, C-10, C-12, C-13, G-15, R-17).

VOLDET is connected internally to  $V_{\rm ss}$

### LOGIC SYMBOL

#### PIN DESCRIPTIONS

The following paragraphs define the Am486DX4 CPU pins (signals).

#### A31-A4/A3-A2

#### Address Lines (Inputs/Outputs)/(Outputs)

A31–A2, together with the byte enables  $\overline{\text{BE3}}$ – $\overline{\text{BE0}}$ , define the physical area of memory or input/output space accessed. Address lines A31–A4 are used to drive addresses into the microprocessor to perform cache line invalidations. Input signals must meet setup and hold times,  $t_{22}$  and  $t_{23}$ . A31–A2 are not driven during bus or address hold.

#### **A20M**

# Address Bit 20 Mask (Active Low; Input)

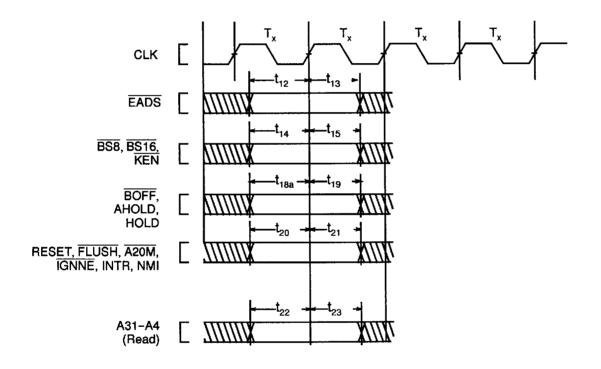

When asserted, the Am486DX4 microprocessor masks physical address bit 20 (A20) before performing a look-up to the internal cache or driving a memory cycle on the bus.  $\overline{A20M}$  emulates the address wraparound at 1 Mbyte, which occurs on the 8086.  $\overline{A20M}$  is active Low and should be asserted only when the processor is in Real Mode. This pin is asynchronous but should meet setup and hold times,  $t_{20}$  and  $t_{21}$ , for recognition in any specific clock. For proper operation,  $\overline{A20M}$  should be sampled High at the falling edge of RESET.

## **ADS**

### **Address Status (Active Low; Output)**

ADS indicates that a valid bus cycle definition and address are available on the cycle definition lines and address bus. ADS is driven active in the same clock as the addresses are driven. ADS is active Low and is not driven during bus hold.

#### **AHOLD**

#### Address Hold (Active High; Input)

This request allows another bus master access to the Am486DX4 microprocessor's address bus for a cache invalidation cycle. The Am486DX4 microprocessor stops driving its address bus in the clock following AHOLD going active. Only the address bus is floated during address hold; the remainder of the bus remains active. AHOLD is active High and is provided with a small internal pull-down resistor. For proper operation, AHOLD must meet setup and hold times,  $t_{18}$  and  $t_{19}$ .

#### BE3-BE0

#### **Byte Enables (Active Low; Outputs)**

These pins indicate active bytes during read and write cycles. During the first cycle of a cache fill, the external system should assume that all byte enables are active. BE3 applies to D31–D24, BE2 applies to D23–D16, BE1 applies to D15–D8, and BE0 applies to D7–D0. BE3–BE0 are active Low and are not driven during bus hold.

The Am486DX4 processor provides four special bus cycles to indicate that certain instructions have been executed, or certain conditions have occurred internally. The special bus cycles (in Table 1) are defined when the bus cycle definition pins are in the following state:  $M/\overline{IO}=0$ ,  $D/\overline{C}=0$ , and  $W/\overline{R}=1$ . During these cycles the address bus is driven Low while the data bus is undefined.

The external hardware must acknowledge these special bus cycles by returning RDY and BRDY.

Table 1 . Special Bus Cycle Encoding

| BE3 | BE2 | BE1 | BE0 | Special Bus Cycles |

|-----|-----|-----|-----|--------------------|

| 1   | 1   | 1   | 0   | Shutdown           |

| 1   | 1   | 0   | 1   | Flush              |

| 1   | 0   | 1   | 1   | Halt               |

| 0   | 1   | 1   | 1   | Write Back         |

#### **BS8/BS16**

# Bus Size 8 (Active Low; Input)/ Bus Size 16 (Active Low; Input)

These pins cause the Am486DX4 microprocessor to run multiple bus cycles to complete a request from devices that cannot provide or accept 32 bits of data in a single cycle. The bus sizing pins are sampled every clock. The state of these pins in the clock before  $\overline{\text{RDY}}$  is used by the Am486DX4 microprocessor to determine the bus size. These signals are active Low and are provided with internal pull-up resistors. These inputs must satisfy setup and hold times,  $t_{14}$  and  $t_{15}$ . for proper operation.

#### BLAST

#### **Burst Last (Active Low; Output)**

BLAST indicates that the next time BRDY is returned, then the burst bus cycle is complete. BLAST is active for both burst and non-burst bus cycles. BLAST is active Low and is not driven during bus hold.

#### **BOFF**

#### **Backoff (Active Low; Input)**

This input pin forces the Am486DX4 microprocessor to float its bus in the next clock. The microprocessor floats all pins normally floated during bus hold, but HLDA is not asserted in response to BOFF. BOFF has higher priority than RDY or BRDY; if both are returned in the same clock, BOFF takes effect. The microprocessor remains in bus hold until BOFF is negated. If a bus cycle is in progress when BOFF is asserted, the cycle is restarted. BOFF is active Low and must meet setup and hold times, t<sub>18a</sub> and t<sub>19</sub>. for proper operation.

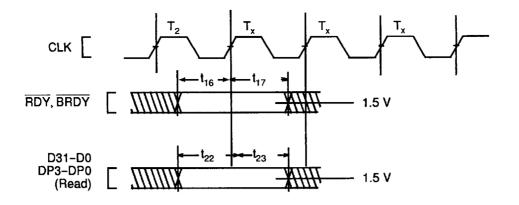

#### BRDY

#### **Burst Ready Input (Active Low; Input)**

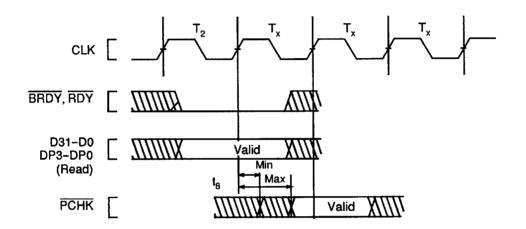

This input pin performs the same cycle during a burst cycle that RDY performs during a non-burst cycle. BRDY indicates that the external system has presented valid data in response to a read or that the external system has accepted data in response to write. BRDY is ignored when the bus is idle and at the end of the first clock in a bus cycle. BRDY is sampled in the second and subsequent clocks of a burst cycle. The data presented on the data bus is strobed into the microprocessor when BRDY is sampled active. If RDY is returned simultaneously with BRDY, BRDY is ignored and the burst cycle is prematurely aborted. BRDY is active Low and is provided with a small pull-up resistor. BRDY must satisfy the setup and hold times, t<sub>16</sub> and t<sub>17</sub>.

# BREQ Internal Cycle Pending (Active High; Output)

BREQ indicates that the Am486DX4 microprocessor has internally generated a bus request. BREQ is generated whether or not the Am486DX4 microprocessor is driving the bus. BREQ is active High and is never floated, except for three-state test mode (see FLUSH).

#### CLK

#### Clock (Input)

CLK is a 1X clock providing the fundamental timing for the bus interface unit and is multiplied in accordance with the CLKMUL pin to provide the internal frequency for the Am486DX4 microprocessor. All external timing parameters are specified with respect to the rising edge of CLK.

#### **CLKMUL**

#### **Clock Multiplier (Input)**

The clock multiplier input defines the ratio of internal core clock frequency to external bus frequency. If sampled Low, the core frequency operates at twice the external bus frequency (speed-double mode). If driven High or left floating speed-triple mode is selected. CLK-MUL has an internal pull-up to  $V_{\rm CC}$  and may be left floating in designs that wish to select speed-triple clock mode.

#### D31-D0

#### Data Lines (Inputs/Outputs)

Lines D7–D0 define the least significant byte and lines D31–D24 define the most significant byte. These signals must meet setup and hold times  $t_{22}$  and  $t_{23}$  for proper operation on reads. The pins are driven during the second and subsequent write cycle clocks.

#### D/C. M/IO. W/R

# Data/Control, Memory/Input/Output, Write/Read (Active High/Active Low; Output)

These are the primary bus definition signals (in Table 2). These signal are driven valid as the ADS signal is asserted. The bus definition signals are not driven during bus hold and follow the timing of the address bus.

The D/C bus cycle definition pin distinguishes memory and I/O data cycles (D) from the control cycles (C): interrupt acknowledge, halt, and instruction fetching.

The M/IO bus cycle definition pin distinguishes memory cycles (M) from input/output cycles (IO).

The  $W/\overline{R}$  bus definition pin distinguishes write cycles from read cycles.

**Table 2. Bus Cycle Definition**

| M/IO | D/C | W/R | Bus Cycle Initiated   |

|------|-----|-----|-----------------------|

| 0    | 0 0 | 0.1 | Interrupt Acknowledge |

|      | 0   | 1   | Halt/Special Cycle    |

|      |     | 0   | I/O Read              |

| 0    | 1   | 1   | I/O Write             |

| 1 1  | 🖔   | U   | Code Read             |

| 1 1  | 0   |     | Reserved              |

| 1 1  | ] ] | U   | Memory Read           |

| 1    | ]   | 1   | Memory Write          |

#### DP3-DP0

#### Data Parity (Active High; Inputs/Outputs)

Data parity is generated on all write data cycles using the same timing as the data lines. Even parity information must be driven back into the microprocessor on the data parity pins with the same timing as read information. This process ensures that the correct parity check status is indicated. The signals read on these pins do not affect program execution. Input signals must meet setup and hold times,  $t_{22}$  and  $t_{23}$ . DP3–DP0 should be connected to  $V_{\rm CC}$  through a pull-up resistor in systems not using parity. DP3–DP0 are active High and are driven during the second and subsequent clocks of write cycles.

#### **EADS**

#### Valid External Address (Active Low; Input)

This pin indicates a valid external address has been driven onto the Am486DX4 microprocessor address pins. This address is used to perform an internal cache invalidation cycle.  $\overline{EADS}$  is active Low and is provided with an internal pull-up resistor.  $\overline{EADS}$  must satisfy setup and hold times,  $t_{12}$  and  $t_{13}$ , for proper operation.

#### **FERR**

#### Floating-Point Error (Active Low; Output)

Driven active when a floating-point error occurs. FERR is similar to the ERROR pin on a 387 math coprocessor.

FERR is included for compatibility with systems using DOS-type floating-point error reporting. FERR is active Low, and is not floated during bus hold, except during three-state test mode (see FLUSH).

#### **FLUSH**

#### Cache Flush (Active Low; Input)

$\overline{\text{FLUSH}}$  forces the Am486DX4 microprocessor to flush its entire internal cache.  $\overline{\text{FLUSH}}$  is active Low and need only be asserted for one clock.  $\overline{\text{FLUSH}}$  is asynchronous but setup and hold times,  $t_{20}$  and  $t_{21}$ , must be met for recognition in any specific clock.  $\overline{\text{FLUSH}}$  being sampled Low in the clock before the falling edge of RESET causes the Am486DX4 microprocessor to enter the three-state test mode.

#### **HLDA**

#### Hold Acknowledge (Active High; Output)

HLDA goes active in response to a hold request presented on the HOLD pin. HLDA indicates that the Am486DX4 microprocessor has given the bus to another local bus master. HLDA is driven active in the same clock that the Am486DX4 microprocessor floats its bus. HLDA is driven inactive when leaving bus hold. HLDA is active High and remains driven during bus hold. HLDA is never floated except during three-state test mode (see FLUSH).

#### HOLD

#### **Bus Hold Request (Active High; Input)**

This input pin allows another bus master complete control of the Am486DX4 microprocessor bus. In response to HOLD going active, the Am486DX4 microprocessor floats most of its output and input/output pins. HLDA is asserted after completing the current bus cycle, burst cycle, or sequence of locked cycles. The Am486DX4 microprocessor remains in this state until HOLD is deasserted. HOLD is active High and is not provided with an internal pull-down resistor. HOLD must satisfy setup and hold times  $t_{18}$  and  $t_{19}$  for proper operation.

#### **IGNNE**

#### Ignore Numeric Error (Active Low; Input)

When this pin is asserted, the Am486DX4 microprocessor will ignore a numeric error and continue executing non-control floating-point instructions. When  $\overline{\text{IGNNE}}$  is deasserted, the Am486DX4 microprocessor will freeze on a non-control floating-point instruction if a previous floating-point instruction caused an error.  $\overline{\text{IGNNE}}$  has no effect when the NE bit in Control Register 0 is set.  $\overline{\text{IGNNE}}$  is active Low and is provided with a small internal pull-up resistor.  $\overline{\text{IGNNE}}$  is asynchronous but must meet setup and hold times,  $t_{20}$  and  $t_{21}$ , to ensure recognition in any specific clock.

#### INTR

#### Maskable Interrupt (Active High; Input)

INTR indicates an external interrupt has been generated. If the internal interrupt flag is set in EFLAGS, active interrupt processing is initiated. The Am486DX4 microprocessor generates two locked interrupt acknowledge bus cycles in response to the INTR pin going active. INTR must remain active until the interrupt acknowledges have been performed. This ensures that the interrupt is recognized. INTR is active High and is not provided with an internal pull-down resistor. INTR is asynchronous, but must meet setup and hold times,  $t_{20}$  and  $t_{21}$ , for recognition in any specific clock.

#### KEN

#### Cache Enable (Active Low; Input)

KEN is used to determine whether the current cycle is cacheable. When the Am486DX4 microprocessor generates a cacheable cycle and  $\overline{\text{KEN}}$  is active, the cycle becomes a cache line fill cycle. Returning  $\overline{\text{KEN}}$  active one clock before  $\overline{\text{RDY}}$  during the last read in the cache line fill causes the line to be placed in the on-chip cache.  $\overline{\text{KEN}}$  is active Low and is provided with a small internal pull-up resistor.  $\overline{\text{KEN}}$  must satisfy setup and hold times,  $t_{14}$  and  $t_{15}$ , for proper operation.  $\overline{\text{LOCK}}$

#### **Bus Lock (Active Low; Output)**

LOCK indicates the current bus cycle is locked. The Am486DX4 microprocessor does not allow a bus hold when LOCK is asserted (but address holds are allowed). LOCK goes active in the first clock of the first locked bus cycle and goes inactive after the last clock of the last locked bus cycle. The last locked cycle ends when RDY is returned. LOCK is active Low and is not driven during bus hold. Locked read cycles are not transformed into cache fill cycles if KEN is active.

#### **NMI**

#### Non-Maskable Interrupt (Active High; Input)

A high NMI signal indicates that external non-maskable interrupt occurred. NMI is rising edge sensitive, but must be held Low for at least four-CLK periods before the rising edge. NMI does not have an internal pull-down resistor. NMI is asynchronous, but must meet setup and hold times,  $t_{20}$  and  $t_{21}$ , for recognition in any specific clock.

#### PCD/PWT

# Page Cache Disable/Page Write-Through (Active High; Outputs)

The outputs reflect the state of the page attribute bits, PWT and PCD, in the page table or page directory entry. If paging is disabled or unpaged cycles occur, PWT and PCD reflect the state of the PWT and PCD bits in Control Register 3. PWT and PCD have the same timing as the cycle definition pins (M/IO, D/C, and W/R). PWT and PCD are active High and are not driven during bus hold. PCD is masked by the Cache Disable Bit (CD) in Control Register 0.

#### **PCHK**

#### Parity Status (Active Low; Output)

Parity status is driven on the PCHK pin the clock after RDY for read operations for data sampled at the end of the previous clock. A parity error is indicated by PCHK being Low. Parity status is only checked for enabled bytes as indicated by the byte enable and bus size signals. PCHK is valid only in the clock immediately after read data is returned to the microprocessor. At all other times PCHK is inactive High. PCHK is never floated except during three-state test mode (see FLUSH).

#### **PLOCK**

#### Pseudo-Lock (Active Low; Output)

PLOCK indicates that the current bus transaction requires more than one bus cycle to complete. Examples of such operations are floating-point long reads and writes (64 bits), segment table descriptor reads (64 bits), and cache line fills (128 bits). The Am486DX4 microprocessor drives PLOCK active until the addresses for the last bus cycle of the transaction have been driven, regardless of whether RDY or BRDY has been returned. Normally PLOCK and BLAST are inverse of each other. However, during the first bus cycle of a 64-bit floating-point write, both PLOCK and BLAST will be asserted. PLOCK is a function of the BS8, BS16, and KEN inputs. PLOCK should be sampled only if the clock RDY is returned. PLOCK is active Low and is not driven during bus hold.

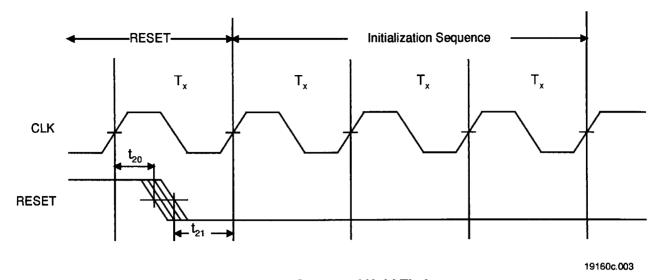

#### **RESET**

#### Reset (Active High; Input)

This pin forces the Am486DX4 microprocessor to begin execution at a known state. The microprocessor cannot begin execution of instructions until at least 1 ms after  $V_{\rm CC}$  and CLK have reached their proper DC and AC specifications. The RESET pin should remain active during this time to ensure proper microprocessor operation. RESET is active High. RESET is asynchronous but must meet setup and hold times,  $t_{\rm 20}$  and  $t_{\rm 21}$ , for recognition in any specific clock.

#### **RDY**

#### Non-Burst Ready (Active Low; Input)

This input pin indicates that the current bus cycle is complete. RDY indicates that the external system has presented valid data on the data pins in response to a read, or that the external system has accepted data from the Am486DX4 microprocessor in response to a write. RDY is ignored when the bus is idle and at the end of the bus cycle's first clock.

RDY is active during address hold. Data can be returned to the processor while AHOLD is active.

$\overline{\text{RDY}}$  is active Low and is not provided with an internal pull-up resistor.  $\overline{\text{RDY}}$  must satisfy setup and hold times,  $t_{16}$  and  $t_{17}$ , for proper chip operation.

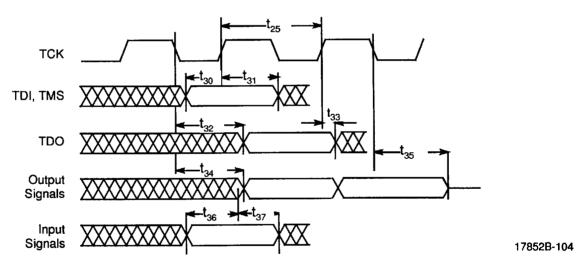

#### TCK

#### **Test Clock (Input)**

Test Clock is an input to the Am486DX4 CPU and provides the clocking function required by the JTAG boundary scan feature. TCK is used to clock state information and data into and out of the component. State select information and data are clocked into the component on the rising edge of TCK on TMS and TDI, respectively. Data is clocked out of the component on the falling edge of TCK on TDO.

#### TDI

#### **Test Data Input (Input)**

TDI is the serial input used to shift JTAG instructions and data into the component. TDI is sampled on the rising edge of TCK, during the SHIFT-IR and the SHIFT-DR TAP controller states. During all other tap controller states, TDI is a "don't care."

#### **TDO**

#### **Test Data Output (Output)**

TDO is the serial output used to shift JTAG instructions and data out of the component. TDO is driven on the falling edge of TCK during the SHIFT-IR and SHIFT-DR Test Access Port (TAP) controller states. At all other times, TDO is driven to the high-impedance state.

#### **TMS**

#### **Test Mode Select (Input)**

TMS is decoded by the JTAG TAP to select the operation of the test logic. TMS is sampled on the rising edge of TCK. To guarantee deterministic behavior of the TAP controller, TMS is provided with an internal pull-up resistor.

#### **UP**

#### **Upgrade Present (Active Low; Input)**

The Upgrade Present pin forces the Am486DX4 CPU to three-state all its outputs and enter the power-down mode. When the Upgrade Present pin is sampled asserted by the CPU in the clock before the falling edge of RESET, the power-down mode is enabled. UP has no effect on the power-down status except during this edge. The CPU is also forced to three-state all of its outputs immediately in response to this signal. The UP signal must remain asserted in order to keep the pins three-state. UP is active Low and is provided with an internal pull-up resistor.

#### **VOLDET**

#### Voltage Detect (Active Low; Output)

The voltage detect signal allows external system logic to distinguish between a 5-V Am486 processor and the 3.3-V Am486DX4 processor. The signal is active Low for a 3.3-V Am486DX4 processor.

**Table 3. Output Pins**

| Name                                                                                 | Active<br>Level                                        | Floated At                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BREQ HLDA BE3-BE0 PCD/PWT W/R, D/C, M/IO LOCK PLOCK ADS BLAST PCHK A3-A2 FERR VOLDET | High High Low High Low Low Low Low Low Low Low Low Low | Three-State Test Mode Three-State Test Mode Bus Hold Three-State Test Mode Three-State Test Mode Three-State Test Mode |

Table 4. Input Pins

| Name      | Active<br>Level | Synchronous/<br>Asynchronous |

|-----------|-----------------|------------------------------|

| CLK       | _               | -                            |

| RESET     | High            | Asynchronous                 |

| HOLD      | High            | Synchronous                  |

| AHOLD     | High            | Synchronous                  |

| EADS      | Low             | Synchronous                  |

| BOFF      | Low             | Synchronous                  |

| FLUSH     | Low             | Asynchronous                 |

| A20M      | Low             | Asynchronous                 |

| BS16, BS8 | Low             | Synchronous                  |

| KEN       | Low             | Synchronous                  |

| RDY       | Low             | Synchronous                  |

| BRDY      | Low             | Synchronous                  |

| INTR      | High            | Asynchronous                 |

| NMI       | High            | Asynchronous                 |

| UP        | Low             | Asynchronous                 |

| IGNNE     | Low             | Asynchronous                 |

| CLKMUL    | _               |                              |

Table 5. Input/Output Pins

| Name    | Active<br>Level | Floated At        |

|---------|-----------------|-------------------|

| D31D0   | High            | Bus Hold          |

| DP3-DP0 | High            | Bus Hold          |

| A31-A4  | High            | Bus, Address Hold |

Table 6. Test Pins

| Name                     | Input or Output                   | Sampled/Driven On                                             |

|--------------------------|-----------------------------------|---------------------------------------------------------------|

| TCK<br>TDI<br>TDO<br>TMS | Input<br>Input<br>Output<br>Input | N/A Rising Edge of TCK Falling Edge of TCK Rising Edge of TCK |

#### **CPU IDENTIFICATION CODES**

The DX register always contains a component identification at the conclusion of RESET. The upper byte of DX (DH) contains 04 and the lower byte of DX (DL) contains a CPU type/stepping identifier.

Table 7. CPU ID

| Component ID | Component ID |

|--------------|--------------|

| (DH)         | (DL)         |

| 04           | 32           |

Table 8, JTAG ID Code

| Version Code | Part Number<br>Code | Manufacturer<br>Identity |

|--------------|---------------------|--------------------------|

| 00h          | 0432                | 01                       |

#### ARCHITECTURAL OVERVIEW

The Am486DX4 processor is a 32-bit architecture with on-chip memory management and cache memory units. It is a fully compatible member of the Am486 Family.

On-chip cache memory allows frequently used data and code to be stored on-chip, thereby reducing accesses to the external bus. A clock multiplier has been added to speed up internal operations. RISC design techniques are used to reduce instruction cycle times. A burst bus feature enables fast cache fills.

The Am486 CPU Memory Management Unit (MMU) consists of a segmentation unit and a paging unit. Segmentation allows management of the logical address space by providing easy data and code relocatibility and efficient sharing of global resources. The paging mechanism operates beneath segmentation and is transparent to the segmentation process. Paging is optional and can be disabled by system software. Each segment can be divided into one or more 4-Kbyte segments. To implement a virtual memory system, the Am486DX4 microprocessor supports full restartability for all page and segment faults.

Memory is organized into one or more variable length segments, each up to 4 Gbyte (232 bytes) in size. A segment can have attributes associated with it. These

attributes include its location, size, type (i.e., stack, code, or data), and protection characteristics. Each task on an Am486DX4 microprocessor can have a maximum of 16,381 segments, each up to 4 Gbyte in size. Thus, each task has a maximum of 64 Tbyte (terabytes) of virtual memory.

The segmentation unit provides four levels of protection for isolating and protecting applications and the operating system from each other. The hardware enforced protection allows high integrity system designs.

The Am486DX4 microprocessor has three modes of operation: Real Address Mode (Real Mode), Virtual Address Mode (Protected Mode), and within Protected Mode, tasks may be performed in Virtual 8086 Mode. In Real Mode, the Am486DX4 microprocessor operates as a very fast 8086. Real Mode is required primarily to set up the processor for Protected Mode operation. Protected Mode provides access to the sophisticated memory management paging and privilege capabilities of the processor.

Within Protected Mode, software can perform a task switch to enter into tasks designated as Virtual 8086 Mode tasks. Each Virtual 8086 task behaves with 8086 semantics, allowing 8086 software (an application program or an entire operating system) to execute.

The on-chip cache is 8 Kbyte. It is four-way set associative and follows a write-through policy. The on-chip cache includes features that provide flexibility in external memory system design. Individual pages can be designated as cacheable or non-cacheable by software or hardware. The cache can also be enabled and disabled by software or hardware.

Finally, the Am486DX4 microprocessor has features that facilitate high-performance hardware designs. The clock multiplier improves execution performance without increasing the board design complexity. This clock multiplier enhances all operations operating out of the cache and/or not blocked by external bus assesses. The burst bus feature enables fast cache fills.

#### **ELECTRICAL DATA**

The following sections describe recommended electrical connections for the Am486DX4 microprocessor and its electrical specifications.

## **Power and Grounding**

#### **Power Connections**

The Am486DX4 CPU is implemented in 0.5 micron CMOS 3-layer metal technology and has modest power requirements. However, its high clock frequency output buffers can cause power surges as multiple output buffers drive new signal levels simultaneously. For clean, on-chip power distribution at high frequency, 23  $V_{\rm CC}$  and 28  $V_{\rm SS}$  pins feed the Am486DX4 microprocessor.

Power and ground connections must be made to all external  $V_{CC}$  and GND pins of the Am486DX4 microprocessor. On the circuit board, all  $V_{CC}$  pins must be connected on a  $V_{CC}$  plane. All  $V_{SS}$  pins must likewise be connected on a GND plane.

#### **Power Decoupling Recommendations**

Liberal decoupling capacitance should be placed near the Am486DX4 microprocessor. The Am486DX4 microprocessor, driving its 32-bit parallel address and data buses at high frequencies, can cause transient power surges, particularly when driving large capacitive loads. Low inductance capacitors and interconnects are recommended for best high-frequency electrical performance. Inductance can be reduced by shortening circuit board traces between the Am486DX4 CPU, and decoupling capacitors as much as possible. Capacitors specifically for PGA packages are also commercially available.

#### **System Clock Recommendations**

The CLK input to the Am486DX4 processor should not be driven until  $V_{\rm CC}$  has reached its normal operating level (3.3 V). Once  $V_{\rm CC}$  has reached its normal operating level, the Am486DX4 CPU can handle the clock frequency for which it is specified and the oscillator/clock driver should have locked onto its desired frequency.

#### **Other Connection Recommendations**

NC pins should always remain unconnected.

For reliable operation, always connect unused inputs to an appropriate signal level. Active Low inputs should be connected to  $V_{CC}$  through a pull-up resistor. Pull-ups in the range of 20 K $\Omega$  are recommended. Active High inputs should be connected to GND.

INC is electrically isolated and has no special requirements.

#### **ABSOLUTE MAXIMUM RATINGS**

Case Temperature under Bias......-65°C to +110°C

Storage Temperature....-65°C to +150°C

Voltage on any pin

with respect to ground ....-0.5 V to V<sub>CC</sub> +2.6 V

Supply voltage with

respect to V<sub>SS</sub>.....-0.5 V to +4.6 V

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability.

# **OPERATING RANGES**

#### Commercial (C) Devices

| T <sub>CASE</sub> | 0°C to +85°C  |

|-------------------|---------------|

| V <sub>cc</sub>   | 3.3 V ± 0.3 V |

Operating Ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over COMMERCIAL operating ranges

Functional Operating Range:  $V_{CC}$ = 3.3 V ± 0.3 V;  $T_{CASE}$ =0°C to +85°C.

|                  |                           |                                      | Preliminary |                      |      |  |

|------------------|---------------------------|--------------------------------------|-------------|----------------------|------|--|

| Symbol           | Parameter Description     | Notes                                | Min         | Max                  | Unit |  |

| V <sub>IL</sub>  | Input Low Voltage         |                                      | -0.3        | +0.8                 | ٧    |  |

| V <sub>IH</sub>  | Input High Voltage        |                                      | 2.0         | V <sub>CC</sub> +2.4 | ٧    |  |

| V <sub>OL</sub>  | Output Low Voltage        | I <sub>OL</sub> =(Note 1)            |             | 0.45                 | ٧    |  |

| V <sub>OH</sub>  | Output High Voltage       | I <sub>OH</sub> =(Note 2)            | 2.4         |                      | ٧    |  |

| I <sub>cc</sub>  | Power Supply Current      | 100 MHz (Note 3)<br>120 MHz (Note 3) |             | 1000<br>1200         | mA   |  |

| l <sub>LI</sub>  | Input Leakage Current     | (Note 4)<br>(Note 8)                 |             | ±15<br>±50           | μА   |  |

| l <sub>IH</sub>  | Input Leakage Current     | (Note 5)                             |             | 200                  | μА   |  |

| I <sub>IL</sub>  | Input Leakage Current     | (Note 6)                             |             | -400                 | μΑ   |  |

| I <sub>LO</sub>  | Output Leakage Current    | (Note 9)<br>(Note 10)                |             | ±15<br>±50           | μА   |  |

| CIN              | Input Capacitance         | F <sub>C</sub> =1 MHz (Note 7)       |             | 10                   | рF   |  |

| C <sub>OUT</sub> | I/O or Output Capacitance | F <sub>C</sub> =1 MHz (Note 7)       |             | 14                   | pF   |  |

| C <sub>CLK</sub> | CLK Capacitance           | F <sub>C</sub> =1 MHz (Note 7)       |             | 12                   | pF   |  |

#### Notes:

1. This parameter is measured at: Address, Data, BE3-BE0

4.0 mA

Definition, Control

5.0 mA

2. This parameter is measured at: Address, Data, BE3

-1.0 mA -0.9 mA

Address, Data, BE3-BE0

Definition, Control

- 3. Typical supply current: 800 mA @ 100 MHz or 960 mA @ 120 MHz

- 4. This parameter is for inputs without pull-ups or pull-downs and  $0 \le V_{IN} \le V_{CC}$ .

- 5. This parameter is for inputs with pull-downs and  $V_{H}$ =2.4 V.

- 6. This parameter is for inputs with pull-ups and  $V_{ii}$ =0.45 V.

- 7. Not 100% tested.

- 8. This parameter is for inputs without pull-ups or pull-downs and  $V_{cc} \le V_{IN} \le 5V$ .

- 9. This parameter is for three-state outputs where  $V_{EXT}$  is driven on the three-state output and  $0 \le V_{EXT} \le V_{CC}$ .

- 10. This parameter is for three-state outputs where  $V_{EXT}$  is driven on the three-state output and  $V_{CC} \le V_{EXT} \le 5V$ .

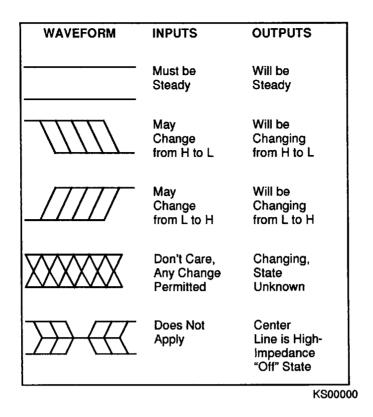

# **SWITCHING CHARACTERISTICS**

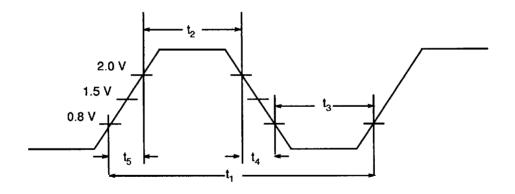

The switching characteristics consist of output delays, input setup requirements, and input hold requirements. All switching characteristics are relative to the rising edge of the CLK signal.

The switching characteristics measurements are defined by Figures 2–9. Inputs must be driven to the voltage levels indicated by Figure 2 when switching characteristics are measured.

Am486DX4 microprocessor output delays are specified with minimum and maximum limits. The minimum Am486DX4 microprocessor delay times are hold times provided to external circuitry. Am486DX4 microprocessor input setup and hold times are specified as minimums, defining the smallest acceptable sampling windows. Within the sampling windows, a synchronous input signal must be stable for correct Am486DX4 microprocessor operation.

# **SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges**

Operating Frequency/Bus Frequency: 120/40MHz; T<sub>CASE</sub>=0°C to +85°C; C<sub>L</sub>=50 pF unless otherwise specified.

|                  |                                                                                          |                 |        | Preliminar |      |      |

|------------------|------------------------------------------------------------------------------------------|-----------------|--------|------------|------|------|

| Symbol           | Parameter Description                                                                    | Notes           | Figure | Min        | Max  | Unit |

|                  | Operating Frequency                                                                      |                 |        | 8          | 40   | MHz  |

| t <sub>1</sub>   | CLK Period                                                                               |                 | 2      | 25         | 125  | ns   |

| t <sub>1a</sub>  | CLK Period Stability                                                                     | Adjacent Clocks |        |            | 0.1% | Δ    |

| t <sub>2</sub>   | CLK High Time                                                                            | @ 2.0 V         | 2      | 9          |      | ns   |

| t <sub>3</sub>   | CLK Low Time                                                                             | @ 0.8 V         | 2      | 9          |      | ns   |

| t <sub>4</sub>   | CLK Fall Time                                                                            |                 | 2      |            | 3    | ns   |

| t <sub>5</sub>   | CLK Rise Time                                                                            |                 | 2      |            | 3    | ns   |

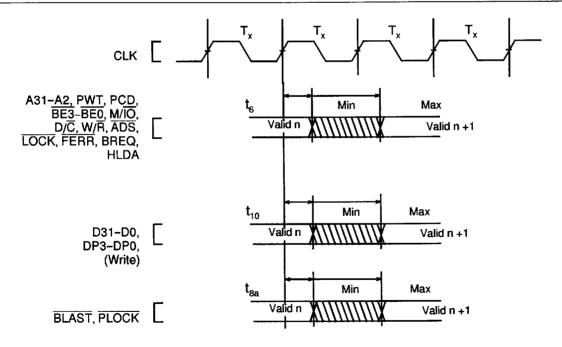

| t <sub>6</sub>   | A31-A2, PWT, PCD, M/IO, BE3-BE0, D/C,<br>W/R, ADS, LOCK, FERR, BREQ, HLDA<br>Valid Delay |                 | 7      | 3          | 14   | ns   |

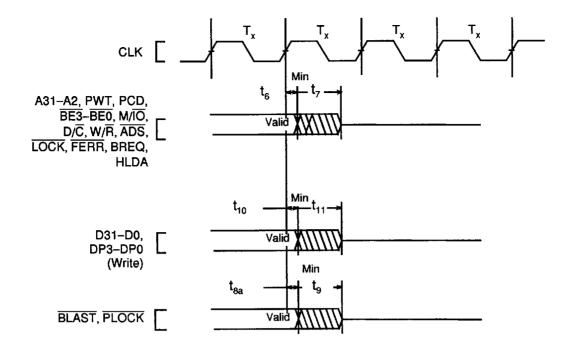

| t <sub>7</sub>   | A31-A2, PWT, PCD, M/IO, BE3-BE0, D/C,<br>W/R, ADS, LOCK, FERR, BREQ, HLDA Float<br>Delay | (Note 1)        | 8      | 3          | 18   | ns   |

| t <sub>8</sub>   | PCHK Valid Delay                                                                         |                 | 6      | 3          | 16   | ns   |

| t <sub>8a</sub>  | BLAST, PLOCK Valid Delay                                                                 |                 | 7      | 3          | 18   | ns   |

| t <sub>9</sub>   | BLAST, PLOCK Float Delay                                                                 | (Note 1)        | 8      | 3          | 16   | ns   |

| t <sub>10</sub>  | D31-D0, DP3-DP0 Write Data Valid Delay                                                   |                 | 7      | 3          | 16   | ns   |

| t <sub>11</sub>  | D31-D0, DP3-DP0 Write Data Float Delay                                                   | (Note 1)        | 8      | 3          | 18   | ns   |

| t <sub>12</sub>  | EADS Setup Time                                                                          |                 | 4      | 5          |      | ns   |

| t <sub>13</sub>  | EADS Hold Time                                                                           |                 | 4      | 3          |      | ns   |

| t <sub>14</sub>  | KEN, BS16, BS8 Setup Time                                                                |                 | 4      | 5          |      | ns   |

| t <sub>15</sub>  | KEN, BS16, BS8 Hold Time                                                                 |                 | 4      | 3          |      | ns   |

| t <sub>16</sub>  | RDY, BRDY Setup Time                                                                     |                 | 5      | 5          |      | ns   |

| t <sub>17</sub>  | RDY, BRDY Hold Time                                                                      |                 | 5      | 3          |      | ns   |

| t <sub>18</sub>  | HOLD, AHOLD Setup Time                                                                   |                 | 4      | 6          |      | ns   |

| t <sub>18a</sub> | BOFF Setup Time                                                                          |                 | 4      | 8          |      | ns   |

| t <sub>19</sub>  | HOLD, AHOLD, BOFF Hold Time                                                              |                 | 4      | 3          |      | ns   |

| t <sub>20</sub>  | RESET, FLUSH, A20M, NMI, INTR, IGNNE<br>Setup Time                                       |                 | 3, 4   | 5          |      | ns   |

| t <sub>21</sub>  | RESET, FLUSH, A20M, NMI, INTR, IGNNE<br>Hold Time                                        |                 | 3, 4   | 3          |      | ns   |

| t <sub>22</sub>  | D31-D0, DP3-DP0, A31-A4 Read Setup Time                                                  |                 | 4, 5   | 5          |      | ns   |

| t <sub>23</sub>  | D31-D0, DP3-DP0, A31-A4 Read Hold Time                                                   |                 | 4, 5   | 3          |      | ns   |

#### Note

<sup>1.</sup> Not 100% tested. Guaranteed by design characterization.

Operating Frequency/Bus Frequency: 100/33 MHz; T<sub>CASE</sub>=0°C to +85°C; C<sub>L</sub> =50 pF unless otherwise specified.

| Symbol           |                                                                                          |                 |        | Prelin  | Unit   |     |

|------------------|------------------------------------------------------------------------------------------|-----------------|--------|---------|--------|-----|

|                  | Parameter Description                                                                    | Notes           | Figure | Min Max |        |     |

|                  | Operating Frequency                                                                      |                 |        | 8       | 33     | MHz |

| t <sub>1</sub>   | CLK Period                                                                               |                 | 2      | 30      | 125.5  | ns  |

| t <sub>1a</sub>  | CLK Period Stability                                                                     | Adjacent Clocks |        |         | 0.1%   | Δ   |

| t <sub>2</sub>   | CLK High Time                                                                            | @ 2.0 V         | 2      | 11      |        | ns  |

| t <sub>3</sub>   | CLK Low Time                                                                             | @ 0.8 V         | 2      | 11      |        | ns  |

| t <sub>4</sub>   | CLK Fall Time                                                                            |                 | 2      |         | 3      | ns  |

| t <sub>5</sub>   | CLK Rise Time                                                                            |                 | 2      |         | 3      | ns  |

| t <sub>6</sub>   | A31-A2, PWT, PCD, M/IO, BE3-BE0, D/C,<br>W/R, ADS, LOCK, FERR, BREQ, HLDA<br>Valid Delay |                 | 7      | 3       | 14     | ns  |

| t <sub>7</sub>   | A31-A2, PWT, PCD, M/IO, BE3-BE0, D/C, W/R, ADS, LOCK, FERR, BREQ, HLDA Float Delay       | (Note 1)        | 8      |         | 20     | ns  |

| t <sub>8</sub>   | PCHK Valid Delay                                                                         |                 | 6      | 3       | 14     | ns  |

| t <sub>8a</sub>  | BLAST, PLOCK Valid Delay                                                                 |                 | 7      | 3       | 14     | ns  |

| t <sub>9</sub>   | BLAST, PLOCK Float Delay                                                                 | (Note 1)        | 8      |         | 20     | ns  |

| t <sub>10</sub>  | D31-D0, DP3-DP0 Write Data Valid Delay                                                   |                 | 7      | 3       | 14     | ns  |

| t <sub>11</sub>  | D31-D0, DP3-DP0 Write Data Float Delay                                                   | (Note 1)        | 8      |         | 20     | ns  |

| t <sub>12</sub>  | EADS Setup Time                                                                          |                 | 4      | 5       |        | ns  |

| t <sub>13</sub>  | EADS Hold Time                                                                           |                 | 4      | 3       |        | ns  |

| t <sub>14</sub>  | KEN, BS16, BS8 Setup Time                                                                |                 | 4      | 5       |        | ns  |

| t <sub>15</sub>  | KEN, BS16, BS8 Hold Time                                                                 |                 | 4      | 3       | į<br>Į | ns  |

| t <sub>16</sub>  | RDY, BRDY Setup Time                                                                     |                 | 5      | 5       |        | ns  |

| t <sub>17</sub>  | RDY, BRDY Hold Time                                                                      |                 | 5      | 3       |        | ns  |

| t <sub>18</sub>  | HOLD, AHOLD Setup Time                                                                   |                 | 4      | 6       |        | ns  |

| t <sub>18a</sub> | BOFF Setup Time                                                                          |                 | 4      | 7       |        | ns  |

| t <sub>19</sub>  | HOLD, AHOLD, BOFF Hold Time                                                              |                 | 4      | 3       |        | ns  |

| t <sub>20</sub>  | RESET, FLUSH, A20M, NMI, INTR, IGNNE<br>Setup Time                                       |                 | 3, 4   | 5       |        | ns  |

| t <sub>21</sub>  | RESET, FLUSH, A20M, NMI, INTR, IGNNE<br>Hold Time                                        |                 | 3, 4   | 3       |        | ns  |

| t <sub>22</sub>  | D31-D0, DP3-DP0, A31-A4 Read Setup<br>Time                                               |                 | 4, 5   | 5       |        | ns  |

| t <sub>23</sub>  | D31-D0, DP3-DP0, A31-A4 Read Hold<br>Time                                                |                 | 4, 5   | 3       |        | ns  |

### Note:

1. Not 100% tested. Guaranteed by design characterization.

# Am486DX4 CPU AC Characteristics for Boundary Scan Test Signals at 25 MHz

$V_{CC}$  = 3.3 V ± 0.3 V;  $T_{CASE}$  = 0°C to +85°C;  $C_L$  = 50 pF. All inputs and outputs are TTL Level.

| Symbol          | Parameter                          | Min | Max | Unit | Figure | Notes    |

|-----------------|------------------------------------|-----|-----|------|--------|----------|

| t <sub>24</sub> | TCK Frequency                      |     | 25  | MHz  |        | 1X Clock |

| t <sub>25</sub> | TCK Period                         | 40  |     | ns   | 9      | Note 2   |

| t <sub>26</sub> | TCK High Time                      | 10  |     | ns   |        | at 2.0 V |

| t <sub>27</sub> | TCK Low Time                       | 10  |     | ns   |        | at 0.8 V |

| t <sub>28</sub> | TCK Rise Time                      |     | 4   | ns   |        | Note 1   |

| t <sub>29</sub> | TCK Fall Time                      | i   | 4   | ns   |        | Note 1   |

| t <sub>30</sub> | TDI, TMS Setup Time                | 8   |     | ns   | 9      | Note 3   |

| t <sub>31</sub> | TDI, TMS Hold Time                 | 7   |     | ns   | 9      | Note 3   |

| t <sub>32</sub> | TDO Valid Delay                    | 3   | 25  | ns   | 9      | Note 3   |

| t <sub>33</sub> | TDO Float Delay                    |     | 30  | ns   | 9      | Note 3   |

| t <sub>34</sub> | All Outputs (Non-Test) Valid Delay | 3   | 25  | ns   | 9      | Note 3   |

| t <sub>35</sub> | All Outputs (Non-Test) Float Delay |     | 36  | ns   | 9      | Note 3   |

| t <sub>36</sub> | All Inputs (Non-Test) Setup Time   | 8   |     | ns   | 9      | Note 3   |

| t <sub>37</sub> | All Inputs (Non-Test) Hold Time    | 7   |     | ns   | 9      | Note 3   |

#### Notes:

<sup>1.</sup> Rise/Fall times are measured between 0.8 V and 2.0 V. Rise/Fall times can be relaxed by 1 ns per 10-ns increase in TCK period.

<sup>2.</sup> TCK period ≥ CLK period.

<sup>3.</sup> Parameter measured from TCK.

Figure 1. Change State Diagram

17852B-095

Figure 2. CLK Waveforms

Figure 3. Reset Setup and Hold Timing

Figure 4. Input Setup and Hold Timing

19160c.004

Figure 5. RDY and BRDY Input Setup and Hold Timing

Figure 6. PCHK Valid Delay Timing

19160c.007

19160c.005

19160c.006

Figure 7. Output Valid Delay Timing

17852A-103

Figure 8. Maximum Float Delay Timing

Figure 9. Test Signal Timing Diagram

# **Package Thermal Specifications**

The Am486DX4 microprocessor is specified for operation when  $T_{CASE}$  (the case temperature) is within the range of 0°C to +85°C.  $T_{CASE}$  can be measured in any environment to determine whether the Am486DX4 microprocessor is within specified operating range. The case temperature should be measured at the center of the top surface opposite the pins.

The ambient temperature ( $T_A$ ) is guaranteed as long as  $T_{CASE}$  is not violated. The ambient temperature can be calculated from  $\theta_{JC}$  and  $\theta_{JA}$  and from the following equations:

$$T_J = T_{CASE} + P \cdot \theta_{JC}$$

$$T_A = T_A - P \cdot \theta_{AA}$$

$$T_{CASF} = T_A + P \cdot [\theta_{JA} - \theta_{JC}]$$

where:

T<sub>J</sub>, T<sub>A</sub>, T<sub>CASE</sub>= Junction, Ambient, and Case Temperature

$\theta_{JC}$ ,  $\theta_{JA}$  = Junction-to-Case and Junction-to-Ambient Thermal Resistance, respectively.

P = Maximum Power Consumption

The values for  $\theta_{JA}$  and  $\theta_{JC}$  are given in Table 9 for the 1.75 sq. in., 168-pin, ceramic PGA.

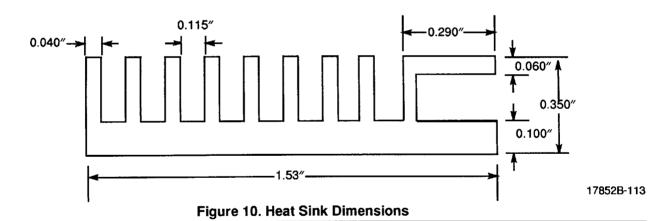

Table 10 shows the  $T_A$  allowable (without exceeding  $T_{CASE}$ ) at various airflows and operating frequencies (Clock). Note that  $T_A$  is greatly improved by attaching fins or a heat sink to the package. Heat sink dimensions are shown in Figure 10. P (the maximum power consumption) is calculated by using the maximum  $I_{CC}$  at 3.3 V as tabulated in the *DC Characteristics*.

Table 9. Thermal Resistance (°C/W) $\theta_{JC}$  and  $\theta_{JA}$  for the 168-Pin, Ceramic PGA Package

|                    | Α   |       | ;)         |            |            |            |             |

|--------------------|-----|-------|------------|------------|------------|------------|-------------|

|                    | θJC | 0 (0) | 200 (1.01) | 400 (2.03) | 600 (3.04) | 800 (4.06) | 1000 (5.07) |

| No Heat Sink       | 1.5 | 16.5  | 14.0       | 12.0       | 10.5       | 9.5        | 9.0         |

| Heat Sink*         | 2.0 | 12.0  | 7.0        | 5.0        | 4.0        | 3.5        | 3.25        |

| Heat Sink* and fan | 2.0 | 5.0   | 4.6        | 4.2        | 3.8        | 3.5        | 3.25        |

<sup>\*0.350&</sup>quot; high unidirectional heat sink (Al alloy 6063-T5, 40 mil fin width, 155 mil center-to-center fin spacing).

Table 10. Maximum T<sub>A</sub> at Various Airflows in °C

|                                   | Clock   | Airflow-ft/min. (m/sec) |            |            |            |            |             |  |

|-----------------------------------|---------|-------------------------|------------|------------|------------|------------|-------------|--|

|                                   |         | 0 (0)                   | 200 (1.01) | 400 (2.03) | 600 (3.04) | 800 (4.06) | 1000 (5.07) |  |

| T <sub>A</sub> —No Heat Sink      | 100 MHz | 31.0                    | 41.8       | 49.0       | 54.4       | 58.0       | 59.8        |  |

| T <sub>A</sub> —Heat Sink         | 100 MHz | 49.0                    | 67.0       | 74.2       | 77.8       | 79.6       | 80.5        |  |

|                                   | 120 MHz | 41.8                    | 63.4       | 72.0       | 76.4       | 78.5       | 79.6        |  |

| T Heat Cink and for               | 100 MHz | 74.2                    | 75.6       | 77.1       | 78.5       | 79.6       | 80.5        |  |

| T <sub>A</sub> —Heat Sink and fan | 120 MHz | 72.0                    | 73.8       | 75.5       | 77.2       | 78.5       | 79.6        |  |

#### PHYSICAL DIMENSIONS

For reference only. All dimensions are measured in inches. BSC is an ANSI standard for Basic Space Centering.

#### **CGM 168**

16734C 5/11/93 MH

AMD, Am386, and Am486 are registered trademarks of Advanced Micro Devices, Inc. FusionPC is a service mark of Advanced Micro Devices, Inc. Microsoft and Windows are registered trademarks of Microsoft Corp.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.