# MIC5002CN/5005CN/5007CN

4-Digit Counter/Display Decoder

7-67-31-51

## General Description

The MIC5002/5/7 is an ion-implanted, P-channel MOS, fourdecade synchronous counter with latches, multiplexing circuits, and a read-only memory programmed for sevensegment outputs and BCD outputs. In addition, many on-chip control circuits provide flexibility of use with a minimum of external components.

The MIC5002/5/7 provides a means of counting up to 9999, transferring the count into latches without interrupting the counting operation, and supplying the latched information to the outputs one decade at a time. Scanning is controlled by the SCAN input which increments a one-of-four counter on its negative edge, thereby scanning the latches from MSD (Most Significant Digit) to LSD (Least Significant Digit).

Low-threshold voltages for input DTL/TTL compatibility are achieved through an ion-implementation process. Enhancement mode devices, as well as depletion-mode devices, are fabricated on the chip, allowing it to operate from a single +5V power supply. Depletion-mode technology also allows the entire circuit to operate on less than 25mW of power.

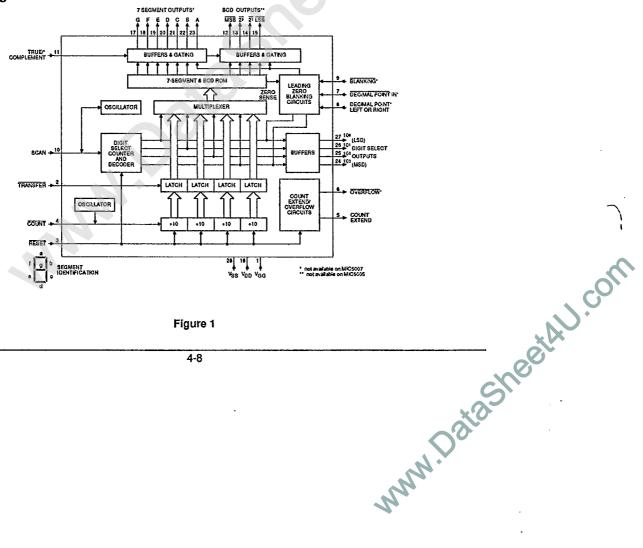

The block diagram, Figure 1, shows all options available on the MIC5002 MOS/LSI. Other members of this family which

#### **Features**

- · Single-supply operation or double-supply for higher output drive

- Multiplexed seven-segment and/or BCD outputs

- TTL-compatible inputs

- Four decades of synchronous counting

- Minimum external component count

- Low power consumption

## **Ordering Information**

| Part Number | Temperature Range | Package            |  |  |

|-------------|-------------------|--------------------|--|--|

| MIC5002CN   | 0°C to +70°C      | 28-Pin Plastic DIP |  |  |

| MIC5005CN   | 0°C to +70°C      | 24-Pin Plastic DIP |  |  |

| MIC5007CN   | 0°C to +70°C      | 16-Pin Plastic DIP |  |  |

# **Functional Diagram**

Figure 1

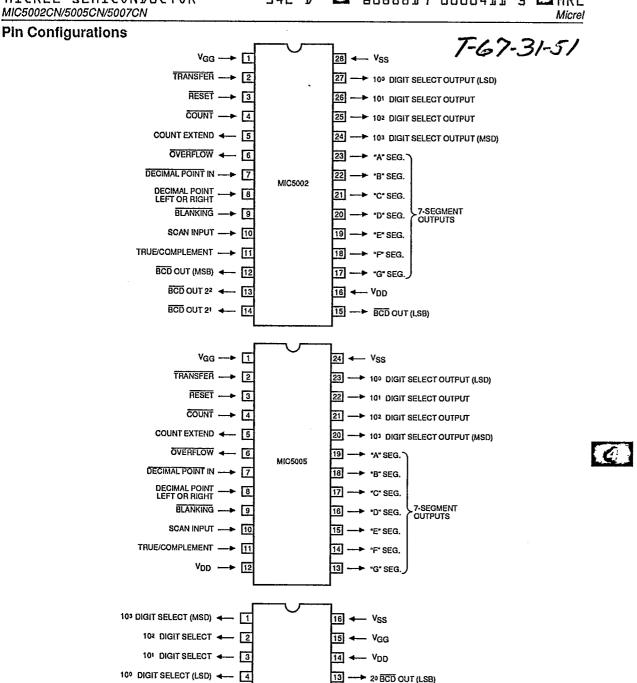

MIC5007

---> 21 BCD OUT

10 → 23 BCD OUT (MSB)

**←** SCAN INPUT

11 --> 22 BCD OUT

TRANSFER -

RESET -

COUNT -

COUNT EXTEND 4-

are different versions of this same chip are the MIC5005 and MIC5007. The MIC5005 is supplied in a 24-pin package and does not include the BCD outputs. The MIC5007 is supplied in a 16-pin package. (See Figure 2 for these members of the display counter/decoder family.)

# Functional Description (MIC5002)

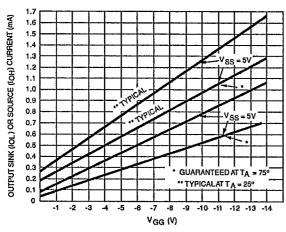

#### V<sub>GG</sub>, Pin 1

VGG is the output gate drive voltage supply. It must be tied to a supply which is no greater than VDD and no less than VDD - 13.2V. Higher output drive capability is realized when VGG is maintained at the recommended level of VDD - 12V. (See Figure 3 for typical output characteristics.)

### TRANSFER, Pin 2

While TRANSFER is at logic 0, data in the decade counters is continuously transferred to the latches. This input may be left at 0 for a continuous transfer and display mode or may be driven high to subsequently cause the latches to store the current counter contents.

Storage occurs internally when TRANSFER is taken to a 1 and the next negative edge of COUNT INPUT occurs. This allows asynchronous COUNT and TRANSFER operation since the transfer is terminated internally prior to incrementing the counters. This means that a COUNT negative edge must follow a TRANSFER command before a reset is applied to assure transfer of data. An external reset command must be delayed at least one COUNT negative edge following a transfer. External transfer should terminate at least 1 µS prior to this COUNT negative edge and RESET should occur no sooner than 1 µS following that edge.

# **Output Drive Characteristics**

(IOL @  $V_0 = V_{SS}-0.75V$ ;  $T_A = 25^{\circ}C$  and  $T_A = 75^{\circ}C$  $IOH @ V_0 = V_{DD} + 0.75V; V_{DD} = 0V)$

Figure 3

#### T-67-31-51 RESET, Pin 3

The decade counters are reset to 0000 when RESET is at logic 0. The RESET input at logic 0 also forces the scan counter to the MSD output and resets the OVERFLOW latch output to a logic 1. It maintains this condition as long as a logic 0 is present at RESET and overrides all other associated inputs. As indicated previously, the decade counter should not be reset until a transfer has been terminated.

Since the RESET input resets the scan counter to the MSD, the scan rate must be much faster than the reset rate to allow the lesser significant digits to be enabled. Therefore, FSCAN should be much greater than four times FRESET.

Ideally, the reset pulse should also be made narrow to prevent its duration from causing the MSD to be on much longer than the other digits and thus appear to be brighter.

## COUNT, Pin 4

The decade counters are synchronously incremented on the negative edge of the COUNT input. The internal oscillator on this input may be overridden by an external signal source or may be allowed to oscillate at a frequency set by a single capacitor tied to this input from the VSS or VDD supply. In systems with considerable noise, better oscillator stability exists when the capacitor is tied to VSS. (See Table 1.)

#### **COUNT EXTEND, Pin 5**

COUNT EXTEND is a feature provided to enable MIC5002s to be cascaded. Whenever the counter state attains 9999 count, the COUNT EXTEND output goes high. This output remains logical 1 only until the next negative transition of COUNT occurs or a RESET signal is applied.

# Typical Count Oscillator Frequencies vs. Capacitance Between VSS and COUNT

| Capacitance | Typical Frequency |  |  |  |  |

|-------------|-------------------|--|--|--|--|

| 470 pF      | 135 kHz           |  |  |  |  |

| 1000 pF     | 90 kHz            |  |  |  |  |

| 4700 pF     | 33 kHz            |  |  |  |  |

| 20000 pF    | 9.5 kHz           |  |  |  |  |

$(V_{SS} = 5.75V; V_{DD} = 0V; V_{GG} = -12V; T_A = 25^{\circ}C)$

Table 1

# Typical Scan Oscillator Frequencies vs. Capacitance Between VSS and SCAN Input

| Capacitance | Typical Frequency |  |  |  |  |

|-------------|-------------------|--|--|--|--|

| 470 pF      | 17 kHz            |  |  |  |  |

| 1000 pF     | 11.2 kHz          |  |  |  |  |

| 4700 pF     | 4.0 kHz           |  |  |  |  |

| 20000 pF    | 1.33 kHz          |  |  |  |  |

$(V_{SS} = 5.75V; V_{DD} = 0V; V_{GG} = -12V; T_A = 25^{\circ}C)$

Table 2

# OVERFLOW, Pin 6 (N/A on MIC5007)

OVERFLOW occurs on the 10,000th count input following a reset. It is normally high and, when activated, goes low to indicate that the decade counters have gone from 9999 to 0000 without encountering a reset. Once activated, the OVERFLOW latch will remain low until RESET is pulled low.

## DECIMAL POINT IN, Pin 7 (N/A on MIC5007)

With DECIMAL POINT IN held high, the device employs leading zero blanking. This causes any leading zeros in the display latches to be blanked when their DIGIT SELECT goes high. At the start of each MSD to LSD scan, blanking of leading zeros occurs until the first non-zero number occurs in the display or DECIMAL POINT IN is clocked to a 0. Any number following will be displayed. Leading zero blanking does not affect the BCD outputs or the LSD in the display which is displayed even if zero. The LSD output resets the blanking circuitry to begin blanking zeros in the next scan

Leading zero blanking may be inhibited by wiring DECIMAL POINT IN to ground. The MIC5007 does not have a pin for DECIMAL POINT IN and therefore does not have leading zero blanking.

In the DECIMAL POINT RIGHT mode, even though the DECIMAL POINT IN is clocked, unblanking is delayed until the following digit is enabled.

## DECIMAL POINT LEFT OR RIGHT, Pin 8 (N/A on MIC5007)

Bringing this control to logic 1 allows the use of displays with the decimal point physically located on the left side of the numeral. Logic 0 on this input allows for a right-handed decimal point.

### **BLANKING, Pin 9**

The BLANKING input at logic 0 forces the 7-segment outputs to the off-state and BCD to the equivalent of the number zero. This condition is maintained on a dc basis as long as the BLANKING input is zero. The DIGIT SELECT outputs continue to operate at the scan rate as described.

#### SCAN INPUT, Pin 10

The DIGIT SELECT COUNTER is incremented by a negative edge on the SCAN INPUT. During the time the SCAN INPUT is at 0, the SEGMENT and DIGIT SELECT outputs are forced off and the complement BCD outputs are forced to logic 1, The off level of the 7-segment and BCD outputs is determined by the state of the TRUE/COMPLEMENT input. This remains until the SCAN INPUT returns to logic 1.

The DIGIT SELECT COUNTER is a one-of-four counter, scanning from MSD to LSD, enabling one guad latch output at a time, and presenting a logic 1 to the corresponding DIGIT SELECT output.

The internal oscillator on this input may be overridden by an external signal source or may be allowed to oscillate at a frequency set by a single capacitor tied to this input from the Vss or Vpp supply. In systems with considerable noise, better oscillator stability exists when the capacitor is tied to Vss. (See Table 2.)

#### TRUE/COMPLEMENT, Pin 11 (N/A on MIC5007)

When this control is driven to 0, inversion of both the BCD and 7-segment outputs occurs. Depending upon the display used, combinations of the BLANKING input and TRUE/ COMPLEMENT control can be chosen to give a lamp test.

# BCD OUT, Pins 12 through 15 (N/A on MIC5005)

The BCD outputs are push-pull and are designed to drive directly to the base of common emitter transistors. Output characteristics are shown in Figure 3.

V<sub>DD</sub>, Pin 16

T-67-31-51

VDD is the negative supply and is nominally ground.

#### **SEGMENT OUTPUTS, Pins 17 through 23** (N/A on MIC5007)

The SEGMENT OUTPUT buffers are identical to the BCD output buffers.

# DIGIT SELECT OUTPUTS, Pins 24 through 27

The DIGIT SELECT OUTPUTS are push-pull and go high during their appropriate times to accomplish the multiplexing of the digits.

## Vss, Pin 28

Vss is the positive supply voltage and is nominally maintained at 5Vdc with respect to VDD.

MICREL SEMICONDUCTOR MIC5002CN/5005CN/5007CN

34E D

■ 6088819 0000414 0 **■**MRL

# Absolute Maximum Ratings\* (See Notes 1 and 2)

T-67-31-5

Absolute Maximum Vss V<sub>GG</sub> Supply Range

$0V \ge V_{GG} \ge -13.2V$ 0°C to +70°C

Operating Temperature Range Storage Temperature Range

-65°C to +150°C

\*Stresses above those listed under \*Absolute Maximum Ratings\* may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Electrical Operating Characteristics**

| Symbol          | Parameter       | Conditions                        | Min.  | Тур. | Max.            | Units | Notes |

|-----------------|-----------------|-----------------------------------|-------|------|-----------------|-------|-------|

| V <sub>SS</sub> | Supply Voltage  | V <sub>SS</sub> - V <sub>DD</sub> | 4.5   | 5.0  | 7.5             | ٧     | 1,2   |

| V <sub>GG</sub> | Supply Voltage  | V <sub>GG</sub> - V <sub>DD</sub> | -13.2 | -12  | V <sub>DD</sub> | ٧     | 1,2   |

| Fc              | Count Frequency |                                   | dc    |      | 250             | kHz   |       |

#### **DC** Characteristics

(VSS =  $+5V \pm 5\%$ ; VGG = VDD = 0V; 0°C  $\leq$  TA  $\leq$  70°C unless otherwise noted)

| Symbol          | Parameter                                                                                      | Min.                 | Тур.            | Max.                     | Units                | Notes                                                              |

|-----------------|------------------------------------------------------------------------------------------------|----------------------|-----------------|--------------------------|----------------------|--------------------------------------------------------------------|

| V <sub>IL</sub> | Input Voltage, Logic 0 (Low)                                                                   |                      | V <sub>DD</sub> | V <sub>DD</sub> +0.8     | V                    |                                                                    |

| V <sub>iH</sub> | Input Voltage, Logic 1 (High)                                                                  | V <sub>SS</sub> - 1  | Vss             | V <sub>SS</sub> +0.3     | ٧                    | 3                                                                  |

| Iss             | Supply Current, V <sub>SS</sub>                                                                |                      | 2.5             | 5.0                      | mA                   | 4, Inputs open                                                     |

| l <sub>GG</sub> | Supply Current, V <sub>GG</sub>                                                                |                      | 0.2             | 0.5                      | mA                   | V <sub>GG</sub> = -12V                                             |

| CIN             | Input Capacitance                                                                              |                      | 3               | 10                       | ρF                   | T <sub>A</sub> = 25°C, f = 1MHz, V <sub>IN</sub> = V <sub>SS</sub> |

| l <sub>IL</sub> | Input Current, Logic 0, Count Input<br>Scan Input<br>Decimal Point Input<br>Other Logic Inputs |                      |                 | 1.6<br>1.6<br>1.0<br>1.0 | mA<br>mA<br>μA<br>mA | 5<br>5                                                             |

| loL             | Output Current, Logic 0                                                                        | 0.5                  |                 |                          | mA                   | 6, V <sub>GG</sub> = -12V                                          |

| Юн              | Output Current, Logic 1                                                                        | 0.5                  |                 |                          | mA                   | 6, V <sub>GG</sub> = -12V                                          |

| V <sub>OL</sub> | Output Voltage, Logic 0                                                                        |                      |                 | V <sub>DD</sub> +0.2     | ٧                    | 4                                                                  |

| V <sub>OH</sub> | Output Voltage, Logic 1                                                                        | V <sub>DD</sub> -0.2 |                 |                          | ٧                    | 4                                                                  |

1. V<sub>DD</sub> = 0V. 2. V<sub>SS</sub> - V<sub>GG</sub> no more than 20.7V.

υ. πποτιται μυτι-υρ resistors (approx. 10K) are provided at all inputs other than Count Input, Scan Input and Decimal Point Input.

4. V<sub>GG</sub> = -12V ± 10%. Outputs open.

5. Measurement made at V<sub>1</sub> = V<sub>DD</sub> + 0.4V. This condition is sufficient to represent a logic 0 and hold off or override the internal oscillators. Maximum current at V<sub>1</sub> = +0.4V is 1.6mA. 400μA source current is sufficient to represent a logic 1 and hold off or override the internal oscillators.

6. I<sub>OL</sub> measured at V<sub>0</sub> = V<sub>SS</sub> - 0.75V. (Direct driving base ppp emitter to V<sub>SS</sub>.) I<sub>OH</sub> measured at V<sub>0</sub> = V<sub>DD</sub> + 0.75V. (Direct driving base npn emitter to V<sub>DD</sub>.)

# MICREL SEMICONDUCTOR MIC5002CN/5005CN/5007CN

34E D № 6088819 0000415 2 MRL

**AC** Characteristics

(Vss = +5V ±%; VGG = VDD = 0V; 0°C  $\leq$  TA  $\leq$  70°C unless otherwise noted)

T-67-31-51

| Symbol           | Parameter                                                               |                                                   | Min.                      | Тур. | Max.     | Units                                | Notes  |

|------------------|-------------------------------------------------------------------------|---------------------------------------------------|---------------------------|------|----------|--------------------------------------|--------|

| fcı              | Count Input Frequency                                                   |                                                   | dc                        |      | 250      | kHz                                  |        |

| f <sub>SI</sub>  | Scan Input Frequency                                                    |                                                   | đc                        |      | 50       | kHz                                  |        |

| t <sub>RD</sub>  | Reset to Any Output Delay                                               |                                                   |                           |      | 15       | μS                                   |        |

| tpW              | Logic Q Pulse Width,                                                    | Reset Input Count Input Scan Input Transfer Input | 1.0<br>1.0<br>10.0<br>2.5 |      |          | р<br>р<br>р<br>р<br>р<br>р<br>р<br>р |        |

| t <sub>PH</sub>  | Logic 1 Time                                                            | Count Input<br>Scan Input                         | 3.0<br>10.0               |      |          | μS<br>μS                             |        |

| tsp              | Scan to Output Disable Time<br>Digit Select Outputs<br>All Data Outputs |                                                   |                           |      | 15<br>15 | μS<br>μS                             | 7 7    |

| t <sub>SE</sub>  | Scan to Output Enable Time<br>Digit Select Outputs<br>All Data Outputs  |                                                   |                           |      | 15<br>15 | μS<br>μS                             | 8<br>8 |

| t <sub>CE</sub>  | Count Input to Count Extend Delay to 1 or 0                             |                                                   |                           |      | 15       | μS                                   | 9      |

| t <sub>OF</sub>  | Count Input to Overflow Delay (On)                                      |                                                   |                           |      | 15       | μS                                   | 9      |

| t <sub>ROF</sub> | Reset Input to Overflow Delay (Off)                                     |                                                   |                           |      | 5        | μS                                   |        |

## NOTES:

1.  $V_{DD} = 0V$ .

2. Vss - Vgg no more than 20.7V.

V<sub>SS</sub> - V<sub>GQ</sub> no more than 20.7V.

Internal pull-up resistors (approx. 10k) are provided at all inputs other than Count Input, Scan Input and Decimal Point Input.

V<sub>GG</sub> = -12V ± 10%. Outputs open.

Measurement made at V<sub>I</sub> = V<sub>DD</sub> + 0.4V. This condition is sufficient to represent a logic 0 and hold off or override the internal oscillators. Maximum current at V<sub>I</sub> = +0.4V is 1.6mA. 400µA source current is sufficient to represent a logic 1 and hold off or override the internal oscillators.

I<sub>OL</sub> measured at V<sub>0</sub> = V<sub>SS</sub> - 0.75V. (Direct driving base pnp emitter to V<sub>SS</sub>.) I<sub>OH</sub> measured at V<sub>0</sub> = V<sub>DD</sub> + 0.75V. (Direct driving base npn emitter to V<sub>DD</sub>.)

Delay measured from the negative edge of the SCAN input.

Delay measured from the negative edge of the COUNT input.

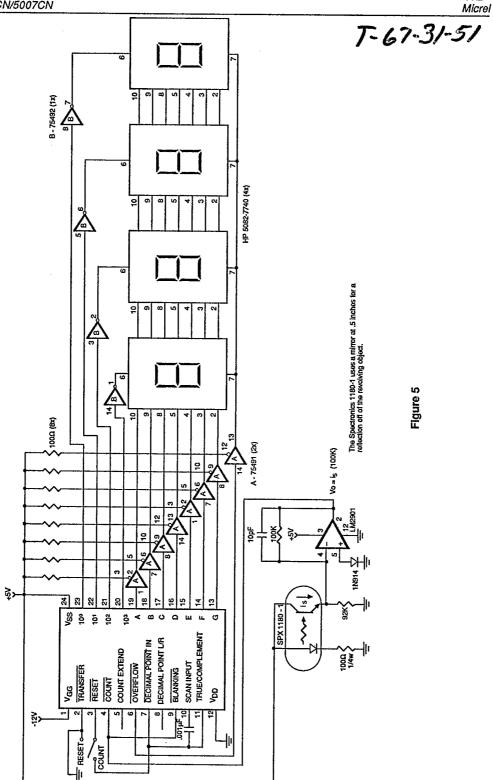

Typical Application: Revolution Counter