# Universal Serial Bus On-The-Go transceiver

**Product data**

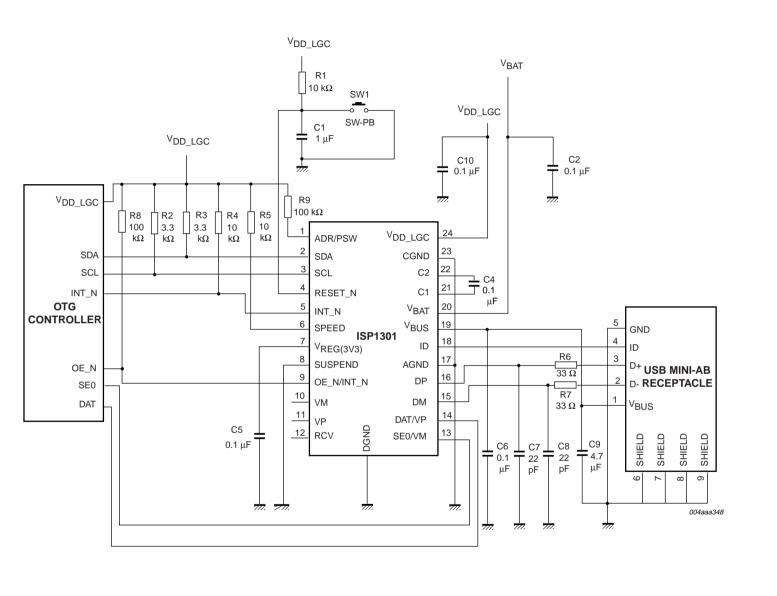

The ISP1301 is a Universal Serial Bus (USB) On-The-Go (OTG) transceiver device that is fully compliant with *Universal Serial Bus Specification Rev. 2.0* and *On-The-Go Supplement to the USB Specification Rev. 1.0a.* The ISP1301 can transmit and receive serial data at both full-speed (12 Mbit/s) and low-speed (1.5 Mbit/s) data rates.

It is ideal for use in portable electronics devices, such as mobile phones, digital still cameras, digital video cameras, Personal Digital Assistants (PDAs) and digital audio players. It allows USB Application Specific Integrated Circuits (ASICs), Programmable Logic Devices (PLDs) and any system chip set (with the USB host or device function built-in but without the USB physical layer) to interface to the physical layer of the USB.

The ISP1301 can interface to devices with digital I/O voltages in the range of 1.65 V to 3.6 V.

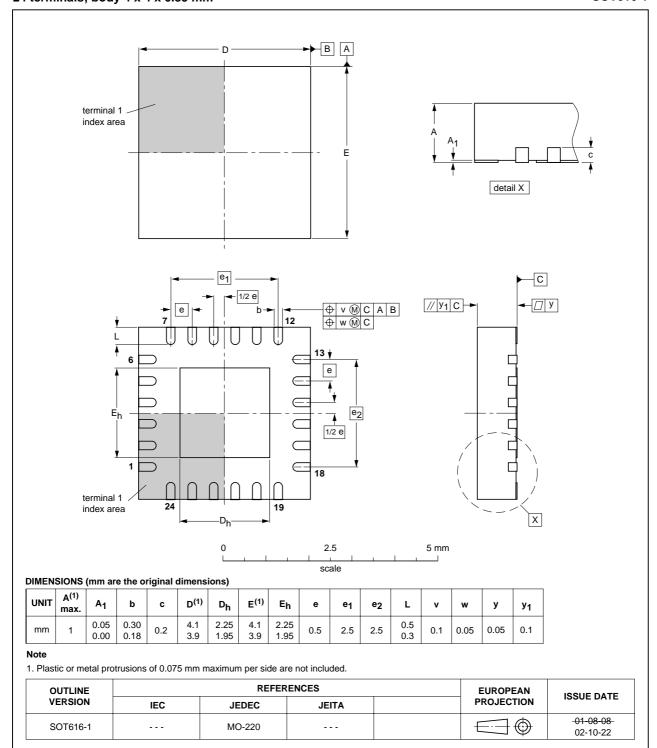

The ISP1301 is available in HVQFN24 package.

## 2. Features

- Fully complies with:

- Universal Serial Bus Specification Rev. 2.0

- On-The-Go Supplement to the USB 2.0 Specification Rev. 1.0a

- ◆ On-The-Go Transceiver Specification (CEA-2011) Rev. 1.0

- Can transmit and receive serial data at both full-speed (12 Mbit/s) and low-speed (1.5 Mbit/s) data rates

- Ideal for system ASICs or chip sets with built-in USB OTG dual-role core

- Supports mini USB analog car kit interface

- Supports various serial data interface protocols; transparent general-purpose buffer mode allows you to control the direction of data transfer

- Supports data line and V<sub>BUS</sub> pulsing session request

- Contains Host Negotiation Protocol (HNP) command and status registers

- Supports serial I<sup>2</sup>C-bus<sup>™</sup> interface for OTG status and command controls

- 2.7 V to 4.5 V power supply input range for the ISP1301

- Built-in charge pump regulator outputs 5 V at current greater than 8 mA

- Supports external charge pump

- Supports wide range interfacing I/O voltage (V<sub>DD\_LGC</sub> = 1.65 V to 3.6 V) for digital control logics

**USB OTG transceiver**

- 8 kV built-in electrostatic discharge (ESD) protection on the DP, DM, V<sub>BUS</sub> and ID lines

- Full industrial grade operation from -40 °C to +85 °C

- Available in a small HVQFN24 (4 × 4 mm²) halogen-free and lead-free package.

# 3. Applications

- Mobile phone

- Digital camera

- Personal digital assistant

- Digital video recorder.

# 4. Abbreviations

**ASIC** — Application-Specific Integrated Circuit

ATX — Analog USB transceiver

**HNP** — Host Negotiation Protocol

**ESD** — ElectroStatic Discharge

I2C-bus — Inter IC-bus

IC — Integrated Circuit

OTG - On-The-Go

PDA — Personal Digital Assistant

SE0 — Single-Ended zero

**SOF** — Start-of-Frame

SRP — Session Request Protocol

**USB** — Universal Serial Bus

**USB-IF** — USB Implementers Forum.

# 5. Ordering information

**Table 1: Ordering information**

| Туре      | Package | Package                                                                                                    |          |  |  |  |  |  |  |  |

|-----------|---------|------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|

| number    | Name    | Description                                                                                                | Version  |  |  |  |  |  |  |  |

| ISP1301BS | HVQFN24 | plastic thermal enhanced very thin quad flat package; no leads; 24 terminals; body $4\times4\times0.85$ mm | SOT616-1 |  |  |  |  |  |  |  |

**USB OTG transceiver**

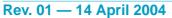

# 6. Block diagram

**USB OTG transceiver**

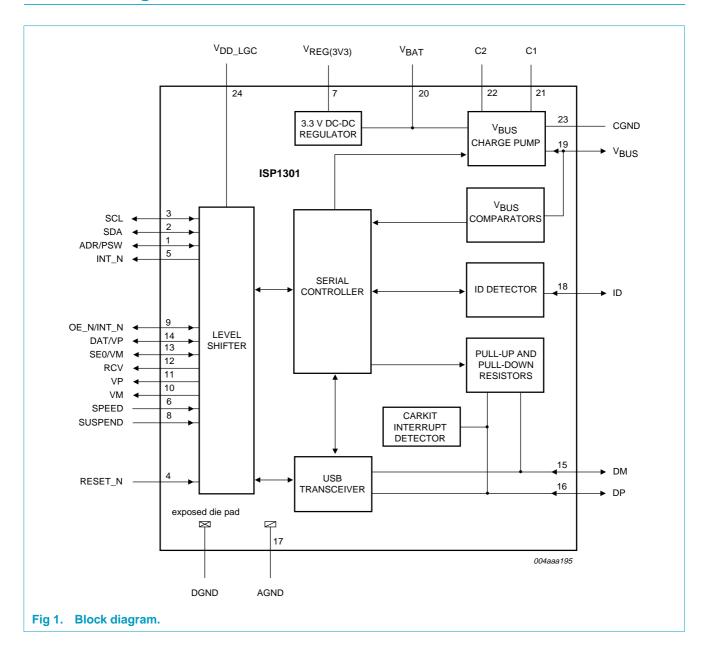

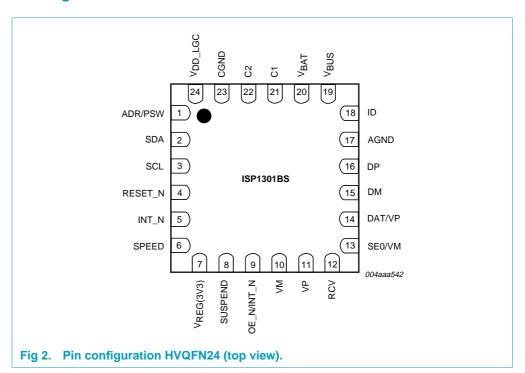

# 7. Pinning information

# 7.1 Pinning

# **USB OTG transceiver**

# 7.2 Pin description

Table 2: Pin description<sup>[1]</sup>

| Table 2:              | Pin descri | ption               |             |                                                                                                                                            |

|-----------------------|------------|---------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol <sup>[2]</sup> | Pin        | Type <sup>[3]</sup> | Reset value | Description                                                                                                                                |

| ADR/PSW               | 1          | I/O                 | high-Z      | <b>ADR input</b> — sets the least-significant I <sup>2</sup> C-bus address bit of the ISP1301; latched-on reset (including power-on reset) |

|                       |            |                     |             | <b>PSW output</b> — enables or disables the external charge pump after reset                                                               |

|                       |            |                     |             | bidirectional; push-pull input; three-state output                                                                                         |

| SDA                   | 2          | I/OD                | high-Z      | serial I <sup>2</sup> C-bus data input and output                                                                                          |

|                       |            |                     |             | bidirectional; push-pull input; open-drain output                                                                                          |

| SCL                   | 3          | I/OD                | high-Z      | serial I <sup>2</sup> C-bus clock input and output                                                                                         |

|                       |            |                     |             | bidirectional; push-pull input; open-drain output                                                                                          |

| RESET_N               | 4          | I                   | -           | asynchronous reset; active LOW                                                                                                             |

|                       |            |                     |             | push-pull input                                                                                                                            |

| INT_N                 | 5          | OD                  | high-Z      | interrupt output; active LOW                                                                                                               |

|                       |            |                     |             | open-drain output                                                                                                                          |

| SPEED                 | 6          | 1                   | -           | speed selection input for the ATX; effective when bit SPD_SUSP_CTRL = 0:                                                                   |

|                       |            |                     |             | LOW: low-speed                                                                                                                             |

|                       |            |                     |             | HIGH: full-speed.                                                                                                                          |

|                       |            |                     |             | push-pull input                                                                                                                            |

| V <sub>REG(3V3)</sub> | 7          | Р                   | -           | output of the internal voltage regulator; an external decoupling capacitor of 0.1 $\mu\text{F}$ is required                                |

| SUSPEND               | 8          | I                   | -           | suspend selection input for ATX; effective when bit SPD_SUSP_CTRL = 0:                                                                     |

|                       |            |                     |             | <ul><li>LOW: normal operating</li></ul>                                                                                                    |

|                       |            |                     |             | HIGH: suspend.                                                                                                                             |

|                       |            |                     |             | push-pull input                                                                                                                            |

| OE_N/<br>INT_N        | 9          | I/O                 | high-Z      | <b>OE_N input</b> — enable driving DP and DM when in the USB mode                                                                          |

|                       |            |                     |             | INT_N output — interrupt (push pull) when suspended and bit OE_INT_EN = 1                                                                  |

|                       |            |                     |             | bidirectional; push-pull input; three-state output                                                                                         |

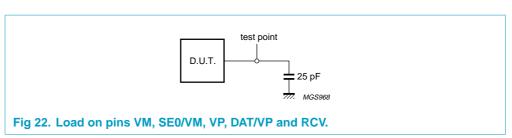

| VM                    | 10         | 0                   | -           | single-ended DM receiver output                                                                                                            |

|                       |            |                     |             | push-pull output                                                                                                                           |

| VP                    | 11         | 0                   | -           | single-ended DP receiver output                                                                                                            |

|                       |            |                     |             | push-pull output                                                                                                                           |

| RCV                   | 12         | 0                   | 0           | differential receiver output; reflects the differential value of DP and DM                                                                 |

|                       |            |                     |             | push-pull output                                                                                                                           |

#### **USB OTG transceiver**

Table 2: Pin description<sup>[1]</sup>...continued

| Table 2.              | riii uescii        | ption               | Jonanaea    |                                                                                                                                     |

|-----------------------|--------------------|---------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Symbol <sup>[2]</sup> | Pin                | Type <sup>[3]</sup> | Reset value | Description                                                                                                                         |

| SE0/VM                | 13                 | I/O                 | _[4]        | <b>SE0 (input and output)</b> — SE0 function in DAT_SE0 USB mode                                                                    |

|                       |                    |                     |             | VM (input and output) — VM function in VP_VM USB mode                                                                               |

|                       |                    |                     |             | bidirectional; push-pull input; three-state output                                                                                  |

| DAT/VP                | 14                 | I/O                 | _[4]        | <b>DAT (input and output)</b> — DAT function in DAT_SE0 USB mode                                                                    |

|                       |                    |                     |             | <b>VP (input and output)</b> — VP function in VP_VM USB mode                                                                        |

|                       |                    |                     |             | bidirectional; push-pull input; three-state output                                                                                  |

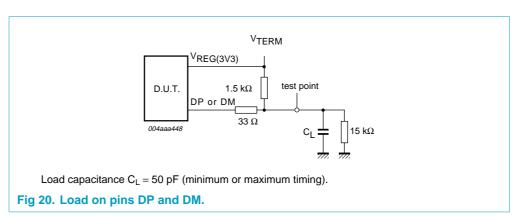

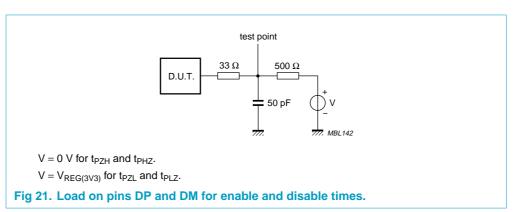

| DM                    | 15                 | AI/O                | -           | USB data minus pin (D-)                                                                                                             |

| DP                    | 16                 | AI/O                | -           | USB data plus pin (D+)                                                                                                              |

| AGND                  | 17                 | Р                   | -           | analog ground                                                                                                                       |

| ID                    | 18                 | AI/O                | -           | identification detector input and output;<br>connected to the ID pin of the USB mini<br>receptacle                                  |

| $V_{BUS}$             | 19                 | AI/O                | -           | $V_{BUS}$ line input and output of the USB interface; place an external decoupling capacitor of 0.1 $\mu\text{F}$ close to this pin |

| $V_{BAT}$             | 20                 | Р                   | -           | supply voltage (2.7 V to 4.5 V)                                                                                                     |

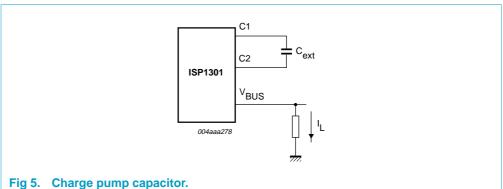

| C1                    | 21                 | AI/O                | -           | charge pump capacitor pin 1; typically use a 100 nF capacitor between pins C1 and C2                                                |

| C2                    | 22                 | AI/O                | -           | charge pump capacitor pin 2; typically use a 100 nF capacitor between pins C1 and C2                                                |

| CGND                  | 23                 | Р                   | -           | ground for the charge pump                                                                                                          |

| $V_{DD\_LGC}$         | 24                 | Р                   | -           | supply voltage for the interface logic signals (1.65 V to 3.6 V)                                                                    |

| DGND                  | exposed<br>die pad | Р                   | -           | digital ground                                                                                                                      |

<sup>[1]</sup> A detailed description of these pins can be found in Section 8.9.

<sup>[2]</sup> Symbol names ending with underscore N (for example, NAME\_N) indicate active LOW signals.

<sup>[3]</sup> I = input; O = output; I/O = digital input/output; OD = open-drain output; AI/O = analog input/output; P = power or ground pin.

<sup>[4]</sup> High-Z when pin OE\_N/INT\_N is LOW. Driven LOW when pin OE\_N/INT\_N is HIGH.

**USB OTG transceiver**

# 8. Functional description

#### 8.1 Serial controller

The serial controller includes the following functions:

- I<sup>2</sup>C-bus slave interface

- Interrupt generator

- Mode Control registers

- OTG registers

- Interrupt related registers

- Device identification registers.

The serial controller acts as an I<sup>2</sup>C-bus slave, and uses the SCL and SDA pins to communicate with the OTG controller.

For more details on serial controller, see Section 11.

# 8.2 V<sub>BUS</sub> charge pump

The charge pump supplies current to the  $V_{BUS}$  line. It can operate in any of the following modes:

- Output 5 V at current greater than 8 mA

- Pull-up V<sub>BUS</sub> to 3.3 V through a resistor (R<sub>VBUS(PU)</sub>) for initiating V<sub>BUS</sub> pulsing SRP

- Pull-down V<sub>BUS</sub> to ground through a resistor (R<sub>VBUS(PD)</sub>) for discharging V<sub>BUS</sub> before initiating SRP.

#### 8.3 V<sub>BUS</sub> comparators

V<sub>BUS</sub> comparators provide indications regarding the voltage level on V<sub>BUS</sub>.

#### 8.3.1 V<sub>BUS</sub> valid comparator

This comparator is used by an A-device to determine whether or not the voltage on  $V_{BUS}$  is at a valid level for operation. The minimum threshold for the  $V_{BUS}$  valid comparator is 4.4 V. Any voltage on  $V_{BUS}$  below this threshold is considered to be a fault. During power up, it is expected that the comparator output will be ignored.

#### 8.3.2 Session valid comparator

The session valid comparator is a TTL-level input that determines when  $V_{BUS}$  is high enough for a session to start. Both the A-device and the B-device use this comparator to detect when a session is being started. The A-device also uses this comparator to indicate when a session is completed. The session valid threshold of the ISP1301 is between 0.8 V and 2.0 V.

#### 8.3.3 Session end comparator

The session end comparator determines when  $V_{BUS}$  is below the B-device session end threshold of 0.2 V to 0.8 V.

9397 750 11355 Product data

7 of 46

**USB OTG transceiver**

#### 8.4 ID detector

In either the active or suspended power mode, the ID detector senses the condition of the ID line and differentiates between the following three conditions:

- Pin ID is floating; bit ID FLOAT = 1

- Pin ID is shorted to ground; bit ID\_GND = 1

- Pin ID is connected to ground through resistor R<sub>ACC\_ID</sub>; bit ID\_FLOAT = 0 and bit ID\_GND = 0.

The ID detector also has a switch that can be used to ground pin ID. This switch is controlled by bit ID PULLDOWN in the serial controller.

# 8.5 Pull-up and pull-down resistors

The pull-up and pull-down resistors include the following switchable resistors:

- Pin DP pull-up

- Pin DP pull-down

- Pin DM pull-up

- Pin DM pull-down.

The pull-up resistor is a context variable as described in the *ECN\_27%\_Resistor* document. The variable pull-up resistor hardware is implemented to meet the USB ECN\_27% specification.

# 8.6 USB transceiver (ATX)

The behavior of the USB transceiver depends on the operation mode of the ISP1301:

- In the USB mode, the USB transceiver block performs USB full-speed or low-speed transceiver functions. This includes differential driver, differential receiver and single-ended receivers.

- In the transparent general purpose buffer mode or the UART mode, the USB transceiver block functions as a level shifter between the pins DAT/VP and SE0/VM and the pins DP and DM.

# 8.7 3.3 V DC-DC regulator

The built-in 3.3 V DC-DC regulator conditions the supply voltage ( $V_{BAT}$ ) for use in the ISP1301:

- $\bullet$  V<sub>BAT</sub> = 3.6 V to 4.5 V: the regulator will output 3.3 V  $\pm$  10 %

- V<sub>BAT</sub> < 3.6 V: the regulator will be bypassed.

The output of the regulator can be monitored on the  $V_{\mbox{\scriptsize REG}(3V3)}$  pin.

# 8.8 Car kit interrupt detector

The car kit interrupt detector is a comparator that detects when the DP line is below the car kit interrupt threshold  $V_{PH\_CR\_INT}$  (0.4 V to 0.6 V). The car kit interrupt detector is enabled in the audio mode only (bit AUDIO\_EN = 1).

9397 750 11355

**USB OTG transceiver**

## 8.9 Detailed description of pins

#### 8.9.1 ADR/PSW

The ADR/PSW pin has two functions. On reset (including power-on reset), the level on this pin is latched as ADR\_REG, which represents the least significant bit (LSB) of the  $I^2C$  address of the ISP1301. If bit ADR\_REG = 0, the  $I^2C$ -bus address for the ISP1301 is 0101100 (0x2C); if bit ADR\_REG = 1, the  $I^2C$ -bus address for the ISP1301 is 0101101 (0x2D).

After reset, the ADR/PSW pin can be programmed as an output. If in the Mode Control 2 register bit PSW\_OE = 1, then the ADR/PSW output will be enabled. The logic level will be determined by bit ADR\_REG. If bit ADR\_REG = 0, then the ADR/PSW pin will drive HIGH. If bit ADR\_REG = 1, then the ADR/PSW pin will drive LOW.

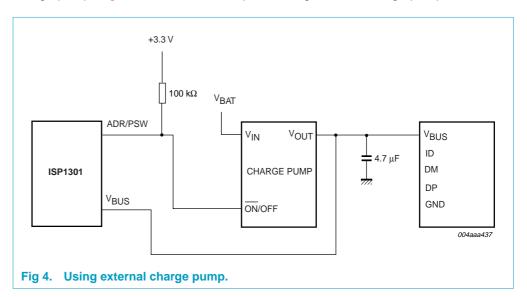

The ADR/PSW pin can be used to turn on or off the external charge pump. The ISP1301 built-in charge pump supports  $V_{BUS}$  current at 8 mA. If the application needs more current support (for example, 50 mA), an external charge pump may be needed. In this case, the ADR/PSW pin can act as a power switch for the external charge pump. Figure 4 shows an example of using external charge pump.

#### 8.9.2 SCL and SDA

The SCL (serial clock) and SDA (serial data) signals implement a two-wire serial I<sup>2</sup>C-bus.

#### 8.9.3 **RESET N**

Active LOW asynchronous reset for all digital logic. Either connect this pin to  $V_{DD\_LGC}$  for power-on reset or apply a minimum of 10  $\mu s$  LOW pulse for hardware reset.

# 8.9.4 INT\_N

The INT\_N (interrupt) pin is asserted while an interrupt condition exists. It is deasserted when the Interrupt Latch register is cleared. The INT\_N pin is open-drain, and, therefore, can be connected using a wired-AND with other interrupt signals.

9397 750 11355

**USB OTG transceiver**

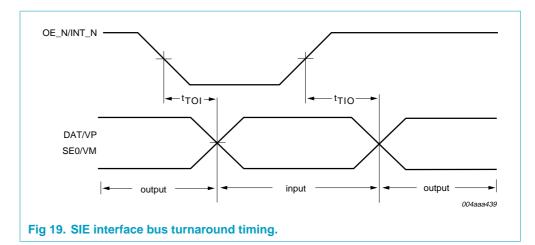

#### 8.9.5 **OE\_N/INT\_N**

Pin OE\_N/INT\_N is normally an input to the ISP1301.

When bit TRANSP\_EN = 0 and bit UART\_EN = 0, the OE\_N/INT\_N pin controls the direction of DAT/VP, SE0/VM, DP and DM as indicated in Table 4.

When suspended (either pin SUSPEND = HIGH or bit SUSPEND\_REG = 1) and bit OE\_INT\_EN = 1, pin OE\_N/INT\_N becomes a push-pull output (active LOW) to indicate the interrupt condition.

# 8.9.6 SE0/VM, DAT/VP, RCV, VM and VP

The ISP1301 transmits USB data on the USB line under the following conditions:

- Bit TRANSP EN = 0

- Bit UART\_EN = 0

- Pin OE N/INT N = LOW.

Table 10 shows the operation of the SE0/VM and DAT/VP pins during the transmit operation. The RCV pin is not used during transmit.

The ISP1301 receives USB data from the USB line under the following conditions:

- Bit TRANSP\_EN = 0

- Bit UART\_EN = 0

- Pin OE N/INT N = HIGH.

Table 12 shows the operation of the SE0/VM, DAT/VP and RCV pins during the receive operation.

The VP and VM pins are single-ended receiver outputs of the DP and DM pins, respectively.

#### 8.9.7 **DP and DM**

The DP (data plus) and DM (data minus) pins implement the USB data signals. When in the transparent general-purpose buffer mode, the ISP1301 operates as a level shifter between the (DAT/VP, SE0/VM) and (DP, DM) pins.

#### 8.9.8 ID

The ID (identification) pin is connected to the ID pin on the USB mini receptacle. An internal pull-up resistor (to  $V_{REG(3V3)}$ ) is connected to this pin. When bit ID\_PULLDOWN is set, the ID pin will be shorted to ground.

# 8.9.9 V<sub>BUS</sub>

This pin acts as an input to the V<sub>BUS</sub> comparator or an output from the charge pump.

When the VBUS\_DRV bit of the OTG Control register is asserted, the ISP1301 tries to drive V<sub>BUS</sub> to a voltage of 4.4 V to 5.25 V with an output current capability of at least 8 mA.

**ISP1301 Philips Semiconductors**

**USB OTG transceiver**

#### 8.9.10 V<sub>BAT</sub>

This pin is an input and supplies power to the ISP1301. The ISP1301 operates when V<sub>BAT</sub> is between 2.7 V and 4.5 V.

#### 8.9.11 C1 and C2

The C1 and C2 pins are for connecting the flying capacitor of the charge pump. The output current capacity of the charge pump depends on the value of the capacitor. For maximum efficiency, place capacitors as close as possible to the pins.

Recommended charge pump capacitor value Table 3:

| C <sub>ext</sub> | I <sub>L</sub> (max) <sup>[1]</sup> |

|------------------|-------------------------------------|

| 47 nF            | 8 mA                                |

| 100 nF           | 18 mA <sup>[2]</sup>                |

- [1] For output voltage  $V_{BUS} > 4.7 \text{ V}$  (bit  $VBUS\_VLD = 1$ ).

- [2] For  $V_{BAT} = 3.0 \text{ V}$  to 4.5 V.

# 8.9.12 V<sub>DD\_LGC</sub>

This pin is an input and sets logic thresholds. It also powers the pads of the following logic pins:

- ADR/PSW

- DAT/VP, SE0/VM and RCV

- VM and VP

- INT N

- OE N/INT N

- RESET N

- SPEED

- SUSPEND

- SCL and SDA.

#### 8.9.13 AGND, CGND and DGND

AGND, CGND and DGND are ground pins for analog, charge pump and digital circuits, respectively. These pins can be connected separately or together depending on the system performance requirements.

**USB OTG transceiver**

# 9. Modes of operation

There are four types of modes in the ISP1301:

- Power modes

- Direct I<sup>2</sup>C-bus mode

- USB modes

- Transparent modes.

# 9.1 Power modes

The power modes of the ISP1301 are as follows:

- Active power mode: power is on.

- USB suspend mode: to reduce power consumption, the USB differential receiver is powered down.

- Global power-down mode: set bit GLOBAL\_PWR\_DN = 1 of the Mode Control 2

register; the differential transmitter and receiver, clock generator, charge pump,

and all biasing circuits are turned off to reduce power consumption to the minimum

possible; for details on waking up the clock, see Section 12.

## 9.2 Direct I<sup>2</sup>C-bus mode

In the direct I<sup>2</sup>C-bus mode, an external I<sup>2</sup>C-bus master (OTG controller) directly communicates with the serial controller through the SCL and SDA lines. The serial controller has a built-in I<sup>2</sup>C-bus slave function.

In this mode, an external  $I^2C$ -bus master can access the internal registers of the device (Status, Control, Interrupt, and so on) through the  $I^2C$ -bus interface.

The supported I<sup>2</sup>C-bus bit rate is 100 kbit/s (maximum).

The ISP1301 is in the direct  $I^2C$ -bus mode when either bit TRANSP\_EN bit = 0 or pin OE\_N/INT\_N is deasserted.

#### 9.3 USB modes

The four USB modes of the ISP1301 are:

- VP VM unidirectional mode

- VP VM bidirectional mode

- DAT\_SE0 unidirectional mode

- DAT SE0 bidirectional mode.

In the VP\_VM USB mode, the DAT/VP pin is used for the VP function, the SE0/VM pin is used for the VM function, and the RCV pin is used for the RCV function.

In the DAT\_SE0 USB mode, the DAT/VP pin is used for the DAT function, the SE0/VM pin is used for the SE0 function, and the RCV pin is not used.

In the unidirectional mode, the DAT/VP and SE0/VM pins are always inputs. In the bidirectional mode, the direction of these signals depends on the OE\_N/INT\_N input.

9397 750 11355

**USB OTG transceiver**

Table 6 specifies the functionality of the device during the four USB modes.

The ISP1301 is in the USB mode when both the TRANSP\_EN and UART\_EN bits are cleared.

# 9.4 Transparent modes

# 9.4.1 Transparent general-purpose buffer mode

In the transparent general-purpose buffer mode, the DAT/VP and SE0/VM pins are connected to the DP and DM pins, respectively. Using bits TRANSP\_BDIR1 and TRANSP\_BDIR0 of the Mode Control 2 register as specified in Table 8, you can control the direction of data transfer. The ISP1301 is in the transparent general-purpose buffer mode if bit TRANSP\_EN = 1 and bit DAT\_SE0 = 1.

#### 9.4.2 Transparent UART mode

When in the transparent UART mode, the ATX behaves as two logic level translator between the following pins:

- For TxD signal: from SE0/VM (V<sub>DD LGC</sub> level) to DM (+3.3 V level)

- For RxD signal: from DP (+3.3 V level) to DAT/VP (V<sub>DD\_LGC</sub> level).

In the UART mode, the OTG controller is allowed to connect a UART to the DAT/VP and SE0/VM pins of the ISP1301.

The UART mode is entered by setting the UART\_EN bit in the Mode Control 1 register. The UART mode is equivalent to one of the transparent general purpose buffer mode (bit TRANSP BDIR1 = 1, bit TRANSP BDIR0 = 0).

#### 9.4.3 Summary tables

Table 4: Device operating modes

| Mode                                    | USB<br>suspend<br>condition <sup>[1]</sup> | Bit<br>DAT<br>_SE0 | Pin<br>OE_N/<br>INT_N | Bit<br>TRANSP<br>_EN | Bit<br>UART<br>_ EN | Description                                                 |

|-----------------------------------------|--------------------------------------------|--------------------|-----------------------|----------------------|---------------------|-------------------------------------------------------------|

| Direct I <sup>2</sup> C-bus mode        |                                            |                    |                       |                      |                     |                                                             |

| Direct I <sup>2</sup> C-bus mode        | Χ                                          | X                  | Χ                     | 0                    | X                   |                                                             |

|                                         | Χ                                          | X                  | HIGH                  | 1                    | Χ                   |                                                             |

|                                         | Χ                                          | 1                  | X                     | 1                    | Χ                   |                                                             |

| USB modes                               |                                            |                    |                       |                      |                     |                                                             |

| USB suspend mode                        | 1                                          | X                  | X                     | 0                    | 0                   | see Table 5 and Table 7                                     |

| USB functional mode                     | 0                                          | Χ                  | Χ                     | 0                    | 0                   | ATX is fully functional; see Table 6                        |

| Transparent modes                       |                                            |                    |                       |                      |                     |                                                             |

| Transparent general-purpose buffer mode | X                                          | 1                  | Х                     | 1                    | 0                   | ATX is not functional; see Table 8                          |

| Transparent UART mode                   | Χ                                          | X                  | X                     | Χ                    | 1                   | DAT/VP <= DP (RxD signal of UART)                           |

|                                         |                                            |                    |                       |                      |                     | SE0/VM => DM (TxD signal of UART);<br>ATX is not functional |

#### [1] Conditions:

9397 750 11355

a) bit SPD\_SUSP\_CTRL = 0 and pin SUSPEND = HIGH, or

b) bit  $SPD\_SUSP\_CTRL = 1$  and bit  $SUSPEND\_REG = 0$ .

**USB OTG transceiver**

Table 5: USB suspend mode: I/O

| Pin              | Function                                                                       |

|------------------|--------------------------------------------------------------------------------|

| DP as output     | can be driven if pin OE_N/INT_N is active LOW, otherwise high-Z <sup>[1]</sup> |

| DM as output     | can be driven if pin OE_N/INT_N is active LOW, otherwise high-Z <sup>[1]</sup> |

| V <sub>BUS</sub> | can be driven depending on bit VBUS_DRV                                        |

| SCL              | connected to SCL I/O of the I <sup>2</sup> C-bus slave                         |

| SDA              | connected to SDA I/O of the I <sup>2</sup> C-bus slave                         |

<sup>[1]</sup> In the USB suspend mode, the ISP1301 can drive the DP and DM lines, if the OE\_N/INT\_N input (when the OE\_INT\_EN bit is not set) is LOW. In such a case, these outputs are driven as in the USB functional modes, but with the full-speed characteristics, irrespective of the value of the SPEED input pin or the SPEED\_REG bit.

Table 6: USB functional modes: I/O values<sup>[1]</sup>

| USB mode      |                | Bit     |       | Pin                |                     |                     |                     |         |                    |

|---------------|----------------|---------|-------|--------------------|---------------------|---------------------|---------------------|---------|--------------------|

|               |                | DAT_SE0 | BI_DI | OE_N/<br>INT_N     | DAT/VP              | SE0/VM              | VP                  | VM      | RCV                |

| VP_VM         | unidirectional | 0       | 0     | X                  | TxD+ <sup>[2]</sup> | TxD-[2]             | RxD+ <sup>[3]</sup> | RxD-[3] | RxD <sup>[3]</sup> |

|               | bidirectional  | 0       | 1     | LOW                | TxD+[2]             | TxD-[2]             |                     |         |                    |

|               |                | 0       | 1     | HIGH               | RxD+[3]             | RxD-[3]             |                     |         |                    |

| DAT_SE0       | unidirectional | 1       | 0     | X                  | TxD <sup>[4]</sup>  | FSE0 <sup>[5]</sup> |                     |         |                    |

| bidirectional | 1              | 1       | LOW   | TxD <sup>[4]</sup> | FSE0 <sup>[5]</sup> |                     |                     |         |                    |

|               |                | 1       | 1     | HIGH               | RxD <sup>[6]</sup>  | RSE0[7]             |                     |         |                    |

- [1] Some of the modes and signals are provided to achieve backward compatibility with IP cores.

- [2] TxD+ and TxD- are single-ended inputs for driving the DP and DM outputs, respectively, in the single-ended mode.

- [3] RxD+ and RxD- are the outputs of the single-ended receivers connected to DP and DM, respectively.

- [4] TxD is the input for driving DP and DM in the DAT\_SE0 mode.

- [5] FSE0 is for forcing an SE0 on the DP and DM lines in the DAT\_SE0 mode.

- [6] RxD is the output of the differential receiver.

- [7] RSE0 is an output indicating that an SE0 has been received on the DP and DM lines.

Table 7: USB suspend mode: I/O values

| <b>USB</b> suspend mode | Input pin |      | Output pin |        |      |      |     |  |

|-------------------------|-----------|------|------------|--------|------|------|-----|--|

|                         | DP        | DM   | DAT/VP     | SE0/VM | VP   | VM   | RCV |  |

| DAT_SE0                 | LOW       | LOW  | LOW        | HIGH   | LOW  | LOW  | LOW |  |

| (bit DAT_SE0 = 1)       | HIGH      | LOW  | HIGH       | LOW    | HIGH | LOW  | LOW |  |

|                         | LOW       | HIGH | LOW        | LOW    | LOW  | HIGH | LOW |  |

|                         | HIGH      | HIGH | HIGH       | LOW    | HIGH | HIGH | LOW |  |

| VP_VM                   | LOW       | LOW  | LOW        | LOW    | LOW  | LOW  | LOW |  |

| (bit DAT_SE0 = 0)       | HIGH      | LOW  | HIGH       | LOW    | HIGH | LOW  | LOW |  |

|                         | LOW       | HIGH | LOW        | HIGH   | LOW  | HIGH | LOW |  |

|                         | HIGH      | HIGH | HIGH       | HIGH   | HIGH | HIGH | LOW |  |

|                         |           |      |            |        |      |      |     |  |

**USB OTG transceiver**

Table 8: Transparent general-purpose buffer mode

| Bit<br>TRANSP_BDIR[1:0] | Direction of the data flow |                         |  |  |

|-------------------------|----------------------------|-------------------------|--|--|

| 00                      | $DAT/VP \Rightarrow DP$    | $SE0/VM \Rightarrow DM$ |  |  |

| 01                      | $DAT/VP \Rightarrow DP$    | $SE0/VM \ll DM$         |  |  |

| 10                      | $DAT/VP \ll DP$            | $SE0/VM \Rightarrow DM$ |  |  |

| 11                      | $DAT/VP \ll DP$            | $SE0/VM \ll DM$         |  |  |

# 10. USB transceiver

# 10.1 Differential driver

The operation of the driver is described in Table 9. The register bits and the pins used in the column heading are described in Section 11.1 and Section 8.9, respectively.

Table 9: Transceiver driver operation setting

| Suspend <sup>[1]</sup> | Bit<br>TRANSP_<br>EN | Pin<br>OE_N/<br>INT_N | Bit<br>DAT_SE0 | Differential driver                                                                       |

|------------------------|----------------------|-----------------------|----------------|-------------------------------------------------------------------------------------------|

| 0                      | 0                    | LOW                   | 0              | output value from DAT/VP to DP and SE0/VM to DM                                           |

| 0                      | 0                    | LOW                   | 1              | output value from DAT/VP to DP and DM if SE0/VM is 0; otherwise, drive both DP and DM LOW |

| 1                      | 0                    | LOW                   | Χ              | output value from DAT/VP to DP and DM                                                     |

| Χ                      | Χ                    | HIGH                  | Χ              | high-Z                                                                                    |

| Χ                      | 1                    | Χ                     | Χ              | high-Z                                                                                    |

<sup>[1]</sup> Can be controlled by using either the SUSPEND pin or the SUSPEND\_REG bit.

Table 10: USB functional mode: transmit operation

| T/VP           |                          |                                           | Output pin                                                          |  |  |

|----------------|--------------------------|-------------------------------------------|---------------------------------------------------------------------|--|--|

| XI/VE          | SE0/VM                   | DP                                        | DM                                                                  |  |  |

| )W             | LOW                      | LOW                                       | HIGH                                                                |  |  |

| GH             | LOW                      | HIGH                                      | LOW                                                                 |  |  |

| W              | HIGH                     | LOW                                       | LOW                                                                 |  |  |

| GH             | HIGH                     | LOW                                       | LOW                                                                 |  |  |

| W              | LOW                      | LOW                                       | LOW                                                                 |  |  |

| GH             | LOW                      | HIGH                                      | LOW                                                                 |  |  |

| W              | HIGH                     | LOW                                       | HIGH                                                                |  |  |

| GH             | HIGH                     | HIGH                                      | HIGH                                                                |  |  |

| ()<br>()<br>() | GH<br>W<br>GH<br>W<br>GH | GH LOW W HIGH GH HIGH W LOW GH LOW W HIGH | GH LOW HIGH W HIGH LOW GH HIGH LOW W LOW LOW GH LOW HIGH W HIGH LOW |  |  |

# 10.2 Differential receiver

Table 11 describes the operation of the differential receiver. The register bits and the pins used in the column heading are described in Section 11.1 and Section 8.9, respectively.

**USB OTG transceiver**

The detailed behavior of the receive transceiver operation is given in Table 12.

Table 11: Differential receiver operation settings

| Suspend <sup>[1]</sup> | Bit<br>TRANSP_EN | Pin<br>OE_N/INT_N | Bit<br>DAT_SE0 | Differential receiver                                      |

|------------------------|------------------|-------------------|----------------|------------------------------------------------------------|

| 1                      | X                | X                 | Χ              | 0                                                          |

| X                      | X                | LOW               | Χ              | 0                                                          |

| X                      | 1                | X                 | Χ              | 0                                                          |

| 0                      | 0                | HIGH              | 1              | output differential value from DP and DM to DAT/VP and RCV |

| 0                      | 0                | HIGH              | 0              | output differential value from DP and DM to RCV            |

<sup>[1]</sup> Can be controlled by using either the SUSPEND pin or the SUSPEND\_REG bit.

Table 12: USB functional mode: receive operation

| USB mode | Suspend <sup>[1]</sup> | Input pin |      | Output pin |        |                   |

|----------|------------------------|-----------|------|------------|--------|-------------------|

|          |                        | DP        | DM   | DAT/VP     | SE0/VM | RCV               |

| DAT_SE0  | 0                      | LOW       | LOW  | RCV        | HIGH   | last value of RCV |

| DAT_SE0  | 0                      | HIGH      | LOW  | HIGH       | LOW    | HIGH              |

| DAT_SE0  | 0                      | LOW       | HIGH | LOW        | LOW    | LOW               |

| DAT_SE0  | 0                      | HIGH      | HIGH | RCV        | LOW    | last value of RCV |

| DAT_SE0  | 1                      | LOW       | LOW  | LOW        | HIGH   | LOW               |

| DAT_SE0  | 1                      | HIGH      | LOW  | HIGH       | LOW    | LOW               |

| DAT_SE0  | 1                      | LOW       | HIGH | LOW        | LOW    | LOW               |

| DAT_SE0  | 1                      | HIGH      | HIGH | HIGH       | LOW    | LOW               |

| VP_VM    | 0                      | LOW       | LOW  | LOW        | LOW    | last value of RCV |

| VP_VM    | 0                      | HIGH      | LOW  | HIGH       | LOW    | HIGH              |

| VP_VM    | 0                      | LOW       | HIGH | LOW        | HIGH   | LOW               |

| VP_VM    | 0                      | HIGH      | HIGH | HIGH       | HIGH   | last value of RCV |

| VP_VM    | 1                      | LOW       | LOW  | LOW        | LOW    | LOW               |

| VP_VM    | 1                      | HIGH      | LOW  | HIGH       | LOW    | LOW               |

| VP_VM    | 1                      | LOW       | HIGH | LOW        | HIGH   | LOW               |

| VP_VM    | 1                      | HIGH      | HIGH | HIGH       | HIGH   | LOW               |

<sup>[1]</sup> Can be controlled by using either the SUSPEND pin or the SUSPEND\_REG bit.

**USB OTG transceiver**

# 11. Serial controller

# 11.1 Register map

Table 13 provides an overview of the serial controller registers.

Table 13: Serial controller registers

| Register              | Width<br>(bits) | Access <sup>[1]</sup> | Memory address   | Functionality                   | Reference                   |  |

|-----------------------|-----------------|-----------------------|------------------|---------------------------------|-----------------------------|--|

| Vendor ID             | 16              | R                     | 00–01H           | device identification registers | s Section 11.1.1 on page 17 |  |

| Product ID            | 16              | R                     | 02-03H           |                                 |                             |  |

| Version ID            | 16              | R                     | 14–15H           |                                 |                             |  |

| Mode Control 1        | 8               | R/S/C                 | <b>Set</b> — 04H | mode control registers          | Section 11.1.2 on page 18   |  |

|                       |                 |                       | Clear — 05H      |                                 |                             |  |

| Mode Control 2        | 8               | R/S/C                 | <b>Set</b> — 12H |                                 |                             |  |

|                       |                 |                       | Clear — 13H      |                                 |                             |  |

| OTG Control           | 8               | R/S/C                 | <b>Set</b> — 06H | OTG registers                   | Section 11.1.3 on page 19   |  |

|                       |                 |                       | Clear — 07H      |                                 |                             |  |

| OTG Status            | 8               | R                     | 10H              | _                               |                             |  |

| Interrupt Source      | 8               | R                     | 08H              | interrupt related registers     | Section 11.1.4 on page 20   |  |

| Interrupt Latch       | 8               | R/S/C                 | Set — 0AH        |                                 |                             |  |

|                       |                 |                       | Clear — 0BH      |                                 |                             |  |

| Interrupt Enable Low  | 8               | R/S/C                 | Set — 0CH        |                                 |                             |  |

|                       |                 |                       | Clear — 0DH      |                                 |                             |  |

| Interrupt Enable High | 8               | R/S/C                 | Set — 0EH        |                                 |                             |  |

|                       |                 |                       | Clear — 0FH      |                                 |                             |  |

<sup>[1]</sup> The R/S/C access type represents a field that can be read, set or cleared (set to 0). A register can be read from either of the indicated addresses—set or clear. Writing logic 1 to the set address causes the associated bit to be set. Writing logic 1 to the clear address causes the associated bit to be cleared. Writing logic 0 to an address has no effect.

#### 11.1.1 Device identification registers

**Vendor ID register (Read: 00H–01H): Table 14** provides the bit allocation of the Vendor ID register.

Table 14: Vendor ID register: bit description

| Bit     | Symbol             | Access | Value | Description                       |

|---------|--------------------|--------|-------|-----------------------------------|

| 15 to 0 | VENDORID<br>[15:0] | R      | 04CCH | Philips Semiconductors' Vendor ID |

Product ID register (Read: 02H–03H): The bit allocation of this register is given in Table 15.

Table 15: Product ID register: bit description

| Bit     | Symbol              | Access | Value | Description               |

|---------|---------------------|--------|-------|---------------------------|

| 15 to 0 | PRODUCTID<br>[15:0] | R      | 1301H | Product ID of the ISP1301 |

9397 750 11355

#### **USB OTG transceiver**

Version ID register (Read: 14H–15H): Table 16 shows the bit allocation of this register.

Table 16: Version ID register: bit description

| Bit     | Symbol              | Access | Value | Description                   |

|---------|---------------------|--------|-------|-------------------------------|

| 15 to 0 | VERSIONID<br>[15:0] | R      | 0210H | Version number of the ISP1301 |

# 11.1.2 Mode control registers

Mode Control 1 register (Set/Clear: 04H/05H): The bit allocation of the Mode Control 1 register is given in Table 17.

Table 17: Mode Control 1 register: bit allocation

| Bit    | 7     | 6       | 5             | 4                | 3             | 2       | 1               | 0             |

|--------|-------|---------|---------------|------------------|---------------|---------|-----------------|---------------|

| Symbol | -     | UART_EN | OE_INT_<br>EN | BDIS_<br>ACON_EN | TRANSP_<br>EN | DAT_SE0 | SUSPEND<br>_REG | SPEED_<br>REG |

| Reset  | -     | 0       | 0             | 0                | 0             | 0       | 0               | 0             |

| Access | R/S/C | R/S/C   | R/S/C         | R/S/C            | R/S/C         | R/S/C   | R/S/C           | R/S/C         |

Table 18: Mode Control 1 register: bit description

| Bit | Symbol       | Description                                                                                                       |

|-----|--------------|-------------------------------------------------------------------------------------------------------------------|

| 7   | -            | reserved                                                                                                          |

| 6   | UART_EN      | When set, the ATX is in the transparent UART mode.                                                                |

| 5   | OE_INT_EN    | When set and when in the suspend mode, pin OE_N/INT_N becomes an output and is asserted when an interrupt occurs. |

| 4   | BDIS_ACON_EN | Enables the A-device to connect if the B-device disconnect is detected; see Section 11.3                          |

| 3   | TRANSP_EN    | When set, the ATX is in the transparent mode.                                                                     |

| 2   | DAT_SE0      | 0 — VP_VM mode                                                                                                    |

|     |              | 1 — DAT_SE0 mode; see Table 6 and Table 7                                                                         |

| 1   | SUSPEND_REG  | Sets the ISP1301 in the suspend mode, if bit SPD_SUSP_CTRL = 1.                                                   |

|     |              | 0 — active-power mode                                                                                             |

|     |              | 1 — USB suspend mode                                                                                              |

| 0   | SPEED_REG    | Sets the rise time and the fall time of the transmit driver in USB modes, if bit SPD_SUSP_CTRL = 1.               |

|     |              | 0 — USB low-speed mode                                                                                            |

|     |              | 1 — USB full-speed mode                                                                                           |

|     |              |                                                                                                                   |

Mode Control 2 register (Set/Clear: 12H/13H): For the bit allocation of this register, see Table 19.

**USB OTG transceiver**

Table 19: Mode Control 2 register: bit allocation

| Bit    | 7     | 6      | 5        | 4                | 3                | 2     | 1                 | 0                 |

|--------|-------|--------|----------|------------------|------------------|-------|-------------------|-------------------|

| Symbol | EN2V7 | PSW_OE | AUDIO_EN | TRANSP_<br>BDIR1 | TRANSP_<br>BDIR0 | BI_DI | SPD_SUSP<br>_CTRL | GLOBAL_<br>PWR_DN |

| Reset  | 0     | 0      | 0        | 0                | 0                | 1     | 0                 | 0                 |

| Access | R/S/C | R/S/C  | R/S/C    | R/S/C            | R/S/C            | R/S/C | R/S/C             | R/S/C             |

Table 20: Mode Control 2 register: bit description

| Bit    | Symbol           | Description                                                                                         |

|--------|------------------|-----------------------------------------------------------------------------------------------------|

| 7      | EN2V7            | <b>0</b> — V <sub>BAT</sub> = 3.0 V to 4.5 V                                                        |

|        |                  | <b>1</b> — V <sub>BAT</sub> = 2.7 V to 4.5 V                                                        |

| 6      | PSW_OE           | 0 — ADR/PSW pin acts as an input                                                                    |

|        |                  | 1 — ADR/PSW pin is driven                                                                           |

| 5      | AUDIO_EN         | <ul><li>0 — SE receiver is enabled; cr_int detector is disabled</li></ul>                           |

|        |                  | 1 — SE receiver is turned off (pin VP = LOW, pin VM = LOW);<br>cr_int detector is enabled           |

| 4 to 3 | TRANSP_BDIR[1:0] | controls the direction of data transfer in the transparent general-purpose buffer mode; see Table 8 |

| 2      | BI_DI            | ${\bf 0} - {\rm direction\ of\ DAT/VP\ and\ SE0/VM\ are\ fixed\ (transmit\ only)}$                  |

|        |                  | 1 — direction of DAT/VP and SE0/VM are controlled by pin OE_N/INT_N; see Table 6                    |

| 1      | SPD_SUSP_CTRL    | control of speed and suspend in USB modes:                                                          |

|        |                  | 0 — controlled by pins SPEED and SUSPEND                                                            |

|        |                  | 1 — controlled by bit SPEED_REG and bit SUSPEND_REG of the Mode Control 1 register                  |

| 0      | GLOBAL_PWR_DN    | 0 — normal operation                                                                                |

|        |                  | 1 — sets the ISP1301 to the power down mode                                                         |

|        |                  | Activities on the I <sup>2</sup> C-bus or any OTG event can wake up the chip; see Section 12        |

# 11.1.3 OTG registers

OTG Control register (Set/Clear: 06H/07H): Table 21 provides the bit allocation of the OTG Control register.

Table 21: OTG Control register: bit allocation

| Bit    | 7             | 6                | 5            | 4               | 3               | 2               | 1             | 0             |

|--------|---------------|------------------|--------------|-----------------|-----------------|-----------------|---------------|---------------|

| Symbol | VBUS_<br>CHRG | VBUS_<br>DISCHRG | VBUS_<br>DRV | ID_PULL<br>DOWN | DM_PULL<br>DOWN | DP_PULL<br>DOWN | DM_PULL<br>UP | DP_PULL<br>UP |

| Reset  | 0             | 0                | 0            | 0               | 1               | 1               | 0             | 0             |

| Access | R/S/C         | R/S/C            | R/S/C        | R/S/C           | R/S/C           | R/S/C           | R/S/C         | R/S/C         |

**USB OTG transceiver**

Table 22: OTG Control register: bit description

| Bit | Symbol       | Description                                             |

|-----|--------------|---------------------------------------------------------|

| 7   | VBUS_CHRG    | charge V <sub>BUS</sub> through a resistor to 3.3 V     |

| 6   | VBUS_DISCHRG | discharge V <sub>BUS</sub> through a resistor to ground |

| 5   | VBUS_DRV     | drive V <sub>BUS</sub> to 5 V through the charge pump   |

| 4   | ID_PULLDOWN  | connect the ID pin to ground                            |

| 3   | DM_PULLDOWN  | connect DM pull-down resistor to ground                 |

| 2   | DP_PULLDOWN  | connect DP pull-down resistor to ground                 |

| 1   | DM_PULLUP    | connect DM pull-up resistor to 3.3 V                    |

| 0   | DP_PULLUP    | connect DP pull-up resistor to 3.3 V                    |

OTG Status register (Read: 10H): Table 23 shows the bit allocation of the OTG Status register.

Table 23: OTG Status register: bit allocation

| Bit    | 7              | 6              | 5 | 4 | 3    | 2    | 1 | 0 |

|--------|----------------|----------------|---|---|------|------|---|---|

| Symbol | B_SESS_<br>VLD | B_SESS_<br>END |   |   | rese | rved |   |   |

| Reset  | 0              | 0              | 0 | 0 | 0    | 0    | 0 | 0 |

| Access | R              | R              | R | R | R    | R    | R | R |

Table 24: OTG Status register: bit description

|        |            | <u> </u>                                                                                           |

|--------|------------|----------------------------------------------------------------------------------------------------|

| Bit    | Symbol     | Description                                                                                        |

| 7      | B_SESS_VLD | set when the $V_{BUS}$ voltage is above the B-device session valid threshold (2.0 V to 4.0 V)      |

| 6      | B_SESS_END | set when the $V_{\text{BUS}}$ voltage is below the B-device session end threshold (0.2 V to 0.8 V) |

| 5 to 0 | -          | reserved                                                                                           |

# 11.1.4 Interrupt related registers

Interrupt Source register (Read: 08H): This register indicates the current state of the signals that can generate an interrupt. The bit allocation of the Interrupt Source register is given in Table 25.

Table 25: Interrupt Source register: bit allocation

| Bit    | 7      | 6             | 5        | 4     | 3      | 2     | 1        | 0        |

|--------|--------|---------------|----------|-------|--------|-------|----------|----------|

| Symbol | CR_INT | BDIS_<br>ACON | ID_FLOAT | DM_HI | ID_GND | DP_HI | SESS_VLD | VBUS_VLD |

| Reset  | 0      | 0             | 0        | 0     | 0      | 0     | 0        | 0        |

| Access | R      | R             | R        | R     | R      | R     | R        | R        |

**USB OTG transceiver**

Table 26: Interrupt Source register: bit description

| Bit | Symbol    | Description                                                                                                     |

|-----|-----------|-----------------------------------------------------------------------------------------------------------------|

| 7   | CR_INT    | DP pin is above the car kit interrupt threshold (0.4 V to 0.6 V)                                                |

| 6   | BDIS_ACON | set when bit BDIS_ACON_EN is set, and the ISP1301 asserts bit DP_PULLUP after detecting the B-device disconnect |

| 5   | ID_FLOAT  | ID pin is floating                                                                                              |

| 4   | DM_HI     | DM pin is HIGH                                                                                                  |

| 3   | ID_GND    | ID pin is connected to ground                                                                                   |

| 2   | DP_HI     | DP pin is HIGH                                                                                                  |

| 1   | SESS_VLD  | session valid comparator; threshold = 0.8 V to 2.0 V                                                            |

| 0   | VBUS_VLD  | A-device $V_{BUS}$ valid comparator; threshold > 4.4 V                                                          |

**Interrupt Latch register (Set/Clear: 0AH/0BH):** This register indicates the source that generated the interrupt. The bit allocation of the Interrupt Latch register is given in Table 27.

Table 27: Interrupt Latch register: bit allocation

| Bit    | 7      | 6             | 5        | 4     | 3      | 2     | 1        | 0        |

|--------|--------|---------------|----------|-------|--------|-------|----------|----------|

| Symbol | CR_INT | BDIS_<br>ACON | ID_FLOAT | DM_HI | ID_GND | DP_HI | SESS_VLD | VBUS_VLD |

| Reset  | 0      | 0             | 0        | 0     | 0      | 0     | 0        | 0        |

| Access | R/S/C  | R/S/C         | R/S/C    | R/S/C | R/S/C  | R/S/C | R/S/C    | R/S/C    |

Table 28: Interrupt Latch register: bit description

| Bit | Symbol    | Description                           |

|-----|-----------|---------------------------------------|

| 7   | CR_INT    | interrupt for CR_INT status change    |

| 6   | BDIS_ACON | interrupt for BDIS_ACON status change |

| 5   | ID_FLOAT  | interrupt for ID_FLOAT status change  |

| 4   | DM_HI     | interrupt for DM_HI status change     |

| 3   | ID_GND    | interrupt for ID_GND status change    |

| 2   | DP_HI     | interrupt for DP_HI status change     |

| 1   | SESS_VLD  | interrupt for SESS_VLD status change  |

| 0   | VBUS_VLD  | interrupt for VBUS_VLD status change  |

**Interrupt Enable Low register (Set/Clear: 0CH/0DH):** This register enables interrupts on transition from true to false. For the bit allocation of this register, see Table 29.

Table 29: Interrupt Enable Low register: bit allocation

| Bit    | 7      | 6             | 5        | 4     | 3      | 2     | 1        | 0        |

|--------|--------|---------------|----------|-------|--------|-------|----------|----------|

| Symbol | CR_INT | BDIS_<br>ACON | ID_FLOAT | DM_HI | ID_GND | DP_HI | SESS_VLD | VBUS_VLD |

| Reset  | 0      | 0             | 0        | 0     | 0      | 0     | 0        | 0        |

| Access | R/S/C  | R/S/C         | R/S/C    | R/S/C | R/S/C  | R/S/C | R/S/C    | R/S/C    |

**USB OTG transceiver**

Table 30: Interrupt Enable Low register: bit description

| Bit | Symbol    | Description                                              |

|-----|-----------|----------------------------------------------------------|

| 7   | CR_INT    | interrupt enable for CR_INT status change from 1 to 0    |

| 6   | BDIS_ACON | interrupt enable for BDIS_ACON status change from 1 to 0 |

| 5   | ID_FLOAT  | interrupt enable for ID_FLOAT status change from 1 to 0  |

| 4   | DM_HI     | interrupt enable for DM_HI status change from 1 to 0     |

| 3   | ID_GND    | interrupt enable for ID_GND status change from 1 to 0    |

| 2   | DP_HI     | interrupt enable for DP_HI status change from 1 to 0     |

| 1   | SESS_VLD  | interrupt enable for SESS_VLD status change from 1 to 0  |

| 0   | VBUS_VLD  | interrupt enable for VBUS_VLD status change from 1 to 0  |

Interrupt Enable High register (Set/Clear: 0EH/0FH): The Interrupt Enable High register enables interrupts on transition from FALSE to TRUE. Table 31 provides the bit allocation of this register.

Table 31: Interrupt Enable High register: bit allocation

| Bit    | 7      | 6             | 5        | 4     | 3      | 2     | 1        | 0        |

|--------|--------|---------------|----------|-------|--------|-------|----------|----------|

| Symbol | CR_INT | BDIS_<br>ACON | ID_FLOAT | DM_HI | ID_GND | DP_HI | SESS_VLD | VBUS_VLD |

| Reset  | 0      | 0             | 0        | 0     | 0      | 0     | 0        | 0        |

| Access | R/S/C  | R/S/C         | R/S/C    | R/S/C | R/S/C  | R/S/C | R/S/C    | R/S/C    |

Table 32: Interrupt Enable High register: bit description

|     |           | 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3                  |

|-----|-----------|----------------------------------------------------------|

| Bit | Symbol    | Description                                              |

| 7   | CR_INT    | interrupt enable for CR_INT status change from 0 to 1    |

| 6   | BDIS_ACON | interrupt enable for BDIS_ACON status change from 0 to 1 |

| 5   | ID_FLOAT  | interrupt enable for ID_FLOAT status change from 0 to 1  |

| 4   | DM_HI     | interrupt enable for DM_HI status change from 0 to 1     |

| 3   | ID_GND    | interrupt enable for ID_GND status change from 0 to 1    |

| 2   | DP_HI     | interrupt enable for DP_HI status change from 0 to 1     |

| 1   | SESS_VLD  | interrupt enable for SESS_VLD status change from 0 to 1  |

| 0   | VBUS_VLD  | interrupt enable for VBUS_VLD status change from 0 to 1  |

|     |           |                                                          |

# 11.2 Interrupts

Table 26 indicates the signals that can generate interrupts. Any of the signals given in Table 26 can generate an interrupt when the signal becomes either LOW or HIGH. After an interrupt has been generated, the OTG controller should be able to read the status of each signal and the bit that indicates whether or not that signal generated the interrupt.

A bit in the Interrupt Latch register is set when any of these occurs:

- Writing logic 1 to its set address causes the corresponding bit to be set

- The corresponding bit in the Interrupt Enable High register is set, and the associated signal changes from LOW to HIGH

- The corresponding bit in the Interrupt Enable Low register is set, and the associated signal changes from HIGH to LOW.

9397 750 11355

**USB OTG transceiver**

The Interrupt Latch register bit is cleared by writing logic 1 to its clear address.

#### 11.3 Autoconnect

The Host Negotiation Protocol (HNP) in the OTG supplement specifies the following sequence of events to transfer the role of the host from the A-device to the B-device:

- 1. The A-device puts the bus in the suspend state

- 2. The B-device simulates a disconnect by deasserting its DP pull-up

- 3. The A-device detects SE0 on the bus, and asserts its DP pull-up

- 4. The B-device detects that the DP line is HIGH, and takes the role of the host.

The OTG supplement specifies that the time between the B-device deasserting its DP pull-up and the A-device asserting its pull-up must be less than 3 ms. For an A-device with a slow interrupt response time, 3 ms may not be enough time to write an I<sup>2</sup>C-bus command to the ISP1301 to assert the DP pull-up. An alternative method is for the A-device transceiver to automatically assert the DP pull-up after detecting an SE0 from the B-device.

The sequence of events is as follows:

After finishing data transfers between the A-device and the B-device and before suspending the bus, the A-device sends SOFs. The B-device receives these SOFs, and does not transmit any packet back to the A-device. During this time, the A-device sets the BDIS\_ACON\_EN bit in the ISP1301. This enables the ISP1301 to look for SE0 whenever the A-device is not transmitting (that is, whenever the OE\_N/INT\_N pin of the ISP1301 is not asserted). After the BDIS\_ACON\_EN bit is set, the A-device stops transmitting SOFs and allows the bus to go to the idle state. If the B-device disconnects, the bus goes to SE0, and the ISP1301 logic automatically turns on the A-device pull-up.

**USB OTG transceiver**

# 12. Clock wake up scheme

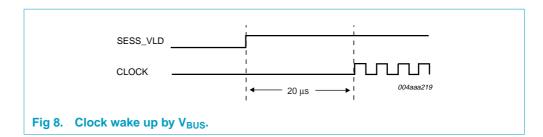

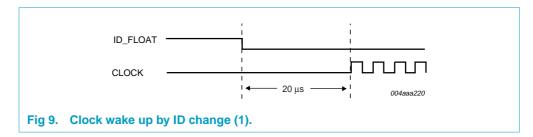

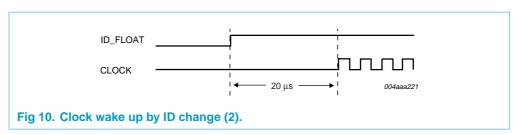

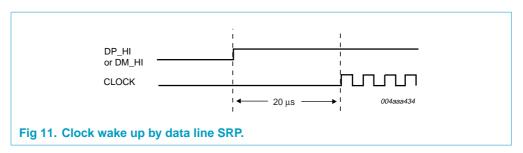

This section explains the ISP1301 clock stop timing, events triggering the clock to wake up, and the timing of the clock wake up.

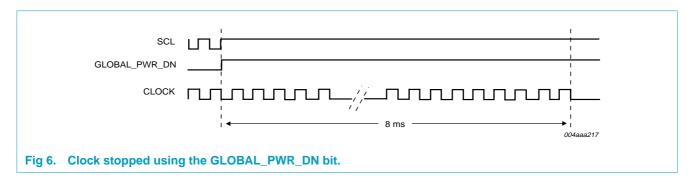

#### 12.1 Power down event

The clock is stopped when the GLOBAL\_PWR\_DN bit is set. It takes approximately 8 ms for the clock to stop from the time the power down condition is detected. The clock always stops at its falling edge. The waveform is given in Figure 6.

# 12.2 Clock wake up events

The clock wakes up when any of the following events occur on the ISP1301 pins:

- SCL goes LOW

- V<sub>BUS</sub> goes above the session valid threshold (0.8 V to 2.0 V), provided the SESS\_VLD bit in the Interrupt Enable High register is set.

- ID changes when mini-A plug is inserted, provided the ID\_FLOAT bit in the Interrupt Enable Low register is set.

- ID changes when mini-A plug is removed, provided the ID\_FLOAT bit in the Interrupt Enable High register is set.

- DP goes HIGH, provided the DP\_HI bit in the Interrupt Enable High register is set.

- DM goes HIGH, provided the DM\_HI bit in the Interrupt Enable High register is set.

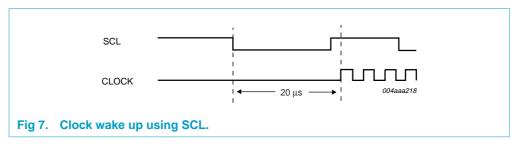

The event triggers the clock to start and a stable clock is guaranteed after about six clock periods, which is approximately 8  $\mu$ s. The startup analog clock time is 10  $\mu$ s. Therefore, the total estimated start time after a triggered event is about 20  $\mu$ s. The clock will always start at its rising edge.

Waveforms of the clock wake up because of different events are given in Figure 7, Figure 8, Figure 9, Figure 10 and Figure 11.

9397 750 11355

**USB OTG transceiver**

When an event is triggered and the clock is started, it will remain active for 8 ms. If the GLOBAL\_PWR\_DN bit is not cleared within this 8 ms period, the clock will stop. If the clock wakes up because of any event other than SCL going LOW, an interrupt will be generated once the clock is active.

**USB OTG transceiver**

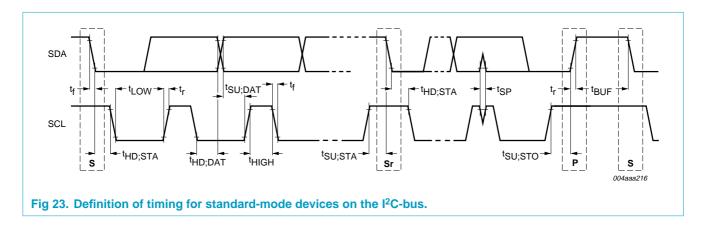

# 13. I<sup>2</sup>C-bus protocol

For detailed information, refer to *The I<sup>2</sup>C-bus specification; version 2.1*.

# 13.1 I<sup>2</sup>C-bus byte transfer format

Table 33: I<sup>2</sup>C-bus byte transfer format<sup>[1]</sup>

| S | Byte 1 | Α | Byte 2 | Α | Byte 3 | Α | <br>Α | Р |

|---|--------|---|--------|---|--------|---|-------|---|

|   | 8 bits |   | 8 bits |   | 8 bits |   |       |   |

<sup>[1]</sup> S = Start; A = Acknowledge; P = Stop.

# 13.2 I<sup>2</sup>C-bus device address

Table 34: Device address byte 1

| Bit   | 7  | 6  | 5  | 4          | 3  | 2  | 1  | 0   |

|-------|----|----|----|------------|----|----|----|-----|

|       |    |    | de | vice addre | ss |    |    | -   |

| Name  | A6 | A5 | A4 | А3         | A2 | A1 | A0 | R/W |

| Value | 0  | 1  | 0  | 1          | 1  | 0  | Χ  | Χ   |

Table 35: Bit description

| Bit    | Symbol | Description                                                                                                                                        |

|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 1 | A[6:0] | <b>Device address</b> : The device address of the ISP1301 is: 0101 10 (A0).                                                                        |

|        |        | The value of A0 (LSB) is loaded from pin ADR/PSW during reset (including power-on reset). If pin ADR/PSW = HIGH, bit A0 = 1; otherwise bit A0 = 0. |

| 0      | R/W    | Read/write command.                                                                                                                                |

|        |        | <b>0</b> — write                                                                                                                                   |

|        |        | <b>1</b> — read.                                                                                                                                   |

# 13.3 Write format

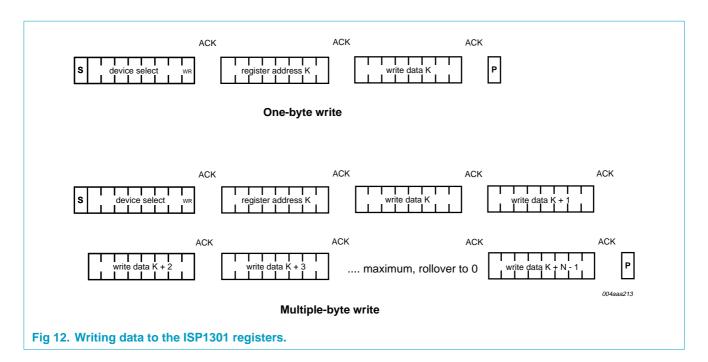

A write operation can be performed as:

- One-byte write to the specified register address

- Multi-byte write to N consecutive registers, starting from the specified start address. N defines the number of registers to write. If N = 1, only the start register is written.

# 13.3.1 One-byte write

Figure 12 illustrates the byte sequence.

Table 36: Transfer format description for one-byte write

| Byte               | Description                                                   |

|--------------------|---------------------------------------------------------------|

| S                  | master starts with a START condition                          |

| Device select      | master transmits device address and write command bit R/W = 0 |

| ACK                | slave generates an acknowledgment                             |

| Register address K | master transmits address of register K                        |

9397 750 11355

# **USB OTG transceiver**

Table 36:

Transfer format description for one-byte write...continued

| Byte         | Description                       |  |  |  |

|--------------|-----------------------------------|--|--|--|

| ACK          | slave generates an acknowledgment |  |  |  |

| Write data K | master writes data to register K  |  |  |  |

| ACK          | slave generates an acknowledgment |  |  |  |

| Р            | master generates a STOP condition |  |  |  |

# 13.3.2 Multiple-byte write

Figure 12 illustrates the byte sequence.

Table 37: Transfer format description for multiple-byte write

| Byte                    | Description                                                                                                                                                                                                                                                      |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S                       | master starts with a START condition                                                                                                                                                                                                                             |

| Device select           | master transmits device address and write command bit R/W = 0                                                                                                                                                                                                    |

| ACK                     | slave generates an acknowledgment                                                                                                                                                                                                                                |

| Register address K      | master transmits address of register K. This is the start address for writing multiple data bytes to consecutive registers. After a byte is written, the register address is automatically incremented by 1.                                                     |

|                         | <b>Remark:</b> If the master writes to a non existent register, the slave must send a 'not ACK' and also must not increment the index address.                                                                                                                   |

| ACK                     | slave generates an acknowledgment                                                                                                                                                                                                                                |

| Write data K            | master writes data to register K                                                                                                                                                                                                                                 |

| ACK                     | slave generates an acknowledgment                                                                                                                                                                                                                                |

| Write data K + 1        | master writes data to register K + 1                                                                                                                                                                                                                             |

| ACK                     | slave generates an acknowledgment                                                                                                                                                                                                                                |