# SIEMENS

# Microcontrollers

# ApNote

# AP163702

Reset and System Startup Configuration via PORT0

This application note presents an overview about the different reset types and the behaviour concerning the system startup configuration via PORT0. The calculation for the Pull-up/down resistors at PORT0 is also included.

Author: Mariutti / HL DC AT

| Conte                                | ents                                                                                                                                              | Page        |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| <b>1</b><br>1.1<br>1.2<br>1.3<br>1.4 | Overview about the different Reset Sources         Hardware Reset         Software Reset         Watchdog Timer Reset         Bidirectional Reset | 3<br>4<br>4 |

| <b>2</b><br>2.1<br>2.2               | System Startup Configuration         Overview about PORT0 Configuration during Reset         PORT0 Sample Timing for the different Reset Types    | 6           |

| <b>3</b><br>3.1<br>3.2               | Calculation of the Pull-up/down Resistors at PORT0 for Startup Configuration Pull-down Calculation Pull-up Calculation at Port_0                  | 10          |

| <b>4</b><br>A<br>B                   | Appendix                                                                                                                                          | 13          |

|                                                                                               | AP163702 ApNote - Revision History              |                                                                     |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|--|--|--|

|                                                                                               | Actual Revision : 6.98 Previous Revision : 9.97 |                                                                     |  |  |  |  |  |  |  |

| Page of<br>actual Rev.       Page of<br>prev.Rel.       Subjects (changes since last release) |                                                 |                                                                     |  |  |  |  |  |  |  |

| 4                                                                                             | 4                                               | 1.4 Bidirectional Reset: Device list updated                        |  |  |  |  |  |  |  |

| 5                                                                                             | 5                                               | 'IO line' replaced by 'IO line with an integrated pull-up resistor' |  |  |  |  |  |  |  |

| 6                                                                                             | 6                                               | Table 2: Column EA and RD added                                     |  |  |  |  |  |  |  |

| 11                                                                                            | 11                                              | Figure 9: Sign of I <sub>SYSH</sub> corrected                       |  |  |  |  |  |  |  |

| 14                                                                                            | 14                                              | Order of CSSEL pins corrected                                       |  |  |  |  |  |  |  |

| 15                                                                                            | 15                                              | Appendix clock options and steps updated                            |  |  |  |  |  |  |  |

#### 1 Overview about the different Reset Sources

During reset, the device executes a special internal sequence in order to set inside signals and the special function registers to their specified default values. The contents of some special function registers are controlled during system startup configuration via PORT0.

The system startup configuration is sampled upon different reset events. See table 1:

- Hardware Reset:

- Power-on Reset

- Short Hardware Reset (Warm Reset)

- Long Hardware Reset (Power Down Wakeup Reset)

- Software Reset

- Watchdog Timer Reset

| Reset Source         | Short-cut | Condition                                                |  |  |

|----------------------|-----------|----------------------------------------------------------|--|--|

| Power-on Reset       | PONR      | Power-on                                                 |  |  |

| Short Hardware Reset | SHWR      | $4 \text{ TCL} < t_{\text{RSTIN}} \leq 1024 \text{ TCL}$ |  |  |

| Long Hardware Reset  | LHWR      | t <sub>RSTIN</sub> > 1024 TCL                            |  |  |

| Watchdog Timer Reset | WDTR      | WDT overflow                                             |  |  |

| Software Reset       | SWR       | SRST command                                             |  |  |

#### Table 1:

#### **Reset Sources and Reset Conditions**

#### 1.1 Hardware Reset

A hardware reset is triggered when the reset input signal  $\overrightarrow{RSTIN}$  is latched low. To ensure the recognition of the  $\overrightarrow{RSTIN}$  signal (latching), it must be held low for at least 2 CPU clock cycles (4 TCL = 100 nsec @ 20 MHz CPU Clock). Also shorter  $\overrightarrow{RSTIN}$  pulses may trigger a hardware reset, if they coincide with the latch's sample point. However, for microcontrollers with an on-chip PLL it is recommended to keep  $\overrightarrow{RSTIN}$  low for ca. 1 msec to guarantee that the PLL is locked. After the reset sequence has been completed, the  $\overrightarrow{RSTIN}$  input is sampled. When the reset input signal is active at that time the internal reset condition is prolonged until  $\overrightarrow{RSTIN}$  gets inactive.

The input RSTIN provides an internal pullup device equalling a resistor of 50 K $\Omega$  to 150 K $\Omega$  (the minimum reset time must be determined by the lowest value). Simply connecting an external capacitor is sufficient for an automatic power-on reset. RSTIN may also be connected to the output of other logic gates.

Three different kinds of external hardware resets have to be considered:

a) Power-on Reset

A complete power-on reset requires an active  $\overline{\text{RSTIN}}$  time of two reset sequences (2 \* 1024 TCL = 51.2 µsec @ 20 MHz CPU Clock) after a stable clock signal is available.

Depending on the oscillation frequency the on-chip oscillator needs about 2...50 ms to stabilize.

b) Long Hardware Reset

A long hardware reset requires an active  $\overrightarrow{\text{RSTIN}}$  time longer than the duration of the internal reset sequence. The duration of the internal reset sequence is 1024 TCL (1024 TCL = 25.6 µsec @ 20 MHz CPU Clock). The long hardware reset is also named power down wakeup reset.

c) Short Hardware Reset

The active  $\overline{\text{RSTIN}}$  time of a short hardware reset is between 4 TCL and 1024 TCL. If the RSTIN signal is active for at least 4 TCL clock cycles (100 nsec @ 20 MHz CPU Clock) the internal reset sequence is started (1024 TCL, 25.6 µsec @ 20 MHz CPU Clock). After the internal reset sequence has been completed, the RSTIN input is sampled. When the reset input is still active at that time the internal reset condition is prolonged until RSTIN gets inactive. If the RSTIN signal is active for more then 1024 TCL then the behaviour of the PORTO latch mechanism is equal to a long hardware reset.

#### 1.2 Software Reset

The reset sequence can be triggered at any time via the protected instruction SRST (Software Reset). This instruction can be executed deliberately within a program, e.g. to leave bootstrap loader mode, or upon a hardware trap that reveals a system failure.

#### 1.3 Watchdog Timer Reset

When the watchdog timer is not disabled during the initialization or serviced regularly during program execution it will overflow and trigger the reset sequence. The watchdog timer reset releases automatically a software reset. Other than a hardware reset the watchdog timer reset completes a running external bus cycle if this bus cycle either does not use READY at all, or if READY is sampled active (low) after the programmed waitstates. When READY is sampled inactive (high) after the programmed waitstates the running external bus cycle is aborted. Then the internal reset sequence is started.

Note: The watchdog timer reset cannot occur while the device is in bootstrap loader mode!

#### **1.4 Bidirectional Reset**

The bidirectional reset is a new feature and implemented since the devices and steps listed below. The steps in parentheses do only reflect a software- or watchdog timer Reset to  $\overline{\text{RSTIN}}$  but not a short hardware reset as shown in figure 7.

| C161RI     | AA             | - Step    | C161CI      | AA       | - Step   |

|------------|----------------|-----------|-------------|----------|----------|

| C164CI-8EM | AA             | - Step    | C167CS-32FM | AA       | - Step   |

| C167CR-LM  | (CA), (        | CB - Step | C167S-4RM   | (BA), Bl | B - Step |

| C167CR-4RM | (AB), <i>I</i> | AC - Step |             |          |          |

In bidirectional reset mode the device's line RSTIN (normally an input) may be driven active by the chip logic e.g. in order to support external equipment which is required for startup (e.g. flash memory).

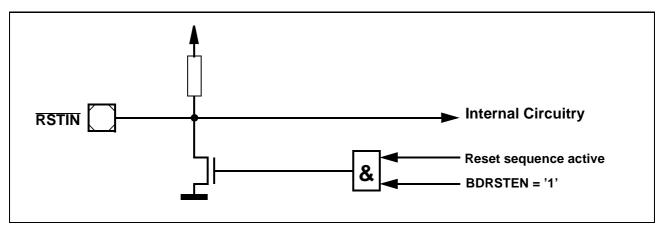

## Figure 1 : Bidirectional Reset Operation

Bidirectional reset reflects internal reset sources (software, watchdog) also to the RSTIN pin and converts short hardware reset pulses to a minimum duration of the internal reset sequence. Bidirectional reset is enabled by setting bit BDRSTEN in register SYSCON (SYSCON.3) and changes RSTIN from a pure input to an open drain IO line with an integrated pull-up resistor. When an internal reset is triggered by the SRST instruction or by a watchdog timer overflow or a low level is applied to the RSTIN line, an internal driver pulls it low for the duration of the internal reset sequence. After that it is released and is then controlled by the external circuitry alone.

The bidirectional reset function is useful in applications where external devices require a defined reset signal but cannot be connected to the device's RSTOUT signal, e.g. an external flash memory which must come out of reset and deliver code well before RSTOUT can be deactivated via EINIT.

The following behaviour differences must be observed when using the bidirectional reset feature in an application:

- Bit BDRSTEN in register SYSCON cannot be changed after EINIT.

- After a reset bit BDRSTEN is cleared (bidirectional reset is disabled).

- Bit WDTR will always be '0', even after a watchdog timer reset.

- The PORT0 configuration is treated like on a hardware reset. Especially the bootstrap loader maybe activated when P0L.4 is low.

- Pin RSTIN may only be connected to external reset devices with an open drain output driver.

### 2 System Startup Configuration

Some system features have to be selected before the first program execution is performed. These selections are made during reset via the Pins of PORT0, which are latched at the end of reset.

#### 2.1 Overview about PORT0 Configuration during Reset

PORT0 startup configuration is sampled either with the end of the internal reset sequence or with the end of the external hardware reset. If the external RSTIN signal is deactivated before the end of the internal reset sequence (short hardware reset) then an internal reset signal (IRS) of the device is used to latch the system startup configuration at PORT0, else (power-on reset or long hardware reset) PORT0 is latched after the rising edge of RSTIN with the IRS. The sampling point of PORT0 is 7 TCL (prescaler enabled) or 10 TCL (direct drive or PLL) after the rising edge of RSTIN as shown in the PORT0 sample timing (see figures below).

The duration of one internal reset sequence is 1024 TCL for initializing the internal special function registers plus 10 TCL for the jump to address  $00'0000_{H}$  after the internal reset sequence.

As already mentioned the bidirectional reset feature converts software reset, WDT reset or short hardware reset to an externally visible hardware reset with a duration of 1024 TCL. This feature is disabled after hardware reset and can be enabled via software.

| <b>X</b> :                                                            |        |       |       |       |       |             |       |         | PC         | RT    | )     |          |       |          |          |            |          |              |                    |               |

|-----------------------------------------------------------------------|--------|-------|-------|-------|-------|-------------|-------|---------|------------|-------|-------|----------|-------|----------|----------|------------|----------|--------------|--------------------|---------------|

| Pin is sampled<br>- :<br>Pin is not<br>transparent and<br>not sampled | BDRST  |       | Clock |       | Segm. | Addr. Lines | Chip  | Selects | WR Config. | Bus   | Type  | Reserved | BSL   | Reserved | Reserved | Adapt Mode | Emu Mode | Invert P0H.7 | Ext. Access Enable | (OWD disable) |

| Sample event                                                          | -      | P0H.7 | P0H.6 | P0H.5 | P0H.4 | P0H.3       | P0H.2 | P0H.1   | P0H.0      | P0L.7 | P0L.6 | P0L.5    | P0L.4 | P0L.3    | P0L.2    | POL.1      | POL.0    |              | ΕA                 | RD            |

| PONR                                                                  | OFF    | Х     | Х     | Х     | Х     | Х           | Х     | Х       | Х          | Х     | Х     | Х        | Х     | Х        | Х        | Х          | Х        | Х            | Х                  | Х             |

| LHWR                                                                  | ON/OFF | Х     | Х     | Х     | Х     | Х           | Х     | Х       | Х          | Х     | Х     | Х        | Х     | Х        | Х        | Х          | Х        | Х            | Х                  | Х             |

| SHWR                                                                  | OFF    | -     | I     | I     | Х     | Х           | Х     | Х       | Х          | Х     | Х     | Х        | Х     | Х        | Х        | Х          | Х        | -            | Х                  | Х             |

| WDTR/SWR                                                              | OFF    | -     | -     | -     | Х     | Х           | Х     | Х       | Х          | Х     | Х     | -        | -     | -        | -        | -          | -        | -            | Х                  | Х             |

| SHWR                                                                  | ON     | Х     | Х     | Х     | Х     | Х           | Х     | Х       | Х          | Х     | Х     | Х        | Х     | Х        | Х        | Х          | Х        | Х            | Х                  | Х             |

| WDTR/SWR                                                              | ON     | Х     | Х     | Х     | Х     | Х           | Х     | Х       | Х          | Х     | Х     | Х        | Х     | Х        | Х        | Х          | Х        | Х            | Х                  | Х             |

#### Table 2:

System Startup Configuration via PORT0

## 2.2 PORT0 Sample Timing for the different Reset Types

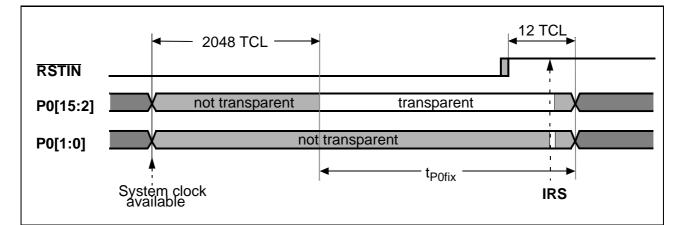

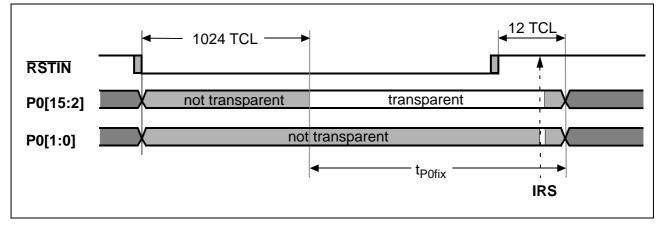

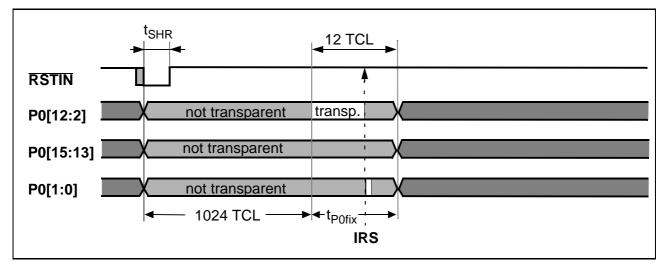

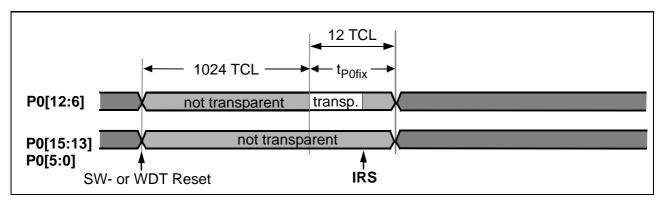

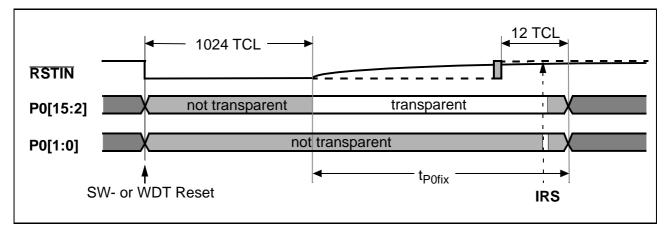

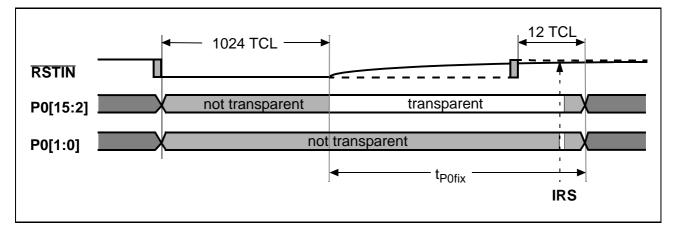

The different reset sources and timing relations at PORT0 during and at the end of reset are shown below. If a reset event occurs then PORT0 is switched to input mode and the internal pull-ups are active. During that time it is possible that the desired input voltage levels at PORT0 ( $V_{IH}$  and  $V_{IL}$  forced by the internal/external pull-ups and pull-downs for the startup configuration) are not reached. Therefore PORT0 is **not** transparent for 1024TCL (power-on reset for 2048 TCL) to prevent unexpected behaviour to the system. After that time a part of PORT0 becomes transparent and at the end of reset these pins are sampled with the IRS signal.

Depending on the reset type some PORT0 pins are not transparent, e.g. P0L.1 and P0L.0 which control Adapt Mode and Emulation Mode. Noise on these lines during reset would force the microcontroller to Adapt Mode or Emulation Mode. Therefore both pins are not transparent until the sample point IRS at the end of the reset condition.

The PORT0 sample timings shown below are based on the following conditions:

- t<sub>P0fix</sub>: During t<sub>P0fix</sub> PORT0 has to be constant so the System Startup Configuration is latched correctly.

- $t_{SHR}$ : Duration of a short hardware reset. 4 TCL <  $t_{SHR} \le 1024$  TCL

- IRS: Internal Reset Signal: Sampling point of PORT0 configuration bits is 7 TCL (prescaler enabled) or 10 TCL (direct drive or PLL) after the rising edge of RSTIN or after the end of the internal reset sequence.

- TCL: 1 TCL = 1 / (2  $f_{CPU}$ ), 1 TCL = 25 nsec @ 20 MHz CPU Clock

Figure 2 : PORT0 sample Timing: Power-on Reset

#### Figure 3 :

PORT0 sample Timing: Long Hardware Reset, Bidirectional Reset enabled or disabled

### Figure 4 :

PORT0 sample Timing: Short Hardware Reset, Bidirectional Reset disabled

#### Figure 5 :

PORT0 sample Timing: Software Reset or WDT Reset, Bidirectional Reset disabled

Figure 7 : PORT0 sample Timing: Short Hardware Reset, Bidirectional Reset <u>enabled</u>

## 3 Calculation of the Pull-up/down Resistors at PORT0 for Startup Configuration

The specification in the Data Sheet includes the values of the PORT0 configuration currents  $I_{P0L}$  and  $I_{P0H}$ .

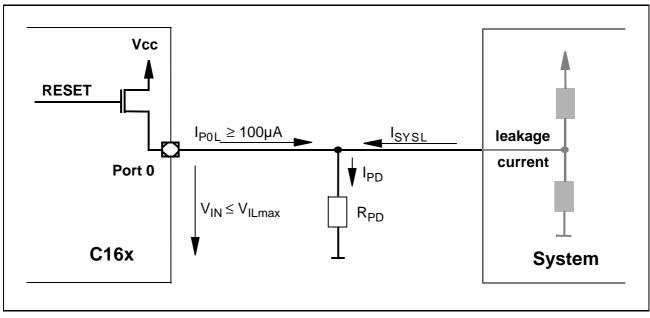

#### 3.1 Pull-down Calculation

$I_{P0L}$  is the base for the calculation of the Pull-down resistors for PORT0 startup configuration.  $I_{P0Lmin} = -100 \ \mu A \ @ V_{IN} = V_{ILmax}$ . That means that the port configuration current has to be more or equal than 100  $\mu A$  to get an input voltage  $V_{IN}$  lower or equal to  $V_{ILmax}$ . The system current  $I_{SYSL}$  has a direct influence on the value of the needed pull-down resistor. The relation between the different parameters and the calculation with an example are shown below.

Note: All currents flowing into the microcontroller are defined as positive and all currents flowing out of it are defined as negative. Because of the internal pull-up transistor the direction of  $I_{POL}$  and  $I_{POH}$  is out of the device and therefore the sign in the current specification is negative.

## Figure 8 : System Environment and Pull-down Resistor for Startup

### **Current Specification in the Data Sheet:**

| Vcc                 | $= 5V \pm 10\%$                      | $\Rightarrow$ | $4.5V \leq Vcc \leq 5.5V$       |

|---------------------|--------------------------------------|---------------|---------------------------------|

| V <sub>ILma</sub> , | $_{\rm c} = 0.2 \rm Vcc - 0.1 \rm V$ | $\Rightarrow$ | $0.8V \leq V_{ILmax} \leq 1.0V$ |

| I <sub>P0Lmin</sub> | _ = -100μA                           | $\Rightarrow$ | I <sub>P0L</sub> ≥  -100µA      |

| Pull-down resistor calculation:                                     | $R_{PD} < \frac{V_{ILmax}}{I_{PD}} = \frac{V_{ILmax}}{I_{P0L} + I_{SYSL}}$ |

|---------------------------------------------------------------------|----------------------------------------------------------------------------|

| Example <b>without</b> system current:<br>(I <sub>SYSL</sub> = 0 A) | $R_{PD} < \frac{V_{ILmax}}{I_{PD}} = \frac{0.8 V}{100 \mu A}$              |

| The recommended maximum value:                                      | $R_{PD} = 8 k\Omega$                                                       |

## 3.2 Pull-up Calculation

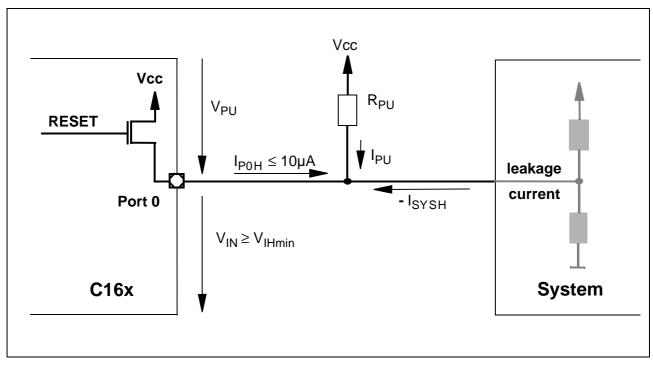

$I_{P0H}$  is the base for the calculation of the pull-up resistors for PORT0 startup configuration.  $I_{P0Hmax} = -10 \ \mu A @ V_{IN} = V_{IHmin}$ . As already mentioned PORT0 supplies internal pull-up resistors which are only active during Reset, or during Hold-or Adapt-mode. For normal systems this internal pull-up resistors are sufficient to reach the input high voltages at the PORT0 pins. This situation changes when the system current  $I_{SYSH}$  exceeds 10  $\mu$ A. Then additional external pull-up resistors are mandatory. For example system flash memory with a high leakage current can cause an increased  $I_{SYSH}$ . The calculation and an example are shown below.

#### Figure 9 : System Environment and Pull-up Resistor for Startup

## **Current Specification in the Data Sheet:**

| Vcc                 | = 5 V $\pm$ 10 %  | $\Rightarrow$ | 4.5 V $\leq$       | Vcc                | $\leq$ 5.5 V |

|---------------------|-------------------|---------------|--------------------|--------------------|--------------|

| V <sub>IHmin</sub>  | = 0.2 Vcc + 0.9 V | $\Rightarrow$ | $1.8 V \leq$       | V <sub>IHmin</sub> | $\leq$ 2.0 V |

| I <sub>P0Hmax</sub> | = -10 µA          | $\Rightarrow$ | I <sub>P0H</sub> ≤ | -10 µA             |              |

Pull-up resistor calculation:

$$R_{PU} < \frac{V_{PU}}{I_{PU}} = \frac{V_{CCmin} - V_{IHmin}}{I_{SYSH} - I_{P0H}}$$

Example:  $I_{SYSH} = 50 \mu A$ :

$$R_{PU} < \frac{4.5 \text{ V} - 1.8 \text{ V}}{50 \mu \text{A} - 10 \mu \text{A}} = 67.5 \text{ k}\Omega$$

The recommended maximum value:  $R_{P\,U}$  = 67.5  $k\Omega$

## 4 Appendix

## A PORT0 Configuration during Reset

| _H.7 | H.6  | H.5 | H.4 | H.3 | H.2 | H.1 | H.0 | L.7 | L.6 | L.5 | L.4 | L.3 | L.2 | _L.1 | L.0 |

|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|-----|

| C    | LKCF | G   | SAL | SEL | CSS | SEL | WRC | BUS | ТҮР |     | SM  | OD  | I   | ADP  | EMU |

|      |      |     |     |     |     |     |     |     |     |     |     |     |     |      |     |

| Pin               | Mode                                           | Comment                                               |

|-------------------|------------------------------------------------|-------------------------------------------------------|

| EMU               | Emulation Mode                                 | Condition for EHM and<br>Quality of P0H.7 is inverted |

| ADP               | Adapt Mode                                     |                                                       |

| SMOD<br>(P0L.5:2) | Special Modes                                  |                                                       |

| 0000              | Reserved                                       | Do not use this combination                           |

| 0001              | Reserved                                       | Do not use this combination                           |

| 0010              | Reserved                                       | Do not use this combination                           |

| 0011              | Reserved                                       | Do not use this combination                           |

| 0100              | Reserved                                       | Do not use this combination                           |

| 0101              | Reserved                                       | Do not use this combination                           |

| 0110              | Reserved                                       | Do not use this combination                           |

| 0111              | External Host Mode (EHM) <sup>1)</sup>         | <b>Requires Emulation Mode</b>                        |

| 1000              | Reserved                                       | Do not use this combination                           |

| 1001              | Reserved                                       | Do not use this combination                           |

| 1010              | Bootstrap Loader + CPU Host Mode <sup>1)</sup> | Serial OTP programming via BSL                        |

| 1011              | Bootstrap Loader                               | Start from internal boot ROM                          |

| 1100              | Reserved                                       | Do not use this combination                           |

| 1101              | Reserved                                       | Do not use this combination                           |

| 1110              | CPU Host Mode (CHM) <sup>1)</sup>              | CPU programming mode for OTP                          |

| 1111              | Normal Start                                   | Normal start as defined by $\overline{EA}$ pin        |

| BUSTYP<br>(P0L.7:6) | External Data Bus Width                                | External Address Bus Mode               |

|---------------------|--------------------------------------------------------|-----------------------------------------|

| 0 0                 | 8-bit Data                                             | Demultiplexed Addresses                 |

| 0 1                 | 8-bit Data                                             | Multiplexed Addresses                   |

| 10                  | 16-bit Data                                            | Demultiplexed Addresses                 |

| 11                  | 16-bit Data                                            | Multiplexed Addresses                   |

| WRC                 | Write Configuration                                    |                                         |

| CSSEL<br>(P0H.2:1)  | Chip Select Lines                                      |                                         |

| 11                  | Max: CSxCS0                                            | Default without pull-downs              |

| 10                  | None                                                   | Port 6 pins free for IO                 |

| 0 1                 | Two: CS1CS0                                            |                                         |

| 0 0                 | Three: CS2CS0                                          |                                         |

| SALSEL<br>(P0H.4:3) | Segment Address Lines                                  | Directly accessible Address Space       |

| 11                  | Two: A17A16                                            | 256 KByte (Default, without pull-downs) |

| 10                  | AxxA16                                                 | (Maximum)                               |

| 0 1                 | None                                                   | 64 KByte (Minimum)                      |

| 0 0                 | Four: A19A16                                           | 1 MByte                                 |

| CLKCFG<br>(P0H.7-5) | CPU Frequency f <sub>CPU</sub> = f <sub>XTAL</sub> * F | Notes <sup>2)</sup>                     |

| 111                 | f <sub>XTAL</sub> * 4                                  | Default configuration                   |

| 110                 | f <sub>XTAL</sub> * 3                                  |                                         |

| 101                 | f <sub>XTAL</sub> * 2                                  |                                         |

| 100                 | f <sub>XTAL</sub> * 5                                  |                                         |

| 011                 | f <sub>XTAL</sub> * 1                                  | Direct drive                            |

| 010                 | f <sub>XTAL</sub> * 1.5                                |                                         |

| 001                 | f <sub>XTAL</sub> / 2                                  | Prescaler                               |

| 000                 | f <sub>xtal</sub> * 2.5                                |                                         |

<sup>1)</sup> This modes are only valid for C161CI, C164CI and C167CS

<sup>2)</sup> The clock configuration bits are not fully decoded in all devices and steps. Please use Appendix B and the User's Manuals for detailed information.

## B Clock Options and Steps

| Device            | Step <sup>1)</sup> | OWD <sup>2)</sup>    | PM <sup>3)</sup> | Clock Options <sup>4)</sup> | PLL Factors (F) |

|-------------------|--------------------|----------------------|------------------|-----------------------------|-----------------|

| SAx-C161V / K / O | AA                 | =                    | no               | 0.5 / 1                     | no              |

| SAx-C161RI        | AA, BA, BB         | ==                   | yes              | 0.5 / 1                     | no              |

| SAx-C161SI / CI   | AA                 | RD                   | yes              | 0.5 / 1 / PLL               | 1.5/2/2.5/3/4/5 |

| SAx-C163          | AA, AB, BA, BB     | V <sub>PP</sub> /OWE | no               | 0.5 / 1 / PLL               | 1.5/2/2.5/3/4/5 |

| SAx-C163-16F      | AA, AB             | V <sub>PP</sub> /OWE | no               | 0.5 / 1 / PLL               | 1.5/2/2.5/3/4/5 |

| SAx-C163-16F x    | BA, BB             | ==                   | no               | 0.5 / 1 / PLL               | 1.5/2/2.5/3/4/5 |

| SAx-C164CI        | AA                 | RD                   | yes              | 0.5 / 1 / PLL               | 1.5/2/2.5/3/4/5 |

| SAx-C165          | BB                 | ==                   | no               | 0.5                         | no              |

| SAx-C165          | CA                 | ==                   | no               | 0.5 / 1                     | no              |

| SAx-C167-LM       | BA, BB, CA, CB, BE | ==                   | no               | 0.5                         | no              |

| SAx-C167SR-LM     | AB                 | ==                   | no               | 1 / PLL                     | 4               |

| SAx-C167SR-LM     | BA                 | ==                   | no               | 1 / PLL                     | 2/3/4/5         |

| SAx-C167SR-LM     |                    | ==                   | no               | 0.5 / 1 / PLL               | 1.5/2/2.5/3/4/5 |

| SAx-C167CR-LM     | AB                 | ==                   | no               | 1 / PLL                     | 4               |

| SAx-C167CR-LM     | BA, BB, CA, CB, BE | ==                   | no               | 1 / PLL                     | 2/3/4/5         |

| SAx-C167S-4RM     | AA,BA, BB          | V <sub>PP</sub>      | no               | 1 / PLL                     | 2/3/4/5         |

| SAx-C167CR-4RM    | AA, AB, AC         | V <sub>PP</sub>      | no               | 0.5 / 1 / PLL               | 1.5/2/2.5/3/4/5 |

| SAx-C167CR-16RM   | AA                 | ==                   | no               | 1 / PLL                     | 2/3/4/5         |

| SAx-C167CR-16FM   | AC                 | ==                   | no               | 1 / PLL                     | 4               |

| SAx-C167CS-32FM   | AA                 | RD                   | yes              | 0.5 / 1 / PLL               | 1.5/2/2.5/3/4/5 |

<sup>1)</sup> The described options are implemented since the steps listed below.

<sup>2)</sup> The Oscillator Watchdog (OWD) can be disabled in different kinds.

| ==                   | : No OWD implemented.                                                                                                                                                     |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>PP</sub> /OWE | : A low level on pin V <sub>PP</sub> /OWE disables the OWD.                                                                                                               |

| RD                   | : A low level on pin $\overline{RD}$ at the end of any type of reset disables the OWD.<br>The level of $\overline{RD}$ is latched with the IRS. See figure 2 to figure 7. |

| V <sub>PP</sub>      | : A low level on pin V <sub>PP</sub> disables the OWD.                                                                                                                    |

<sup>3)</sup> Besides other features the Power Management (PM) includes the Slow Down Devider. A separate clock path can be selected for Slow Down operation bypassing the basic clock path used for standard operation. The programmable Slow Down Devider devides the oscillator frequency by a factor of 1 ... 32.

| <sup>4)</sup> Prescaler option | : 0.5                       |                              |

|--------------------------------|-----------------------------|------------------------------|

| Direct drive option            | : 1                         |                              |

| The PLL clock is not           | $(f_{CPU} = f_{OSC} * 0.5)$ |                              |

| and direct drive optic         | on                          | $(f_{CPU} = f_{OSC} * 1.0).$ |