# Intel386<sup>™</sup> EX Embedded Microprocessor

### Datasheet

### **Product Features**

- Static Intel386<sup>TM</sup> CPU Core —Low Power Consumption

- -Operating Power Supply EXTB: 2.7 V to 3.6 V

- EXTC: 4.5 V to 5.5 V — Operating Frequency 20 MHz EXTB at 2.7 V to 3.6 V 25 MHz EXTB at 3.0 V to 3.6 V; 25/33 MHz EXTC at 4.5 V to 5.5 V

- Transparent Power-management System Architecture

- Intel System Management Mode Architecture Extension for Truly Compatible Systems

- Power Management Transparent to Operating Systems and Application Programs

- Programmable Power-management Modes

- Powerdown Mode

- —Clock Stopping at Any Time

- —Only 10–20 μA Typical CPU Sink Current

- Full 32-bit Internal Architecture

8-, 16-, 32-bit Data Types

8 General Purpose 32-bit Registers

- Runs Intel386 Architecture Software in a Cost-effective 16-bit Hardware Environment

- Runs Same Applications and Operating Systems as the Intel386 SX and Intel386 DX Processors

- Object Code Compatible with 8086, 80186, 80286, and Intel386 Processors

- High-performance 16-bit Data Bus — Two-clock Bus Cycles

- Address Pipelining Allows Use of Slower, Inexpensive Memories

- Extended Temperature Range

- Integrated Memory Management Unit — Virtual Memory Support

- -Optional On-chip Paging

- -4 Levels of Hardware-enforced Protection

- MMU Fully Compatible with MMUs of the 80286 and Intel386 DX Processors

- Virtual 8086 Mode Allows Execution of 8086 Software in a Protected and Paged System

- Large Uniform Address Space

64 Megabyte Physical

64 Terrebute Virtual

- —64 Terabyte Virtual

- -4 Gigabyte Maximum Segment Size

- On-chip Debugging Support Including Breakpoint Registers

- Complete System Development Support

- High Speed CHMOS Technology

- Two Package Types

132-pin Plastic Quad Flatpack

144-pin Thin Quad Flatpack

- Integrated Peripheral Functions

Clock and Power Management Unit

- -Chip-select Unit

- -Interrupt Control Unit

- —Timer/Counter Unit

- -Watchdog Timer Unit

- -Asynchronous Serial I/O Unit

- -Synchronous Serial I/O Unit

- —Parallel I/O Unit

- —DMA and Bus Arbiter Unit

- —Refresh Control Unit

- -JTAG-compliant Test-logic Unit

This datasheet applies to devices marked EXTB and EXTC. If you require information about devices marked EXSA or EXTA, refer to a previous revision of this datasheet, order number 272420-004.

Order Number: 272420-007 October 1998

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel386<sup>TM</sup> EX Microprocessor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1998

\*Third-party brands and names are the property of their respective owners.

# intel. Contents

| 1.0 | Introduction                                                                |                                                                                                                                                                                                                                                                                                       |                                                                |  |  |  |  |

|-----|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| 2.0 | Pin Assignment                                                              |                                                                                                                                                                                                                                                                                                       |                                                                |  |  |  |  |

| 3.0 | Pin [                                                                       | Description                                                                                                                                                                                                                                                                                           | 12                                                             |  |  |  |  |

| 4.0 | Fund                                                                        | tional Description                                                                                                                                                                                                                                                                                    |                                                                |  |  |  |  |

|     | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11 | Clock Generation and Power Management Unit<br>Chip-select Unit<br>Interrupt Control Unit<br>Timer/Counter Unit<br>Watchdog Timer Unit<br>Asynchronous Serial I/O Unit<br>Synchronous Serial I/O Unit<br>Parallel I/O Unit<br>DMA and Bus Arbiter Unit<br>Refresh Control Unit<br>JTAG Test-logic Unit | 19<br>19<br>20<br>20<br>20<br>20<br>21<br>21<br>21<br>21<br>22 |  |  |  |  |

| 5.0 | <b>Desi</b><br>5.1<br>5.2<br>5.3                                            | gn Considerations<br>Instruction Set<br>Component and Revision Identifiers<br>Package Thermal Specifications                                                                                                                                                                                          | 23<br>24                                                       |  |  |  |  |

| 6.0 | <b>Elect</b><br>6.1<br>6.2<br>6.3                                           | trical Specifications<br>Maximum Ratings<br>DC Specifications<br>AC Specifications                                                                                                                                                                                                                    | 27<br>                                                         |  |  |  |  |

| 7.0 | Bus                                                                         | Cycle Waveforms                                                                                                                                                                                                                                                                                       | 47                                                             |  |  |  |  |

# **Figures**

| Intel386™ EX Embedded Processor Block Diagram                                                             | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intel386™ EX Embedded Processor 132-Pin PQFP Pin Assignment                                               | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Intel386™ EX Embedded Processor 144-Pin TQFP Pin Assignment                                               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

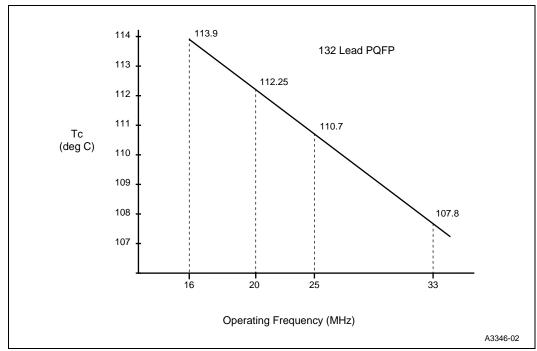

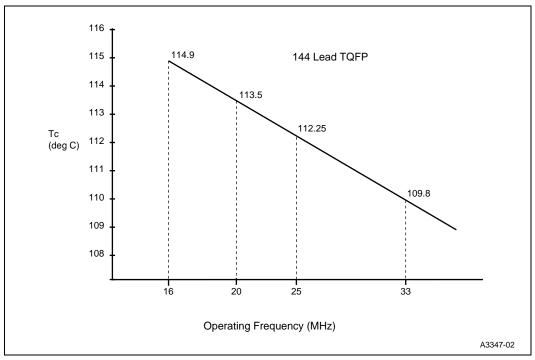

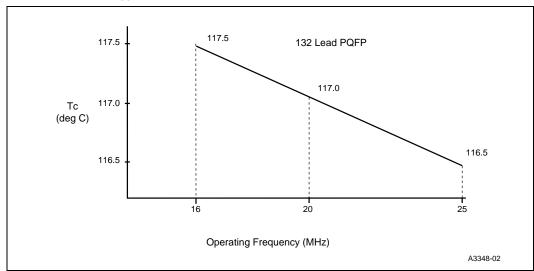

| Maximum Case Temperature vs. Frequency for Typical Power Values (132-lead PQFP, $V_{cc}$ = 5.5 V)         | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Maximum Case Temperature vs. Frequency for Typical Power Values (144-lead TQFP, $V_{cc}$ = 5.5 V nominal) | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

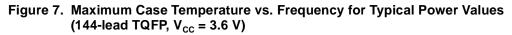

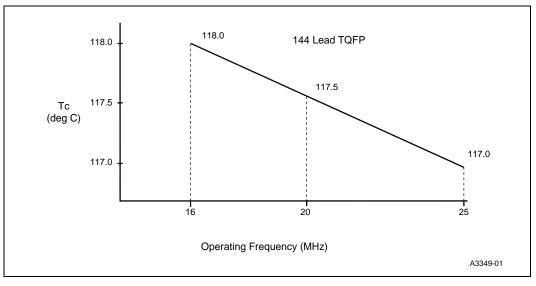

| Maximum Case Temperature vs. Frequency for Typical Power Values (132-lead PQFP, $V_{cc}$ = 3.6 V)         | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Maximum Case Temperature vs. Frequency for Typical Power Values (144-lead TQFP, $V_{cc}$ = 3.6 V)         | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

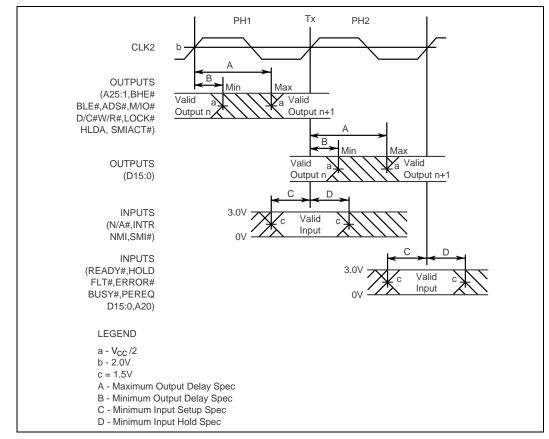

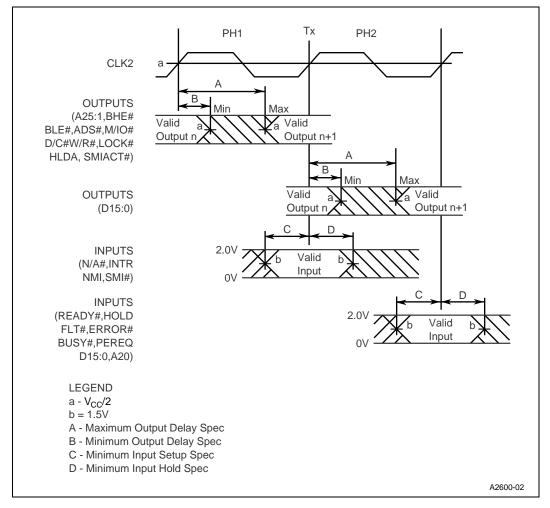

| Drive Levels and Measurement Points for AC Specifications (EXTC)                                          | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Drive Levels and Measurement Points for AC Specifications (EXTB)                                          | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

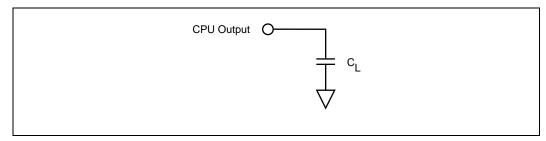

| AC Test Loads                                                                                             | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                           | Intel386 <sup>™</sup> EX Embedded Processor 132-Pin PQFP Pin Assignment<br>Intel386 <sup>™</sup> EX Embedded Processor 144-Pin TQFP Pin Assignment<br>Maximum Case Temperature vs. Frequency for Typical Power Values<br>(132-lead PQFP, V <sub>cc</sub> = 5.5 V)<br>Maximum Case Temperature vs. Frequency for Typical Power Values<br>(144-lead TQFP, V <sub>cc</sub> = 5.5 V nominal)<br>Maximum Case Temperature vs. Frequency for Typical Power Values<br>(132-lead PQFP, V <sub>cc</sub> = 3.6 V)<br>Maximum Case Temperature vs. Frequency for Typical Power Values<br>(132-lead PQFP, V <sub>cc</sub> = 3.6 V)<br>Maximum Case Temperature vs. Frequency for Typical Power Values<br>(144-lead TQFP, V <sub>cc</sub> = 3.6 V)<br>Drive Levels and Measurement Points for AC Specifications (EXTC)<br>Drive Levels and Measurement Points for AC Specifications (EXTB) |

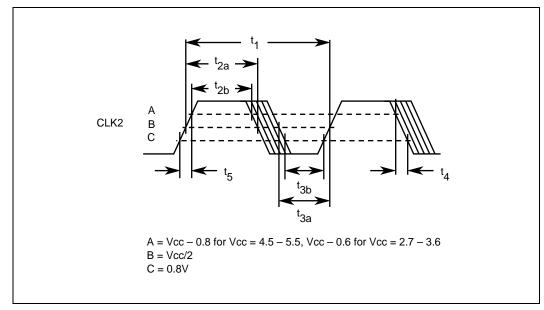

| 11 | CLK2 Waveform                                                        | .42  |

|----|----------------------------------------------------------------------|------|

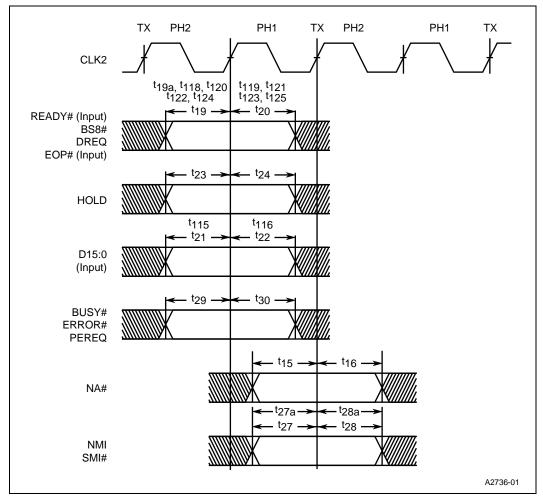

| 12 | AC Timing Waveforms — Input Setup and Hold Timing                    | 43   |

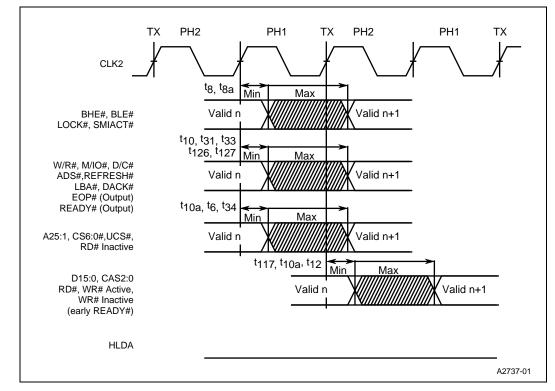

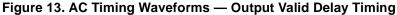

| 13 | AC Timing Waveforms — Output Valid Delay Timing                      | 44   |

| 14 | AC Timing Waveforms — Output Valid Delay Timing for                  |      |

|    | External Late READY#                                                 |      |

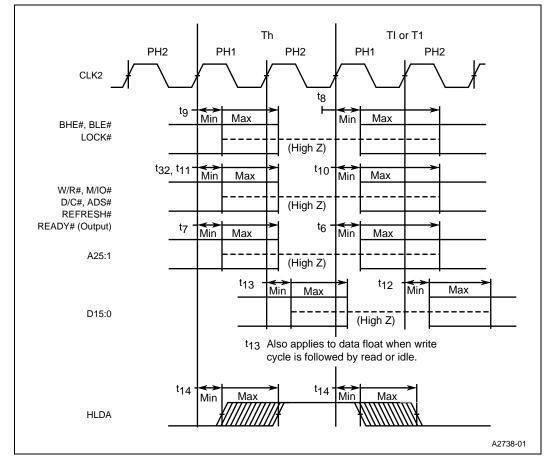

| 15 | AC Timing Waveforms — Output Float Delay and HLDA Valid Delay Timing |      |

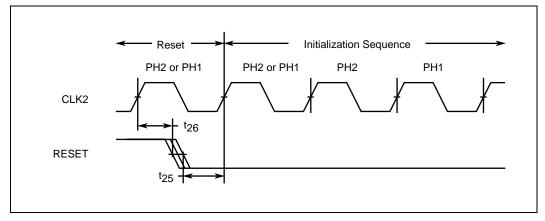

| 16 | AC Timing Waveforms — RESET Setup and Hold Timing and Internal Phase | .45  |

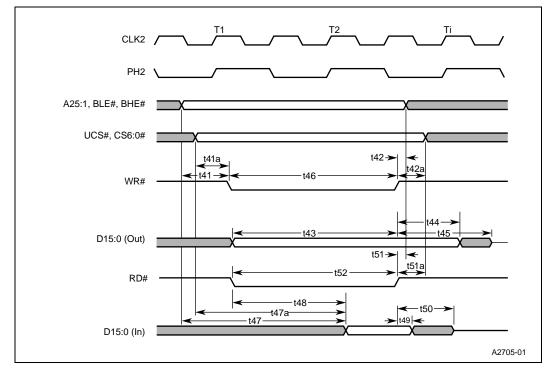

| 17 | AC Timing Waveforms — Relative Signal Timing                         | . 46 |

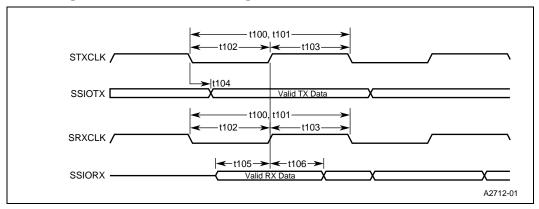

| 18 | AC Timing Waveforms — SSIO Timing                                    | 46   |

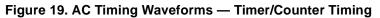

| 19 | AC Timing Waveforms — Timer/Counter Timing                           | 46   |

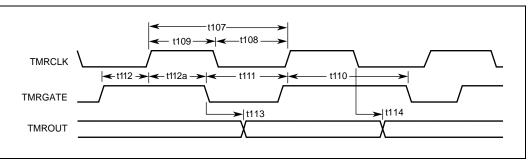

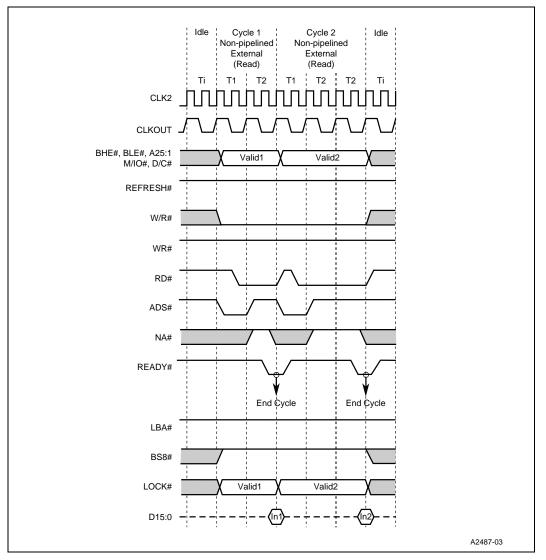

| 20 | Basic Internal and External Bus Cycles                               | .47  |

| 21 | Nonpipelined Address Read Cycles                                     |      |

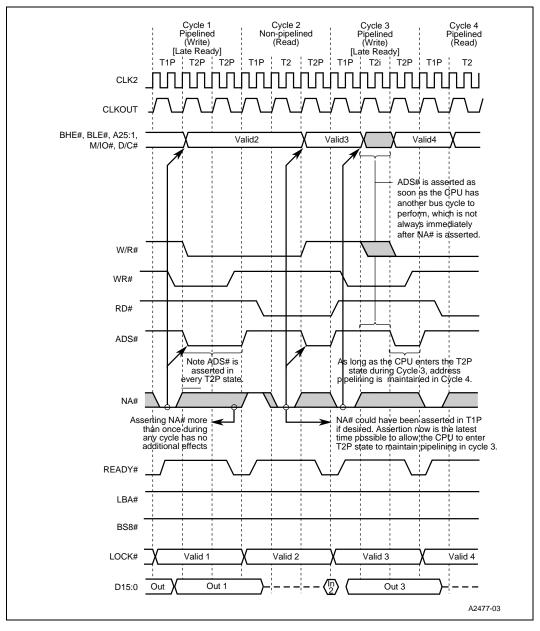

| 22 | Pipelined Address Cycle                                              | 49   |

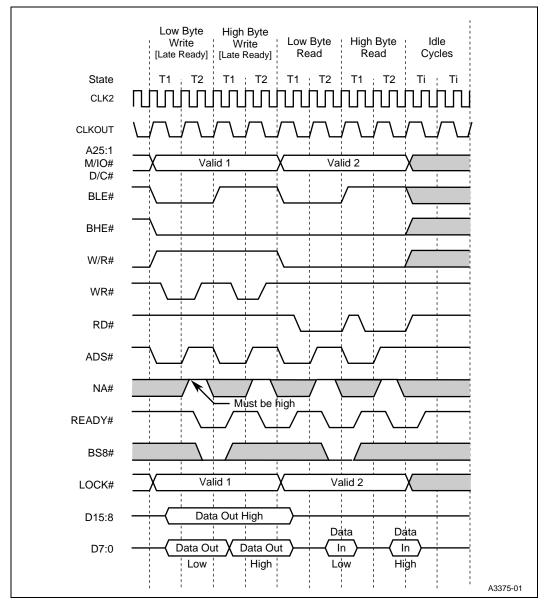

| 23 | 16-bit Cycles to 8-bit Devices (using BS8#)                          | 50   |

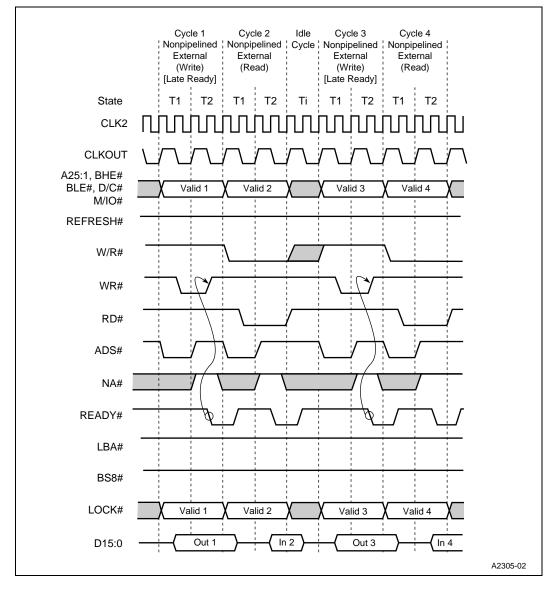

| 24 | Basic External Bus Cycles                                            | .51  |

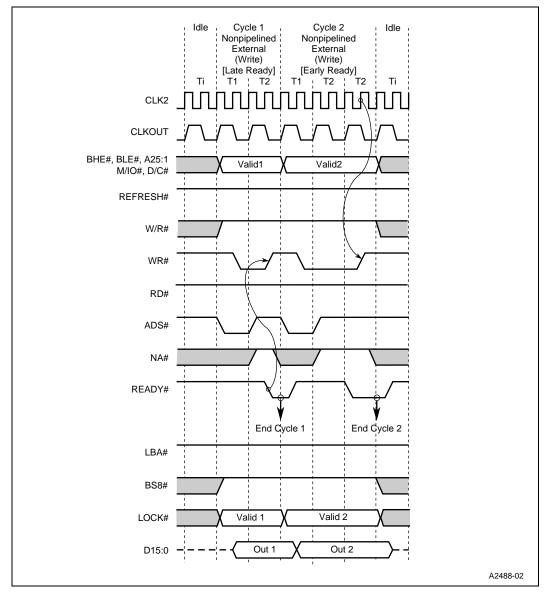

| 25 | Nonpipelined Address Write Cycles                                    | 52   |

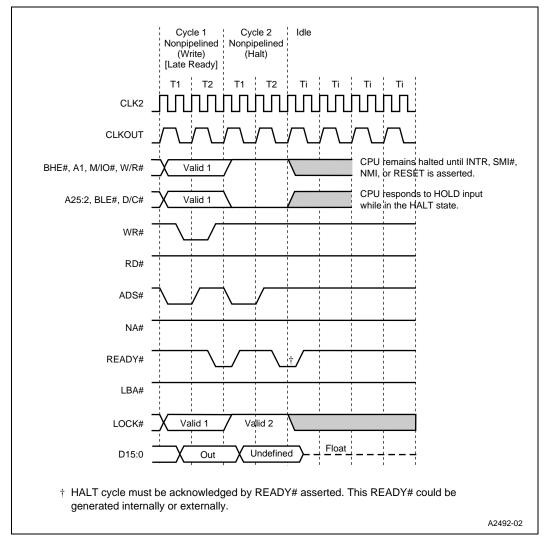

| 26 | Halt Cycle                                                           | .53  |

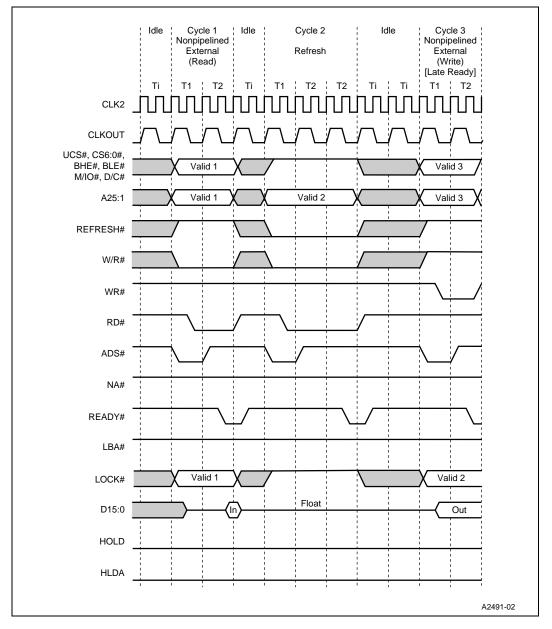

| 27 | Basic Refresh Cycle                                                  | .54  |

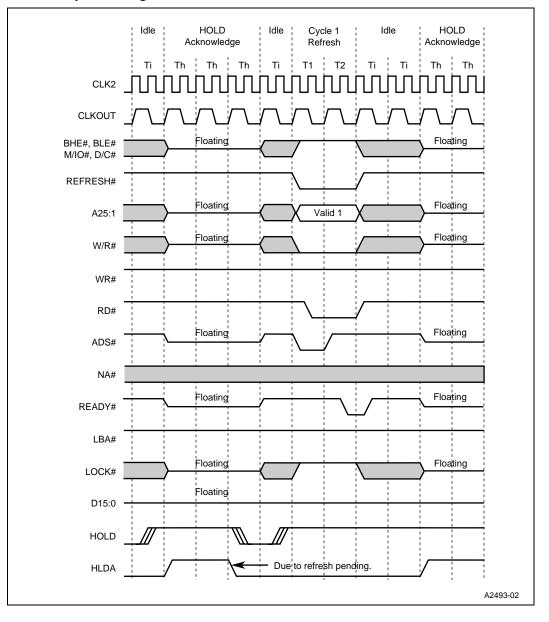

| 28 | Refresh Cycle During HOLD/HLDA                                       | 55   |

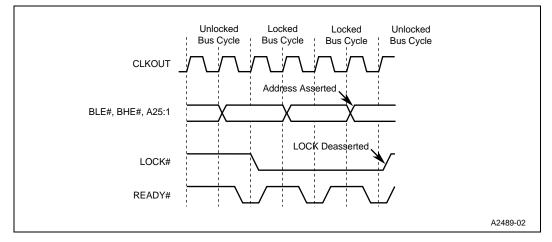

| 29 | LOCK# Signal During Address Pipelining                               | 56   |

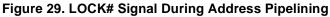

| 30 | Interrupt Acknowledge Cycles                                         | 56   |

|    |                                                                      |      |

## Tables

| 1  | 132-Pin PQFP Pin Assignment                                   | 9  |

|----|---------------------------------------------------------------|----|

| 2  | 144-Pin TQFP Pin Assignment                                   |    |

| 3  | Pin Type and Output State Nomenclature                        |    |

| 4  | Intel386 <sup>™</sup> EX Microprocessor Pin Descriptions      |    |

| 5  | Microprocessor Clocks Per Instruction                         | 23 |

| 6  | Thermal Resistances (0°C/W) θ <sub>JA</sub> , θ <sub>JC</sub> | 24 |

| 7  | 5 V Intel386 EXTC Processor Maximum Ratings                   | 27 |

| 8  | 3 V Intel386 EXTB Processor Maximum Ratings                   | 27 |

| 9  | 5-Volt DC Characteristics                                     |    |

| 10 | 3-Volt DC Characteristics                                     |    |

| 11 | 5-Volt AC Characteristics                                     |    |

| 12 | 3-Volt AC Characteristics                                     |    |

|    |                                                               |    |

# **Revision History**

This datasheet applies to devices marked EXTB and EXTC. If you require information about devices marked EXSA or EXTA, refer to a previous revision of this datasheet, order number 272420-004.

| Revision | Date  | Description                                                                                                                                |  |

|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| 007      | 10/98 | The document was updated to the larger page size. All known device errata for the datasheet have been incorporated into this new revision. |  |

| 006      | 5/96  | Corrections added.                                                                                                                         |  |

| 005      | 12/95 | This datasheet applied to the new EXTB and EXTC devices.                                                                                   |  |

| 004      | 9/94  | This datasheet applied to devices marked EXSA or EXTA.                                                                                     |  |

### 1.0 Introduction

The Intel386<sup>™</sup> EXTB embedded processor operates at 20 or 25 MHz at 3 Volts nominal. The Intel386 EXTC embedded processor operates at 25 or 33 MHz at 5 Volts. In this datasheet, "Intel386 EX processor" refers to both the Intel386 EXTB and EXTC processors.

The Intel386 EX embedded processor is a highly integrated, 32-bit, fully static processor optimized for embedded control applications. With a 16-bit external data bus, a 26-bit external address bus, and Intel's System Management Mode (SMM), the Intel386 EX microprocessor brings the vast software library of Intel386 architecture to embedded systems. It provides the performance benefits of 32-bit programming with the cost savings associated with 16-bit hardware systems.

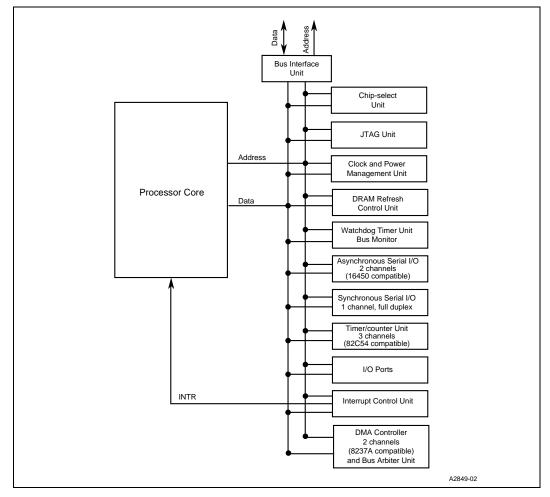

Figure 1. Intel386™ EX Embedded Processor Block Diagram

### 2.0 Pin Assignment

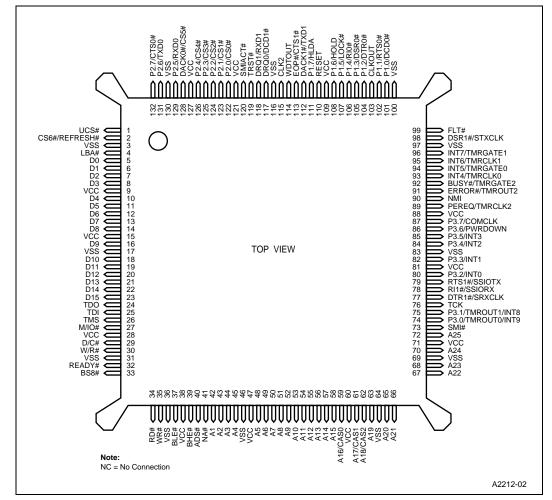

Figure 2. Intel386™ EX Embedded Processor 132-Pin PQFP Pin Assignment

#### Table 1. 132-Pin PQFP Pin Assignment

| Pin | Symbol          | Pin | Symbol          | Pin | Symbol            | Pin | Symbol          |

|-----|-----------------|-----|-----------------|-----|-------------------|-----|-----------------|

| 1   | UCS#            | 34  | RD#             | 67  | A22               | 100 | V <sub>SS</sub> |

| 2   | CS6#/REFRESH#   | 35  | WR#             | 68  | A23               | 101 | P1.0/DCD0#      |

| 3   | V <sub>SS</sub> | 36  | V <sub>ss</sub> | 69  | V <sub>ss</sub>   | 102 | P1.1/RTS0#      |

| 4   | LBA#            | 37  | BLE#            | 70  | A24               | 103 | CLKOUT          |

| 5   | D0              | 38  | V <sub>cc</sub> | 71  | V <sub>cc</sub>   | 104 | P1.2/DTR0#      |

| 6   | D1              | 39  | BHE#            | 72  | A25               | 105 | P1.3/DSR0#      |

| 7   | D2              | 40  | ADS#            | 73  | SMI#              | 106 | P1.4/RI0#       |

| 8   | D3              | 41  | NA#             | 74  | P3.0/TMROUT0/INT9 | 107 | P1.5/LOCK#      |

| 9   | V <sub>cc</sub> | 42  | A1              | 75  | P3.1/TMROUT1/INT8 | 108 | P1.6/HOLD       |

| 10  | D4              | 43  | A2              | 76  | ТСК               | 109 | V <sub>cc</sub> |

| 11  | D5              | 44  | A3              | 77  | DTR1#/SRXCLK      | 110 | RESET           |

| 12  | D6              | 45  | A4              | 78  | RI1#/SSIORX       | 111 | P1.7/HLDA       |

| 13  | D7              | 46  | V <sub>ss</sub> | 79  | RTS1#/SSIOTX      | 112 | DACK1#/TXD1     |

| 14  | D8              | 47  | V <sub>cc</sub> | 80  | P3.2/INT0         | 113 | EOP#/CTS1#      |

| 15  | V <sub>cc</sub> | 48  | A5              | 81  | V <sub>cc</sub>   | 114 | WDTOUT          |

| 16  | D9              | 49  | A6              | 82  | P3.3/INT1         | 115 | CLK2            |

| 17  | V <sub>ss</sub> | 50  | A7              | 83  | V <sub>SS</sub>   | 116 | V <sub>SS</sub> |

| 18  | D10             | 51  | A8              | 84  | P3.4/INT2         | 117 | DRQ0/DCD1#      |

| 19  | D11             | 52  | A9              | 85  | P3.5/INT3         | 118 | DRQ1/RXD1       |

| 20  | D12             | 53  | A10             | 86  | P3.6/PWRDOWN      | 119 | TRST#           |

| 21  | D13             | 54  | A11             | 87  | P3.7/COMCLK       | 120 | SMIACT#         |

| 22  | D14             | 55  | A12             | 88  | V <sub>cc</sub>   | 121 | V <sub>cc</sub> |

| 23  | D15             | 56  | A13             | 89  | PEREQ/TMRCLK2     | 122 | P2.0/CS0#       |

| 24  | TDO             | 57  | A14             | 90  | NMI               | 123 | P2.1/CS1#       |

| 25  | TDI             | 58  | A15             | 91  | ERROR#/TMROUT2    | 124 | P2.2/CS2#       |

| 26  | TMS             | 59  | A16/CAS0        | 92  | BUSY#/TMRGATE2    | 125 | P2.3/CS3#       |

| 27  | M/IO#           | 60  | V <sub>cc</sub> | 93  | INT4/TMRCLK0      | 126 | P2.4/CS4#       |

| 28  | V <sub>cc</sub> | 61  | A17/CAS1        | 94  | INT5/TMRGATE0     | 127 | V <sub>cc</sub> |

| 29  | D/C#            | 62  | A18/CAS2        | 95  | INT6/TMRCLK1      | 128 | DACK0#/CS5#     |

| 30  | W/R#            | 63  | A19             | 96  | INT7/TMRGATE1     | 129 | P2.5/RXD0       |

| 31  | V <sub>SS</sub> | 64  | V <sub>SS</sub> | 97  | V <sub>SS</sub>   | 130 | V <sub>ss</sub> |

| 32  | READY#          | 65  | A20             | 98  | DSR1#/STXCLK      | 131 | P2.6/TXD0       |

| 33  | BS8#            | 66  | A21             | 99  | FLT#              | 132 | P2.7/CTS0#      |

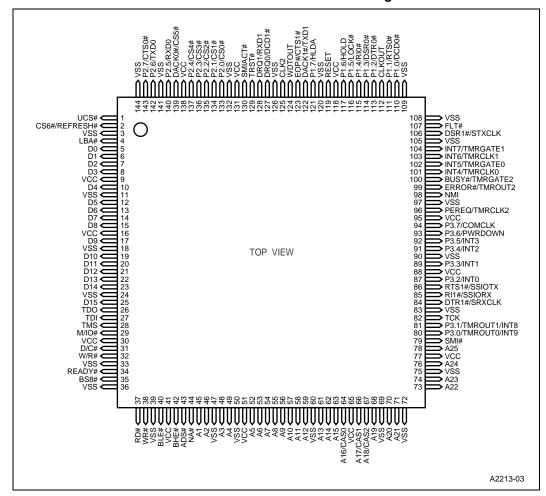

Figure 3. Intel386™ EX Embedded Processor 144-Pin TQFP Pin Assignment

#### Table 2. 144-Pin TQFP Pin Assignment

| Pin | Symbol          | Pin | Symbol          | Pin | Symbol            | Pin | Symbol          |

|-----|-----------------|-----|-----------------|-----|-------------------|-----|-----------------|

| 1   | UCS#            | 37  | RD#             | 73  | A22               | 109 | V <sub>SS</sub> |

| 2   | CS6#/REFRESH#   | 38  | WR#             | 74  | A23               | 110 | P1.0/DCD0#      |

| 3   | V <sub>ss</sub> | 39  | V <sub>SS</sub> | 75  | V <sub>ss</sub>   | 111 | P1.1/RTS0#      |

| 4   | LBA#            | 40  | BLE#            | 76  | A24               | 112 | CLKOUT          |

| 5   | D0              | 41  | V <sub>cc</sub> | 77  | V <sub>cc</sub>   | 113 | P1.2/DTR0#      |

| 6   | D1              | 42  | BHE#            | 78  | A25               | 114 | P1.3/DSR0#      |

| 7   | D2              | 43  | ADS#            | 79  | SMI#              | 115 | P1.4/RI0#       |

| 8   | D3              | 44  | NA#             | 80  | P3.0/TMROUT0/INT9 | 116 | P1.5/LOCK#      |

| 9   | V <sub>cc</sub> | 45  | A1              | 81  | P3.1/TMROUT1/INT8 | 117 | P1.6/HOLD       |

| 10  | D4              | 46  | A2              | 82  | тск               | 118 | V <sub>cc</sub> |

| 11  | V <sub>ss</sub> | 47  | V <sub>SS</sub> | 83  | V <sub>ss</sub>   | 119 | RESET           |

| 12  | D5              | 48  | A3              | 84  | DTR1#/SRXCLK      | 120 | V <sub>ss</sub> |

| 13  | D6              | 49  | A4              | 85  | RI1#/SSIORX       | 121 | P1.7/HLDA       |

| 14  | D7              | 50  | V <sub>SS</sub> | 86  | RTS1#/SSIOTX      | 122 | DACK1#/TXD1     |

| 15  | D8              | 51  | V <sub>cc</sub> | 87  | P3.2/INT0         | 123 | EOP#/CTS1#      |

| 16  | V <sub>cc</sub> | 52  | A5              | 88  | V <sub>cc</sub>   | 124 | WDTOUT          |

| 17  | D9              | 53  | A6              | 89  | P3.3/INT1         | 125 | CLK2            |

| 18  | V <sub>SS</sub> | 54  | A7              | 90  | V <sub>ss</sub>   | 126 | V <sub>SS</sub> |

| 19  | D10             | 55  | A8              | 91  | P3.4/INT2         | 127 | DRQ0/DCD1#      |

| 20  | D11             | 56  | A9              | 92  | P3.5/INT3         | 128 | DRQ1/RXD1       |

| 21  | D12             | 57  | A10             | 93  | P3.6/PWRDOWN      | 129 | TRST#           |

| 22  | D13             | 58  | A11             | 94  | P3.7/COMCLK       | 130 | SMIACT#         |

| 23  | D14             | 59  | A12             | 95  | V <sub>cc</sub>   | 131 | V <sub>cc</sub> |

| 24  | V <sub>SS</sub> | 60  | V <sub>ss</sub> | 96  | PEREQ/TMRCLK2     | 132 | V <sub>SS</sub> |

| 25  | D15             | 61  | A13             | 97  | V <sub>SS</sub>   | 133 | P2.0/CS0#       |

| 26  | TDO             | 62  | A14             | 98  | NMI               | 134 | P2.1/CS1#       |

| 27  | TDI             | 63  | A15             | 99  | ERROR#/TMROUT2    | 135 | P2.2/CS2#       |

| 28  | TMS             | 64  | A16/CAS0        | 100 | BUSY#/TMRGATE2    | 136 | P2.3/CS3#       |

| 29  | M/IO#           | 65  | V <sub>cc</sub> | 101 | INT4/TMRCLK0      | 137 | P2.4/CS4#       |

| 30  | V <sub>cc</sub> | 66  | A17/CAS1        | 102 | INT5/TMRGATE0     | 138 | V <sub>cc</sub> |

| 31  | D/C#            | 67  | A18/CAS2        | 103 | INT6/TMRCLK1      | 139 | DACK0#/CS5#     |

| 32  | W/R#            | 68  | A19             | 104 | INT7/TMRGATE1     | 140 | P2.5/RXD0       |

| 33  | V <sub>SS</sub> | 69  | V <sub>ss</sub> | 105 | V <sub>ss</sub>   | 141 | V <sub>SS</sub> |

| 34  | READY#          | 70  | A20             | 106 | DSR1#/STXCLK      | 142 | P2.6/TXD0       |

| 35  | BS8#            | 71  | A21             | 107 | FLT#              | 143 | P2.7/CTS0#      |

| 36  | V <sub>ss</sub> | 72  | V <sub>SS</sub> | 108 | V <sub>ss</sub>   | 144 | V <sub>ss</sub> |

## 3.0 Pin Description

Table 4 lists the Intel386 EX embedded processor pin descriptions. Table 3 defines the abbreviations used in the Type and Output States columns of Table 4.

Table 3. Pin Type and Output State Nomenclature

| Symbol                                                 | Description                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Type                                               |                                                                                                                                                                                                                                                                                                                                                                                 |

| #                                                      | The named signal is active low.                                                                                                                                                                                                                                                                                                                                                 |

| I                                                      | Standard TTL input signal.                                                                                                                                                                                                                                                                                                                                                      |

| O                                                      | Standard CMOS output signal.                                                                                                                                                                                                                                                                                                                                                    |

| I/O                                                    | Input and output signal.                                                                                                                                                                                                                                                                                                                                                        |

| I/OD                                                   | Input and open-drain output signal.                                                                                                                                                                                                                                                                                                                                             |

| ST                                                     | Schmitt-triggered input signal.                                                                                                                                                                                                                                                                                                                                                 |

| P                                                      | Power pin.                                                                                                                                                                                                                                                                                                                                                                      |

| G                                                      | Ground pin.                                                                                                                                                                                                                                                                                                                                                                     |

| Output State                                           |                                                                                                                                                                                                                                                                                                                                                                                 |

| H(1)                                                   | Output driven to $V_{CC}$ during Bus Hold                                                                                                                                                                                                                                                                                                                                       |

| H(0)                                                   | Output driven to $V_{SS}$ during Bus Hold                                                                                                                                                                                                                                                                                                                                       |

| H(Z)                                                   | Output floats during Bus Hold                                                                                                                                                                                                                                                                                                                                                   |

| H(Q)                                                   | Output remains active during Bus Hold                                                                                                                                                                                                                                                                                                                                           |

| H(X)                                                   | Output retains current state during Bus Hold                                                                                                                                                                                                                                                                                                                                    |

| R(WH)<br>R(WL)<br>R(1)<br>R(0)<br>R(Z)<br>R(Q)<br>R(X) | $\begin{array}{c} \mbox{Output Weakly Held at $V_{CC}$ during Reset} \\ \mbox{Output Weakly Held at $V_{SS}$ during Reset} \\ \mbox{Output driven to $V_{CC}$ during Reset} \\ \mbox{Output driven to $V_{SS}$ during Reset} \\ \mbox{Output floats during Reset} \\ \mbox{Output remains active during Reset} \\ \mbox{Output retains current state during Reset} \end{array}$ |

| (1) <sup>†</sup>                                       | Output driven to $V_{CC}$ during Idle Mode                                                                                                                                                                                                                                                                                                                                      |

| (0)                                                    | Output driven to $V_{SS}$ during Idle Mode                                                                                                                                                                                                                                                                                                                                      |

| (Z)                                                    | Output floats during Idle Mode                                                                                                                                                                                                                                                                                                                                                  |

| (Q)                                                    | Output remains active during Idle Mode                                                                                                                                                                                                                                                                                                                                          |

| (X)                                                    | Output retains current state during Idle Mode                                                                                                                                                                                                                                                                                                                                   |

| P(1)                                                   | Output driven to $V_{CC}$ during Powerdown Mode                                                                                                                                                                                                                                                                                                                                 |

| P(0)                                                   | Output driven to $V_{SS}$ during Powerdown Mode                                                                                                                                                                                                                                                                                                                                 |

| P(Z)                                                   | Output floats during Powerdown Mode                                                                                                                                                                                                                                                                                                                                             |

| P(Q)                                                   | Output remains active during Powerdown Mode                                                                                                                                                                                                                                                                                                                                     |

| P(X)                                                   | Output retains current state during Powerdown Mode                                                                                                                                                                                                                                                                                                                              |

† The idle mode output states assume that no internal bus master (DMA or RCU) has control of the bus during idle mode

| Symbol  | Туре | Output States                 | Name and Function                                                                                                                                                                                                                                                                                         |

|---------|------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A25:1   | ο    | H(Z)<br>R(1)<br>I(1)<br>P(1)  | Address Bus outputs physical memory or port I/O addresses.<br>These signals are valid when ADS# is active and remain valid<br>until the next T1, T2P, or Ti. During HOLD cycles they are driven<br>to a high-impedance state. A18:16 are multiplexed with CAS2:0.                                         |

| ADS#    | ο    | H(Z)<br>R(1)<br>I(1)<br>P(1)  | Address Status indicates that the processor is driving a valid bus-cycle definition and address (W/R#, D/C#, M/IO#, A25:1, BHE#, BLE#) onto its pins.                                                                                                                                                     |

| BHE#    | ο    | H(Z)<br>R(0)<br>I(X)<br>P(0)  | Byte High Enable indicates that the processor is transferring a high data byte.                                                                                                                                                                                                                           |

| BLE#    | 0    | H(Z)<br>R(0)<br>I(X)<br>P(1)  | Byte Low Enable indicates that the processor is transferring a low data byte.                                                                                                                                                                                                                             |

| BS8#    | I    |                               | Bus Size indicates that an 8-bit device is currently being addressed.                                                                                                                                                                                                                                     |

| BUSY#   | I    |                               | <b>Busy</b> indicates that the math coprocessor is busy. If BUSY# is sampled LOW at the falling edge of RESET, the processor performs an internal self test. BUSY# is multiplexed with TMRGATE2 and has a temporary weak pull-up resistor.                                                                |

| CAS2:0  | 0    | H(Z)<br>R(1)<br>I(1)<br>P(1)  | <b>Cascade Address</b> carries the slave address information from<br>the 8259A master interrupt module during interrupt acknowledge<br>bus cycles. CAS2:0 are multiplexed with A18:16.                                                                                                                    |

| CLK2    | ST   |                               | <b>Clock Input</b> is connected to an external clock that provides the fundamental timing for the device.                                                                                                                                                                                                 |

| CLKOUT  | 0    | H(Q)<br>R(Q)<br>I(Q)<br>P(0)  | CLKOUT is a PH1P clock output.                                                                                                                                                                                                                                                                            |

| COMCLK  | I    |                               | Serial Communications Baud Clock is an alternate clock<br>source for the asynchronous serial ports. COMCLK is<br>multiplexed with P3.7 and has a temporary weak pull-down<br>resistor.                                                                                                                    |

| CS4:0#  | ο    | H(1)<br>R(WH)<br>I(Q)<br>P(X) | <b>Chip-selects</b> are activated when the address of a memory or I/C bus cycle is within the address region programmed by the user. They are multiplexed as follows: CS6# with REFRESH#, CS5# with DACK0#, and CS4:0# with P2.4:0.                                                                       |

| CS6:5#  | ο    | H(1)<br>R(1)<br>I(Q)<br>P(X)  | <b>Chip-selects</b> are activated when the address of a memory or I/C bus cycle is within the address region programmed by the user. They are multiplexed as follows: CS6# with REFRESH#, CS5# with DACK0#, and CS4:0# with P2.4:0.                                                                       |

| CTS1:0# | I    |                               | Clear to Send SIO1 and SIO0 prevent the transmission of data<br>to the asynchronous serial port's RXD1 and RXD0 pins,<br>respectively. CTS1# is multiplexed with EOP#, and CTS0# is<br>multiplexed with P2.7. CTS1# requires an external pull-up<br>resistor. Both have temporary weak pull-up resistors. |

#### Table 4. Intel386<sup>™</sup> EX Microprocessor Pin Descriptions (Sheet 1 of 6)

NOTES:

| Symbol   | Туре | Output States                 | Name and Function                                                                                                                                                                                                                                                                                                                 |

|----------|------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D15:0    | I/O  | H(Z)<br>R(Z)<br>P(Z)          | <b>Data Bus</b> inputs data during memory read, I/O read, and interrupt acknowledge cycles and outputs data during memory and I/O write cycles. During writes, this bus is driven during phase 2 of T1 and remains active until phase 2 of the next T1, T1P, or Ti. During reads, data is latched on the falling edge of phase 2. |

| DACK1:0# | 0    | H(1)<br>R(1)<br>I(Q)<br>P(X)  | <b>DMA Acknowledge 1 and 0</b> signal to an external device that the processor has acknowledged the corresponding DMA request and is relinquishing the bus. DACK1# is multiplexed with TXD1, and DACK0# is multiplexed with CS5#.                                                                                                 |

| D/C#     | 0    | H(Z)<br>R(1)<br>I(0)<br>P(0)  | <b>Data/Control</b> indicates whether the current bus cycle is a data cycle (memory or I/O read or write) or a control cycle (interrupt acknowledge, halt, or code fetch).                                                                                                                                                        |

| DCD1:0   | I    |                               | <b>Data Carrier Detect SIO1 and SIO0</b> indicate that the modem or data set has detected the corresponding asynchronous serial channel's data carrier. DCD1# is multiplexed with DRQ0, and DCD0# is multiplexed with P1.0 and has a temporary weak pullup resistor.                                                              |

| DRQ1:0   | I    |                               | <b>DMA External Request 1 and 0</b> indicate that a peripheral requires DMA service. DRQ1 is multiplexed with RXD1, and DRQ0 is multiplexed with DCD1#.                                                                                                                                                                           |

| DSR1:0#  | I    |                               | <b>Data Set Ready SIO1 and SIO0</b> indicate that the modem or data set is ready to establish a communication link with the corresponding asynchronous serial channel. DSR1# is multiplexed with STXCLK and has a permanent weak pull-up resistor, and DSR0# is multiplexed with P1.3 and has a temporary weak pull-up resistor.  |

| DTR1:0#  | 0    | H(X)<br>R(WH)<br>I(X)<br>P(X) | <b>Data Terminal Ready SIO1 and SIO0</b> indicate that the corresponding asynchronous serial channel is ready to establish a communication link with the modem or data set. DTR1# is multiplexed with SRXCLK, and DTR0# is multiplexed with P1.2.                                                                                 |

| EOP#     | I/OD | H(Z)<br>R(WH)<br>I(Z)<br>P(Z) | <b>End of Process</b> indicates that the processor has reached terminal count during a DMA transfer. An external device can also pull this pin LOW. EOP# is multiplexed with CTS1#.                                                                                                                                               |

| ERROR#   | I    |                               | <b>Error</b> indicates that the math coprocessor has an error condition.<br>ERROR# is multiplexed with TMROUT2 and has a temporary weak pull-up resistor.                                                                                                                                                                         |

| FLT#     | I    |                               | <b>Float</b> forces all bidirectional and output signals except TDO to a high-impedance state. It has a permanent weak pull-up resistor. This pin should be tied to $V_{CC}$ through a 3 to 7 KOhm pull-up resistor.                                                                                                              |

| HLDA     | 0    | H(1)<br>R(WL)<br>I(Q)<br>P(X) | <b>Bus Hold Acknowledge</b> indicates that the processor has surrendered control of its local bus to another bus master. HLDA is multiplexed with P1.7.                                                                                                                                                                           |

| HOLD     | I    |                               | <b>Bus Hold Request</b> allows another bus master to request control of the local bus. HLDA active indicates that bus control has been granted. HOLD is multiplexed with P1.6. It has a temporary weak pull-down resistor.                                                                                                        |

#### Table 4. Intel386<sup>™</sup> EX Microprocessor Pin Descriptions (Sheet 2 of 6)

NOTES:

| Symbol   | Туре | Output States                 | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT9:0   | I    |                               | Interrupt Requests are maskable inputs that cause the CPU to suspend execution of the current program and then execute an interrupt acknowledge cycle. They are multiplexed as follows: INT9 with TMROUT0 and P3.0, INT8 with TMROUT1 and P3.1, INT7 with TMRGATE1, INT6 with TMRCLK1, INT5 with TMRGATE0, INT4 with TMRCLK0, and INT3:0 with P3.5:2. INT9, INT8, and INT3:0 have temporary weak pull-down resistors. |

| LBA#     | 0    | H(1)<br>R(1)<br>I(Q)<br>P(X)  | <b>Local Bus Access</b> is asserted whenever the processor provides<br>the READY# signal to terminate a bus transaction. This occurs<br>when an internal peripheral address is accessed or when the<br>chip-select unit provides the READY# signal.                                                                                                                                                                   |

| LOCK#    | 0    | H(Z)<br>R(WH)<br>I(X)<br>P(X) | <b>Bus Lock</b> prevents other bus masters from gaining control of the system bus.<br>LOCK# is multiplexed with P1.5.                                                                                                                                                                                                                                                                                                 |

| M/IO#    | 0    | H(Z)<br>R(0)<br>I(1)<br>P(1)  | <b>Memory/IO</b> Indicates whether the current bus cycle is a memory cycle or an I/O cycle. When M/IO# is HIGH, the bus cycle is a memory cycle; when M/IO# is LOW, the bus cycle is an I/O cycle                                                                                                                                                                                                                     |

| NA#      | I    |                               | Next Address requests address pipelining.                                                                                                                                                                                                                                                                                                                                                                             |

| NMI      | ST   |                               | <b>Nonmaskable Interrupt Request</b> is a non-maskable input that causes the CPU to suspend execution of the current program and execute an interrupt acknowledge cycle.                                                                                                                                                                                                                                              |

| PEREQ    | I    |                               | <b>Processor Extension Request</b> indicates that the math coprocessor has data to transfer to the processor. PEREQ is multiplexed with TMRCLK2 and has a temporary weak pull-dowr resistor.                                                                                                                                                                                                                          |

| P1.5:0   | I/O  | H(X)<br>R(WH)<br>I(X)<br>P(X) | <b>Port 1, Pins 7:0</b> are multipurpose bidirectional port pins. They are multiplexed as follows: P1.7 with HLDA, P1.6 with HOLD, P1.5 with LOCK#, P1.4 with RI0#, P1.3 with DSR0#, P1.2 with DTR0#, P1.1 with RTS0#, and P1.0 with DCD0#.                                                                                                                                                                           |

| P1.7:6   | I/O  | H(X)<br>R(WL)<br>I(X)<br>P(X) | <b>Port 1, Pins 7:0</b> are multipurpose bidirectional port pins. They are multiplexed as follows: P1.7 with HLDA, P1.6 with HOLD, P1.5 with LOCK#, P1.4 with RI0#, P1.3 with DSR0#, P1.2 with DTR0#, P1.1 with RTS0#, and P1.0 with DCD0#.                                                                                                                                                                           |

| P2.7,4:0 | I/O  | H(X)<br>R(WH)<br>I(X)<br>P(X) | <b>Port 2, Pins 7:0</b> are multipurpose bidirectional port pins. They are multiplexed as follows: P2.7 with CTS0#, P2.6 with TXD0, P2.5 with RXD0, and P2.4:0 with CS4:0#.                                                                                                                                                                                                                                           |

| P2.6:5   | I/O  | H(X)<br>R(WL)<br>I(X)<br>P(X) | <b>Port 2, Pins 7:0</b> are multipurpose bidirectional port pins. They are multiplexed as follows: P2.7 with CTS0#, P2.6 with TXD0, P2.5 with RXD0, and P2.4:0 with CS4:0#.                                                                                                                                                                                                                                           |

| P3.7:0   | I/O  | H(X)<br>R(WL)<br>I(X)<br>P(X) | <b>Port 3, Pins 7:0</b> are multipurpose bidirectional port pins. They are multiplexed as follows: P3.7 with COMCLK, P3.6 with PWRDOWN, P3.5:2 with INT3:0, and P3.1:0 with TMROUT1:0 and INT8:9.                                                                                                                                                                                                                     |

#### Table 4. Intel386<sup>™</sup> EX Microprocessor Pin Descriptions (Sheet 3 of 6)

NOTES:

| Symbol   | Туре | Output States                 | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWRDOWN  | 0    | H(Q)<br>R(WL)<br>I(X)<br>P(1) | <b>Powerdown</b> indicates that the processor is in powerdown mode.<br>PWRDOWN is multiplexed with P3.6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RD#      | 0    | H(1)<br>R(1)<br>I(1)<br>P(1)  | <b>Read Enable</b> indicates that the current bus cycle is a read cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| READY#   | I/O  | H(Z)<br>R(Z)<br>I(Z)<br>P(Z)  | <b>Ready</b> indicates that the current bus transaction has completed.<br>An external device or an internal signal can drive READY#.<br>Internally, the chip-select wait-state logic can generate the ready<br>signal and drive the READY# pin active.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RESET    | ST   |                               | <b>Reset</b> suspends any operation in progress and places the processor into a known reset state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| REFRESH# | 0    | H(1)<br>R(1)<br>I(Q)<br>P(X)  | <b>Refresh</b> indicates that the current bus cycle is a refresh cycle.<br>REFRESH# is multiplexed with CS6#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RI1:0#   | I    |                               | <b>Ring Indicator SIO1 and SIO0</b> indicate that the modem or data set has received a telephone ringing signal. RI1# is multiplexed with SSIORX, and RI0# is multiplexed with P1.4 and has a temporary weak pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RTS1#    | 0    | H(X)<br>R(WL)<br>I(X)<br>P(X) | <b>Request-to-send SIO1 and SIO0</b> indicate that corresponding asynchronous serial channel is ready to exchange data with the modem or data set. RTS1# is multiplexed with SSIOTX, and RTS0# is multiplexed with P1.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RTS0#    | 0    | H(X)<br>R(WH)<br>I(X)<br>P(X) | <b>Request-to-send SIO1 and SIO0</b> indicate that corresponding asynchronous serial channel is ready to exchange data with the modem or data set. RTS1# is multiplexed with SSIOTX, and RTS0# is multiplexed with P1.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RXD1:0   | I    |                               | <b>Receive Data SIO1 and SIO0</b> accept serial data from the modem or data set to the corresponding asynchronous serial channel. RXD1 is multiplexed with DRQ1, and RXD0 is multiplexed with P2.5 and has a temporary weak pull-down resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SMI#     | ST   |                               | System Management Interrupt invokes System Management<br>Mode (SMM). SMI# is the highest priority external interrupt. It is<br>latched on its falling edge and forces the CPU into SMM upon<br>completion of the current instruction. SMI# is recognized on an<br>instruction boundary and at each iteration for repeat string<br>instructions. SMI# cannot interrupt LOCKed bus cycles or a<br>currently executing SMM. When the processor receives a<br>second SMI# while in SMM, it latches the second SMI# on the<br>SMI# falling edge. However, the processor must exit SMM by<br>executing a resume instruction (RSM) before it can service the<br>second SMI#. SMI# has a permanent weak pull-up resistor. |

| SMIACT#  | 0    | H(1)<br>R(1)<br>I(X)<br>P(X)  | System Management Interrupt Active indicates that the processor is operating in System Management Mode (SMM). It is asserted when the processor initiates an SMM sequence and remains asserted (LOW) until the processor executes the resume instruction (RSM).                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### Table 4. Intel386<sup>™</sup> EX Microprocessor Pin Descriptions (Sheet 4 of 6)

NOTES:

| Symbol     | Туре | Output States                                                                                                             | Name and Function                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|------------|------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SRXCLK     | I/O  | H(Q)<br>R(WH)<br>I(Q)<br>P(X)/P(Q) <sup>Note 1</sup>                                                                      | <b>SSIO Receive Clock</b> synchronizes data being accepted by the synchronous serial port. SRXCLK is multiplexed with DTR1#.                                                                                                                                                                                                |  |  |  |  |

| SSIORX     | I    |                                                                                                                           | <b>SSIO Receive Serial Data</b> accepts serial data (most-significant bit first) being sent to the synchronous serial port. SSIORX is multiplexed with RI1#.                                                                                                                                                                |  |  |  |  |

| SSIOTX     | 0    | H(Q)<br>R(WL)                                                                                                             | <b>SSIO Transmit Serial Data</b> sends serial data (most-significant bit first) from the synchronous serial port. SSIOTX is multiplexed with RTS1#.                                                                                                                                                                         |  |  |  |  |

| 33101 X    | 0    | I(Q)<br>P(X)/P(Q) <sup>Note 1</sup>                                                                                       | Intel does not specify a data hold time for SSIOTX. Slower external devices may require additional hardware to properly interface the SSIO unit.                                                                                                                                                                            |  |  |  |  |

| STXCLK     | I/O  | H(Q)<br>R(WH)<br>I(Q)<br>P(X)/P(Q) <sup>Note 1</sup>                                                                      | <b>SSIO Transmit Clock</b> synchronizes data being sent by the synchronous serial port. STXCLK is multiplexed with DSR1.                                                                                                                                                                                                    |  |  |  |  |

| тск        | I    |                                                                                                                           | <b>TAP (Test Access Port) Controller Clock</b> provides the clock input for the JTAG logic. It has a permanent weak pull-up resistor.                                                                                                                                                                                       |  |  |  |  |

| TDI        | I    |                                                                                                                           | TAP (Test Access Port) Controller Data Input is the serial<br>input for test instructions and data. It has a permanent weak pull<br>up resistor.                                                                                                                                                                            |  |  |  |  |

| TDO        | ο    | H(Z)/H(Q) <sup>Note 2</sup><br>R(Z)/R(Q) <sup>Note 2</sup><br>I(Z)/I(Q) <sup>Note 2</sup><br>P(Z)/ P(Q) <sup>Note 2</sup> | TAP (Test Access Port) Controller Data Output is the serial output for test instructions and data.                                                                                                                                                                                                                          |  |  |  |  |

| TMRCLK2:0  | I    |                                                                                                                           | <b>Timer/Counter Clock Inputs</b> can serve as external clock inputs<br>for the corresponding timer/counters. (The timer/counters can<br>also be clocked internally.) They are multiplexed as follows:<br>TMRCLK2 with PEREQ, TMRCLK1 with INT6, and TMRCLK0<br>with INT4. TMRCLK2 has a temporary weak pull-down resistor. |  |  |  |  |

| TMRGATE2:0 | I    |                                                                                                                           | <b>Timer/Counter Gate Inputs</b> can control the corresponding timer/counter's counting (enable, disable, or trigger, depending on the programmed mode). They are multiplexed as follows: TMRGATE2 with BUSY#, TMRGATE1 with INT7, and TMRGATE0 with INT5. TMRGATE2 has a temporary weak pullup resistor.                   |  |  |  |  |

| TMROUT2    | 0    | H(Q)<br>R(WH)<br>I(Q)<br>P(X)/P(Q) <sup>Note 1</sup>                                                                      | <b>Timer/Counter Outputs</b> provide the output of the corresponding timer/counter. The form of the output depends on the programmed mode. They are multiplexed as follows: TMROUT2 with ERROR#, TMROUT1 with P3.1 and INT8, and TMROUT0 with P3.0 and INT9.                                                                |  |  |  |  |