# S6B0725A

### 104 SEG / 65 COM DRIVER & CONTROLLER FOR STN LCD

Aug. 2001

Ver. 1.5

Contents in this document are subject to change without notice. No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, for any purpose, without the express written permission of LCD Driver IC Team.

#### **Precautions for Light**

Light has characteristics to move electrons in the integrated circuitry of semiconductors, therefore may change the characteristics of semiconductor devices when irradiated with light. Consequently, the users of the packages which may expose chips to external light such as COB, COG, TCP and COF must consider effective methods to block out light from reaching the IC on all parts of the surface area, the top, bottom and the sides of the chip. Follow the precautions below when using the products.

- 1. Consider and verify the protection of penetrating light to the IC at substrate (board or glass) or product design stage.

- 2. Always test and inspect products under the environment with no penetration of light.

| S6B0725A Specification Revision History |                                                                                                                                                                                                                                                                                                                                                                           |         |  |  |  |  |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|--|

| Version                                 | Content                                                                                                                                                                                                                                                                                                                                                                   | Date    |  |  |  |  |  |

| 0.0                                     | Initial version                                                                                                                                                                                                                                                                                                                                                           | 2000.07 |  |  |  |  |  |

| 1.0                                     | <ol> <li>VLCD pin: Input or output pin → only output pin (page 8, 24)</li> <li>Regulator resistor select: (1,1,0), (1,1,1) → not available (page 27, 38)</li> <li>VLCD absolute maximum rating:-0.3V to 15V → -0.3V to 13V (page 47)</li> <li>X4 voltage boosting VCI range: 2.4V to 3.3V → 2.4V to 3.0V (page 48)</li> <li>Power consumption: TBD valid value</li> </ol> | 2000.10 |  |  |  |  |  |

| 1.1                                     | Oscillator frequency (fCL): (TYP.) 4.75KHz → 5.45KHz (page 48)                                                                                                                                                                                                                                                                                                            | 2000.11 |  |  |  |  |  |

| 1.2                                     | VLCD capacitor is greater than 1μF (page 8, 61)                                                                                                                                                                                                                                                                                                                           | 2001.01 |  |  |  |  |  |

| 1.3                                     | <ol> <li>Figure 15 is changed (page 27)</li> <li>Figure 2-1, 2-2 are added (page 14)</li> <li>Figure 21 is changed (page 43)</li> <li>Table 21 is changed (page 50)</li> <li>Added detail information for several items</li> </ol>                                                                                                                                        | 2001.03 |  |  |  |  |  |

| 1.4                                     | Added dynamic current consumption at 4 times boosting operation (page 48)                                                                                                                                                                                                                                                                                                 | 2001.05 |  |  |  |  |  |

| 1.5                                     | Correct some misspellings                                                                                                                                                                                                                                                                                                                                                 | 2001.08 |  |  |  |  |  |

## **CONTENTS**

| INTRODUCTION                               |    |

|--------------------------------------------|----|

| FEATURES                                   | 1  |

| BLOCK DIAGRAM                              | 3  |

| PAD CONFIGURATION                          | 4  |

| PAD CENTER COORDINATES                     | 6  |

| PIN DESCRIPTION                            | 8  |

| POWER SUPPLY                               |    |

| LCD DRIVER SUPPLY                          |    |

| SYSTEM CONTROL                             | 9  |

| MICROPROCESSOR INTERFACE                   | 10 |

| LCD DRIVER OUTPUTS                         | 12 |

| FUNCTIONAL DESCRIPTION                     | 13 |

| MICROPROCESSOR INTERFACE                   | 13 |

| DISPLAY DATA RAM (DDRAM)                   | 18 |

| LCD DISPLAY CIRCUITS                       | 21 |

| LCD DRIVER CIRCUITS                        |    |

| POWER SUPPLY CIRCUITS                      |    |

| RESET CIRCUIT                              |    |

| INSTRUCTION DESCRIPTION                    |    |

| SPECIFICATIONS                             |    |

| ABSOLUTE MAXIMUM RATINGS                   |    |

| DC CHARACTERISTICS                         |    |

| AC CHARACTERISTICS                         |    |

| REFERENCE APPLICATIONS                     |    |

| MICROPROCESSOR INTERFACE                   | 54 |

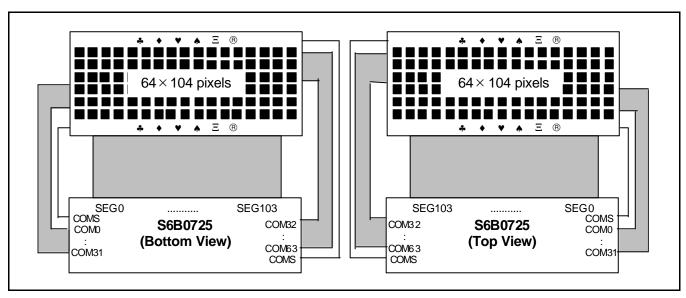

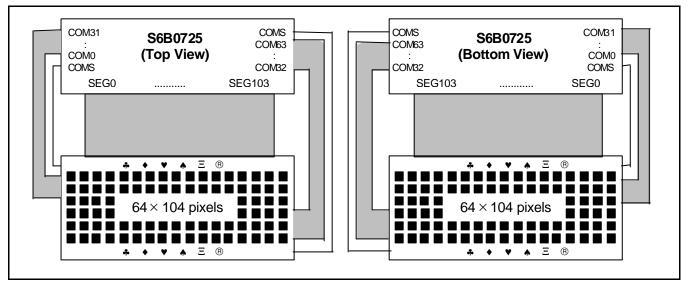

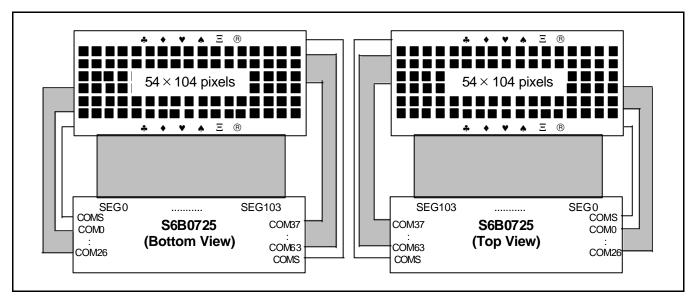

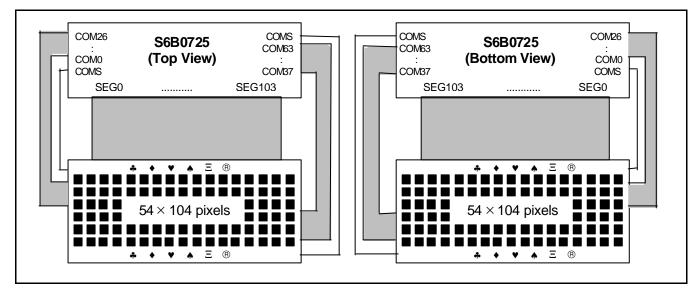

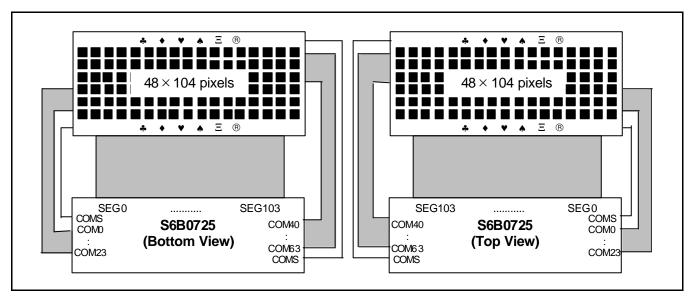

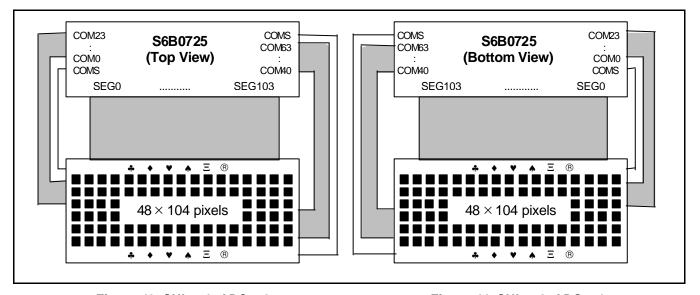

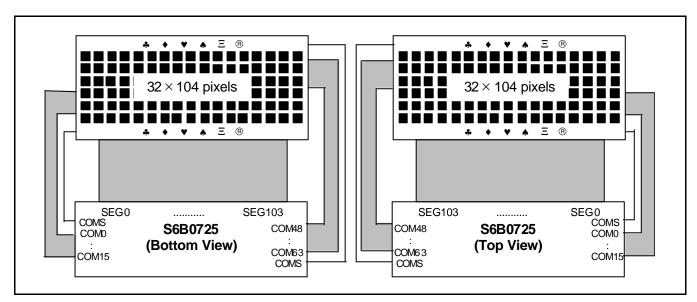

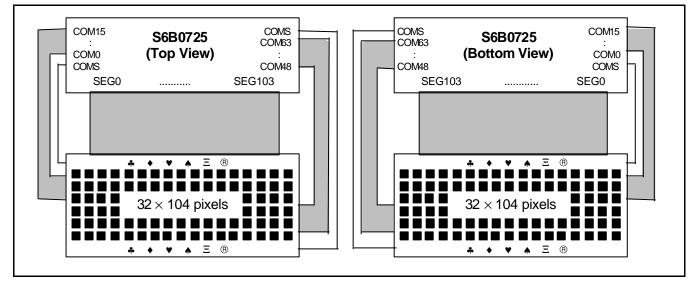

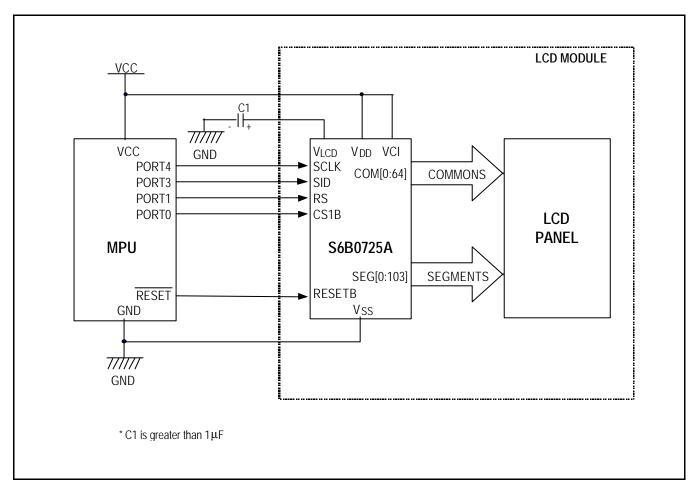

| CONNECTIONS BETWEEN SCROTZEN AND LCD DANEL | 56 |

#### INTRODUCTION

The S6B0725A is a single-chip driver & controller LSI for graphic dot-matrix liquid crystal display systems. This chip can be connected directly to a microprocessor, accepts serial or 8-bit parallel display data from the microprocessor, stores the display data in an on-chip display data RAM of 65 x 104 bits and generates a liquid crystal display drive signal independent of the microprocessor. It provides a high-flexible display section due to 1-to-1 correspondence between on-chip display data RAM bits and LCD panel pixels. It contains 65 common driver circuits and 104 segment driver circuits, so that a single chip can drive a 65 x 104 dot display. This chip is able to minimize power consumption because it performs display data RAM read/write operation with no external operation clock. In addition, because it contains power supply circuits necessary to drive liquid crystal, which is a display clock oscillator circuit, high performance voltage converter circuit, high-accuracy voltage regulator circuit, low power consumption voltage divider resistors and OP-Amp for liquid crystal driver power voltage, it is possible to make the lowest power consumption display system with the fewest components for high performance portable systems.

#### **FEATURES**

#### **Display Driver Output Circuits**

65 common outputs and 104 segment outputs

#### **On-chip Display Data RAM**

Capacity: 65 x 104 = 6.760 bits

RAM bit data "1": a dot of display is illuminated

RAM bit data "0": a dot of display is not illuminated

#### **Applicable Duty Ratios**

| Duty ratio | Applicable LCD bias | Maximum display area |

|------------|---------------------|----------------------|

| 1/65       | 1/7 or 1/9          | 65 × 104             |

| 1/55       | 1/6 or 1/8          | 55 × 104             |

| 1/49       | 1/6 or 1/8          | 49 × 104             |

| 1/33       | 1/5 or 1/6          | 33 × 104             |

#### Microprocessor Interface

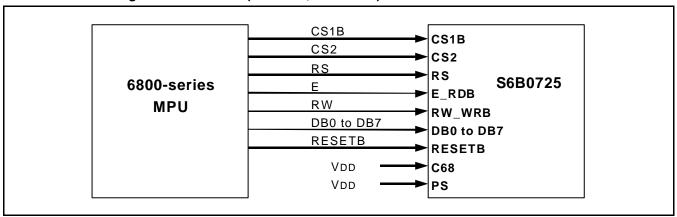

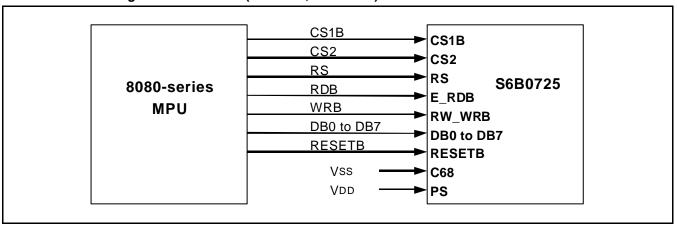

- High-speed 8-bit parallel bi-directional interface with 6800-series or 8080-series

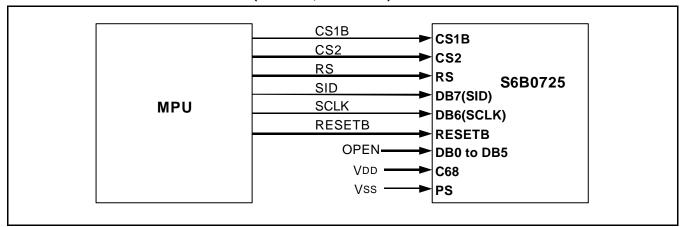

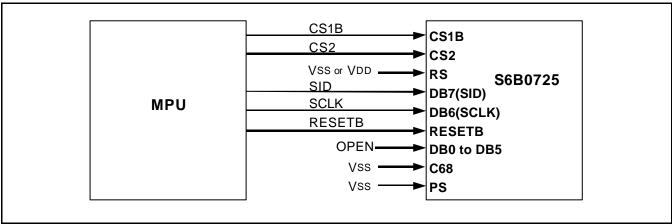

- SPI (Serial Peripheral Interface) available. (Only write operation)

#### **Various Function Set**

- Display ON / OFF, set initial display line, set page address, set column address, read status, write/read display data, select segment driver output, reverse display ON / OFF, entire display ON / OFF, select LCD bias, set/reset modify-read, select common driver output, control display power circuit, select internal regulator resistor ratio for VLCD voltage regulation, electronic volume, set static indicator state.

- H/W and S/W Reset available

- Static drive circuit equipped internally for indicators with 4 flashing mode

#### **Built-in Analog Circuit**

- On-chip oscillator circuit for display clock

- High performance voltage converter (with booster ratios of x3 and x4)

- High accuracy voltage regulator (temperature coefficient: -0.05 ± 0.03%/°C or external input)

- Electronic contrast control function (64 steps)

- Vref =  $2.1V \pm 3\%$  (VLCD voltage adjustment voltage)

- High performance voltage follower (V1 to V4 voltage divider resistors and OP-Amp for increasing drive capacity)

#### **Operating Voltage Range**

- Supply voltage (VDD): 2.4 to 3.6 V

- LCD driving voltage (VLCD): 4.5 to 9.0 V

#### **Low Power Consumption**

- Operating power: 120 μA typical (conditions: VDD = 3V, x 3 boosting (VCI = VDD), V0 = 7.6V, Internal power supply ON, display OFF and normal mode is selected)

- Standby power: 10 μA maximum (during power save[standby] mode)

#### **Operating Temperatures**

Wide range of operating temperatures : -40 to 85°C

#### **CMOS Process**

#### **Package Type**

Gold bumped chip

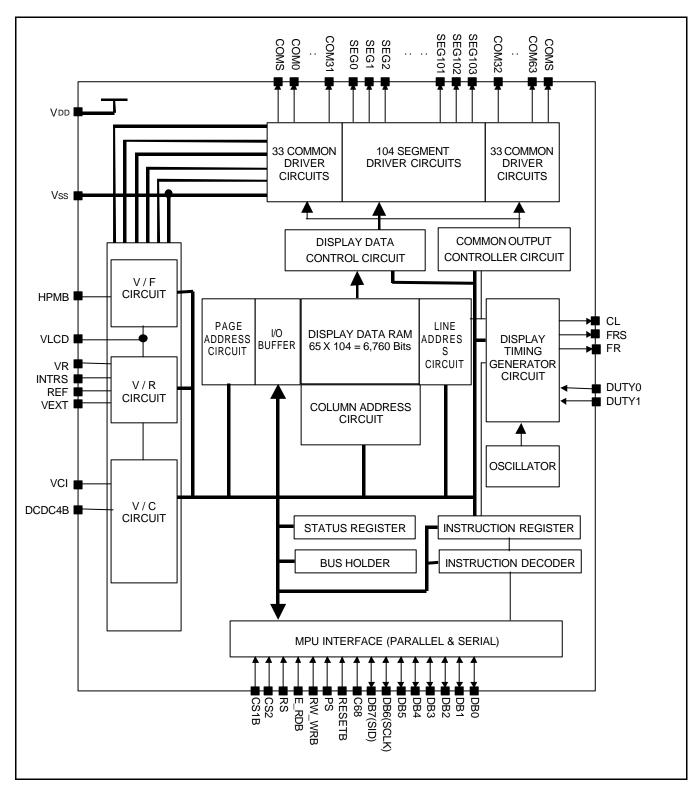

#### **BLOCK DIAGRAM**

Figure 1. Block Diagram

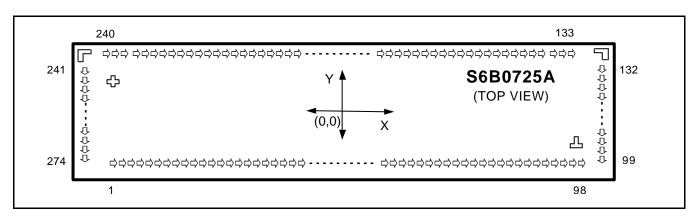

## **PAD CONFIGURATION**

Figure 2. S6B0725A Chip Configuration

Table 1. S6B0725A Pad Dimensions

| Item              | Pad No.    | Si   | ze    | Unit  |  |

|-------------------|------------|------|-------|-------|--|

| itein             | Pau No.    | Х    | Υ     | Oilit |  |

| Chip size         | -          | 8220 | 2540  |       |  |

|                   | 1 to 98    | 7    | 0     |       |  |

|                   | 99 to 100  | 7    | 0     |       |  |

|                   | 100 to 132 | 6    | 0     |       |  |

|                   | 133 to 134 | 8    | 0     |       |  |

| 5                 | 134 to 135 | 19   | 94    |       |  |

| Pad pitch         | 135 to 238 | 6    | 8     |       |  |

|                   | 238 to 239 | 19   | 94    |       |  |

|                   | 239 to 240 | 8    | 0     |       |  |

|                   | 241 to 273 | 60   |       |       |  |

|                   | 273 to 274 | 70   |       | μm    |  |

|                   | 1 to 98    | 42   | 92    |       |  |

|                   | 99         | 102  | 52    |       |  |

|                   | 100 to 132 | 102  | 32    |       |  |

| Bumped pad size   | 133 to 134 | 52   | 102   |       |  |

| (Bottom)          | 135 to 238 | 32   | 102   |       |  |

|                   | 239 to 240 | 52   | 102   |       |  |

|                   | 241 to 273 | 102  | 32    |       |  |

|                   | 274        | 102  | 52    |       |  |

| Bumped pad height | All pad    | 14 ( | Гур.) |       |  |

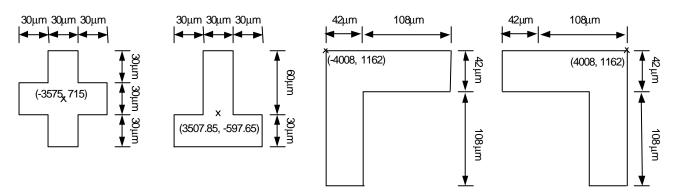

#### **COG Align Key Coordinate**

#### ILB Align Key Coordinate(with Gold Bump \*)

\* When designing COG pattern, ITO pattern must be prohibited on ILB Align Key, DUMMY pads, TEST pads. If ITO pattern is used for routing over these area, it can be happened pattern-short through bumped pattern on these area.

## **PAD CENTER COORDINATES**

**Table 2. Pad Center Coordinates**

[Unit: µm]

| Pad | Pad    | Х     | Υ             | Pad       | Pad    | х    | Υ             | Pad | Pad    | Х    | [Unit: μm]<br>Y |

|-----|--------|-------|---------------|-----------|--------|------|---------------|-----|--------|------|-----------------|

| No. | Name   |       |               | No.       | Name   |      |               | No. | Name   |      |                 |

| 1   | DUMMY1 | -3390 | -1155         | 51        | VCI    | 110  | -1155         | 101 | COM30  | 3963 | -930            |

| 2   | FRS    | -3320 | -1155         | 52        | VCI    | 180  | -1155         | 102 | COM29  | 3963 | -870            |

| 3   | FR     | -3250 | -11 <u>55</u> | 53        | VCI    | 250  | -1155         | 103 | COM28  | 3963 | -810            |

| 4   | CL     | -3180 | -1155         | 54        | VCI    | 320  | -1155         | 104 | COM27  | 3963 | -750            |

| 5   | TEST1  | -3110 | -1155         | 55        | VCI    | 390  | -1155         | 105 | COM26  | 3963 | -690            |

| 6   | VDD    | -3040 | -1155         | 56        | VCI    | 460  | -11 <u>55</u> | 106 | COM25  | 3963 | -630            |

| 7   | VDD    | -2970 | -11 <u>55</u> | 57        | VCI    | 530  | -11 <u>55</u> | 107 | COM24  | 3963 | -570            |

| 8   | VDD    | -2900 | -11 <u>55</u> | 58        | VDD    | 600  | -11 <u>55</u> | 108 | COM23  | 3963 | -510            |

| 9   | VDD    | -2830 | -11 <u>55</u> | <u>59</u> | VEXT   | 670  | -11 <u>55</u> | 109 | COM22  | 3963 | -450            |

| 10  | VDD    | -2760 | -1155         | 60        | VSS    | 740  | -1155         | 110 | COM21  | 3963 | -390            |

| 11  | VDD    | -2690 | -1155         | 61        | REF    | 810  | -1155         | 111 | COM20  | 3963 | -330            |

| 12  | VDD    | -2620 | -11 <u>55</u> | 62        | VDD    | 880  | -11 <u>55</u> | 112 | COM19  | 3963 | -270            |

| 13  | VDD    | -2550 | -1155         | 63        | DCDC4B | 950  | -1155         | 113 | COM18  | 3963 | -210            |

| 14  | VDD    | -2480 | -11 <u>55</u> | 64        | VSS    | 1020 | -11 <u>55</u> | 114 | COM17  | 3963 | -150            |

| 15  | VDD    | -2410 | -1155         | 65        | HPMB   | 1090 | -1155         | 115 | COM16  | 3963 | -90             |

| 16  | VDD    | -2340 | -1155         | 66        | VDD    | 1160 | -1155         | 116 | COM15  | 3963 | -30             |

| 17  | VDD    | -2270 | -1155         | 67        | INTRS  | 1230 | -1155         | 117 | COM14  | 3963 | 30              |

| 18  | VDD    | -2200 | -1155         | 68        | VSS    | 1300 | -1155         | 118 | COM13  | 3963 | 90              |

| 19  | VDD    | -2130 | -1155         | 69        | VSS    | 1370 | -1155         | 119 | COM12  | 3963 | 150             |

| 20  | DB0    | -2060 | -1155         | 70        | VSS    | 1440 | -1155         | 120 | COM11  | 3963 | 210             |

| 21  | DB1    | -1990 | -1155         | 71        | VSS    | 1510 | -1155         | 121 | COM10  | 3963 | 270             |

| 22  | DB2    | -1920 | -1155         | 72        | VSS    | 1580 | -1155         | 122 | COM9   | 3963 | 330             |

| 23  | DB3    | -1850 | -1155         | 73        | VSS    | 1650 | -1155         | 123 | COM8   | 3963 | 390             |

| 24  | DB4    | -1780 | -1155         | 74        | VSS    | 1720 | -1155         | 124 | COM7   | 3963 | 450             |

| 25  | DB5    | -1710 | -1155         | 75        | VSS    | 1790 | -1155         | 125 | COM6   | 3963 | 510             |

| 26  | DB6    | -1640 | -1155         | 76        | VSS    | 1860 | -1155         | 126 | COM5   | 3963 | 570             |

| 27  | DB7    | -1570 | -1155         | 77        | VSS    | 1930 | -1155         | 127 | COM4   | 3963 | 630             |

| 28  | VSS    | -1500 | -1155         | 78        | VR     | 2000 | -1155         | 128 | COM3   | 3963 | 690             |

| 29  | TEST2  | -1430 | -1155         | 79        | VSS    | 2070 | -1155         | 129 | COM2   | 3963 | 750             |

| 30  | TEST3  | -1360 | -1155         | 80        | TESTA0 | 2140 | -1155         | 130 | COM1   | 3963 | 810             |

| 31  | VSS    | -1290 | -1155         | 81        | TESTB0 | 2210 | -1155         | 131 | COM0   | 3963 | 870             |

| 32  | RS     | -1220 | -1155         | 82        | VSS    | 2280 | -1155         | 132 | COMS   | 3963 | 930             |

| 33  | VDD    | -1150 | -1155         | 83        | VLCD   | 2350 | -1155         | 133 | DUMMY4 | 3776 | 1117            |

| 34  | DUTY0  | -1080 | -1155         | 84        | VLCD   | 2420 | -1155         | 134 | DUMMY5 | 3696 | 1117            |

| 35  | VSS    | -1010 | -1155         | 85        | VLCD   | 2490 | -1155         | 135 | SEG0   | 3502 | 1117            |

| 36  | DUTY1  | -940  | -1155         | 86        | VLCD   | 2560 | -1155         | 136 | SEG1   | 3434 | 1117            |

| 37  | VDD    | -870  | -1155         | 87        | VLCD   | 2630 | -1155         | 137 | SEG2   | 3366 | 1117            |

| 38  | PS     | -800  | -1155         | 88        | VLCD   | 2700 | -1155         | 138 | SEG3   | 3298 | 1117            |

| 39  | VSS    | -730  | -1155         | 89        | TESTA1 | 2770 | -1155         | 139 | SEG4   | 3230 | 1117            |

| 40  | C68    | -660  | -1155         | 90        | TESTB1 | 2840 | -1155         | 140 | SEG5   | 3162 | 1117            |

| 41  | VDD    | -590  | -1155         |           | TESTA2 | 2910 | -1155         | 141 | SEG6   | 3094 |                 |

| 42  | E RDB  | -520  | -1155         | 92        | TESTB2 | 2980 | -1155         | 142 | SEG7   | 3026 | 1117            |

| 43  | RW WRB | -450  | -1155         | 93        | TESTA3 | 3050 | -1155         | 143 | SEG8   | 2958 | 1117            |

| 44  | VSS    | -380  | -1155         | 94        | TESTB3 | 3120 | -1155         | 144 | SEG9   | 2890 | 1117            |

| 45  | CS1B   | -310  | -1155         | 95        | TESTA4 | 3190 | -1155         | 145 | SEG10  | 2822 | 1117            |

| 46  | CS2    | -240  | -1155         | 96        | TESTB4 | 3260 | -1155         | 146 | SEG11  | 2754 | 1117            |

| 47  | VDD    | -170  | -1155         | 97        | RESETB | 3330 | -1155         | 147 | SEG12  | 2686 | 1117            |

| 48  | VCI    | -100  | -1155         | 98        | DUMMY2 | 3400 | -1155         | 148 | SEG13  | 2618 | 1117            |

| 49  | VCI    | -30   | -1155         | 99        | DUMMY3 | 3963 | -1060         | 149 | SEG14  | 2550 | 1117            |

| 50  | VCI    | 40    | -1155         | 100       | COM31  | 3963 | -990          | 150 | SEG15  | 2482 | 1117            |

**Table 2. Pad Center Coordinates (Continued)**

[Unit: um]

|            |             |                           |      |            |             |       |      | [Unit: µm] |             |                                                  |       |

|------------|-------------|---------------------------|------|------------|-------------|-------|------|------------|-------------|--------------------------------------------------|-------|

| Pad<br>No. | Pad<br>Name | Х                         | Y    | Pad<br>No. | Pad<br>Name | х     | Y    | Pad<br>No. | Pad<br>Name | Х                                                | Y     |

| 151        | SEG16       | 2414                      | 1117 | 201        | SEG66       | -986  | 1117 | 251        | COM42       | -3963                                            | 330   |

| 152        | SEG17       | 2346                      | 1117 | 202        | SEG67       | -1054 | 1117 | 252        | COM43       | -3963                                            | 270   |

| 153        | SEG18       | 2278                      | 1117 | 203        | SEG68       | -1122 | 1117 | 253        | COM44       | -3963                                            | 210   |

| 154        | SEG19       | 2210                      | 1117 | 204        | SEG69       | -1190 | 1117 | 254        | COM45       | -3963                                            | 150   |

| 155        | SEG20       | 2142                      | 1117 | 205        | SEG70       | -1258 | 1117 | 255        | COM46       | -3963                                            | 90    |

| 156        | SEG21       | 2074                      | 1117 | 206        | SEG71       | -1326 | 1117 | 256        | COM47       | -3963                                            | 30    |

| 157        | SEG22       | 2006                      | 1117 | 207        | SEG72       | -1394 | 1117 | 257        | COM48       | -3963                                            | -30   |

| 158        | SEG23       | 1938                      | 1117 | 208        | SEG73       | -1462 | 1117 | 258        | COM49       | -3963                                            | -90   |

| 159        | SEG24       | 1870                      | 1117 | 209        | SEG74       | -1530 | 1117 | 259        | COM50       | -3963                                            | -150  |

| 160        | SEG25       | 1802                      | 1117 | 210        | SEG75       | -1598 | 1117 | 260        | COM51       | -3963                                            | -210  |

| 161        | SEG26       | 1734                      | 1117 | 211        | SEG76       | -1666 | 1117 | 261        | COM52       | -3963                                            | -270  |

| 162        | SEG27       | 1666                      | 1117 | 212        | SEG77       | -1734 | 1117 | 262        | COM53       | -3963                                            | -330  |

| 163        | SEG28       | 1598                      | 1117 | 213        | SEG78       | -1802 | 1117 | 263        | COM54       | -3963                                            | -390  |

| 164        | SEG29       | 1530                      | 1117 | 214        | SEG79       | -1870 | 1117 | 264        | COM55       | -3963                                            | -450  |

| 165        | SEG30       | 1462                      | 1117 | 215        | SEG80       | -1938 | 1117 | 265        | COM56       | -3963                                            | -510  |

| 166        | SEG31       | 1394                      | 1117 | 216        | SEG81       | -2006 | 1117 | 266        | COM57       | -3963                                            | -570  |

| 167        | SEG32       | 1326                      | 1117 | 217        | SEG82       | -2074 | 1117 | 267        | COM58       | -3963                                            | -630  |

| 168        | SEG33       | 1258                      | 1117 | 218        | SEG83       | -2142 | 1117 | 268        | COM59       | -3963                                            | -690  |

| 169        | SEG34       | 1190                      | 1117 | 219        | SEG84       | -2210 | 1117 | 269        | COM60       | -3963                                            | -750  |

| 170        | SEG35       | 1122                      | 1117 | 220        | SEG85       | -2278 | 1117 | 270        | COM61       | -3963                                            | -810  |

| 171        | SEG36       | 1054                      | 1117 | 221        | SEG86       | -2346 | 1117 | 271        | COM62       | -3963                                            | -870  |

| 172        | SEG37       | 986                       | 1117 | 222        | SEG87       | -2414 | 1117 | 272        | COM63       | -3963                                            | -930  |

| 173        | SEG38       | 918                       | 1117 | 223        | SEG88       | -2482 | 1117 | 273        | COMS        | -3963                                            | -990  |

| 174        | SEG39       | 850                       | 1117 | 224        | SEG89       | -2550 | 1117 | 274        | DUMMY8      | -3963                                            | -1060 |

| 175        | SEG40       | 782                       | 1117 | 225        | SEG90       | -2618 | 1117 | 217        | DOIVIIVITO  | 3300                                             | 1000  |

| 176        | SEG41       | 714                       | 1117 | 226        | SEG91       | -2686 | 1117 |            | 1           | 1                                                |       |

| 177        | SEG42       | 646                       | 1117 | 227        | SEG92       | -2754 | 1117 |            | 1           | 1                                                |       |

| 178        | SEG43       | 578                       | 1117 | 228        | SEG93       | -2822 | 1117 |            |             |                                                  |       |

| 179        | SEG44       | 510                       | 1117 | 229        | SEG94       | -2890 | 1117 |            |             |                                                  |       |

| 180        | SEG45       | 442                       | 1117 | 230        | SEG95       | -2958 | 1117 |            | 1           | 1                                                |       |

| 181        | SEG46       | 374                       | 1117 | 231        | SEG96       | -3026 | 1117 |            |             |                                                  |       |

| 182        | SEG47       | 306                       | 1117 | 232        | SEG97       | -3094 | 1117 |            |             |                                                  |       |

| 183        | SEG48       | 238                       | 1117 | 233        | SEG98       | -3162 | 1117 |            | 1           | 1                                                |       |

| 184        | SEG49       | 170                       | 1117 | 234        | SEG99       | -3230 | 1117 |            |             |                                                  |       |

| 185        | SEG50       | 102                       | 1117 | 235        | SEG100      | -3298 | 1117 |            |             |                                                  |       |

| 186        | SEG51       | 34                        | 1117 | 236        | SEG101      | -3366 | 1117 |            | 1           | 1                                                |       |

| 187        | SEG52       | -34                       | 1117 | 237        | SEG102      | -3434 | 1117 |            |             |                                                  |       |

| 188        | SEG53       | -102                      | 1117 | 238        | SEG103      | -3502 | 1117 |            | 1           | 1                                                |       |

| 189        | SEG54       | -170                      | 1117 | 239        | DUMMY6      | -3696 | 1117 |            |             |                                                  |       |

| 190        | SEG55       | -238                      | 1117 | 240        | DUMMY7      | -3036 | 1117 |            |             |                                                  |       |

| 191        | SEG56       | -306                      | 1117 | 241        | COM32       | -3963 | 930  |            | +           |                                                  |       |

| 192        | SEG57       | -374                      | 1117 | 242        | COM33       | -3963 | 870  |            |             |                                                  |       |

| 193        | SEG58       | -374<br>-442              | 1117 | 242        | COM34       | -3963 | 810  |            |             |                                                  |       |

| 193        | SEG59       | - <del>44</del> 2<br>-510 | 1117 | 243        | COM35       | -3963 | 750  |            | +           | <del>                                     </del> |       |

| 195        | SEG60       | -510<br>-578              | 1117 | 245        | COM36       | -3963 | 690  |            | +           |                                                  |       |

| 195        | SEG61       | -578<br>-646              | 1117 | 245        | COM37       | -3963 | 630  |            | +           | <del>                                     </del> |       |

| 196        | SEG62       | -046<br>-714              | 1117 | 246        | COM38       | -3963 | 570  |            | +           |                                                  |       |

| 198        | SEG63       | -714<br>-782              | 1117 | 248        | COM39       | -3963 | 510  |            | +           | <del>                                     </del> |       |

| 198        | SEG64       | -782<br>-850              | 1117 | 248        | COM40       | -3963 | 450  |            | +           | <del>                                     </del> |       |

|            | SEG65       |                           |      |            | COM41       |       |      |            | +           |                                                  |       |

| 200        | 3EG03       | -918                      | 1117 | 250        | COIVI41     | -3963 | 390  |            |             | I                                                |       |

## **PIN DESCRIPTION**

#### **POWER SUPPLY**

**Table 3. Power Supply Pins Description**

| Name | I/O    | Description  |  |  |  |  |  |

|------|--------|--------------|--|--|--|--|--|

| VDD  | Supply | Power supply |  |  |  |  |  |

| VSS  | Supply | Ground       |  |  |  |  |  |

#### **LCD DRIVER SUPPLY**

**Table 4. LCD Driver Supply Pins Description**

| Name   | I/O | Description                                                                                                                                                                                                                            |  |  |  |  |  |

|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| VLCD   | 0   | LCD power supply output pin Connect this pin to VSS through capacitor.(Capacitor is greater than 1μF)                                                                                                                                  |  |  |  |  |  |

| DCDC4B | I   | 4 times boosting circuit enable input pin  – DCDC4B = "H": 3 times boosting  – DCDC4B = "L": 4 times boosting                                                                                                                          |  |  |  |  |  |

| VR     | I   | VLCD voltage adjustment pin It is valid only when internal voltage regulator resistors are not used (INTRS = "L").                                                                                                                     |  |  |  |  |  |

| VCI    | I   | This is the reference voltage for the voltage converter circuit for the LCD driving. Whether internal voltage converter use or not use, this pin should be fixed. The voltage should have the following range: $2.4V \le VCI \le 3.6V$ |  |  |  |  |  |

| VEXT   | I   | This is the external-input reference voltage (VREF) for the internal voltage regulator.  It is valid only when external VREF is used (REF = "L").  When using internal VREF, this pin is Open                                          |  |  |  |  |  |

| REF    | I   | Select the external VREF voltage via VEXT pin  REF = "L": using the external VREF  REF = "H": using the internal VREF                                                                                                                  |  |  |  |  |  |

## **SYSTEM CONTROL**

**Table 5. System Control Pins Description**

| Name  | I/O | Description                                                                                                                                                                                                                                                                               |                                         |            |  |  |  |  |  |

|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------|--|--|--|--|--|

| CL    | 0   | Display clock outpu                                                                                                                                                                                                                                                                       | Display clock output pin                |            |  |  |  |  |  |

| FRS   | 0   | Static driver segmer<br>This pin is used togo                                                                                                                                                                                                                                             | nt output pin ether with the FR pin.    |            |  |  |  |  |  |

| FR    | 0   | Static driver commo<br>This pin is used tog                                                                                                                                                                                                                                               | n output pin<br>ether with the FRS pin. |            |  |  |  |  |  |

| INTRS | -   | Internal resistor select pin This pin selects the resistors for adjusting VLCD voltage level.  - INTRS = "H": the internal resistors are used  - INTRS = "L": the external resistors are used  VLCD voltage is controlled by VR pin and external resistive divider.  (* refer to page 28) |                                         |            |  |  |  |  |  |

|       |     | The LCD driver duty ratio depends on the following table.                                                                                                                                                                                                                                 |                                         |            |  |  |  |  |  |

|       |     | DUTY1                                                                                                                                                                                                                                                                                     | DUTY0                                   | Duty ratio |  |  |  |  |  |

| DUTY0 |     | L                                                                                                                                                                                                                                                                                         | L                                       | 1/33       |  |  |  |  |  |

| DUTY1 | I   | L                                                                                                                                                                                                                                                                                         | Н                                       | 1/49       |  |  |  |  |  |

|       |     | Н                                                                                                                                                                                                                                                                                         | L                                       | 1/55       |  |  |  |  |  |

|       |     | Н                                                                                                                                                                                                                                                                                         | Н                                       | 1/65       |  |  |  |  |  |

|       |     |                                                                                                                                                                                                                                                                                           |                                         |            |  |  |  |  |  |

| НРМВ  | I   | Power control pin of the power supply circuits for LCD driver.  - HPMB = "H": normal mode  - HPMB = "L": high power mode                                                                                                                                                                  |                                         |            |  |  |  |  |  |

#### **MICROPROCESSOR INTERFACE**

**Table 6. Microprocessor Interface Pins Description**

| Name        | I/O   |                            | Description                                                                                                                                                                                                                                                                   |                           |                    |                                                          |                   |               |  |  |

|-------------|-------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------|----------------------------------------------------------|-------------------|---------------|--|--|

| RESETB      | I     |                            | Reset input pin When RESETB is "L", initialization is executed.                                                                                                                                                                                                               |                           |                    |                                                          |                   |               |  |  |

|             |       | Paralle                    | / Serial data                                                                                                                                                                                                                                                                 | input seled               | ct input           |                                                          |                   |               |  |  |

|             |       | PS                         | Interface<br>mode                                                                                                                                                                                                                                                             | Chip<br>select            | Data / instruction | Data                                                     | Read / Write      | Serial clock  |  |  |

| PS          | ı     | Н                          | Parallel                                                                                                                                                                                                                                                                      | CS1B,<br>CS2              | RS                 | DB0 to DB7                                               | E_RDB<br>RW_WRB   | -             |  |  |

|             |       | L                          | Serial                                                                                                                                                                                                                                                                        | CS1B,<br>CS2              | RS                 | SID (DB7)                                                | Write only        | SCLK (DB6)    |  |  |

|             |       |                            |                                                                                                                                                                                                                                                                               |                           |                    | d data from the o                                        |                   |               |  |  |

| C68         | I     | - PS =<br>- PS =<br>- PS = | Microprocessor interface select input pin  - PS = "H", C68 = "H": 6800-series parallel MPU interface  - PS = "H", C68 = "L": 8080-series parallel MPU interface  - PS = "L", C68 = "H": 4 pin-SPI serial MPU interface  - PS = "L", C68 = "L": 3 pin-SPI serial MPU interface |                           |                    |                                                          |                   |               |  |  |

| CS1B<br>CS2 | I     | Data/in                    | Chip select input pins Data/instruction I/O is enabled only when CS1B is "L" and CS2 is "H". When chip select is non-active, DB0 to DB7 may be high impedance.                                                                                                                |                           |                    |                                                          |                   |               |  |  |

| RS          | I     | - RS =<br>- RS =           | er select input<br>"H": DB0 to E<br>"L": DB0 to D<br>oin must be fix                                                                                                                                                                                                          | DB7 are dis<br>DB7 are co | ntrol data         | in case of 3 pin-                                        | SPI serial MPU i  | nterface mode |  |  |

|             |       | Read /                     | Write execution                                                                                                                                                                                                                                                               | on control                | pin                |                                                          |                   |               |  |  |

|             |       | C68                        | MPU Type                                                                                                                                                                                                                                                                      | RW_V                      | VRB                | ]                                                        | Description       |               |  |  |

| RW_WRB      | WRB I |                            | H 6800-series RW Read / Write control input pin - RW = "H": read - RW = "L": write                                                                                                                                                                                            |                           |                    |                                                          | nput pin          |               |  |  |

|             |       | L                          | 8080-series                                                                                                                                                                                                                                                                   | /W                        | R The              | e enable clock in<br>data on DB0 to I<br>of the /WR sign | DB7 are latched a | at the rising |  |  |

|             |       |                            |                                                                                                                                                                                                                                                                               | -                         | •                  |                                                          |                   |               |  |  |

**Table 6. Microprocessor Interface Pins Description (Continued)**

| Name             | I/O |                                       | Description                                                                                                                                                                                                                                                                                                      |       |                                                                                                                                                                                   |  |  |  |  |  |

|------------------|-----|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                  |     | Read / Write execution control pin    |                                                                                                                                                                                                                                                                                                                  |       |                                                                                                                                                                                   |  |  |  |  |  |

|                  |     | C68                                   | MPU Type                                                                                                                                                                                                                                                                                                         | E_RDB | Description                                                                                                                                                                       |  |  |  |  |  |

| E_RDB            | I   | Н                                     | 6800-series                                                                                                                                                                                                                                                                                                      | E     | Read/Write control input pin  - RW = "H": When E is "H", DB0 to DB7 are in an output status.  - RW = "L": The data on DB0 to DB7 are latched at the falling edge of the E signal. |  |  |  |  |  |

|                  |     | L                                     | 8080-series                                                                                                                                                                                                                                                                                                      | /RD   | Read enable clock input pin When /RD is "L", DB0 to DB7 are in an output status.                                                                                                  |  |  |  |  |  |

|                  |     |                                       |                                                                                                                                                                                                                                                                                                                  |       |                                                                                                                                                                                   |  |  |  |  |  |

| DB0<br>to<br>DB7 | I/O | bus. W<br>- DB0 1<br>- DB6:<br>- DB7: | 8-bit bi-directional data bus that is connected to the standard 8-bit microprocessor data bus. When the serial interface selected (PS = "L"),  — DB0 to DB5: high impedance  — DB6: serial input clock (SCLK)  — DB7: serial input data (SID)  When chip select is not active, DB0 to DB7 may be high impedance. |       |                                                                                                                                                                                   |  |  |  |  |  |

| TESTs            | I/O | These                                 | These are pins for chip test. They are set to open.                                                                                                                                                                                                                                                              |       |                                                                                                                                                                                   |  |  |  |  |  |

NOTE: DUMMYs – These pins should be opened (floated).

#### **LCD DRIVER OUTPUTS**

**Table 7. LCD Driver Output Pins Description**

| Name         | I/O |                                                                                                                 | D      | escription                   |                         |  |  |  |  |  |

|--------------|-----|-----------------------------------------------------------------------------------------------------------------|--------|------------------------------|-------------------------|--|--|--|--|--|

|              |     | LCD segment driver ou<br>The display data and the                                                               |        | ol the output voltage of se  | gment driver.           |  |  |  |  |  |

|              |     | Dienlay data                                                                                                    | - FD   | Segment driv                 | er output voltage       |  |  |  |  |  |

|              |     | Display data                                                                                                    | FR     | Normal display               | Reverse display         |  |  |  |  |  |

| SEG0         |     | Н                                                                                                               | Н      | VLCD                         | V2                      |  |  |  |  |  |

| to<br>SEG103 | 0   | Н                                                                                                               | L      | Vss                          | V3                      |  |  |  |  |  |

| 020.00       |     | L                                                                                                               | Н      | V2                           | VLCD                    |  |  |  |  |  |

|              |     | L                                                                                                               | L      | V3                           | Vss                     |  |  |  |  |  |

|              |     | Power save                                                                                                      | e mode | Vss                          | Vss                     |  |  |  |  |  |

|              |     |                                                                                                                 |        |                              |                         |  |  |  |  |  |

|              |     | LCD common driver outputs The internal scanning data and FR signal control the output voltage of common driver. |        |                              |                         |  |  |  |  |  |

|              |     | Scan data                                                                                                       | FR     | Common driver output voltage |                         |  |  |  |  |  |

| 00140        |     | Н                                                                                                               | Н      | ,                            | Vss                     |  |  |  |  |  |

| COM0<br>to   | 0   | Н                                                                                                               | L      | V                            | /LCD                    |  |  |  |  |  |

| COM63        |     | L                                                                                                               | Н      |                              | V1                      |  |  |  |  |  |

|              |     | L                                                                                                               | L      |                              | V4                      |  |  |  |  |  |

|              |     | Power save                                                                                                      | e mode | ,                            | Vss                     |  |  |  |  |  |

|              |     |                                                                                                                 |        |                              |                         |  |  |  |  |  |

| COMS         | 0   | Common output for the The output signals of to                                                                  |        | When not used, these pi      | ns should be left open. |  |  |  |  |  |

#### **FUNCTIONAL DESCRIPTION**

#### MICROPROCESSOR INTERFACE

#### **Chip Select Input**

There are CS1B and CS2 pins for chip selection. The S6B0725A can interface with an MPU only when CS1B is "L" and CS2 is "H". When these pins are set to any other combination, RS, E\_RDB, and RW\_WRB inputs are disabled and DB0 to DB7 are to be high impedance. And, in case of serial interface, the internal shift register and the counter are reset.

#### Parallel / Serial Interface

S6B0725A has four types of interface with an MPU, which are two serial and two parallel interfaces. This parallel or serial interface is determined by PS pin as shown in table 8.

PS CS1B CS<sub>2</sub> **C68** Interface mode Type Н 6800-series MPU mode Н Parallel CS1B CS2 L 8080-series MPU mode 4 pin-SPI serial MPU mode Н CS1B L Serial CS2 L 3 pin-SPI serial MPU mode

Table 8. Parallel / Serial Interface Mode

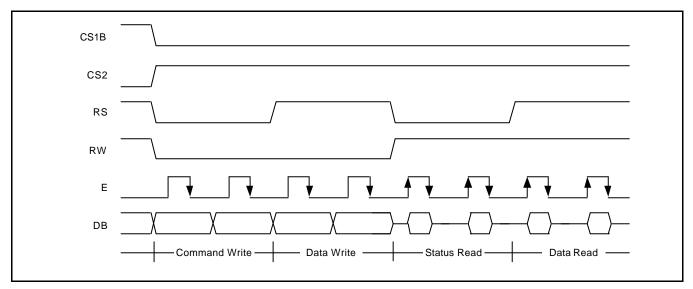

#### Parallel Interface (PS = "H")

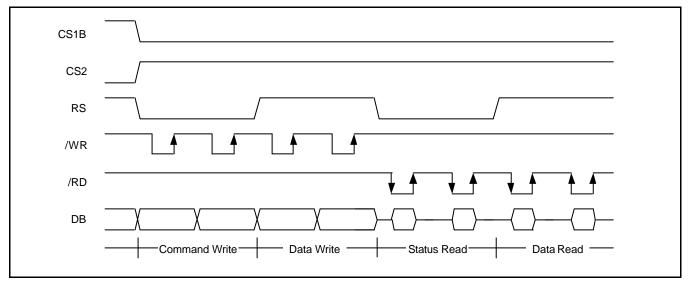

The 8-bit bi-directional data bus is used in parallel interface and the type of MPU is selected by C68 as shown in table 9. The type of data transfer is determined by signals at RS, E\_RDB and RW\_WRB as shown in table 10.

CS1B E RDB MPU bus **C68** CS2 RS RW WRB DB0 to DB7 CS<sub>2</sub> Ε Н CS1B RS RW DB0 to DB7 6800-series CS1B CS<sub>2</sub> RS /RD /WR DB0 to DB7 8080-series

**Table 9. Microprocessor Selection for Parallel Interface**

| Table | 10. | Paralle | I Data | Transf | er |

|-------|-----|---------|--------|--------|----|

|-------|-----|---------|--------|--------|----|

| Common | 6800-        | series         | 8080-          | series          |                                           |

|--------|--------------|----------------|----------------|-----------------|-------------------------------------------|

| RS     | E_RDB<br>(E) | RW_WRB<br>(RW) | E_RDB<br>(/RD) | RW_WRB<br>(/WR) | Description                               |

| Н      | Н            | Н              | L              | Н               | Display data read out                     |

| Н      | Н            | L              | Н              | L               | Display data write                        |

| L      | Н            | Н              | L              | Н               | Register status read                      |

| L      | Н            | L              | Н              | L               | Writes to internal register (instruction) |

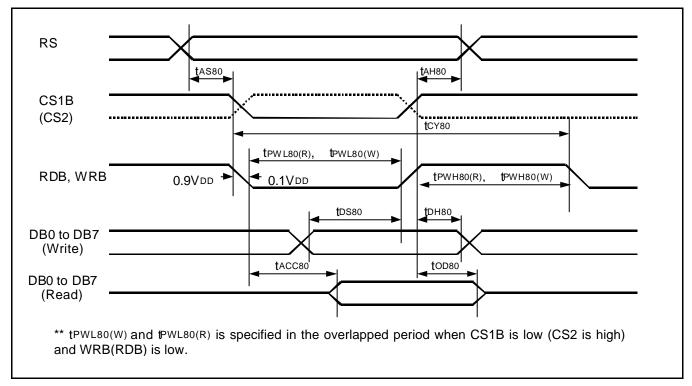

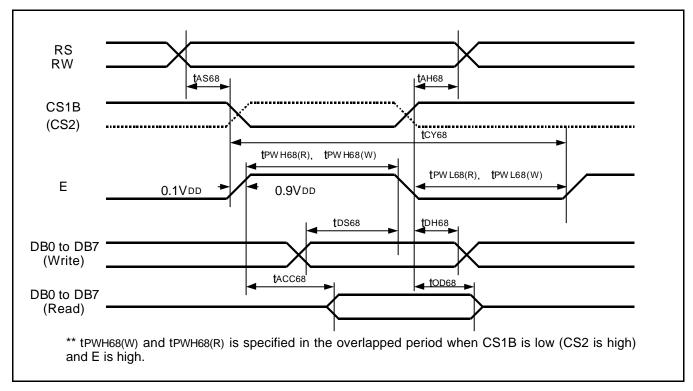

Figure 2-1. 6800-Series MPU Interface protocol (PS="H", C68="H")

Figure 2-2. 8080-Series MPU Interface Protocol (PS="H", C68="L")

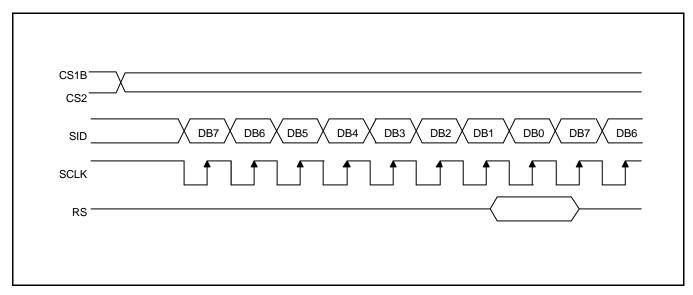

#### Serial Interface (PS = "L")

When the S6B0725A is active (CS1B="L", CS2="H'), serial data (DB7) and serial clock (DB6) inputs are enabled. And not active, the internal 8-bit shift register and the 3-bit counter are reset. The display data/command indication may be controlled either via software or the Register Select (RS) Pin, based on the setting of C68. When the RS pin is used (PS = "H"), data is display data when RS is high, and command data when RS is low. When RS is not used (C68 = "L"), the LCD Driver will receive command from MPU by default. If messages on the data pin are data rather than command, MPU should send Data Direction command (10000000) to control the data direction and then one more command to define the number of data bytes will be write. After these two continuous commands are sending, the following messages will be data rather than command. Serial data can be read on the rising edge of serial clock going into DB6 and processed as 8-bit parallel data on the eighth serial clock. And the DDRAM column address pointer will be increased by one automatically. The next bytes after the display data string is handled as command data.

Serial data can be read on the rising edge of serial clock going into DB6 and processed as 8-bit parallel data on the eighth serial clock. Since the clock signal (DB6) is easy to be affected by the external noise caused by the line length, the operation check on the actual machine is recommended.

The serial interface type is selected by setting C68 as shown in table 11.

| Serial Mode           | PS | C68 | Chip Select | Register Select | Serial Data / Clock input |

|-----------------------|----|-----|-------------|-----------------|---------------------------|

| 4 pin SPI serial mode | L  | Н   | CS1B, CS2   | RS pin          | DB7 / DB6                 |

| 3 pin SPI serial mode | L  | L   | CS1B, CS2   | Software        | DB7 / DB6                 |

Table 11. Parallel / Serial Interface Mode

#### 4 Pin SPI Serial Interface (PS = "L", C68 = "H")

In 4-pin serial interface mode, RS pin is used for indicating whether serial data input is display or instruction data. Data is display data when RS is high and instruction data when RS is low.

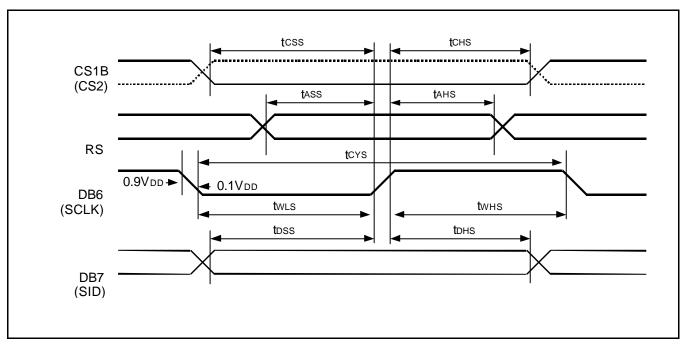

Figure 3. 4 Pin SPI serial Interface Timing (RS used)

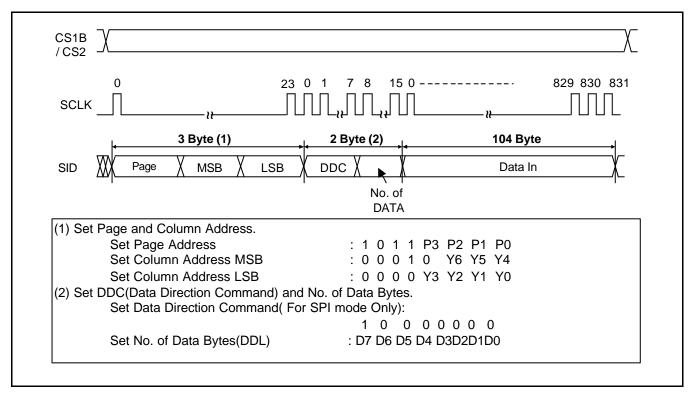

#### 3 Pin-SPI Interface (PS = "L", C68 = "L")

In 3-Pin SPI Interface mode, the pre-defined instruction called Display Data Length, is used to indicate whether serial data input is display or instruction data instead of RS pin. The data is handled as instruction data until the Display Data Length instruction is issued. This Display Data Length instruction consists of two bytes instruction. The first byte instruction enables the next instruction to be valid, and the data of the second byte indicates that a specified number of display data bytes (1 to 256) are to be transmitted. The next byte after the display data string is handled as instruction data. For details, refers to figure 4.

Figure 4. 3 Pin SPI Timing (RS is not used)

This command is used in 3-Pin SPI mode only. It will be two continuous commands, the first byte controls the data direction and informs the LCD driver the second byte will be number of data bytes will be write. After these two commands sending out, the following messages will be data. If data is stopped in transmitting, it is not valid data. New data will be transferred serially with most significant bit first.

#### \*NOTES:

- In spite of transmission of data, if CS1B will be disable, state terminates abnormally. Next state is initialized.

- The number of writing display data = DDL register value + 1

#### **Busy Flag**

The busy flag indicates whether the S6B0725A is operating or not. When DB7 is "H" in read status operation, this device is in busy status and will accept only read status instruction. If the cycle time is correct, the microprocessor needs not to check this flag before each instruction, which improves the MPU performance.

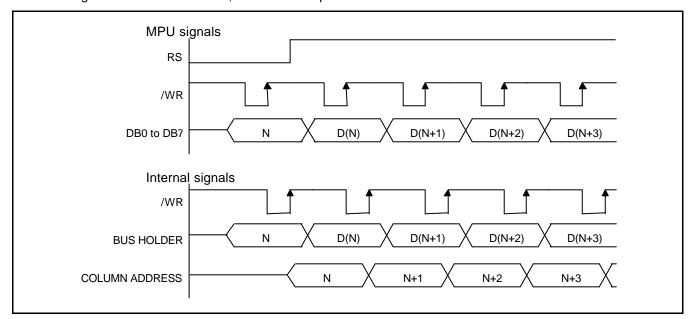

#### **Data Transfer**

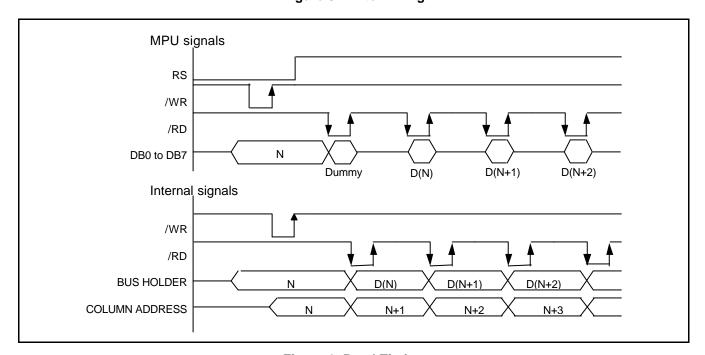

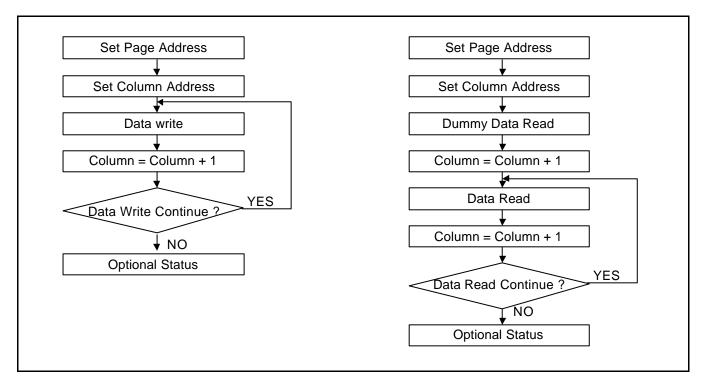

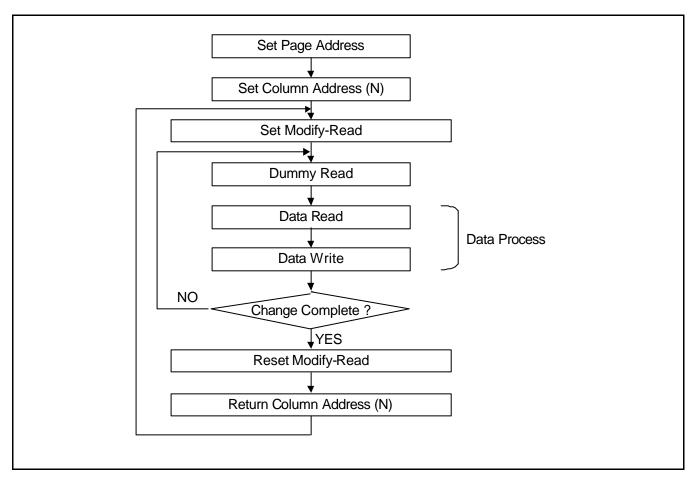

The S6B0725A uses bus holder and internal data bus for data transfer with the MPU. When writing data from the MPU to on-chip RAM, data is automatically transferred from the bus holder to the RAM as shown in figure 5. And when reading data from on-chip RAM to the MPU, the data for the initial read cycle is stored in the bus holder (dummy read) and the MPU reads this stored data from bus holder for the next data read cycle as shown in figure 6. This means that a dummy read cycle must be inserted between each pair of address sets when a sequence of address sets is executed. Therefore, the data of the specified address cannot be output with the read display data instruction right after the address sets, but can be output at the second read of data.

Figure 5. Write Timing

Figure 6. Read Timing

#### **DISPLAY DATA RAM (DDRAM)**

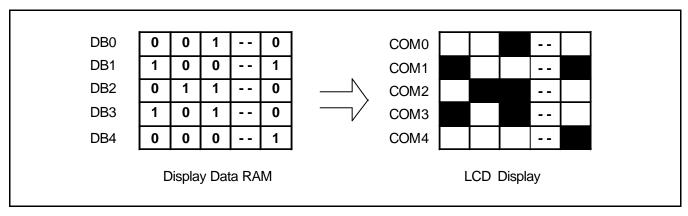

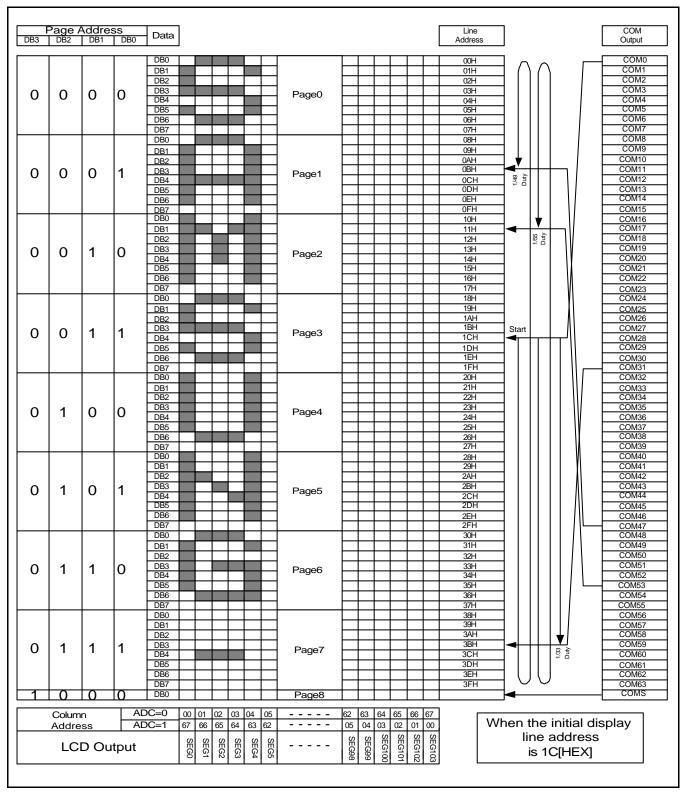

The Display Data RAM stores pixel data for the LCD. It is 65-row by 104-column addressable array. Each pixel can be selected when the page and column addresses are specified. The 65 rows are divided into 8 pages of 8 lines and the 9th page with a single line (DB0 only). Data is read from or written to the 8 lines of each page directly through DB0 to DB7. The display data of DB0 to DB7 from the microprocessor correspond to the LCD common lines as shown in figure 7. The microprocessor can read from and write to RAM through the I/O buffer. Since the LCD controller operates independently, data can be written into RAM at the same time as data is being displayed without causing the LCD flicker.

Figure 7. RAM-to-LCD Data Transfer

#### **Page Address Circuit**

This circuit is for providing a page address to Display Data RAM shown in figure 9. It incorporates 4-bit page address register changed by only the "Set Page" instruction. Page Address 8 (DB3 is "H", but DB2, DB1 and DB0 are "L") is a special RAM area for the icons and display data DB0 is only valid. When Page Address is above 8, it is impossible to access to on-chip RAM.

#### **Line Address Circuit**

This circuit assigns DDRAM a line address corresponding to the first line (COM0) of the display. Therefore, by setting line address repeatedly, it is possible to realize the screen scrolling and page switching without changing the contents of on-chip RAM as shown in figure 9. It incorporates 6-bit line address register changed by only the Initial Display Line instruction and 6-bit counter circuit. At the beginning of each LCD frame, the contents of register are copied to the line counter which is increased by CL signal and generates the line address for transferring the 104-bit RAM data to the display data latch circuit. However, display data of icons are not scrolled because the MPU cannot access line address of icons.

#### **Column Address Circuit**

Column address circuit has a 7-bit preset counter that provides column address to the Display Data RAM as shown in figure 9. When Set Column Address MSB / LSB instruction is issued, 7-bit [Y6:Y0] is updated. And, since this address is increased by 1 each a Read or Write data instruction, microprocessor can access the display data continuously. However, the counter is not increased and locked if a non-existing address above 67H. It is unlocked if a column address is set again by set Column Address MSB/LSB instruction. And the column address counter is independent of page address register.

ADC Select instruction makes it possible to invert the relationship between the column address and the segment outputs. It is necessary to rewrite the display data on built-in RAM after issuing ADC Select instruction. Refer to the following figure 8.

| SEG output             | SEG<br>0 | SEG<br>1 | SEG<br>2 | SEG<br>3 | <br>SEG<br>100 | SEG<br>101 | SEG<br>102 | SEG<br>103 |

|------------------------|----------|----------|----------|----------|----------------|------------|------------|------------|

| Column address [Y7:Y0] | 00H      | 01H      | 02H      | 03H      | <br>64H        | 65H        | 66H        | 67H        |

| Display data           | 1        | 0        | 1        | 0        | 1              | 1          | 0          | 0          |

| LCD panel display      |          |          |          |          |                |            |            |            |

| ( ADC = 0 )            |          |          |          |          |                |            |            |            |

|                        | <b>A</b> |          |          |          |                |            |            | <b>A</b>   |

|                        |          |          |          |          |                |            |            |            |

|                        | <b>\</b> |          |          |          |                |            |            | <b>♦</b>   |

| LCD panel display      |          |          |          |          |                |            |            |            |

| ( ADC = 1 )            |          |          |          |          |                |            |            |            |

Figure 8. The Relationship between the Column Address and the Segment Outputs

#### **Segment Control Circuit**

This circuit controls the display data by the display ON / OFF, reverse display ON / OFF and entire display ON / OFF instructions without changing the data in the display data RAM.

Figure 9. Display Data RAM Map

#### LCD DISPLAY CIRCUITS

#### Oscillator

This is completely on-chip oscillator and its frequency is nearly independent of VDD. This oscillator signal is used in display timing generation circuit.

#### **Display Timing Generator Circuit**

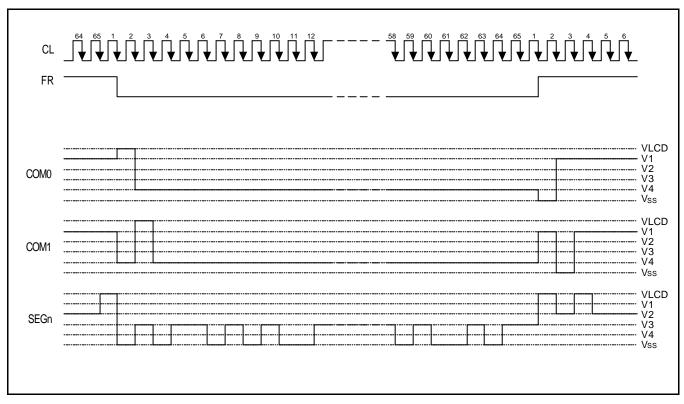

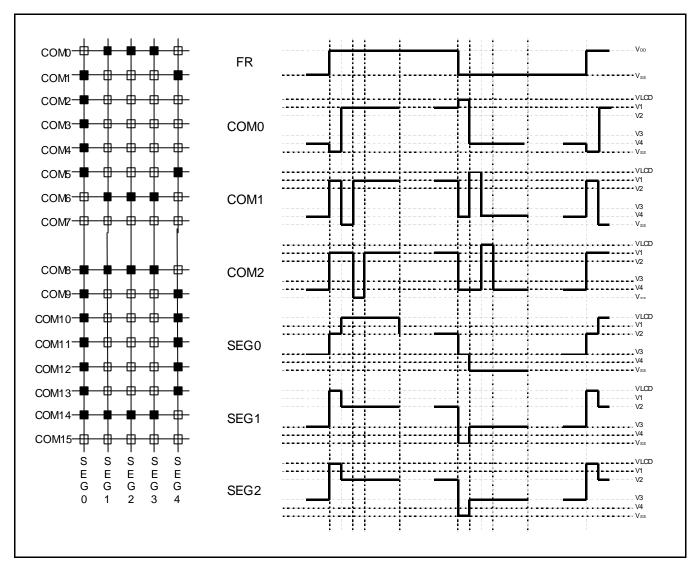

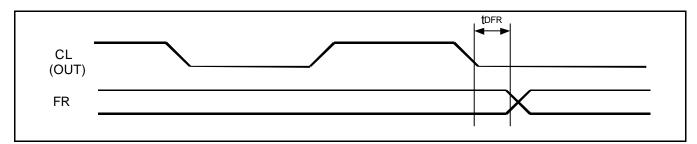

This circuit generates some signals to be used for displaying LCD. The display clock, CL generated by oscillation clock, generates a clock to the line counter and a latch signal to the display data latch. The line address of on-chip RAM is generated in synchronization with the display clock (CL) and the 104-bit display data is latched by the display data latch circuit in synchronization with the display clock. The display data which is read to the LCD driver is completely independent of the access to the display data RAM from the microprocessor. The LCD AC signal, FR is generated from the display clock. 2-frame AC driver waveforms with internal timing signal are shown in figure 10.

Figure 10. 2-frame AC Driving Waveform (Duty Ratio = 1/65)

#### **Common Output Control Circuit**

This circuit controls the relationship between the number of common output and specified duty ratio. SHL Select Instruction specifies the scanning direction of the common output pins.

Table 12. The Relationship between Duty Ratio and Common Output

|      |     |               |                |                | Common ou      | utput pins     |                |                |      |

|------|-----|---------------|----------------|----------------|----------------|----------------|----------------|----------------|------|

| Duty | SHL | COM<br>[0:15] | COM<br>[16:23] | COM<br>[24:26] | COM<br>[27:36] | COM<br>[37:39] | COM<br>[40:47] | COM<br>[48:63] | COMS |

| 4/00 | 0   | COM[0:15]     |                |                | *NC            |                |                | COM[16:31]     | COMC |

| 1/33 | 1   | COM[31:16]    | *NC            |                |                |                |                | COM[15:0]      | COMS |

| 1/49 | 0   | COM[0         | 0:23]          |                | *NC            |                | COM            | [24:47]        | COME |

| 1/49 | 1   | COM[4         | 7:24]          |                | *NC            |                |                | [23:0]         | COMS |

| 1/55 | 0   |               | COM[0:26]      |                | *NC            |                | COM[27:53]     |                | COMS |

| 1/55 | 1   | (             | COM[53:27]     |                | *NC COM[26:0]  |                |                |                | COMS |

| 4/05 | 0   | COM[0:63]     |                |                |                |                |                |                | COMC |

| 1/65 | 1   |               |                |                | COM[63:0]      |                | •              |                | COMS |

\*NC: No Connection

#### LCD DRIVER CIRCUITS

This driver circuit is configured by 66-channel (including 2 COMS channels) common driver and 104-channel segment driver. This LCD panel driver voltage depends on the combination of display data and FR signal.

Figure 11. Segment and Common Timing

#### **POWER SUPPLY CIRCUITS**

The power supply circuits generate the voltage levels necessary to drive liquid crystal driver circuits with low-power consumption and the fewest components. There are voltage converter circuits, voltage regulator circuits, and voltage follower circuits. They are controlled by power control instruction. For details, refers to "Instruction Description".

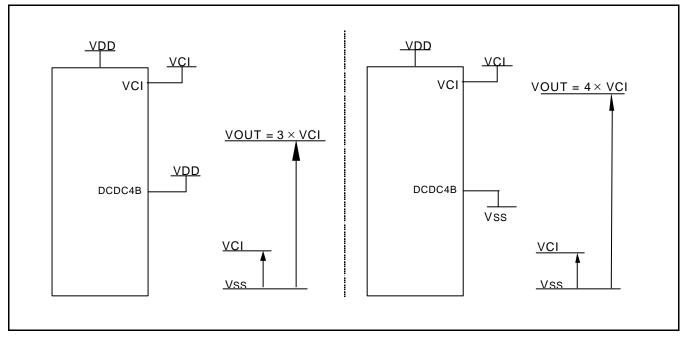

#### **Voltage Converter Circuits**

These circuits boost up the electric potential between VCI and VSS to 3 or 4 times toward positive side.

Figure 12. Three Times Boosting Circuit

Figure 13. Four Times Boosting Circuit

<sup>\*</sup> The VCI voltage range must be set so that the VOUT (Voltage converter output) does not exceed the absolute maximum rating value

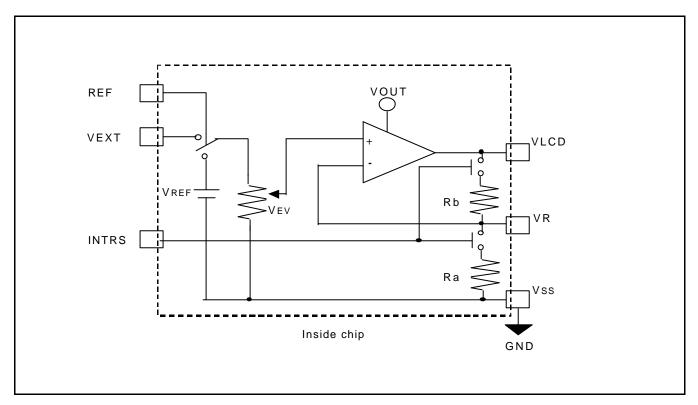

#### **Voltage Regulator Circuits**

The function of the internal voltage regulator circuits is to determine liquid crystal operating voltage, VLCD, by adjusting resistors, Ra and Rb, within the range of |VLCD| < |VOUT|. Because VOUT is the operating voltage of operational-amplifier circuits shown in figure 14, it is necessary to be applied internally.

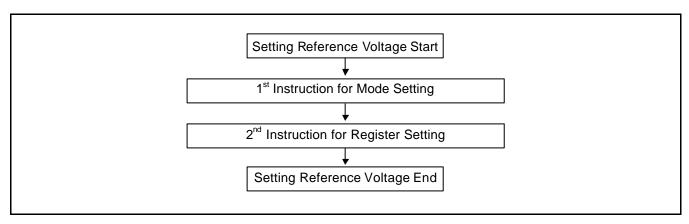

For the Eq. 1, we determine VLCD by Ra, Rb and VEV. The Ra and Rb are connected internally or externally by INTRS pin. And VEV called the voltage of electronic volume is determined by Eq. 2, where the parameter  $\alpha$  is the value selected by instruction, "Set Reference Voltage Register", within the range 0 to 63. VREF voltage at Ta = 25°C is shown in table 13.

VLCD =

$$(1 + \frac{Rb}{Ra}) \times VEV [V] ----- (Eq. 1)$$

$$VEV = (1 - \frac{(63 - \alpha)}{162}) \times VREF [V] ----- (Eq. 2)$$

Table 13. VREF Voltage at Ta = 25 °C

| REF | Temp. coefficient | VREF [V] |  |  |

|-----|-------------------|----------|--|--|

| Н   | -0.05% / °C       | 2.1      |  |  |

| L   | External input    | VEXT     |  |  |

Table 14. Electronic Contrast Control Register (64 Steps)

| SV5 | SV4 | SV3 | SV2 | SV1 | SV0 | Reference voltage parameter (a) | VLCD    | Contrast |

|-----|-----|-----|-----|-----|-----|---------------------------------|---------|----------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0                               | Minimum | Low      |

| 0   | 0   | 0   | 0   | 0   | 1   | 1                               |         |          |

| :   | :   | :   | :   | :   | :   | :                               | :       | :        |

| :   | :   | :   | :   | :   | :   | :                               | :       | :        |

| 1   | 0   | 0   | 0   | 0   | 0   | 32 (default)                    | :       | :        |

| :   | :   | :   | :   | :   | :   | :                               | :       | :        |

| :   | :   | :   | :   | :   | :   | :                               | :       | :        |

| 1   | 1   | 1   | 1   | 1   | 0   | 62                              |         |          |

| 1   | 1   | 1   | 1   | 1   | 1   | 63                              | Maximum | High     |

Figure 14. Internal Voltage Regulator Circuit

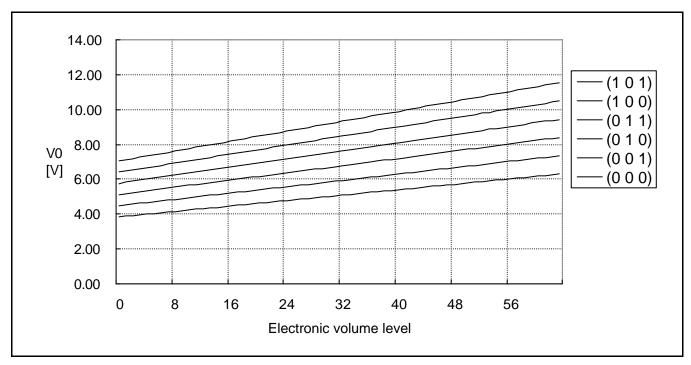

#### In Case of Using Internal Resistors, Ra and Rb (INTRS = "H")

When INTRS pin is "H", resistor Ra is connected internally between VR pin and VSS, and Rb is connected between VLCD and VR. We determine VLCD by two instructions, "Regulator Resistor Select" and "Set Reference Voltage".

|               | 3-bit data settings (R2 R1 R0) |       |     |     |     |       |                  |                  |  |  |  |

|---------------|--------------------------------|-------|-----|-----|-----|-------|------------------|------------------|--|--|--|

|               | 0 0 0                          | 0 0 1 | 010 | 011 | 100 | 1 0 1 | 110              | 111              |  |  |  |

| 1 + (Rb / Ra) | 3.0                            | 3.5   | 4.0 | 4.5 | 5.0 | 5.5   | Not<br>available | Not<br>available |  |  |  |

Table 15. Internal Rb / Ra ratio depending on 3-bit data (R2 R1 R0)

The following figure shows VLCD voltage measured by adjusting internal regulator resistor ratio (Rb / Ra) and 6-bit electronic volume registers for each temperature coefficient at Ta = 25 °C.

Figure 15. Electronic Volume Level

#### In Case of Using External Resistors, Ra and Rb (INTRS = "L")

When INTRS pin is "L", it is necessary to connect external regulator resistor Ra between VR and VSS, and Rb between VLCD and VR.

Example: For the following requirements

- 1. LCD driver voltage, VLCD = 6V

- 2. 6-bit reference voltage register = (1, 0, 0, 0, 0, 0)

- 3. Maximum current flowing Ra, Rb = 1 uA

From Eq. 1

Rb

$$6 = (1 + \frac{Rb}{Ra}) \times VEV [V] ----- (Eq. 3)$$

VEV =

$$(1 - \frac{(63 - 32)}{162})$$

x 2.1  $\cong$  1.698 [V] ----- (**Eq. 4**)

From requirement 3.

From equations Eq. 3, 4 and 5

$Ra \cong 1.698 [M\Omega]$

$Rb \cong 4.302 [M\Omega]$

The following table shows the range of VLCD depending on the above requirements.

Table 16. VLCD Depending on Electronic Volume Level

|      |      | Electronic volume level |      |  |      |  |  |  |  |  |  |

|------|------|-------------------------|------|--|------|--|--|--|--|--|--|

|      | 0    |                         | 32   |  | 63   |  |  |  |  |  |  |

| VLCD | 4.53 |                         | 6.00 |  | 7.42 |  |  |  |  |  |  |

#### **Voltage Follower Circuits**

VLCD voltage is resistively divided into four voltage levels (V1, V2, V3, V4), and those output impedance are converted by the voltage follower for increasing drive capability. The following table shows the relationship between V1 to V4 level and each duty ratio.

Table 17. The Relationship between V1 to V4 Level and Duty Ratio

| Duty ratio | DUTY1 | DUTY0 | LCD bias | V1         | V2         | V3         | V4         |

|------------|-------|-------|----------|------------|------------|------------|------------|

| 1/33       | ı     | ı     | 1/5      | (4/5) VLCD | (3/5) VLCD | (2/5) VLCD | (1/5) VLCD |

| 1/33       | ı     | L     | 1/6      | (5/6) VLCD | (4/6) VLCD | (2/6) VLCD | (1/6) VLCD |

| 1/49       | ı     | Н     | 1/6      | (5/6) VLCD | (4/6) VLCD | (2/6) VLCD | (1/6) VLCD |

| 1/49       | ı     | 11    | 1/8      | (7/8) VLCD | (6/8) VLCD | (2/8) VLCD | (1/8) VLCD |

| 1/55       | Н     | ı     | 1/6      | (5/6) VLCD | (4/6) VLCD | (2/6) VLCD | (1/6) VLCD |

| 1/55       | П     | L     | 1/8      | (7/8) VLCD | (6/8) VLCD | (2/8) VLCD | (1/8) VLCD |

| 1/65       | Н     | Н     | 1/7      | (6/7) VLCD | (5/7) VLCD | (2/7) VLCD | (1/7) VLCD |

| 1/05       | 17    | 11    | 1/9      | (8/9) VLCD | (7/9) VLCD | (2/9) VLCD | (1/9) VLCD |

#### **High Power Mode**

The power supply circuit equipped in the S6B0725A for LCD drive has very low power consumption (in normal mode: HPMB = "H"). If use for LCD panels with large loads, this low-power power supply may cause display quality to degrade. When this occurs, setting the HPMB pin to "L" (high power mode) can improve the quality of the display.

#### **RESET CIRCUIT**

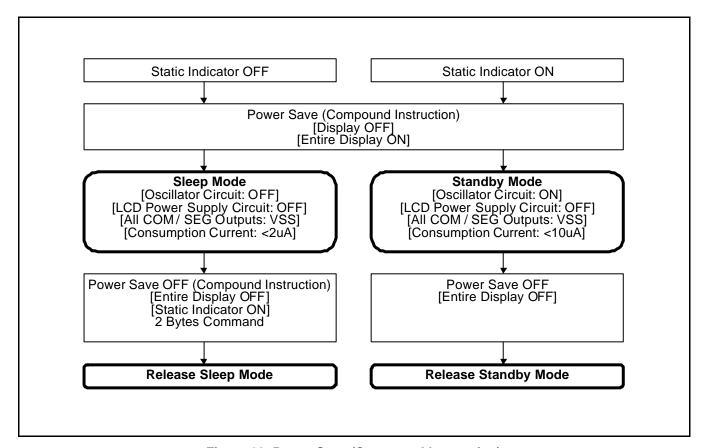

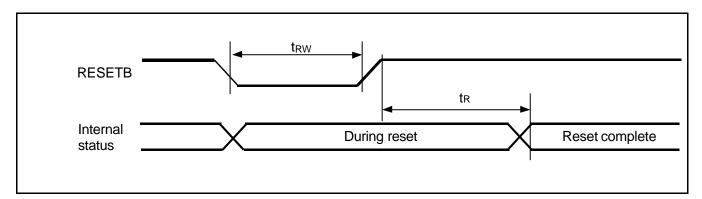

Setting RESETB to "L" or Reset instruction can initialize internal function. When RESETB becomes "L", the initialized driver has following states.

Display ON / OFF: OFF

Entire display ON / OFF: OFF (normal)

ADC select: OFF (normal)

Reverse display ON / OFF: OFF (normal) Power control register (VC, VR, VF) = (0, 0, 0) Serial interface internal register data clear

LCD bias ratio: 1/9 (1/65 duty), 1/8 (1/55 duty), 1/8 (1/49 duty), 1/6 (1/33 duty)

On-chip oscillator OFF Power save release Read-modify-write: OFF SHL select: OFF (normal) Static indicator mode: OFF

Static indicator register: (S1, S0) = (0, 0)

Display start line: 0 (first) Column address: 0 Page address: 0

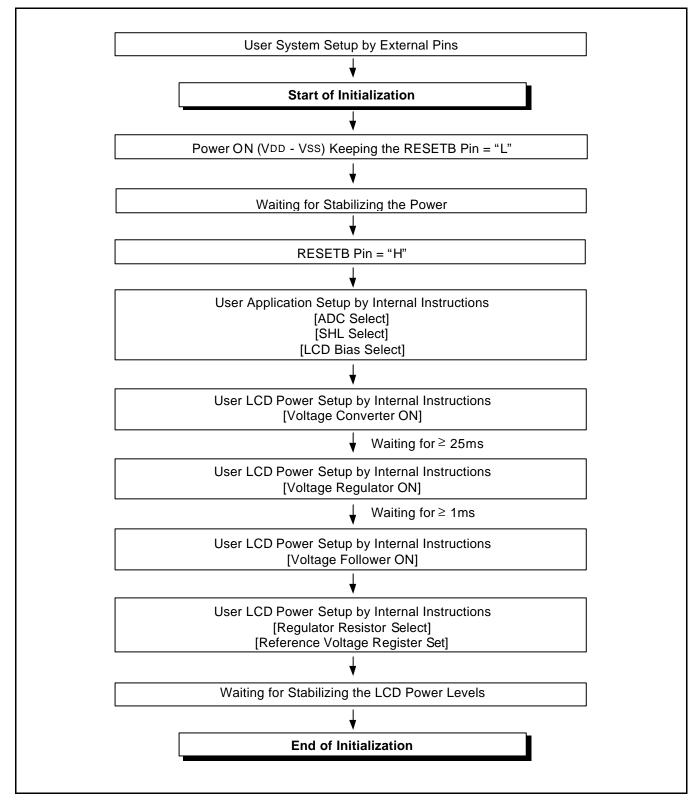

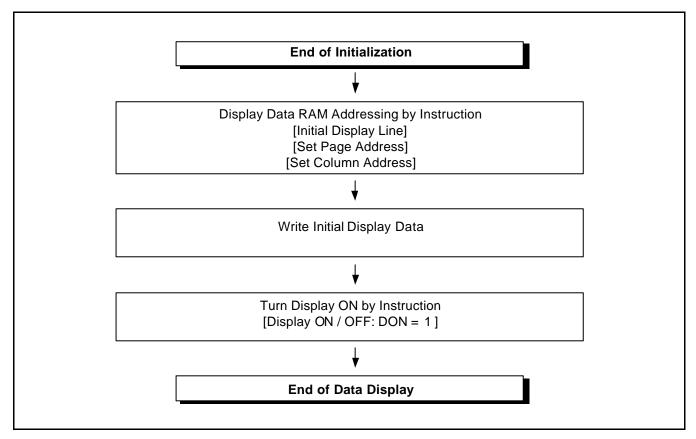

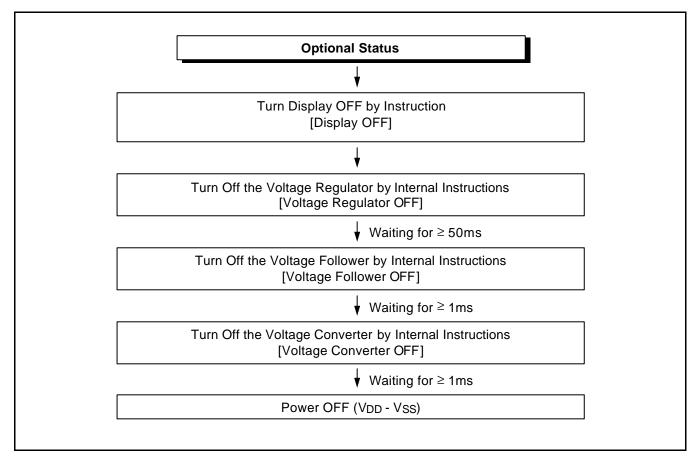

Regulator resistor select register: (R2, R1, R0) = (0, 1, 1)