# GUARANTEED LOW SKEW CMOS 20 OUTPUT CLOCK DRIVER/BUFFER

### **FEATURES:**

- 20 output, low skew clock signal buffer

- High drive FCT-type outputs

- Reduced swing TTL outputs for low noise

- Input hysteresis for better noise margin

- Monitor output

- Guaranteed low skew

- -0.5ns output skew

- 0.7ns pulse skew

- 1ns part-to-part skew

- Available in 40-pin QVSOP

### **DESCRIPTION:**

The QS5820T clock driver/buffer circuits can be used for clock distribution schemes where low skew, high speed, and small footprint are primary concerns. The QS5820T offers four banks of five non-inverting outputs. Designed in IDT's proprietary QCMOS process, this device provides low propagation delay buffering with on-chip skew of 0.5ns for same-transition, same-bank signals. The QS5820T provides major skew advantages over octal type devices where total part-to-part skew (tsk(t)) of >1ns is unacceptable. Furthermore, board area consumed by the QVSOP package is almost one-third that of the typical SOIC package offered for octal devices. This clock buffer product is designed for use in high performance workstation, multi-board computing and telecommunications systems. The QS5820T is available in the 40-pin QVSOP package which offers the world's smallest logic footprint.

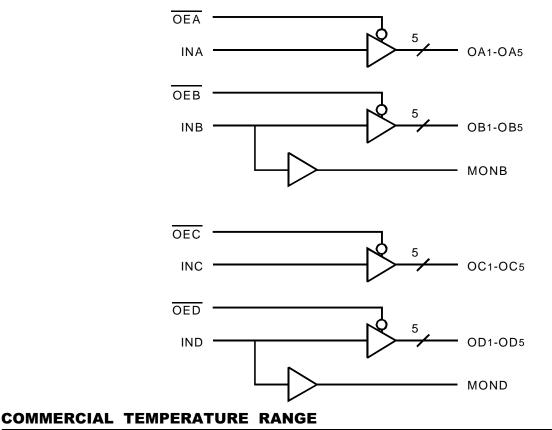

# **FUNCTIONAL BLOCK DIAGRAM**

#### **DECEMBER 2000**

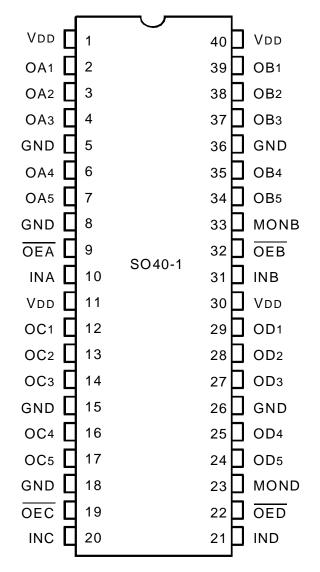

### **PIN CONFIGURATION**

QVSOP TOP VIEW

### ABSOLUTE MAXIMUM RATINGS (1)

| Symbol               | Rating                                 | Max.        | Unit |

|----------------------|----------------------------------------|-------------|------|

| VTERM <sup>(2)</sup> | Supply Voltage to Ground               | –0.5 to +7  | V    |

| VTERM <sup>(3)</sup> | DC Switch Voltage Vs                   | –0.5 to +7  | V    |

| VTERM <sup>(3)</sup> | DC Input Voltage VIN                   | –0.5 to +7  | V    |

| VAC                  | AC Input Voltage (pulse width ≤20ns)   | -3          | V    |

|                      | DC Input Diode Current with VIN < 0    | -20         | mA   |

| Ιουτ                 | DC Output Current Max Sink Current/Pin | 120         | mA   |

| Рмах                 | Maximum Power Dissipation              | 1.2         | W    |

| Tstg                 | Storage Temperature Range              | -65 to +150 | °C   |

NOTES:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. VDD Terminals.

3. All terminals except VDD.

#### **CAPACITANCE** (T<sub>A</sub> = 25° C, f = 1MHz, V<sub>IN</sub> = 0V, V<sub>OUT</sub> = 0V)

| •/ / . • / • • | -(   |      |      | ' |

|----------------|------|------|------|---|

| Pins           | Тур. | Max. | Unit |   |

5

8

pF

All Pins

NOTE:

1. Capacitance is characterized but not tested.

#### **PIN DESCRIPTION**

| Pin Name           | Туре | Description                 |

|--------------------|------|-----------------------------|

| OEA, OEB, OEC, OED | I    | Output Enable Inputs        |

| INA, INB, INC, IND | Ι    | Clock Inputs                |

| OAn, OBn, OCn, ODn | 0    | Clock Outputs               |

| MONB, MOND         | 0    | Non-disable Monitor Outputs |

# RECOMMENDED OPERATING CONDITIONS

| Symbol | Description                   | Min. | Max. | Unit |

|--------|-------------------------------|------|------|------|

| Vdd    | Power Supply Voltage          | 4.75 | 5.25 | V    |

| VIN    | Input Voltage                 | 0    | 5.5  | V    |

| Vout   | Voltage Applied to Outputs    | 0    | 5.5  | ۷    |

| Та     | Ambient Operating Temperature | 0    | +70  | °C   |

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

| Symbol | Parameter                              | Conditions                                       | Min. | Тур.  | Max.  | Unit |

|--------|----------------------------------------|--------------------------------------------------|------|-------|-------|------|

| Vih    | Input HIGH Voltage                     | Guaranteed Logic HIGH for Inputs                 | 2    | —     | —     | V    |

| VIL    | Input LOW Voltage                      | Guaranteed Logic LOW for Inputs                  | —    | —     | 0.8   | V    |

| VIC    | Clamp Diode Voltage (3)                | V <sub>DD</sub> = Min., I <sub>IN</sub> = -18mA  | —    | - 0.7 | - 1.2 | V    |

| Vон    | Output HIGH Voltage                    | Vdd = Min., Ioн = -24mA                          | 2.4  | —     | —     | V    |

| Vol    | Output LOW Voltage                     | VDD = Min., IOL = 64mA                           | —    | —     | 0.55  | V    |

| lin    | Input Leakage Current                  | $V_{DD} = Max., V_{IN} = V_{DD} \text{ or } GND$ | —    | —     | ±1    | μA   |

| loz    | Output Leakage Current                 | VDD = Max., Outputs High-Z                       | _    | _     | ±1    | μA   |

| los    | Short Circuit Current <sup>(2,3)</sup> | VDD = Max., VOUT = GND                           | - 60 | _     | _     | mA   |

#### NOTES:

1. Typical values are at VDD = 5.0V, TA =  $25^{\circ}$ C.

2. Not more than one output should be used to test this high power condition. Duration is  $\leq 1$  second.

3. Guaranteed by design but not tested.

### **POWER SUPPLY CHARACTERISTICS**

| Symbol | Parameter                                              | Test Conditions <sup>(1)</sup>                                  | Тур. <sup>(3)</sup> | Max. | Unit   |

|--------|--------------------------------------------------------|-----------------------------------------------------------------|---------------------|------|--------|

| Icc    | Quiescent Power Supply Current                         | VDD = Max., VIN = GND or VDD                                    | 0.4                 | 3    | mA     |

| Δlcc   | Supply Current per Input HIGH                          | VDD = Max., VIN = 3.4V, fi = 0MHz                               | 0.5                 | 2.5  | mA     |

| ICCD   | Dynamic Power Supply Current per Output <sup>(2)</sup> | VDD = Max., VIN = GND or VDD<br>Outputs Enabled, 50% duty cycle | 0.1                 | 0.2  | mA/MHz |

NOTES:

1. For conditions shown as Min. or Max., use the appropriate values specified under DC specifications.

2. Guaranteed but not tested.

3. Typical values are for reference only. Conditions are VDD = 5.0V and  $T_A = 25^{\circ}C$ .

4. IC = ICC +  $(\Delta ICC)(DH)(NT)$  + ICCD (fO)(NO)

where:

DH = Input duty cycle

NT = Number of TTL HIGH inputs at DH

fo = Output frequency

No = Number of outputs at fo

# **SKEW CHARACTERISTICS OVER OPERATING RANGE**

|         |                                                                                          | QS5820AT |      | QS5820BT |      |      |

|---------|------------------------------------------------------------------------------------------|----------|------|----------|------|------|

| Symbol  | Description <sup>(1)</sup>                                                               | Min.     | Max. | Min.     | Max. | Unit |

| tsk(01) | Skew between two outputs, same transition, same bank                                     | -        | 0.5  | -        | 0.5  | ns   |

| tsk(02) | Skew between two outputs, same transition, different bank                                | -        | 0.6  | _        | 0.6  | ns   |

| tSK(p)  | Duty cycle distortion (pulse skew) on a single output opposite transitions (tPHL - tPLH) | -        | 1    | _        | 0.7  | ns   |

| tsk(t)  | Part-to-part skew, same transition <sup>(2)</sup>                                        | -        | 1.5  | _        | 1    | ns   |

NOTES:

1. Skew parameters are guaranteed across temperature range, but not production tested. Skew parameters apply to propagation delays only. 2. tsk(t) only applies to devices of the same transition, same VDD, same temperature, same speed grade, and same loading.

# SWITCHING CHARACTERISTICS OVER OPERATING RANGE

CLOAD = 50pF, RLOAD =  $500\Omega$  unless otherwise noted.

|              |                                    | QS5820AT |      | QS5820BT |      | QS5820AT QS5820BT |  |  |

|--------------|------------------------------------|----------|------|----------|------|-------------------|--|--|

| Symbol       | Description <sup>(1)</sup>         | Min.     | Max. | Min.     | Max. | Unit              |  |  |

| tplh<br>tphl | Propagation Delay <sup>(1,2)</sup> | 1.5      | 5.8  | 1.5      | 5    | ns                |  |  |

| tR           | Output Rise Time, 0.8V to 2V       | —        | 1.5  | _        | 1.5  | ns                |  |  |

| tF           | Output Fall Time, 2V to 0.8V       | _        | 1.5  | _        | 1.5  | ns                |  |  |

| tpzl<br>tpzн | Output Enable Time                 | 1.5      | 8    | 1.5      | 7    | ns                |  |  |

| tplz<br>tphz | Output Disable Time                | 1.5      | 7    | 1.5      | 6    | ns                |  |  |

NOTES:

1. Minimums guaranteed but not tested.

2. The propagation delay range indicated by Min. and Max. specifications results from process and environmental variables. These propagation delay limits do not imply skew.

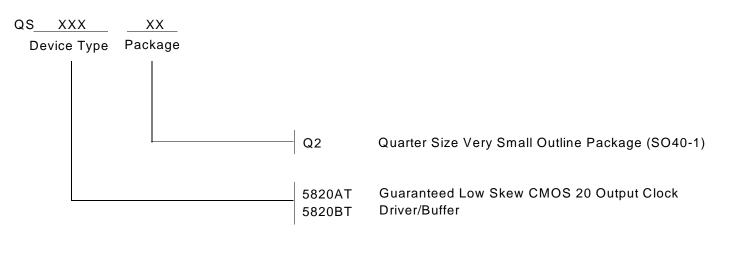

# **ORDERING INFORMATION**

*CORPORATE HEADQUARTERS* 2975 Stender Way Santa Clara, CA 95054 for SALES: 800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com\*

\*To search for sales office near you, please click the sales button found on our home page or dial the 800# above and press 2. The IDT logo is a registered trademark of Integrated Device Technology, Inc. Turboclock is a registered trademark of Integrated Device Technology, Inc.