15 Mega Byte CompactFlash<sup>TM</sup>

# HITACHI

ADE-203-624A (Z) Rev. 1.0 Feb. 28, 1997

#### Description

HB286015C1 is a 15 Mega bytes CompactFlash<sup>TM</sup>. This card complies with CompactFlash<sup>TM</sup> specification, and is suitable for the usage of data storage memory medium for PC or any other electric equipment and digital still camera. This card is equipped with Hitachi 64 Mega bit Flash memory HN29W6411. This card is suitable for ISA (Industry Standard Architecture) bus interface standard, and read/write unit is 1 sector (512 bytes) sequential access. By using this card it is possible to operate good performance for the system which have CompactFlash<sup>TM</sup> slots.

#### Features

- CompactFlash<sup>™</sup> specification standard

50 pin two pieces connector

- 3.3V / 5V single power supply operation

- Card density is 15 Mega bytes

- This card is equipped with Hitachi 64 Mega bit Flash memory (HN29W6411)

- Internal self-diagnostic program operates at  $V_{CC}$  power on

- Memory Card Mode / I/O Card Mode / True-IDE Mode

- High reliability based on internal ECC (Error Correcting Code) function

- Data write endurance is 100,000 cycle (min) per logical sector

- Data reliability is 1 error in 10<sup>14</sup> bits read

- Auto Sleep Mode

Note: CompactFlash<sup>™</sup> is a trademark of SanDisk Corporation and is licensed royalty-free to the CFA which in turn will license it royalty-free to CFA members. Hitachi is member of CFA. \*CFA: CompactFlash<sup>™</sup> Association.

#### **Card Line Up**

| Type no.   | Card density |

|------------|--------------|

| HB286015C1 | 15 MB        |

# **Card Pin Assignment**

| GND          GND          GND            2         D3         I/O         D3         I/O         D3         I/O           3         D4         I/O         D4         I/O         D4         I/O           4         D5         I/O         D5         I/O         D5         I/O           5         D6         I/O         D6         I/O         D6         I/O           6         D7         I/O         D7         I/O         D7         I/O           6         D7         I/O         D7         I/O         D7         I/O           7         -CE1         I         -CE11         I         -CE1         I           8         A10         I         A10         I         A10         I           9         -OE         I         -OE         I         -ATASEL         I           10         A9         I         A8         I         A8         I           11         A8         I         A8         I         I         I           12         A7         I         A7         I         I         I <th></th> <th>Memory card n</th> <th>node</th> <th>I/O card mode</th> <th></th> <th>True IDE mode</th> <th></th>                        |         | Memory card n | node | I/O card mode |     | True IDE mode |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------|------|---------------|-----|---------------|-----|

| 2         D3         I/O         D3         I/O         D3         I/O           3         D4         I/O         D4         I/O         D4         I/O           4         D5         I/O         D5         I/O         D5         I/O           5         D6         I/O         D6         I/O         D6         I/O           6         D7         I/O         D7         I/O         D7         I/O           7         -CE1         I         -CE1         I         -CE1         I           8         A10         I         A10         I         A10         I           9         -OE         I         OE         I         -ATASEL         I           10         A9         I         A9         I         A9         I           11         A8         I         A8         I         A8         I           12         A7         I         A7         I         A7         I           13         VCC         -         VCC         -         VCC         -           14         A6         I         A6         I         I                                                                                                                   | Pin NO. | Signal name   | I/O  | Signal name   | I/O | Signal name   | I/O |

| 3         D4         I/O         D4         I/O         D4         I/O           4         D5         I/O         D5         I/O         D5         I/O           5         D6         I/O         D6         I/O         D6         I/O           6         D7         I/O         D7         I/O         D7         I/O           6         D7         I/O         D7         I/O         D7         I/O           7         -CE1         I         -CE1         I         -CE1         I           8         A10         I         A10         I         A10         I           9         -OE         I         OE         I         -ATASEL         I           10         A9         I         A9         I         A9         I           11         A8         I         A8         I         A8         I           12         A7         I         A7         I         A7         I           13         VCC         -         VCC         -         VCC         -           14         A6         I         A6         I         I                                                                                                                   | 1       | GND           | _    | GND           |     | GND           |     |

| 4         D5         I/O         D5         I/O         D5         I/O           5         D6         I/O         D6         I/O         D6         I/O           6         D7         I/O         D7         I/O         D7         I/O           7         -CE1         I         -CE1         I         -CE1         I           8         A10         I         A10         I         A10         I           9         -OE         I         -OE         I         -ATASEL         I           10         A9         I         A9         I         A9         I           11         A8         I         A8         I         A8         I           12         A7         I         A7         I         A7         I           13         VCC         -         VCC         -         VCC         -           14         A6         I         A6         I         A6         I           15         A5         I         A2         I         A2         I           16         A4         I         A1         I         I      <                                                                                                                     | 2       | D3            | I/O  | D3            | I/O | D3            | I/O |

| 5         D6         I/O         D6         I/O         D6         I/O           6         D7         I/O         D7         I/O         D7         I/O           7         -CE1         I         -CE1         I         -CE1         I           8         A10         I         A10         I         A10         I           9         -OE         I         -OE         I         -ATASEL         I           10         A9         I         A9         I         A9         I         I           11         A8         I         A8         I         A8         I           12         A7         I         A7         I         A7         I           13         VCC         -         VCC         -         VCC         -           14         A6         I         A6         I         A6         I           15         A5         I         A2         I         A2         I           16         A4         I         A1         I         I         I           19         A1         I         A1         I         I                                                                                                                        | 3       | D4            | I/O  | D4            | I/O | D4            | I/O |

| 6         D7         I/O         D7         I/O         D7         I/O           7         -CE1         I         -CE1         I         -CE1         I           8         A10         I         A10         I         A10         I           9         -OE         I         -OE         I         -ATASEL         I           10         A9         I         A9         I         A9         I           11         A8         I         A8         I         A8         I           12         A7         I         A7         I         A7         I         -           13         VCC          VCC          VCC         -         -           14         A6         I         A6         I         A6         I         -           15         A5         I         A6         I         A6         I         -           16         A4         I         A4         I         A1         I         -           19         A1         I         A1         I         A1         I         I         I         I <td>4</td> <td>D5</td> <td>I/O</td> <td>D5</td> <td>I/O</td> <td>D5</td> <td>I/O</td>                                                   | 4       | D5            | I/O  | D5            | I/O | D5            | I/O |

| 7-CE1I-CE1I-CE1I8A10IA10IA10I9-OEI-OEI-ATASELI10A9IA9IA9I11A8IA8IA8I12A7IA7IA7I13VCCVCCVCC14A6IA6IA6I15A5IA2IA3I16A4IA4IA4I17A3IA2IA2I18A2IA0IA0I20A0IA0IA0I21D0VOD1VOD1VO22D1VOD2VOD2VO23D2VOD2O-CD2O24WPO-CD1O-CD1O25-CD2O-CD2O-CD2O26-CD1O-CD1VOD11VO28D12I/OD13I/OD13I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5       | D6            | I/O  | D6            | I/O | D6            | I/O |

| 8         A10         I         A10         I         A10         I           9         -OE         I         -OE         I         -ATASEL         I           10         A9         I         A9         I         A9         I         A9         I           11         A8         I         A8         I         A8         I         I           12         A7         I         A7         I         A7         I         I         I           13         VCC         -         VCC         -         VCC         -         -           14         A6         I         A6         I         A6         I         I         I           15         A5         I         A5         I         A5         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I </td <td>6</td> <td>D7</td> <td>I/O</td> <td>D7</td> <td>I/O</td> <td>D7</td> <td>I/O</td> | 6       | D7            | I/O  | D7            | I/O | D7            | I/O |

| 9         -OE         I         -OE         I         -ATASEL         I           10         A9         I         A9         I         A9         I         A9         I           11         A8         I         A8         I         A8         I         A1           12         A7         I         A7         I         A7         I         A7         I           13         VCC          VCC          VCC            14         A6         I         A6         I         A6         I            14         A6         I         A6         I         A6         I             14         A6         I         A6         I         A6         I             15         A5         I         A5         I         A5         I              16         A4         I         A4         I                                                                                                                                                                                                                                                                                                                                                              | 7       | -CE1          | I    | -CE1          | I   | -CE1          | I   |

| 10A9IA9IA9IA9I11A8IA8IA8IA8I12A7IA7IA7II13VCCVCCVCC14A6IA6IA6I15A5IA5IA5I16A4IA4IA4I17A3IA3IA3I18A2IA2IA1I20A0IA0IA0I21D0VOD0VOD0VO22D1VOD2VOD2VO24WPO-IOIS16O-IOIS16O25-CD2O-CD2O-CD2O26-CD1OD11VOD12VO29D13VOD13VOD13VO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8       | A10           | I    | A10           | Ι   | A10           | I   |

| 11A8IA8IA8IA8I12A7IA7IA7IA7I13VCCVCCVCC14A6IA6IA6I15A5IA5IA5I16A4IA4IA4I17A3IA3IA3I18A2IA1IA1I20A0IA0IA0I21D0I/OD0I/OD0I/O22D1I/OD1I/OD1I/O23D2I/OD2I/OD2I/O24WPO-CD2O-CD2O25-CD2O-CD1O-CD1O27D11I/OD11I/OD11I/O28D12I/OD13I/OD13I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9       | -OE           | I    | -OE           | I   | -ATASEL       | I   |

| 12A7IA7IA7IA7I13VCCVCCVCC14A6IA6IA6I15A5IA5IA5I16A4IA4IA4I17A3IA3IA3I18A2IA2IA2I19A1IA1IA1I20A0IA0IA0I21D0I/OD0I/OD0I/O22D1I/OD1I/OD1I/O23D2I/OD2I/OD2I/O24WPO-CD1O-CD2O25-CD2O-CD1O-CD1O27D11I/OD11I/OD11I/O28D12I/OD13I/OD13I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10      | A9            | I    | A9            | I   | A9            | I   |

| 13VCCVCCVCC14A6IA6IA6II15A5IA5IA5II16A4IA4IA4II17A3IA3IA3II18A2IA2IA2I19A1IA1IA0II20A0IA0IA0I21D0I/OD0I/OD0I/O22D1I/OD1I/OD1I/O23D2I/OD2I/OD2I/O24WPO-CD2O-CD2O26-CD1O-CD1O-CD1O27D11I/OD11I/OD11I/O28D12I/OD13I/OD13I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11      | A8            | I    | A8            | Ι   | A8            | I   |

| 14A6IA6IA6I15A5IA5IA5I16A4IA4IA4I17A3IA3IA3I18A2IA2IA2I19A1IA1IA1I20A0IA0IA0I21D0I/OD0I/OD0I/O22D1I/OD1I/OD1I/O23D2I/OD2I/OD2I/O24WPO-CD2O-CD2O26-CD1O-CD1O-CD1O27D11I/OD11I/OD11I/O28D12I/OD13I/OD13I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12      | A7            | I    | A7            | I   | A7            | I   |

| 15A5IA5IA5I $16$ A4IA4IA4I $17$ A3IA3IA3I $18$ A2IA2IA2I $19$ A1IA1IA1I $20$ A0IA0IA0I $21$ D0I/OD0I/OD0I/O $22$ D1I/OD1I/OD1I/O $23$ D2I/OD2I/OD2I/O $24$ WPO-CD2O-CD2O $26$ -CD1O-CD1O-CD1O $27$ D11I/OD11I/OD11I/O $28$ D12I/OD12I/OD12I/O $29$ D13I/OD13I/OD13I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13      | VCC           | _    | VCC           | _   | VCC           | _   |

| 16         A4         I         A4         I         A4         I           17         A3         I         A3         I         A3         I           18         A2         I         A2         I         A2         I           19         A1         I         A1         I         A1         I           20         A0         I         A0         I         A0         I           21         D0         I/O         D0         I/O         D0         I/O           21         D0         I/O         D1         I/O         D1         I/O           22         D1         I/O         D1         I/O         D1         I/O           23         D2         I/O         D2         I/O         D2         I/O           24         WP         O         -IOIS16         O         -IOIS16         O           25         -CD2         O         -CD1         O         -CD1         O           26         -CD1         O         D11         I/O         III         I/O           28         D12         I/O         D13         I/O <td< td=""><td>14</td><td>A6</td><td>Ι</td><td>A6</td><td>Ι</td><td>A6</td><td>I</td></td<>                   | 14      | A6            | Ι    | A6            | Ι   | A6            | I   |

| 17       A3       I       A3       I       A3       I         18       A2       I       A2       I       A2       I         19       A1       I       A1       I       A1       I         20       A0       I       A0       I       A0       I         21       D0       I/O       D0       I/O       D0       I/O         22       D1       I/O       D1       I/O       D1       I/O         23       D2       I/O       D2       I/O       D2       I/O         24       WP       O       -IOIS16       O       -IOIS16       O         25       -CD2       O       -CD2       O       -CD2       O         26       -CD1       O       -CD1       O       -CD1       O         26       -CD1       O       -CD1       O       -CD1       O         27       D11       I/O       D11       I/O       D11       I/O         28       D12       I/O       D12       I/O       D13       I/O                                                                                                                                                                                                                                                                    | 15      | A5            | I    | A5            | I   | A5            | I   |

| 18       A2       I       A2       I       A2       I         19       A1       I       A1       I       A1       I       I       A1       I         20       A0       I       A0       I       A0       I       A0       I         21       D0       I/O       D0       I/O       D0       I/O       D0       I/O         22       D1       I/O       D1       I/O       D1       I/O         23       D2       I/O       D2       I/O       D2       I/O         24       WP       O       -IOIS16       O       -IOIS16       O         25       -CD2       O       -CD2       O       -CD2       O         26       -CD1       O       -CD1       O       -CD1       O         27       D11       I/O       D11       I/O       D11       I/O         28       D12       I/O       D12       I/O       D13       I/O                                                                                                                                                                                                                                                                                                                                         | 16      | A4            | I    | A4            | I   | A4            | I   |

| 19       A1       I       A1       I       A1       I         20       A0       I       A0       I       A0       I         21       D0       I/O       D0       I/O       D0       I/O         22       D1       I/O       D1       I/O       D1       I/O         23       D2       I/O       D2       I/O       D2       I/O         24       WP       O       -IOIS16       O       -IOIS16       O         25       -CD2       O       -CD2       O       -CD2       O         26       -CD1       O       -CD1       O       -CD1       O         27       D11       I/O       D11       I/O       D11       I/O         28       D12       I/O       D12       I/O       D12       I/O         29       D13       I/O       D13       I/O       D13       I/O                                                                                                                                                                                                                                                                                                                                                                                             | 17      | A3            | I    | A3            | I   | A3            | I   |

| 20         A0         I         A0         I         A0         I           21         D0         I/O         D0         D0         D0         D0         I/O           22         D1         I/O         D1         I/O         D1         I/O           23         D2         I/O         D2         I/O         D2         I/O           24         WP         O         -IOIS16         O         -IOIS16         O           25         -CD2         O         -CD2         O         -CD2         O           26         -CD1         O         -CD1         O         -CD1         O           27         D11         I/O         D11         I/O         D11         I/O           27         D11         I/O         D11         I/O         D11         I/O           28         D12         I/O         D12         I/O         D13         I/O                                                                                                                                                                                                                                                                                                       | 18      | A2            | I    | A2            | I   | A2            | I   |

| 21         D0         I/O         D0         I/O         D0         I/O           22         D1         I/O         D1         I/O         D1         I/O           23         D2         I/O         D2         I/O         D2         I/O           24         WP         O         -IOIS16         O         -IOIS16         O           25         -CD2         O         -CD2         O         -CD2         O           26         -CD1         O         -CD1         O         -CD1         O           27         D11         I/O         D11         I/O         D11         I/O           28         D12         I/O         D12         I/O         D12         I/O           29         D13         I/O         D13         I/O         D13         I/O                                                                                                                                                                                                                                                                                                                                                                                             | 19      | A1            | I    | A1            | I   | A1            | I   |

| 22         D1         I/O         D1         I/O         D1         I/O           23         D2         I/O         D2         I/O         D2         I/O           24         WP         O         -IOIS16         O         -IOIS16         O           25         -CD2         O         -CD2         O         -CD2         O           26         -CD1         O         -CD1         O         -CD1         O           27         D11         I/O         D11         I/O         D11         I/O           28         D12         I/O         D12         I/O         D12         I/O           28         D12         I/O         D13         I/O         D13         I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20      | A0            | I    | A0            | Ι   | A0            | I   |

| 23         D2         I/O         D2         I/O         D2         I/O           24         WP         O         -IOIS16         O         -IOIS16         O           25         -CD2         O         -CD2         O         -CD2         O           26         -CD1         O         -CD1         O         -CD1         O           27         D11         I/O         D11         I/O         D11         I/O           28         D12         I/O         D12         I/O         D12         I/O           29         D13         I/O         D13         I/O         D13         I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21      | D0            | I/O  | D0            | I/O | D0            | I/O |

| 24         WP         O         -IOIS16         O         -IOIS16         O           25         -CD2         O         -CD2         O         -CD2         O           26         -CD1         O         -CD1         O         -CD1         O           27         D11         I/O         D12         I/O         D12         I/O           28         D12         I/O         D13         I/O         D13         I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22      | D1            | I/O  | D1            | I/O | D1            | I/O |

| 25       -CD2       O       -CD2       O       -CD2       O         26       -CD1       O       -CD1       O       -CD1       O         27       D11       I/O       D11       I/O       D11       I/O         28       D12       I/O       D12       I/O       D12       I/O         29       D13       I/O       D13       I/O       D13       I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23      | D2            | I/O  | D2            | I/O | D2            | I/O |

| 26         -CD1         O         -CD1         O         -CD1         O           27         D11         I/O         D11         I/O         D11         I/O           28         D12         I/O         D12         I/O         D12         I/O           29         D13         I/O         D13         I/O         D13         I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24      | WP            | 0    | -IOIS16       | 0   | -IOIS16       | 0   |

| 27         D11         I/O         D11         I/O           28         D12         I/O         D12         I/O         D12         I/O           29         D13         I/O         D13         I/O         D13         I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25      | -CD2          | 0    | -CD2          | 0   | -CD2          | 0   |

| 28         D12         I/O         D12         I/O         D12         I/O           29         D13         I/O         D13         I/O         D13         I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26      | -CD1          | 0    | -CD1          | 0   | -CD1          | 0   |

| 29 D13 I/O D13 I/O D13 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27      | D11           | I/O  | D11           | I/O | D11           | I/O |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28      | D12           | I/O  | D12           | I/O | D12           | I/O |

| 30 D14 I/O D14 I/O D14 I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29      | D13           | I/O  | D13           | I/O | D13           | I/O |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30      | D14           | I/O  | D14           | I/O | D14           | I/O |

|         | Memory card n | node | I/O card mode |     | True IDE mode |     |

|---------|---------------|------|---------------|-----|---------------|-----|

| Pin NO. | Signal name   | I/O  | Signal name   | I/O | Signal name   | I/O |

| 31      | D15           | I/O  | D15           | I/O | D15           | I/O |

| 32      | -CE2          | I    | -CE2          | I   | -CE2          | I   |

| 33      | -VS1          | 0    | -VS1          | 0   | -VS1          | 0   |

| 34      | -IORD         | I    | -IORD         | I   | -IORD         | I   |

| 35      | -IOWR         | I    | -IOWR         | I   | -IOWR         | I   |

| 36      | -WE           | I    | -WE           | I   | -WE           | I   |

| 37      | RDY/-BSY      | 0    | -IREQ         | 0   | INTRQ         | 0   |

| 38      | VCC           | _    | VCC           |     | VCC           | _   |

| 39      | -CSEL         | I    | -CSEL         | I   | -CSEL         | I   |

| 40      | -VS2          | 0    | -VS2          | 0   | -VS2          | 0   |

| 41      | RESET         | I    | RESET         | I   | -RESET        | I   |

| 42      | -WAIT         | 0    | -WAIT         | 0   | IORDY         | 0   |

| 43      | -INPACK       | 0    | -INPACK       | 0   | -INPACK       | 0   |

| 44      | -REG          | I    | -REG          | I   | -REG          | I   |

| 45      | BVD2          | I/O  | -SPKR         | I/O | -DASP         | I/O |

| 46      | BVD1          | I/O  | -STSCHG       | I/O | -PDIAG        | I/O |

| 47      | D8            | I/O  | D8            | I/O | D8            | I/O |

| 48      | D9            | I/O  | D9            | I/O | D9            | I/O |

| 49      | D10           | I/O  | D10           | I/O | D10           | I/O |

| 50      | GND           | _    | GND           | —   | GND           | —   |

#### **Card Pin Explanation**

Address bus (A0 to A10: input): Address bus is A0 to A10. A0 is invalid in word mode. A10 is MSB and A0 is LSB. In True IDE Mode only A0 to A2 are used for selecting the one of eight registers in the Task File, the remaining address lines should be grounded by the host.

**Data bus (D0 to D15: input/output):** Data bus is D0 to D15. D0 is the LSB of the Even Byte of the Word. D8 is the LSB of the Odd Byte of the Word.

**Card enable** (-**CE1, -CE2: input):** -CE1 and -CE2 are low active card select signals. Even addresses are controlled by -CE1 and odd addresses are by -CE2. In True IDE Mode -CE2 is used for select the Alternate Status Register and the Device Control Register while -CE1 is the chip select for the other task file registers.

**Output enable, ATA select (-OE, -ATASEL: input):** -OE is used for the control of read data in Attribute area or Common memory task file area. To enable True IDE Mode this input should be grounded by the host.

Write enable (-WE: input): -WE is used for the control of data write in Attribute memory area or Common memory task file area. In True IDE Mode this input signal is not used and should be connected to VCC by the host.

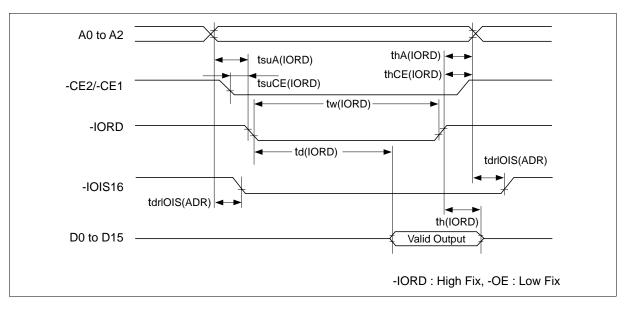

**I/O read (-IORD: input):** -IORD is used for control of read data in I/O Task File area. This card dose not respond to -IORD until I/O card interface setting up.

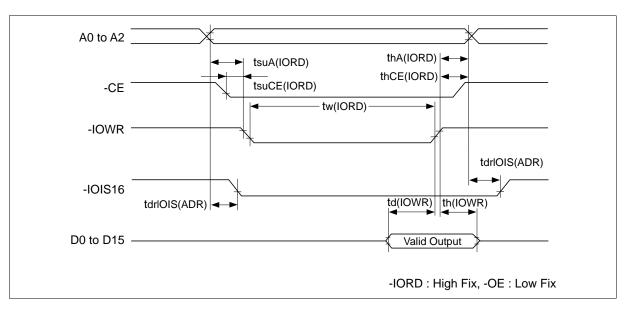

**I/O write** (**-IOWR: input):** -IOWR is used for control of data write in I/O Task File area. This card dose not respond to -IOWR until I/O card interface setting up.

**Ready/Busy, Interrupt request (RDY/-BSY, -IREQ, INTRQ: output):** In I/O card mode, this signal is -IREQ pin. The signal of low level indicates that the card is requesting software service to host, and high level indicates that the card is not requesting. In memory card mode, the signal is RDY/-BSY pin. RDY/-BSY pin turns low level during the card internal initialization operation at VCC applied or reset applied, so next access to the card should be after the signal turned high level. In True IDE Mode signal is the active high Interrupt Request to the host.

**Card detection** (-CD1, -CD2: output): -CD1 and -CD2 are the card detection signals. -CD1 and -CD2 are connected to ground in this card, so host can detect that the card is inserted or not.

Write protect, 16 bit I/O port (WP, -IOIS16: output): In memory card mode, +WP is held low because this card dose not have write protect switch. In I/O card mode, -IOIS16 is asserted when Task File registers are accessed in 16bit mode. In True IDE Mode this output signal is asserted low when this device is expecting a word data transfer cycle.

Attribute memory area selection (-REG: input): -REG should be high level during common memory area accessing, and low level during Attribute area accessing. Attribute memory area is located only even address, so D0 to D7 are valid and D8 to D15 are invalid in the word access mode. Odd addresses are invalid in the byte access mode. In True IDE Mode this input signal is not used and should be connected to VCC.

**Battery voltage detection, Digital audio output, Disk active/slave present (BVD2, -SPKR, -DASP: output/output):** In memory card mode, BVD2 outputs the battery voltage status in the card. This card has no battery, so this output is high level constantly. In I/O card mode, -SPKR is held High because this card dose not have digital audio output. In True IDE Mode -DASP is the Disk Active/Slave Present signal in the Master/Slave handshake protocol.

**Reset (RESET, -RESET: input):** By assertion of RESET signal, all registers of this card are cleared and RDY/-BSY signal turns to high level. In True IDE Mode -RESET is the active low hardware reset from the host.

**Wait (-WAIT, IORDY: output):** This signal outputs low level for the purpose of delaying memory access cycle or I/O access cycle. In True IDE Mode this output signal may be used as IORDY.

**Input acknowledge (-INPACK: output):** This signal not used for memory card mode. This signal is asserted by this card when the card is selected and responding to an I/O read cycle at the address that is on the address bus. This signal is used for the input data buffer control. In True IDE Mode this output signal is not used and should not be connected at the host.

**Battery voltage detection, Status change Pass diagnostic (BVD1, -STSCHG, -PDIAG: input/output):** In memory card mode, BVD1 outputs the battery voltage status in the card. This card has no battery, so this output is high level constantly. In I/O card mode, -STSCHG is used for changing the status of Configuration status register in Attribute area, while the card is set I/O card interface. In True IDE Mode, -PDIAG is the Pass Diagnostic signal in Master/Slave handshake protocol.

**VCC voltage sense (-VS1, -VS2: output):** This signals are intended to notify the socket of PC Card's CIS VCC requirement. VS1 is held low and VS2 is nonconnected in this card.

**Card select** (-**CSEL: input):** This signal is not used for memory card mode and I/O card mode. This internally pulled up signal is used for configure this device as a Master or a Slave when configured in the True IDE Mode. When this pin is grounded, this device is configured as a Master. When the pin is open, this device is configured as a Slave.

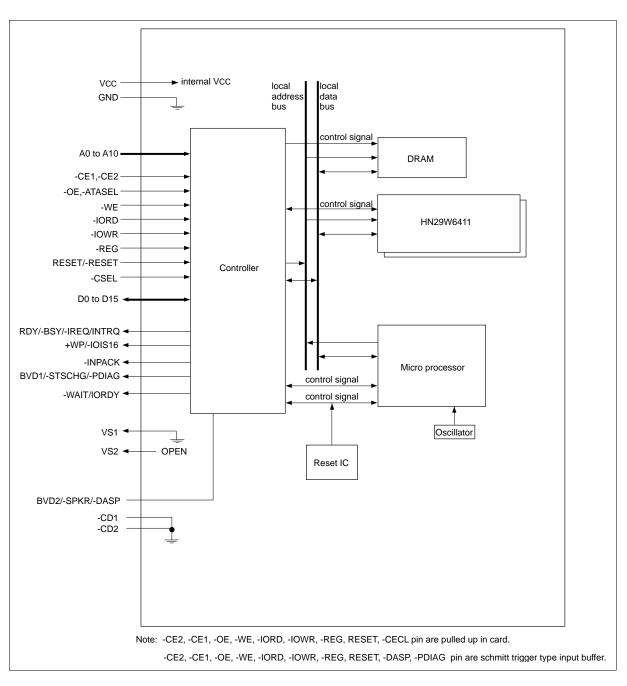

#### **Card Block Diagram**

## **Card Function Explanation**

#### **Register construction**

- Attribute region

- Configuration register

- Configuration Option register

- Configuration and Status register

- Pin Replacement register

- Socket and Copy register

- CIS (Card Information Structure)

- Task File region

- Data register

- Error register

- Feature register

- Sector Count register

- Sector Number register

- Cylinder Low register

- Cylinder High register

- Drive Head register

- Status register

- Alternate Status register

- Command register

- Device Control register

- Drive Address register

#### Host access specifications

#### 1. Attribute access specifications

When CIS-ROM region or Configuration register region is accessed, read and write operations are executed under the condition of -REG = "L" as follows. That region can be accessed by Byte/Word/Odd-byte modes which are defined by PC card standard specifications.

| Mode                    | -REG | -CE2 | -CE1 | A0 | -OE | -WE | D8 to D15 | D0 to D7  |

|-------------------------|------|------|------|----|-----|-----|-----------|-----------|

| Standby mode            | ×    | Н    | Н    | ×  | Х   | ×   | High-Z    | High-Z    |

| Byte access (8-bit)     | L    | Н    | L    | L  | L   | Н   | High-Z    | even byte |

|                         | L    | Н    | L    | Н  | L   | Н   | High-Z    | invalid   |

| Word access (16-bit)    | L    | L    | L    | ×  | L   | Н   | invalid   | even byte |

| Odd byte access (8-bit) | L    | L    | Н    | ×  | L   | Н   | invalid   | High-Z    |

#### Attribute Read Access Mode

Note: X: L or H

#### Attribute Write Access Mode

| Mode                    | -REG | -CE2 | -CE1 | A0 | -OE | -WE | D8 to D15  | D0 to D7   |

|-------------------------|------|------|------|----|-----|-----|------------|------------|

| Standby mode            | ×    | Н    | Н    | ×  | ×   | ×   | Don't care | Don't care |

| Byte access (8-bit)     | L    | Н    | L    | L  | Н   | L   | Don't care | even byte  |

|                         | L    | Н    | L    | Н  | Н   | L   | Don't care | Don't care |

| Word access (16-bit)    | L    | L    | L    | ×  | Н   | L   | Don't care | even byte  |

| Odd byte access (8-bit) | L    | L    | Н    | ×  | Н   | L   | Don't care | Don't care |

Note: X: L or H

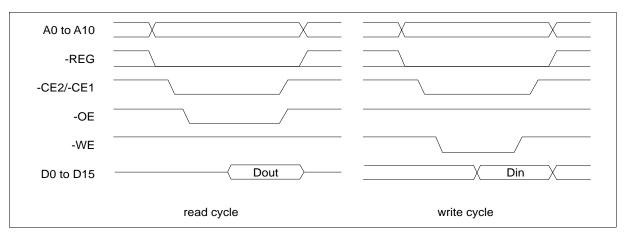

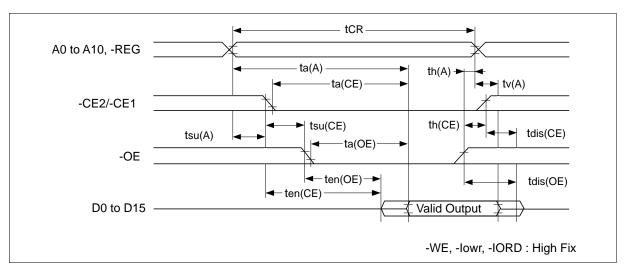

#### **Attribute Access Timing Example**

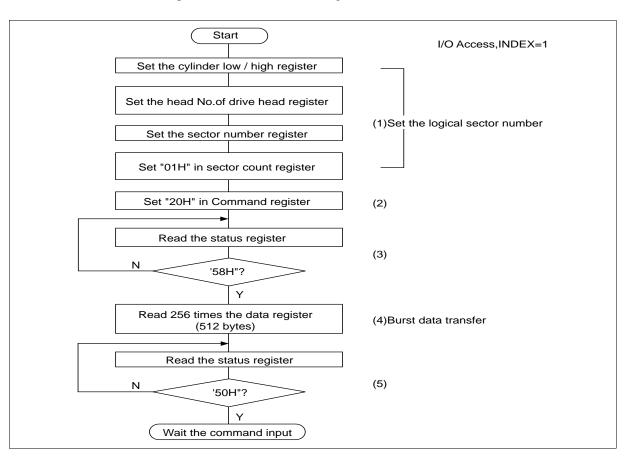

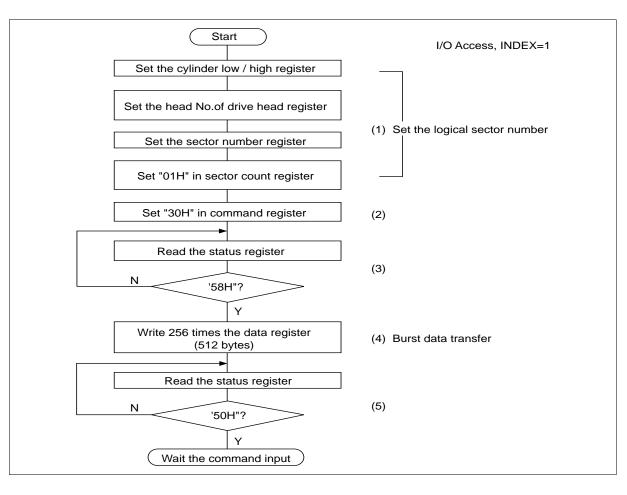

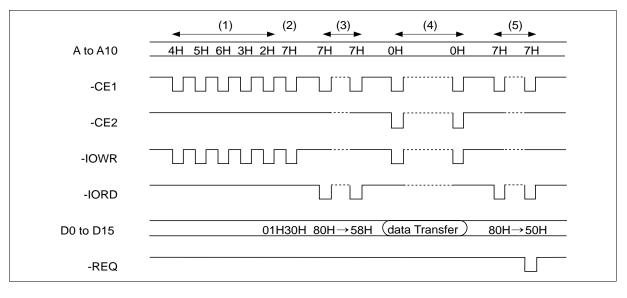

#### 2. Task File register access specifications

There are two cases of Task File register mapping, one is mapped I/O address area, the other is mapped Memory address area. Each case of Task File register read and write operations are executed under the condition as follows. That area can be accessed by Byte/Word/Odd Byte mode which are defined by PC card standard specifications.

#### (1) I/O address map

| Mode                    | -REG | -CE2 | -CE1 | A0 | -IORD | -IOWR | -OE | -WE | D8 to D15 | D0 to D7  |

|-------------------------|------|------|------|----|-------|-------|-----|-----|-----------|-----------|

| Standby mode            | ×    | Н    | Н    | ×  | ×     | ×     | ×   | ×   | High-Z    | High-Z    |

| Byte access (8-bit)     | L    | Н    | L    | L  | L     | Н     | Н   | Н   | High-Z    | even byte |

|                         | L    | Н    | L    | Н  | L     | Н     | Н   | Н   | High-Z    | odd byte  |

| Word access (16-bit)    | L    | L    | L    | ×  | L     | Н     | Н   | Н   | odd byte  | even byte |

| Odd byte access (8-bit) | L    | L    | Н    | ×  | L     | Н     | Н   | Н   | odd byte  | High-Z    |

#### Task File Register Read Access Mode (1)

Note: X: L or H

#### Task File Register Write Access Mode (1)

| Mode                    | -REG | -CE2 | -CE1 | A0 | -IORD | -IOWR | -OE | -WE | D8 to D15  | D0 to D7   |

|-------------------------|------|------|------|----|-------|-------|-----|-----|------------|------------|

| Standby mode            | ×    | Н    | Н    | ×  | ×     | ×     | ×   | ×   | Don't care | Don't care |

| Byte access (8-bit)     | L    | Н    | L    | L  | Н     | L     | Н   | Н   | Don't care | even byte  |

|                         | L    | Н    | L    | Н  | Н     | L     | Н   | Н   | Don't care | odd byte   |

| Word access (16-bit)    | L    | L    | L    | ×  | Н     | L     | Н   | Н   | odd byte   | even byte  |

| Odd byte access (8-bit) | L    | L    | Н    | ×  | Н     | L     | Н   | Н   | odd byte   | Don't care |

Note: X: L or H

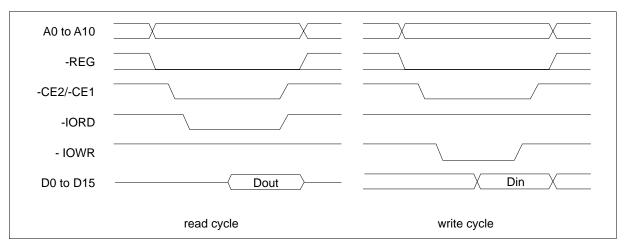

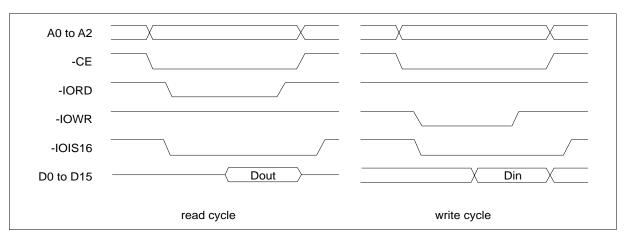

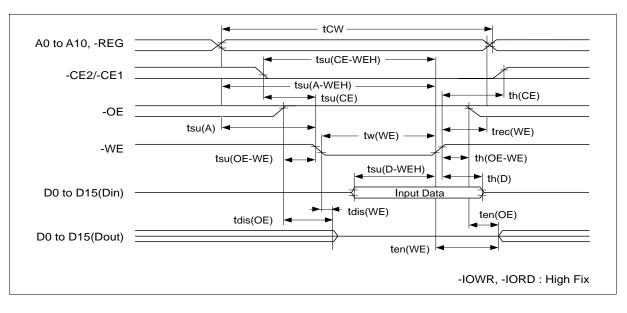

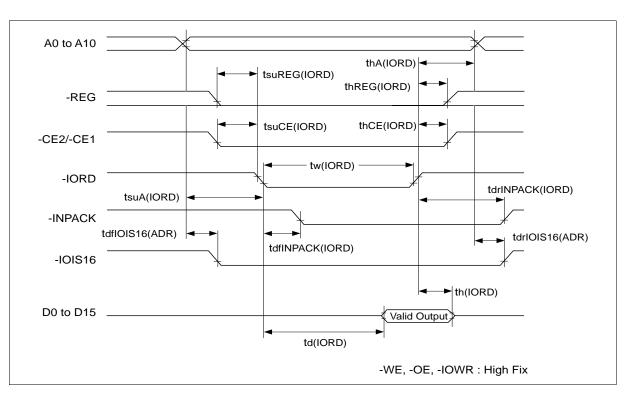

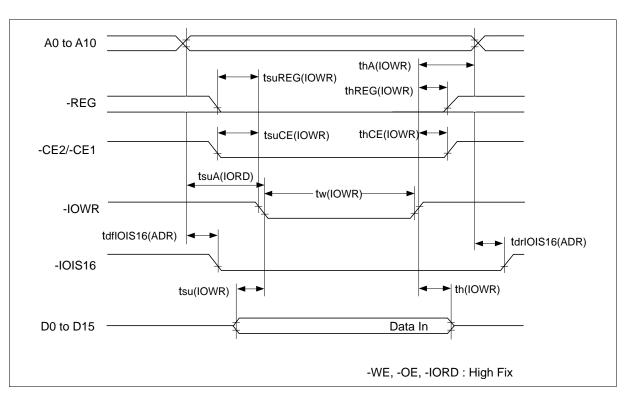

#### Task File Register Access Timing Example (1)

#### (2) Memory address map

#### Task File Register Read Access Mode (2)

| Mode                    | -REG | -CE2 | -CE1 | A0 | -OE | -WE | -IORD | -IOWR | D8 to D15 | D0 to D7  |

|-------------------------|------|------|------|----|-----|-----|-------|-------|-----------|-----------|

| Standby mode            | ×    | Н    | Н    | х  | ×   | ×   | ×     | ×     | High-Z    | High-Z    |

| Byte access (8-bit)     | Н    | Н    | L    | L  | L   | Н   | Н     | Н     | High-Z    | even byte |

|                         | Н    | Н    | L    | Н  | L   | Н   | Н     | Н     | High-Z    | odd byte  |

| Word access (16-bit)    | Н    | L    | L    | ×  | L   | Н   | Н     | Н     | odd byte  | even byte |

| Odd byte access (8-bit) | Н    | L    | Н    | ×  | L   | Н   | Н     | Н     | odd byte  | High-Z    |

Note: ×: L or H

#### Task File Register Write Access Mode (2)

| Mode                    | -REG | -CE2 | -CE1 | A0 | -OE | -WE | -IORD | -IOWR | D8 to D15  | D0 to D7   |

|-------------------------|------|------|------|----|-----|-----|-------|-------|------------|------------|

| Standby mode            | ×    | Н    | Н    | ×  | ×   | ×   | ×     | ×     | Don't care | Don't care |

| Byte access (8-bit)     | Н    | Н    | L    | L  | Н   | L   | Н     | Н     | Don't care | even byte  |

|                         | Н    | Н    | L    | Н  | Н   | L   | Н     | Н     | Don't care | odd byte   |

| Word access (16-bit)    | Н    | L    | L    | ×  | Н   | L   | Н     | Н     | odd byte   | even byte  |

| Odd byte access (8-bit) | Н    | L    | Н    | ×  | Н   | L   | Н     | Н     | odd byte   | Don't care |

| Note: v: Lor H          |      |      |      |    |     |     |       |       |            |            |

Note: X: L or H

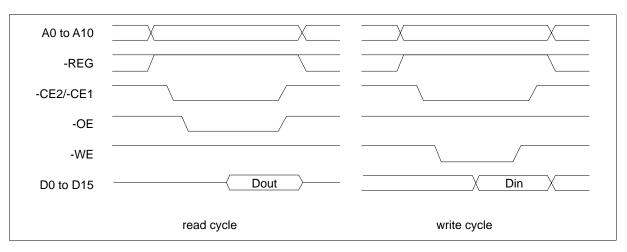

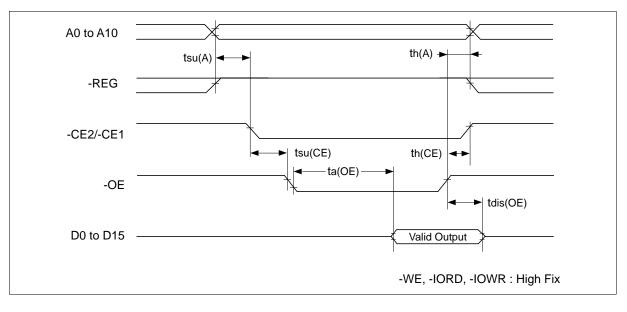

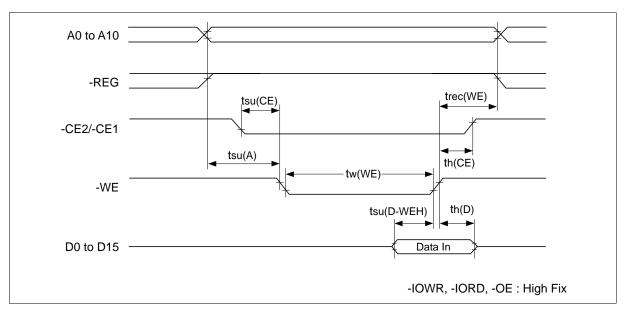

#### Task File Register Access Timing Example (2)

#### 3. True IDE Mode

The card can be configured in a True IDE Mode of operation. This card is configured in this mode only when the -OE input signal is asserted low by the host during the power off to power on cycle. In this True IDE Mode the PCMCIA protocol and confuguration is disabled and only I/O operations to the Task File and Data Register are allowed. In this mode no Memory or Attribute Registers are accessible to the host. The card permit 8 bit accesses if the user issues a Set Feature Command to put the device in 8 bit Mode.

#### **True IDE Mode Read I/O Function**

| Mode                   | -CE2 | -CE1 | A0 to A2 | -IORD | -IOWR | D8 to D15 | D0 to D7  |

|------------------------|------|------|----------|-------|-------|-----------|-----------|

| Invalid mode           | L    | L    | ×        | ×     | ×     | High-Z    | High-Z    |

| Standby mode           | Н    | Н    | ×        | ×     | ×     | High-Z    | High-Z    |

| Data register access   | Н    | L    | 0        | L     | Н     | odd byte  | even byte |

| All status access      | L    | L    | 6H       | L     | Н     | High-Z    | status    |

| Other task file access | Н    | L    | 1-7H     | L     | Н     | High-Z    | data      |

Note: X: L or H

#### True IDE Mode Write I/O Function

| Mode                    | -CE2 | -CE1 | A0 to A | 2 -IORD | -IOWR | D8 to D15  | D0 to D7   |

|-------------------------|------|------|---------|---------|-------|------------|------------|

| Invalid mode            | L    | L    | ×       | ×       | ×     | don't care | don't care |

| Standby mode            | Н    | Н    | ×       | ×       | ×     | don't care | don't care |

| Data register access    | Н    | L    | 0       | Н       | L     | odd byte   | even byte  |

| Control register access | L    | L    | 6H      | L       | Н     | don't care | control    |

| Other task file access  | Н    | L    | 1-7H    | L       | Н     | don't care | data       |

|                         |      |      |         |         |       |            |            |

Note: X: L or H

#### True IDE Mode I/O Access Timing Example

#### **Configuration register specifications**

This card supports four Configuration registers for the purpose of the configuration and observation of this card.

#### 1. Configuration Option register (Address 200H)

This register is used for the configuration of the card configuration status and for the issuing soft reset to the card.

| bit7   | bit6    | bit5  | bit4 | bit3 | bit2 | bit1 | bit0 |

|--------|---------|-------|------|------|------|------|------|

| SRESET | LevIREQ | INDEX |      |      |      |      |      |

|        |         |       |      |      |      |      |      |

Note: initial value: 00H

| Name                | R/W | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRESET<br>(HOST->)  | R/W | Setting this bit to "1", places the card in the reset state (Card Hard Reset). This operation is equal to Hard Reset, except this bit is not cleared. Then this bit set to "0", places the card in the reset state of Hard Reset (This bit is set to "0" by Hard Reset). Card configuration status is reset and the card internal initialized operation starts when Card Hard Reset is executed, so next access to the card should be the same sequence as the power on sequence. |

| LevIREQ<br>(HOST->) | R/W | This bit sets to "0" when pulse mode interrupt is selected, and "1" when level mode interrupt is selected.                                                                                                                                                                                                                                                                                                                                                                        |

| INDEX<br>(HOST->)   | R/W | This bits is used for select operation mode of the card as follows.<br>When Power on, Card Hard Reset and Soft Reset, this data is "000000" for the purpose<br>of Memory card interface recognition.                                                                                                                                                                                                                                                                              |

#### **INDEX** bit assignment

| INDEX | bit |

|-------|-----|

|-------|-----|

| 5 | 4 | 3 | 2 | 1 | 0 | Card mode   | Task File register address | Mapping mode          |

|---|---|---|---|---|---|-------------|----------------------------|-----------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | Memory card | 0H to FH, 400H to 7FFH     | memory mapped         |

| 0 | 0 | 0 | 0 | 0 | 1 | I/O card    | xx0H to xxFH               | contiguous I/O mapped |

| 0 | 0 | 0 | 0 | 1 | 0 | I/O card    | 1F0H to 1F7H, 3F6H to 3F7H | primary I/O mapped    |

| 0 | 0 | 0 | 0 | 1 | 1 | I/O card    | 170H to 177H, 376H to 377H | secondary I/O mapped  |

#### 2. Configuration and Status register (Address 202H)

This register is used for observing the card state.

| bit7  | bit6   | bit5  | bit4 | bit3 | bit2 | bit1 | bit0 |

|-------|--------|-------|------|------|------|------|------|

| CHGED | SIGCHG | IOIS8 | 0    | 0    | PWD  | INTR | 0    |

Note: initial value: 00H

| Name               | R/W | Function                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHGED<br>(CARD->)  | R   | This bit indicates that CRDY/-BSY bit on Pin Replacement register is set to "1". When CHGED bit is set to "1", -STSCHG pin is held "L" at the condition of SIGCHG bit set to "1" and the card configured for the I/O interface.                                                                                                                                                                                                   |

| SIGCHG<br>(HOST->) | R/W | This bit is set or reset by the host for enabling and disabling the status-change signal (-<br>STSCHG pin). When the card is configured I/O card interface and this bit is set to "1", -<br>STSCHG pin is controlled by CHGED bit. If this bit is set to "0", -STSCHG pin is kept<br>"H".                                                                                                                                         |

| IOIS8<br>(HOST->)  | R/W | The host sets this field to "1" when it can provide I/O cycles only with on 8 bit data bus (D7 to D0).                                                                                                                                                                                                                                                                                                                            |

| PWD<br>(HOST->)    | R/W | When this bit is set to "1", the card enters sleep state (Power Down mode). When this bit is reset to "0", the card transfers to idle state (active mode). RRDY/-BSY bit on Pin Replacement Register becomes BUSY when this bit is changed. RRDY/-BSY will not become Ready until the power state requested has been entered. This card automatically powers down when it is idle, and powers back up when it receives a command. |

| INTR<br>(CARD->)   | R   | This bit indicates the internal state of the interrupt request. This bit state is available whether I/O card interface has been configured or not. This signal remains true until the condition which caused the interrupt request has been serviced. If interrupts are disabled by the -IEN bit in the Device Control Register, this bit is a zero.                                                                              |

#### 3. Pin Replacement register (Address 204H)

This register is used for providing the signal state of -IREQ signal when the card configured I/O card interface.

| bit7 | bit6 | bit5      | bit4 | bit3 | bit2 | bit1      | bit0 |

|------|------|-----------|------|------|------|-----------|------|

| 0    | 0    | CRDY/-BSY | 0    | 1    | 1    | RRDY/-BSY | 0    |

|      |      |           |      |      |      |           |      |

Note: initial value: 0CH

| Name                  | R/W | Function                                                                                                   |

|-----------------------|-----|------------------------------------------------------------------------------------------------------------|

| CRDY/-BSY<br>(HOST->) | R/W | This bit is set to "1" when the RRDY/-BSY bit changes state. This bit may also be written by the host.     |

| RRDY/-BSY<br>(HOST->) | R/W | When read, this bit indicates +READY pin states. When written, this bit is used for CRDY/-BSY bit masking. |

#### 4. Socket and Copy register (Address 206H)

This register is used for identification of the card from the other cards. Host can read and write this register. This register should be set by host before this card's Configuration Option register set.

| 0 0 0 DRV# 0 0 0 0 | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|--------------------|------|------|------|------|------|------|------|------|

|                    | 0    | 0    | 0    | DRV# | 0    | 0    | 0    | 0    |

Note: initial value: 00H

| Name             | R/W | Function                                                                                                                                                                                                                 |

|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRV#<br>(HOST->) | R/W | This fields are used for the configuration of the plural cards. When host configures the plural cards, written the card's copy number in this field. In this way, host can perform the card's master/slave organization. |

#### **CIS** informations

CIS informations are defined as follows. By reading attribute address from "0000 H", card CIS informations can be confirmed.

| Address | Data | 7            | 6    | 5             | 4   | 3           | 2       | 1          | 0         |    | Description of contents                                                       | CIS function                |

|---------|------|--------------|------|---------------|-----|-------------|---------|------------|-----------|----|-------------------------------------------------------------------------------|-----------------------------|

| 000H    | 01H  | CIST         | ΡL   | DEV           | IC  | E           |         |            |           |    | Device info tuple                                                             | Tuple code                  |

| 002H    | 04H  | TPL_         | LIN  | ١K            |     |             |         |            |           |    | Link length is 4 byte                                                         | Link to next tuple          |

| 004H    | DFH  | Devi         | ce t | уре           |     | W<br>P<br>S | De      | vic        | e spee    | d  | Device type = DH: I/O device<br>WPS = 0: No WP<br>Device speed = 7: ext speed | Device type, WPS, speed     |

| 006H    | 4AH  | EXT          |      | eed<br>antiss | а   |             | •       | eec<br>oon | d<br>ent  |    | 400 ns if no wait                                                             | Extended speed              |

| 008H    | 01H  | 1x           |      |               |     |             | 2k      | uni        | ts        |    | 2k byte of address space                                                      | Device size                 |

| 00AH    | FFH  | List e       | end  | mark          | er  |             |         |            |           |    | End of device                                                                 | END marker                  |

| 00CH    | 1CH  | CIST         | PL   | DEV           | IC  | ΕC          | C       |            |           |    | Other conditions device info tuple                                            | Tuple code                  |

| 00EH    | 05H  | TPL_         | LIN  | ١K            |     |             |         |            |           |    | Link length is 5 bytes                                                        | Link to next tuple          |

| 010H    | 00H  | EXT          | Re   | serve         | ed  |             | Vc      | 5          | MWA       | IT | 5 V, wait is not used                                                         | Other conditions info field |

| 012H    | DFH  | Devi         | ce t | уре           |     | W<br>P<br>S | De      | vic        | e spee    | d  | Device type = DH: I/O device<br>WPS = 0: No WP<br>Device speed = 7: ext speed | Device type, WPS, speed     |

| 014H    | 4AH  | EXT          | -    | eed<br>antiss | а   |             |         | eec<br>oon | d<br>Ient |    | 400 ns if no wait                                                             | Extended speed              |

| 016H    | 01H  | 1x           |      |               |     |             | 2k      | uni        | ts        |    | 2k byte of address space                                                      | Device size                 |

| 018H    | FFH  | List e       | end  | mark          | er  |             |         |            |           |    | End of device                                                                 | END marker                  |

| 01AH    | 1CH  | CIST         | PL   | DEV           | IC  | ΕC          | C       |            |           |    | Other conditions device info tuple                                            | Tuple code                  |

| 01CH    | 04H  | TPL_         |      | ١K            |     |             |         |            |           |    | Link length is 4 bytes                                                        | Link to next tuple          |

| 01EH    | 01H  | EXT          | Re   | serve         | əd  |             | $V_{c}$ | C          | MWA       | IT | 5 V, wait is used                                                             | Other conditions info field |

| 020H    | D2H  | Devid        | ce t | уре           |     | W<br>P<br>S | De      | vic        | e spee    | d  | Device type = DH: I/O device<br>WPS = 0: No WP<br>Device speed = 2: 200 ns    | Device type, WPS, speed     |

| 022H    | 01H  | 1x           |      |               |     |             | 2k      | uni        | ts        |    | 2k byte of address space                                                      | Device size                 |

| 024H    | FFH  | List e       | end  | mark          | er  |             |         |            |           |    | End of device                                                                 | END marker                  |

| 026H    | 18H  | CIST         | PL   | JED           | EC  | С           |         |            |           |    | JEDEC ID common memory                                                        | Tuple code                  |

| 028H    | 02H  | TPL_         | LIN  | ١K            |     |             |         |            |           |    | Link length is 2 bytes                                                        | Link to next tuple          |

| 02AH    | DFH  | PCM<br>ID co |      | \'s m         | an  | ufa         | ctur    | er's       | JEDE      | С  | Manufacturer's ID code                                                        | JEDEC ID of PC Card ATA     |

| 02CH    | 01H  | PCM          | CIA  | A JEC         | )E( | C d         | evic    | e c        | ode       |    | 2nd byte of JEDEC ID                                                          | -                           |

|         |      |              |      |               |     |             |         |            |           |    |                                                                               |                             |

| Address | Data | 7 6 5 4 3 2 1 0                           | Description of contents                                                                                                                                                                                                                                                                                         | CIS function                          |

|---------|------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 02EH    | 20H  | CISTPL MANFID                             | Manufacturer's ID tuple                                                                                                                                                                                                                                                                                         | Tuple code                            |

| 030H    | 04H  | TPL_LINK                                  | Link length is 4 bytes                                                                                                                                                                                                                                                                                          | Link to next tuple                    |

| 032H    | 07H  | Low byte of PCMCIA<br>manufacturer's code | HITACHI JEDEC<br>manufacturer's ID                                                                                                                                                                                                                                                                              | Low byte of manufacturer's ID code    |

| 034H    | 00H  | High byte of PCMCIA manufacturer's code   | Code of 0 because other byte is JEDEC 1 byte manufac ID                                                                                                                                                                                                                                                         |                                       |

| 036H    | 00H  | Low byte of product code                  | HITACHI code for PC CARD<br>ATA                                                                                                                                                                                                                                                                                 | Low byte of product code              |

| 038H    | 00H  | High byte of product code                 | -                                                                                                                                                                                                                                                                                                               | High byte of product code             |

| 03AH    | 21H  | CISTPL MANFID                             | Function ID tuple                                                                                                                                                                                                                                                                                               | Tuple code                            |

| 03CH    | 02H  | TPL_LINK                                  | Link length is 2 bytes                                                                                                                                                                                                                                                                                          | Link to next tuple                    |

| 03EH    | 04H  | TPLFID_FUNCTION = 04H                     | Disk function, may be silicon, may be removable                                                                                                                                                                                                                                                                 | PC card function code                 |

| 040H    | 01H  | Reserved R P                              | R = 0: No BIOS ROM<br>P = 1: Configure card at<br>power on                                                                                                                                                                                                                                                      | System initialization byte            |

| 042H    | 22H  | CISTPL FUNCE                              | Function extension tuple                                                                                                                                                                                                                                                                                        | Tuple code                            |

| 044H    | 02H  | TPL_LINK                                  | Link length is 2 bytes                                                                                                                                                                                                                                                                                          | Link to next tuple                    |