## **Low-Cost Phase-Control IC with Soft Start**

## **Description**

The U2008B is designed as a phase-control circuit in bipolar technology. It enables load-current detection as well as mains-compensated phase control. Motor control

with load-current feedback and overload protection are preferred applications.

#### **Features**

- Full wave current sensing

- Mains supply variation compensated

- Variable soft-start or load-current sensing

- Voltage and current synchronization

- Automatic retriggering switchable

- Triggering pulse typ. 125 mA

- Internal supply-voltage monitoring

- Current requirement ≤ 3 mA

## **Applications**

- Low-cost motor control

- Domestic appliance

## **Block Diagram**

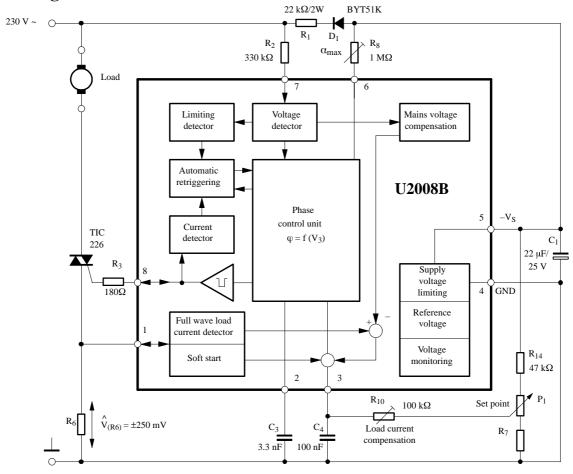

Figure 1. Block diagram with typical circuit: Load current sensing

Rev. A3, 08-Nov-99

# **Ordering Information**

| Extended Type Number | Package | Remarks          |

|----------------------|---------|------------------|

| U2008B-x             | DIP8    | Tube             |

| U2008B-xFP           | SO8     | Tube             |

| U2008B-xFPG3         | SO8     | Taped and reeled |

Figure 2. Block diagram with typical circuit: Soft start

## **Pin Description**

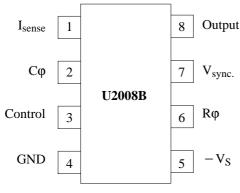

Figure 3. Pinning

## Mains Supply, Pin 5, Figure 2

The integrated circuit U2008B, which also contains voltage limiting, can be connected via  $D_1$  and  $R_1$  via the mains supply. Supply voltage — between Pin 4 (pos.,  $\perp$ ) and Pin 5 — is smoothed by  $C_1$ .

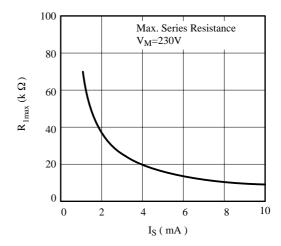

Series resistance R<sub>1</sub> can be calculated as follows:

$$R_{1\text{max}} = 0.85 \text{ x } \frac{V_{\text{M}} - V_{\text{Smax}}}{2 \text{ x } I_{\text{tot}}}$$

where:

$V_{\rm M}$  = Mains voltage

$V_{Smax}$  = Maximum supply voltage

$I_{tot}$  =  $I_{Smax}$  +  $I_x$  = Total current compensation  $I_{Smax}$  = Maximum current consumption of the IC  $I_x$  = Current consumption of the external

components

An operation with external stabilized DC voltage is not recommended.

## **Voltage Monitoring**

When the voltage is built up, uncontrolled output pulses are avoided by internal voltage monitoring. Apart from that, all latches in the circuit (phase control, load limit regulation) are reset and the soft-start capacitor is short circuited. This guarantees a specified start-up behavior each time the supply voltage is switched on or after short interruptions of the mains supply. Soft start is initiated after the supply voltage has been built up. This behavior guarantees a gentle start-up for the motor and automatically ensures the optimum run-up time.

| Pin | Symbol             | Function                     |

|-----|--------------------|------------------------------|

| 1   | I <sub>sense</sub> | Load current sensing         |

| 2   | Сф                 | Ramp voltage                 |

| 3   | Control            | Control input / compensation |

|     |                    | output                       |

| 4   | GND                | Ground                       |

| 5   | $-V_S$             | Supply voltage               |

| 6   | Rφ                 | Ramp current adjustment      |

| 7   | V <sub>sync.</sub> | Voltage synchronization      |

| 8   | Output             | Trigger output               |

#### Phase Control, Pin 6

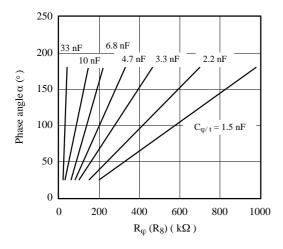

The function of the phase control is largely identical to that of the well-known IC U211B. The phase angle of the trigger pulse is derived by comparing the ramp voltage  $V_2$  at Pin 2 with the set value on the control input, Pin 3. The slope of the ramp is determined by  $C_3$  and its charging current I  $_{\varpi}$ .

The charging current can be regulated, changed, altered using  $R_8$  at Pin 6. The maximum phase angle,  $\alpha_{max}$ , (minimum current flow angle  $\phi_{min}$ ) can also be adjusted by using  $R_8$  (see figure 5).

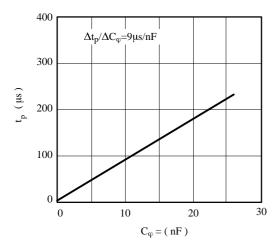

When the potential on Pin 2 reaches the set point level of Pin 3, a trigger pulse is generated whose pulse width,  $t_p$ , is determined from the value of  $C_3$  ( $t_p=9~\mu s/nF$ , see figure 7). At the same time, a latch is set with the output pulse, as long as the automatic retriggering has not been activated, then no more pulses can be generated in that half cycle. Control input at Pin 3 (with respect to Pin 4) has an active range from -9~V to -2~V. When  $V_3=-9~V$ , then the phase angle is at its maximum  $\alpha_{max}$ , i.e., the current flow angle is minimum. The minimum phase angle  $\alpha_{min}$  is set with  $V_3 \geq -1~V$ .

#### **Automatic Retriggering**

The current-detector circuit monitors the state of the triac after triggering by measuring the voltage drop at the triac gate. A current flow through the triac is recognized when the voltage drop exceeds a threshold level of typ. 40 mV.

If the triac is quenched within the relevant half wave after triggering (for example owing to low load currents before or after the zero crossing of current wave, or for commutator motors, owing to brush lifters), the automatic retriggering circuit ensures immediate retriggering, if necessary with a high repetition rate,  $t_{pp}/t_p$ , until the triac remains reliably triggered.

Rev. A3, 08-Nov-99

### **Current Synchronization, Pin 8**

Current synchronization fulfils two functions:

- Monitoring the current flow after triggering.

In case the triac extinguishes again or it does not switch on, automatic triggering is activated as long as triggering is successful.

- Avoiding triggering due to inductive load. In the case of inductive load operation, the current synchronization ensures that in the new half wave no pulse is enabled as long as there is a current available from the previous half wave, which flows from the opposite polarity to the actual supply voltage.

A special feature of the IC is the realization of current synchronization. The device evaluates the voltage at the pulse output between the gate and reference electrode of the triac. This results in saving separate current synchronization input with specified series resistance.

## **Voltage Synchronization with Mains Voltage Compensation, Pin 7**

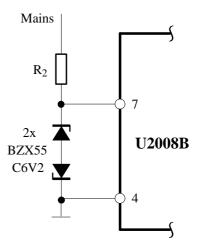

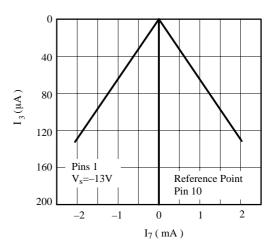

The voltage detector synchronizes the reference ramp with the mains supply voltage. At the same time, the mains-dependent input current at Pin 7 is shaped and rectified internally. This current activates the automatic retriggering and at the same time is available at Pin 3 (see figure 9). By suitable dimensioning, it is possible to attain specified compensation effect. retriggering and mains voltage compensation are not activated until  $|V_7 - 4|$  increases to 8 V. The resistance R<sub>svnc.</sub> defines the width of the zero voltage cross-over pulse, synchronization current, and hence the mains supply voltage compensation current. If the mains voltage compensation and the automatic retriggering are not required, both functions can be suppressed by limiting  $|V_{7-4}| \le 7 \text{ V (see figure 4)}.$

Figure 4. Suppression of automatic retriggering and mains voltage compensation

A further feature of the IC is the selection between softstart or load-current compensation. Soft start is possible by connecting a capacitor between Pin 1 and Pin 4, see figure 8. In the case of load-current compensation, Pin 1 is directly connected with resistance  $R_6$ , which is used for sensing load current.

#### **Load Current Detection, Pin 1**

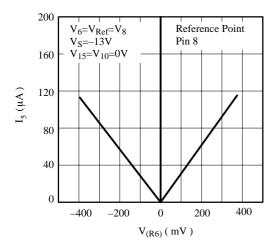

The circuit continuously measures the load current as a voltage drop at resistance  $R_6$ . The evaluation and use of both half waves results in a quick reaction to load-current change. Due to voltage at resistance  $R_6$ , there is an increase of input current at Pin 1. This current increase controls the internal current source, whose positive current values is available at Pin 3 (see figure 11). The output current generated at Pin 3 contains the difference from the load-current detection and from the mains-voltage compensation (see figure 9).

The effective control voltage is the final current at Pin 3 together with the desired value network. An increase of mains voltage causes the increase of control angle  $\alpha$ . An increase of load current results in a decrease in the control angle. This avoids a decrease in revolution by increasing the load as well as the increase of revolution by the increment of mains supply voltage.

# **Absolute Maximum Ratings**

$V_S = 14 \text{ V}$ , reference point Pin 4, unless otherwise specified

| Parameters                                  |       | Symbol               | Value          | Unit |

|---------------------------------------------|-------|----------------------|----------------|------|

| Current limitation                          | Pin 5 | $-I_S$               | 30             | mA   |

| $t \leq 10 \mu s$                           |       | $-i_S$               | 100            | mA   |

| Sync. currents                              | Pin 7 | ± I <sub>syncV</sub> | 5              | mA   |

| $t \le 10 \mu s$                            |       | ±i <sub>syncV</sub>  | 20             | mA   |

| Phase control                               | Pin 3 | -                    |                |      |

| Control voltage                             |       | $-V_{I}$             | $V_S$ to $0$   | V    |

| Input current                               |       | $\pm$ $I_{I}$        | 500            | μΑ   |

| Charge current Pin 6                        |       | -I <sub>omax</sub>   | 0.5            | mA   |

| Load current monitoring / Soft start, Pin 1 |       |                      |                |      |

| Input current                               |       | $I_{\mathbf{I}}$     | 1              | mA   |

| Input voltage                               |       | $V_{\rm I}$          | -40  to + 125  | V    |

| Pulse output                                |       |                      |                |      |

| Input voltage                               | Pin 8 | $+V_{I}$             | 2              | V    |

|                                             |       | $-V_{I}$             | $V_{S}$        | V    |

| Storage temperature range                   |       | $T_{stg}$            | -40  to  + 125 | °C   |

| Junction temperature range                  |       | $T_{j}$              | -10  to  +125  | °C   |

# **Thermal Resistance**

| Parameters       |                | Symbol     | Value | Unit |

|------------------|----------------|------------|-------|------|

| Junction ambient | DIP8           | $R_{thJA}$ | 110   | K/W  |

|                  | SO8 on p.c.    | $R_{thJA}$ | 220   | K/W  |

|                  | SO8 on ceramic | $R_{thJA}$ | 140   | K/W  |

Rev. A3, 08-Nov-99 5 (10)

# **U2008B**

# **Electrical Characteristics**

$V_S = -13 \text{ V}, T_{amb} = 25^{\circ}\text{C},$  reference point Pin 4, unless otherwise specified

| Parameters                                               | Test Conditions / Pins                        | Symbol               | Min.  | Тур.   | Max.  | Unit           |

|----------------------------------------------------------|-----------------------------------------------|----------------------|-------|--------|-------|----------------|

| Supply Pin 5                                             |                                               |                      |       |        |       |                |

| Supply-voltage limitation                                | $-I_S = 3.5 \text{ mA}$                       | $-V_{S}$             | 14.5  |        | 16.5  | V              |

|                                                          | $-I_S = 30 \text{ mA}$                        | $-V_{S}$             | 14.6  |        | 16.8  | V              |

| Current requirement                                      | Pins 1, 4 and 7 open                          | $-I_S$               |       |        | 3.0   | mA             |

| Voltage monitoring                                       | Pin 5                                         |                      |       |        |       |                |

| Turn-on threshold                                        |                                               | -V <sub>TON</sub>    |       | 11.3   | 12.3  | V              |

| Phase control                                            |                                               |                      |       |        |       |                |

| Input current                                            | Voltage sync. Pin 7                           | ± I <sub>syncV</sub> |       | 0.15   | 2     | mA             |

|                                                          | Current sync. Pin 8                           | ±I <sub>syncI</sub>  | 3     |        | 30    | μA             |

| Voltage limitation                                       | $\pm I_L = 2 \text{ mA}$ Pin 7                | $\pm V_{syncV}$      | 8.0   | 8.5    | 9.0   | V              |

| Reference ramp, see figure 5                             | 5                                             |                      |       | •      |       |                |

| Charge current                                           | Pin 7                                         | Ιφ                   | 1     |        | 100   | μA             |

| Start voltage                                            | Pin 2                                         | -V <sub>max</sub>    | 1.85  | 1.95   | 2.05  | V              |

| Temperature coefficient of                               |                                               |                      |       |        |       |                |

| start voltage                                            | Pin 2                                         | -TC <sub>R</sub>     |       | -0.003 |       | %/K            |

| $R_{\phi}$ – reference voltage                           | $I_{\phi} = 10 \mu A$ Pins $6 - 5$            | $V_{R\phi}$          | 0.96  | 1.02   | 1.10  | V              |

| Temperature coefficient                                  | $I_{\varphi} = 10 \mu A$ Pin 6                | $TC_{VR\phi}$        |       | 0.03   |       | %/K            |

|                                                          | $I_{\varphi} = 1 \mu A$                       | $TC_{VR\phi}$        |       | 0.06   |       | %/K            |

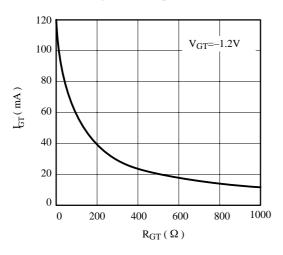

| <b>Pulse output,</b> see figure 6                        | Pin 8                                         |                      | 1     |        | 1     |                |

| Output-pulse current                                     | $V_8 = -1.2$ , $R_{GT} = 0 \Omega$            | $I_0$                | 100   | 125    | 150   | mA             |

| Output-pulse width                                       | $C_3 = 3.3 \text{ nF}, V_S = V_{limit}$       | t <sub>p</sub>       |       | 30     |       | μs             |

| Automatic retriggering                                   | Pin 8                                         |                      |       | •      |       |                |

| Turn-on threshold voltage                                |                                               | $\pm V_{ION}$        | 20    |        | 60    | mV             |

| Repetition rate                                          | $I_7 \geq 150 \mu\text{A}$                    | t <sub>pp</sub>      | 3     | 5      | 7.5   | t <sub>p</sub> |

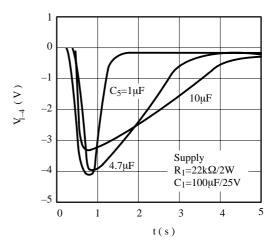

| <b>Soft start,</b> see figure 8                          | Pin 1                                         |                      |       |        |       |                |

| Starting current                                         | $V_{1-4} = 8 V$                               | $I_0$                | 5     | 10     | 15    | μΑ             |

| Final current                                            | $V_{1-4} = -2 V$                              | $I_0$                | 15    | 25     | 40    | μΑ             |

| Discharge current                                        |                                               | $-I_0$               | 0.5   |        |       | mA             |

| Output current                                           | Pin 3                                         | -I <sub>0</sub>      | 0.2   |        | 2     | mA             |

| Mains voltage compensation                               | n, see figure 9                               |                      |       |        |       |                |

| Current transfer gain I <sub>7</sub> /I <sub>3</sub>     | Pins 7, Pin 3                                 |                      |       |        |       |                |

|                                                          | Pins 1 and 2 open                             | Gi                   | 14    | 17     | 20    |                |

| Reverse current                                          | $V_{(R6)} = V_3 = V_7 = 0$ , Pin 3            | $\pm I_R$            |       |        | 2     | μΑ             |

| <b>Load-current detection,</b> $V_7 = 0$ , see figure 11 |                                               |                      |       |        |       |                |

| Transfer gain                                            | I <sub>3</sub> /V <sub>1</sub>                | G                    | 0.280 | 0.320  | 0.370 | μA/mV          |

| Offset current                                           | $V_1 = 0, V_3 = -8 \text{ V}, \text{ Pin } 3$ | $I_0$                | 0     | 3      | 6     | μA             |

| Input voltage                                            | Pin 1                                         | $-V_{I}$             | 300   |        | 400   | mV             |

| Input offset voltage                                     | Pin 1                                         | ±V <sub>0</sub>      |       |        | 6     | mV             |

Figure 5. Ramp control

Figure 6. Pulse output

Figure 7. Output-pulse width

Figure 8. Option soft start

Figure 9. Mains voltage compensation

Figure 10. Maximum resistance of R<sub>1</sub>

Rev. A3, 08-Nov-99 7 (10)

Figure 11. Load-current detection

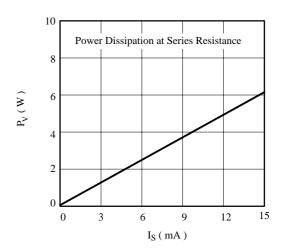

Figure 13. Power dissipation of R<sub>1</sub> according to current consumption

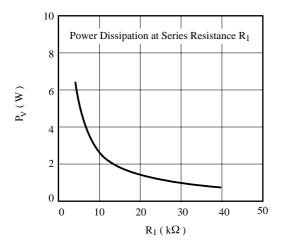

Figure 12. Power dissipation of R<sub>1</sub>

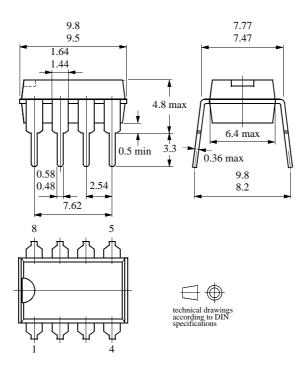

# **Package Information**

Package DIP8

Dimensions in mm

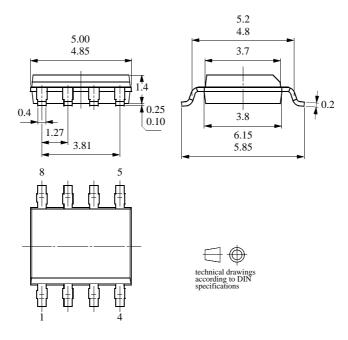

Package SO8

Dimensions in mm

Rev. A3, 08-Nov-99

## **Ozone Depleting Substances Policy Statement**

It is the policy of **TEMIC Semiconductor GmbH** to

- 1. Meet all present and future national and international statutory requirements.

- 2. Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

**TEMIC Semiconductor GmbH** has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

- 1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

- 2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

- 3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

**TEMIC Semiconductor GmbH** can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

We reserve the right to make changes to improve technical design and may do so without further notice.

Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use TEMIC Semiconductors products for any unintended or unauthorized application, the buyer shall indemnify TEMIC Semiconductors against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

TEMIC Semiconductor GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Telephone: 49 (0)7131 67 2594, Fax number: 49 (0)7131 67 2423