#### **New Product**

# **Vishay Siliconix**

# Half-Bridge N-Channel MOSFET Driver for DC/DC Conversion

#### **FEATURES**

- PWM With Tri-State Enable

- 12-V Low-Side Gate Drive (SiP41109)

- 8-V Low-Side Gate Drive (SiP41110)

- Undervoltage Lockout

- Internal Bootstrap Diode

- Switching Frequency Up to 1 MHz

- 30-ns Max Propagation Delay

- Drive MOSFETs In 5- to 48-V Systems

- Adaptive Shoot-Through Protection

#### **APPLICATIONS**

- Multi-Phase DC/DC Conversion

- High Current Low Voltage DC/DC Converters

- High Frequency DC/DC Converters

- Mobile and Desktop Computer DC/DC Converters

- Core Voltage Supplies for PC Micro-Processors

#### **DESCRIPTION**

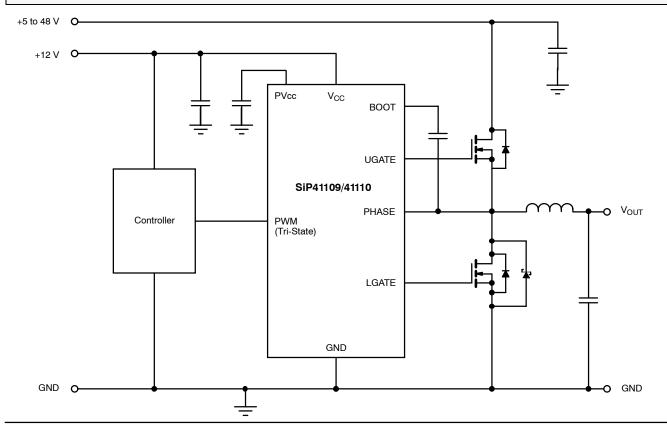

The SiP41109 and SiP41110 are high-speed half-bridge MOSFET drivers for use in high frequency, high current, multiphase dc-to-dc synchronous rectifier buck power supplies. They are designed to operate at switching frequencies up to 1 MHz. The high-side driver is bootstrapped to allow driving n-channel MOSFETs.

They feature adaptive shoot-through protection to prevent simultaneous conduction of the external MOSFETs. There are two options available for the voltage of the high-side and

low-side drivers. In the SiP41109, the regulator supplies gate drive voltage to the high-side driver and  $V_{CC}$  supplies the low-side driver. in the SiP41110, the regulator supplies the high- and low-side gate drive voltage.

The SiP41109 and SiP41110 are assembled in a lead (Pb)-free 8-pin SOIC package for operation over the industrial operating range (-40 °C to 85 °C).

#### TYPICAL APPLICATION CIRCUIT

# Vishay Siliconix

### **New Product**

#### ABSOLUTE MAXIMUM RATINGS (ALL VOLTAGES REFERENCED TO GND = 0 V)

| V <sub>CC</sub> , PV <sub>CC</sub> | Thermal Impedance (⊖ <sub>JA</sub> ) <sup>b</sup>             |

|------------------------------------|---------------------------------------------------------------|

| BOOT, PHASE0.3 to 55 V             | SO-8                                                          |

| BOOT to PHASE0.3 to 15 V           |                                                               |

| Storage Temperature                | Notes                                                         |

| Operating Junction Temperature     | Device mounted with all leads soldered or welded to PC board. |

| Power Dissipation <sup>a</sup>     | b. Derate 7.7 mW/°C                                           |

| SO-8 770 mW                        |                                                               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING RANGE (ALL VOLTAGES REFERENCED TO GND = 0 V)

| V <sub>CC</sub> | BOOT to PHASE8 V                      |

|-----------------|---------------------------------------|

| V <sub>LX</sub> | Operating Temperature Range40 to 85°C |

| CROOT           |                                       |

| SPECIFICAT            | <b>FIONS</b> <sup>a</sup> |                          |                                                                                                                                                |                      |                  |              |                  |      |

|-----------------------|---------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|--------------|------------------|------|

|                       |                           |                          | Test Conditions Unless Specified $V_{CC} = 12 \text{ V, V}_{BOOT} - \text{V}_{PHASE} = 8 \text{ V}$ $T_A = -40 \text{ to } 85^{\circ}\text{C}$ |                      |                  | Limits       |                  |      |

| Parame                | eter                      | Symbol                   |                                                                                                                                                |                      | Min <sup>a</sup> | Турь         | Max <sup>a</sup> | Unit |

| Power Supplie         | s                         |                          |                                                                                                                                                |                      |                  |              |                  |      |

| Supply Voltage        |                           | V <sub>CC</sub>          |                                                                                                                                                |                      | 10.8             |              | 13.2             | V    |

| Quiescent Current     |                           | I <sub>CCQ</sub>         | PWM Non-Switching                                                                                                                              |                      |                  | 5.6          | 9.5              |      |

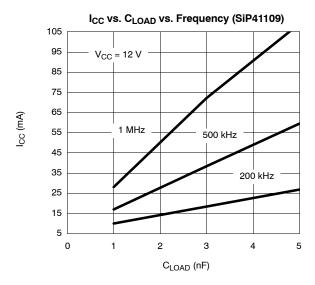

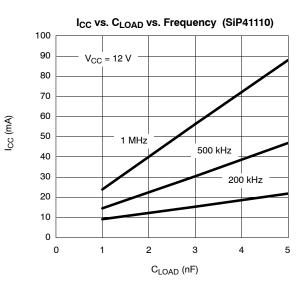

| Supply Current        |                           | I <sub>DD</sub>          | f <sub>PWM</sub> = 100 kHz, C <sub>LOAD</sub> = 3 nF                                                                                           | SiP41109<br>SiP41110 |                  | 12.5<br>11.0 |                  | mA   |

| Tristate (Shutdown)   | Current                   | I <sub>CCT</sub>         | PWM = Open                                                                                                                                     | 1                    |                  | 850          | 1200             | μΑ   |

| Reference Volt        | age                       |                          |                                                                                                                                                |                      |                  |              |                  | l    |

| Break-Before-Make     |                           | $V_{BBM}$                |                                                                                                                                                |                      |                  | 2.5          |                  | V    |

| PWM Input             |                           |                          |                                                                                                                                                |                      | •                | •            |                  |      |

| Input High            |                           | V <sub>IH</sub>          |                                                                                                                                                |                      | 4.0              |              | V <sub>CC</sub>  | v    |

| Input Low             |                           | V <sub>IL</sub>          |                                                                                                                                                |                      |                  |              | 1.0              | · ·  |

| Bias Current          |                           | Ι <sub>Β</sub>           | PWM 5 V or 0 V                                                                                                                                 |                      |                  | ±600         | ±1000            | μΑ   |

| Tristate Threshold    | High                      | V <sub>TSH</sub>         |                                                                                                                                                |                      | 3.0              |              |                  | V    |

|                       | Low                       | V <sub>TSL</sub>         |                                                                                                                                                |                      |                  |              | 2.0              | V    |

| Tristate Holdoff Time | eout <sup>c</sup>         | t <sub>TST</sub>         |                                                                                                                                                |                      |                  | 240          |                  | ns   |

| Bootstrap Dioc        | de                        |                          |                                                                                                                                                |                      |                  |              |                  |      |

| Forward Voltage       |                           | V <sub>F</sub>           | $I_F = 40 \text{ mA}, T_A = 25^{\circ}\text{C}$                                                                                                | ;                    | 0.70             | 0.85         | 1.0              | V    |

| MOSFET Drive          | rs                        |                          |                                                                                                                                                |                      |                  |              |                  |      |

| High-Side Drive Cur   | rontC                     | I <sub>PKH(source)</sub> | V <sub>BOOT</sub> – V <sub>PHASE</sub> = 8 V                                                                                                   |                      |                  | 0.8          |                  |      |

| High-Side Drive Cui   | i enic                    | I <sub>PKH(sink)</sub>   |                                                                                                                                                |                      |                  | 1.0          |                  |      |

|                       |                           | I <sub>PKL(source)</sub> | V <sub>PVCC</sub> = 8 V SiP41110                                                                                                               |                      | 0.9              |              | Α                |      |

| Low-Side Drive Cur    | -ent <sup>C</sup>         | I <sub>PKL(sink)</sub>   | *PVCC - 0 *                                                                                                                                    | S., 1110             | 1.2              |              | )                |      |

| Low-Olde Dilve Odil   | CIT                       | I <sub>PKL(source)</sub> | V <sub>PVCC</sub> = 12 V                                                                                                                       | SiP41109             |                  | 1.4          |                  |      |

|                       |                           | I <sub>PKL(sink)</sub>   | *PVCC - 12 *                                                                                                                                   | 011 41109            |                  | 1.8          |                  |      |

### **New Product**

# Vishay Siliconix

|                         | Test Conditions Unless Specified                                                                                                                                 |                           |                                                                               | Limits                                    |                                                                               |                                                                               |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|

| Symbol                  | $V_{CC}$ = 12 V, $V_{BOOT}$ - $V_{PHASE}$<br>$T_A$ = -40 to 85°C                                                                                                 | = 8 V                     | Min <sup>a</sup>                                                              | Typb                                      | Max <sup>a</sup>                                                              | Unit                                                                          |  |

| •                       |                                                                                                                                                                  |                           | •                                                                             | •                                         | •                                                                             | ı                                                                             |  |

| R <sub>DH(source)</sub> | V <sub>BOOT</sub> - V <sub>PHASE</sub> = 8 V, PHASE                                                                                                              | E = GND                   |                                                                               | 2.3                                       | 4.2<br>3.5                                                                    |                                                                               |  |

| R <sub>DL(source)</sub> | V <sub>PVCC</sub> = 8 V                                                                                                                                          | SiP41110                  |                                                                               | 2.9                                       | 5.2                                                                           |                                                                               |  |

| R <sub>DL(source)</sub> | V <sub>PVCC</sub> = 12 V                                                                                                                                         | SiP41109                  |                                                                               | 2.4                                       | 4.3                                                                           |                                                                               |  |

| ` '                     |                                                                                                                                                                  |                           |                                                                               |                                           | 2.2                                                                           |                                                                               |  |

|                         | 10% - 90%, V <sub>BOOT</sub> - V <sub>PHASE</sub> = 8 V,                                                                                                         | C <sub>LOAD</sub> = 3 nF  |                                                                               |                                           |                                                                               |                                                                               |  |

| чн                      |                                                                                                                                                                  |                           |                                                                               |                                           |                                                                               |                                                                               |  |

| <del> </del>            | 10% – 90%, V <sub>BOOT</sub> – V <sub>PHASE</sub> = 12 V,                                                                                                        | $C_{LOAD} = 3 \text{ nF}$ |                                                                               |                                           | -                                                                             |                                                                               |  |

| † <sub>4/-</sub>        |                                                                                                                                                                  |                           |                                                                               |                                           | -                                                                             |                                                                               |  |

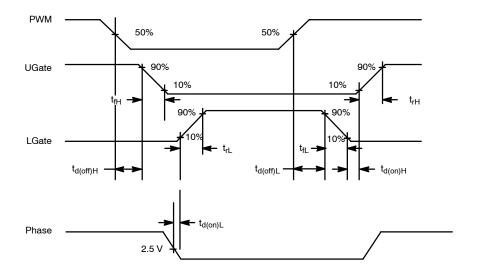

| t <sub>d(on)</sub> H    |                                                                                                                                                                  |                           |                                                                               | 15                                        |                                                                               | }                                                                             |  |

| +.                      |                                                                                                                                                                  | SiP41110                  |                                                                               | 40                                        |                                                                               | ns                                                                            |  |

| ۲L                      |                                                                                                                                                                  | SiP41109                  |                                                                               | 40                                        |                                                                               |                                                                               |  |

| te                      | C <sub>LOAD</sub> = 3 nF                                                                                                                                         | SiP41110                  |                                                                               | 30                                        |                                                                               |                                                                               |  |

|                         | 10% – 90%, V <sub>BOOT</sub> – V <sub>PHASE</sub> = 12 V<br>C <sub>LOAD</sub> = 3 nF                                                                             | SiP41109                  |                                                                               | 30                                        |                                                                               |                                                                               |  |

|                         | See Timing Waveforms                                                                                                                                             |                           |                                                                               |                                           |                                                                               |                                                                               |  |

| <sup>t</sup> d(on)L     |                                                                                                                                                                  |                           |                                                                               | 13                                        |                                                                               |                                                                               |  |

| touvee                  |                                                                                                                                                                  |                           |                                                                               | 380                                       |                                                                               | ns                                                                            |  |

| PHASE                   |                                                                                                                                                                  |                           |                                                                               | 000                                       |                                                                               | 110                                                                           |  |

|                         | T                                                                                                                                                                |                           | 7.0                                                                           | 1 0                                       | 0.4                                                                           |                                                                               |  |

|                         |                                                                                                                                                                  |                           | 7.6                                                                           |                                           |                                                                               | V                                                                             |  |

|                         | V <sub>DDV</sub> = 0 V                                                                                                                                           |                           | 120                                                                           |                                           |                                                                               | mA                                                                            |  |

| LNR                     |                                                                                                                                                                  |                           |                                                                               | 0.05                                      | 0.5                                                                           | %/V                                                                           |  |

| LDR                     | 5 mA to 80 mA                                                                                                                                                    |                           |                                                                               | 0.1                                       | 1.0                                                                           | %                                                                             |  |

|                         | l                                                                                                                                                                |                           |                                                                               | 1                                         |                                                                               | 1                                                                             |  |

| T                       |                                                                                                                                                                  |                           |                                                                               | 6.7                                       | 7.2                                                                           |                                                                               |  |

| V <sub>UVLO2</sub>      |                                                                                                                                                                  |                           |                                                                               | 6.4                                       | 6.9                                                                           | V                                                                             |  |

| Hyst                    |                                                                                                                                                                  |                           | 100                                                                           | 300                                       | 500                                                                           | mV                                                                            |  |

| Lockout                 |                                                                                                                                                                  |                           |                                                                               |                                           |                                                                               |                                                                               |  |

| V <sub>UVHS</sub>       | Rising or Falling                                                                                                                                                |                           | 2.5                                                                           | 3.35                                      | 4.0                                                                           | V                                                                             |  |

| ut                      |                                                                                                                                                                  |                           |                                                                               |                                           |                                                                               |                                                                               |  |

| V <sub>UVLO1</sub>      |                                                                                                                                                                  |                           | 5.0                                                                           | 5.3                                       | 5.6                                                                           | V                                                                             |  |

| POR                     |                                                                                                                                                                  |                           |                                                                               | 2.5                                       |                                                                               | ms                                                                            |  |

|                         | ·                                                                                                                                                                |                           |                                                                               | •                                         |                                                                               | •                                                                             |  |

| T <sub>SD</sub>         | Temperature Rising                                                                                                                                               |                           |                                                                               | 165                                       |                                                                               |                                                                               |  |

| i                       | Temperature Falling                                                                                                                                              |                           | 1                                                                             | 25                                        | <b>.</b>                                                                      | °C                                                                            |  |

|                         | RDH(source) RDH(sink) RDL(source) RDL(sink) RDL(source) RDL(sink) RDL(sink) trH tfH  td(off)H td(on)H  trL  tfL  VUVLO2 Hyst LDR  VUVLO2 Hyst LOCKOUT VUVLO1 POR | Symbol                    | Symbol   V <sub>CC</sub> = 12 V, V <sub>BOOT</sub> - V <sub>PHASE</sub> = 8 V | Symbol   VCC = 12 V, VBOOT - VPHASE = 8 V | Symbol   V <sub>CC</sub> = 12 V, V <sub>BOOT</sub> - V <sub>PHASE</sub> = 8 V | Symbol   V <sub>CC</sub> = 12 V, V <sub>BOOT</sub> - V <sub>PHASE</sub> = 8 V |  |

Notes

a. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum.

b. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing and are measured at V<sub>CC</sub> = 12 V unless otherwise noted.

# Vishay Siliconix

# **New Product**

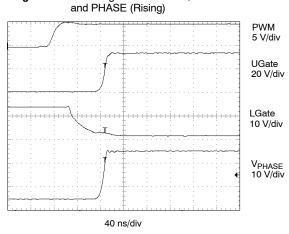

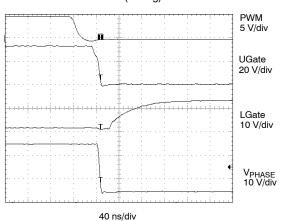

### **TIMING WAVEFORMS**

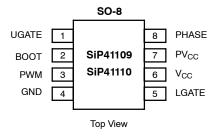

# PIN CONFIGURATION AND TRUTH TABLE

| TRUTH TABLE |       |       |  |

|-------------|-------|-------|--|

| PWM         | UGATE | LGATE |  |

| L           | L     | Н     |  |

| Н           | Н     | L     |  |

| Tri-State   | L     | L     |  |

| ORDERING INFORMATION                 |                           |         |

|--------------------------------------|---------------------------|---------|

| Part Number Temperature Range Markin |                           | Marking |

| SiP41109DY-T1—E3                     | −40 to 85°C               | 41109   |

| SiP41110DY-T1—E3                     | - <del>4</del> 0 to 63 °C | 41110   |

| Eval Kit   | Temperature Range |  |

|------------|-------------------|--|

| SiP41109DB | -40 to 85°C       |  |

| SiP41110DB | 7 40 10 00 0      |  |

| PIN DESCRIP | PIN DESCRIPTION  |                                                                                                    |  |  |  |

|-------------|------------------|----------------------------------------------------------------------------------------------------|--|--|--|

| Pin Number  | Name             | Function                                                                                           |  |  |  |

| 1           | UGATE            | 8-V high-side MOSFET gate drive                                                                    |  |  |  |

| 2           | BOOT             | Bootstrap supply for high-side driver. The bootstap capacitor is connected between BOOT and PHASE. |  |  |  |

| 3           | PWM              | Input signal for the MOSFET drivers and tri-state enable                                           |  |  |  |

| 4           | GND              | Ground                                                                                             |  |  |  |

| 5           | LGATE            | Synchronous or low-side MOSFET gate drive                                                          |  |  |  |

| 6           | V <sub>CC</sub>  | 12-V supply. Connect a bypass capacitor ≥1 μF from here to ground                                  |  |  |  |

| 7           | PV <sub>CC</sub> | 8-V Voltage Regulator Output. Connect a bypass capacitor ≥ 1 μF from here to ground                |  |  |  |

| 8           | PHASE            | Connection to source of high-side MOSFET, drain of the low-side MOSFET, and the inductor           |  |  |  |

#### **New Product**

# **Vishay Siliconix**

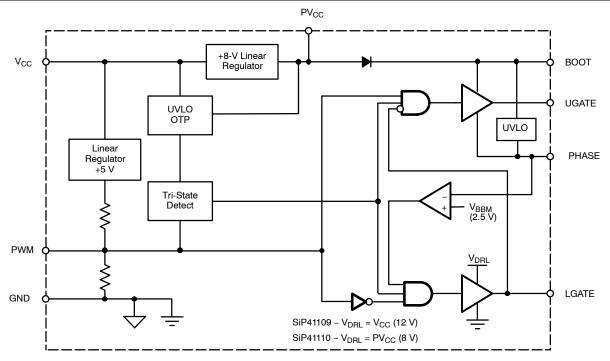

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

#### **DETAILED OPERATION**

#### PWM/Tri-State Enable

The PWM pin controls the switching of the external MOSFETs. The driver logic operates in a noninverting configuration. The PWM input stage should be driven by a signal with fast transition times, like those provided by a PWM controller or logic gate, (<200 ns). The PWM input functions as a logic input and is not intended for applications where a slow changing input voltage is used to generate a switching output when the input switching threshold voltage is reached.

#### Shutdown

The SiP41109/41110 enters shutdown mode when the signal driving PWM enters the tri-state window for more than 240 ns. The shutdown state is removed when the PWM signal moves outside the tri-state window. If the PWM is left open, the pin is held to 2.5 V by an internal voltage divider, thus forcing the tri-state condition.

#### **Low-Side Driver**

In the SiP41109, the low-side driver voltage is supplied by  $V_{CC}$ . In the SiP41110, the low-side driver voltage is supplied by  $PV_{CC}$ . During shutdown, LGATE is held low.

#### **High-Side Driver**

The high-side driver is isolated from the substrate to create a floating high-side driver so that an n-channel MOSFET can be

used for the high-side switch. The high-side driver voltage is supplied by  $PV_{CC}$ . The voltage is maintained by a floating bootstrap capacitor, which is continually recharged by the switching action of the output. During shutdown UGATE is held low.

#### Gate Drive Voltage (PV<sub>CC</sub>) Regulator

An integrated 80-mA, 8-V regulator supplies voltage to the  $PV_{CC}$  pin and it current limits at 200 mA typical when the output is shorted to ground. A capacitor (1  $\mu F$  minimum) must be connected to the  $PV_{CC}$  pin to stabilize the regulator output. The voltage on  $PV_{CC}$  is supplied to the integrated bootstrap diode.  $PV_{CC}$  is used to recharge the bootstrap capacitor and powers the SiP41110 low-side driver.  $PV_{CC}$  pin can be externally connected to  $V_{CC}$  to bypass the 8-V regulator and increase high-side gate drive to 12 V. If the  $PV_{CC}$  pin is connected to  $V_{CC}$  the system voltage should not exceed 43V.

### **Bootstrap Circuit**

The internal bootstrap diode and an external bootstrap capacitor supply voltage to the BOOT pin. An integrated bootstrap diode replaces the external diode normally needed for the bootstrap circuit; only a capacitor is necessary to complete the bootstrap circuit. The bootstrap capacitor is sized according to,

$C_{BOOT} = (Q_{GATE}/(\Delta V_{BOOT} - V_{PHASE})) \times 10$

# **Vishay Siliconix**

#### **New Product**

where  $Q_{GATE}$  is the gate charge needed to turn on the high-side MOSFET and  $\Delta V_{BOOT}-$  PHASE is the amount of droop allowed in the bootstrapped supply voltage when the high-side MOSFET is driven high. The bootstrap capacitor value is typically 0.1  $\mu F$  to 1  $\mu F$ . The bootstrap capacitor voltage rating must be greater than  $V_{CC}$  + 12 V to withstand transient spikes and ringing.

#### **Shoot-Through Protection**

The external MOSFETs are prevented from conducting at the same time during transitions. Break-before-make circuits monitor the voltages on the PHASE pin and the LGATE pin and control the switching as follows: When the signal on PWM goes low, UGATE will go low after an internal propagation delay. After the voltage on PHASE falls below 2.5 V by the inductor action, the low-side driver is enabled and LGATE goes high after some delay. When the signal on PWM goes high, LGATE will go low after an internal propagation delay. After the voltage on LGATE drops below 2.5 V the high-side driver is enabled and UGATE will go high after an internal propagation delay. If PHASE does not drop below 2.5 V within 380 ns after UGATE goes low, LGATE is forced high until the next PWM transition.

#### **V<sub>CC</sub>** Bypass Capacitor

MOSFET drivers draw large peak currents from the supplies when they switch. A local bypass capacitor is required to supply this current and reduce power supply noise. Connect a 1- $\mu$ F ceramic capacitor as close as practical between the V<sub>CC</sub> and GND pins.

#### **Undervoltage Lockout**

Undervoltage lockout prevents control of the circuit until the supply voltages reach valid operating levels. The UVLO circuit forces LGATE and UGATE to low when  $V_{CC}$  is below its specified voltage. A separate UVLO forces UGATE low when the voltage between BOOT and PHASE is below the specified voltage.

#### **Thermal Protection**

If the die temperature rises above 165°C, the thermal protection disables the drivers. The drivers are re-enabled after the die temperature has decreased below 140°C.

#### TYPICAL CHARACTERISTICS

### **TYPICAL WAVEFORMS**

Figure 2. PWM Signal vs. HS Gate, LS Gate

**Figure 3.** PWM Signal vs. HS Gate, LS Gate and PHASE (Falling)

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="http://www.vishay.com/ppg?73023">http://www.vishay.com/ppg?73023</a>.

# **Legal Disclaimer Notice**

Vishay

# **Notice**

Specifications of the products displayed herein are subject to change without notice. Vishay Intertechnology, Inc., or anyone on its behalf, assumes no responsibility or liability for any errors or inaccuracies.

Information contained herein is intended to provide a product description only. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Vishay's terms and conditions of sale for such products, Vishay assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of Vishay products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Vishay for any damages resulting from such improper use or sale.

Document Number: 91000 www.vishay.com Revision: 08-Apr-05