**SAA7199B**

#### **FEATURES**

- Monolithic integrated CMOS video encoder circuit

- Standard MPU (12 lines) and I<sup>2</sup>C-bus interfaces for controls

- Three 8-bit signal inputs PD7 to PD0 for RGB respectively YUV or indexed colour signals (Tables 19 to 26)

- Square pixel and CCIR input data rates

- Band limited composite sync pulses

- Three 256 x 8 colour look-up tables (CLUTs) for example for gamma correction

- External subcarrier from a digital decoder (SAA7151B or SAA7191B)

- · Multi-purpose key for real time format switching

- · Autonomous internal blanking

- Optional GENLOCK operation with adjustable horizontal sync timing and adjustable subcarrier phase

- Stable GENLOCK operation in VCR standard playback mode

- · Optional still video capture extension

- Three suitable video 9-bit digital-to-analog converters

- Composite analog output signals CVBS, Y and C for PAL/NTSC

- Line 21 data insertion possible.

#### **GENERAL DESCRIPTION**

The SAA7199B encodes digital baseband colour/video data into analog Y, C and CVBS signals (S-video included). Pixel clock and data are line-locked to the horizontal scanning frequency of the video signal. The circuit can be used in a square pixel or in a consumer TV application. Flexibility is provided by programming facilities via MPU-bus (parallel) or I<sup>2</sup>C-bus (serial).

#### **QUICK REFERENCE DATA**

| SYMBOL              | PARAMETER                                                             | MIN.           | TYP. | MAX. | UNIT |

|---------------------|-----------------------------------------------------------------------|----------------|------|------|------|

| $V_{DDD}$           | digital supply voltage (pins 2, 21 and 41)                            | 4.5            | 5.0  | 5.5  | v    |

| $V_{DDA}$           | analog supply voltage (pins 64, 66, 70 and 72)                        | 4.75           | 5.0  | 5.25 | V    |

| I <sub>P(tot)</sub> | total supply current                                                  | _              | _    | 200  | mA   |

| VI                  | input signal levels                                                   | TTL-compatible |      |      |      |

| Vo                  | analog output voltage Y, C and CVBS without load (peak-to-peak value) |                | 2    | _    | v    |

| RL                  | output load resistance                                                | 90             | 1_   | _    | Ω    |

| ILE                 | LF integral linearity error in output signal (9-bit DAC)              | _              | -    | ±1   | LSB  |

| DLE                 | LF differential linearity error in output signal (9-bit DAC)          | _              | 1_   | ±0.5 | LSB  |

| T <sub>amb</sub>    | operating ambient temperature                                         | 0              | 1_   | 70   | °C   |

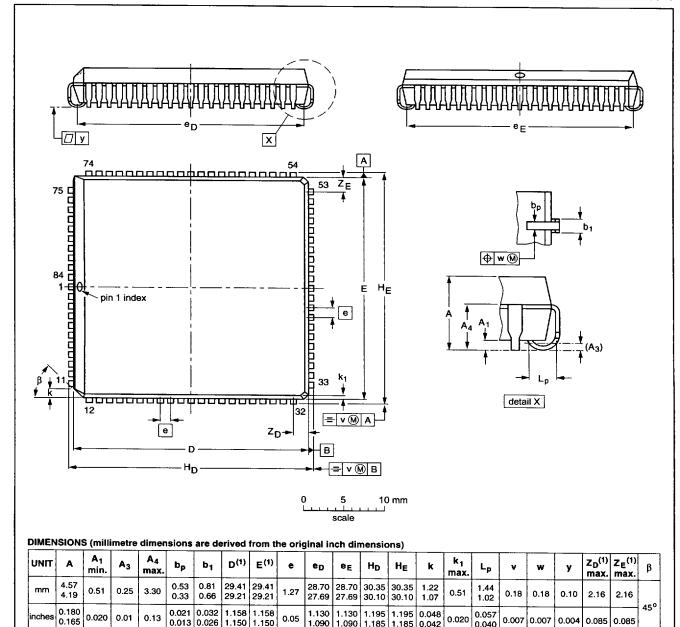

#### **ORDERING INFORMATION**

| TYPE       |        | PACKAGE                               |          |

|------------|--------|---------------------------------------|----------|

| NUMBER     | NAME   | DESCRIPTION                           | VERSION  |

| SAA7199BWP | PLCC84 | plastic leaded chip carrier; 84 leads | SOT189-2 |

1996 Sep 27

2

**-** 7110826 0109318 877 **--**

**SAA7199B**

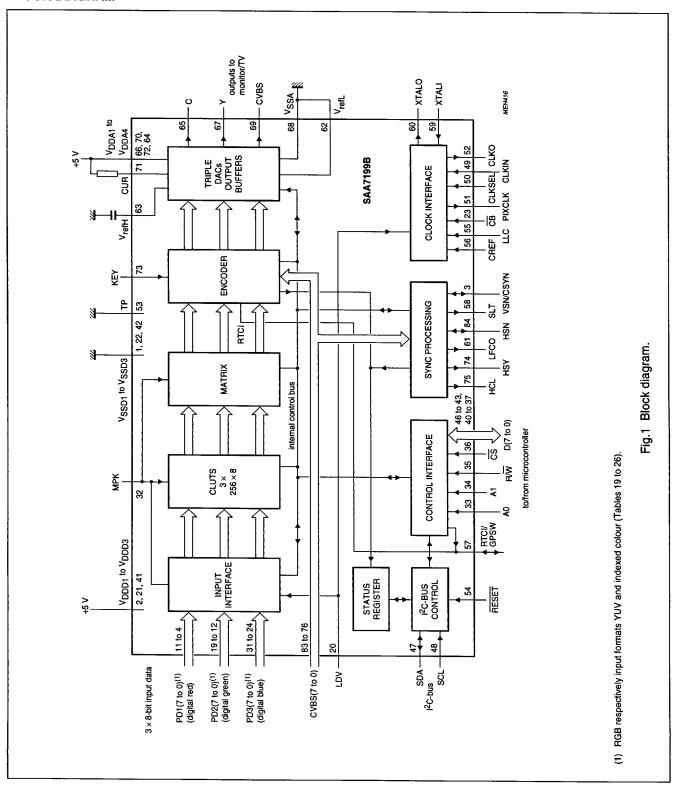

#### **BLOCK DIAGRAM**

1996 Sep 27

3

**■** 7110826 0109319 703 **■**

**SAA7199B**

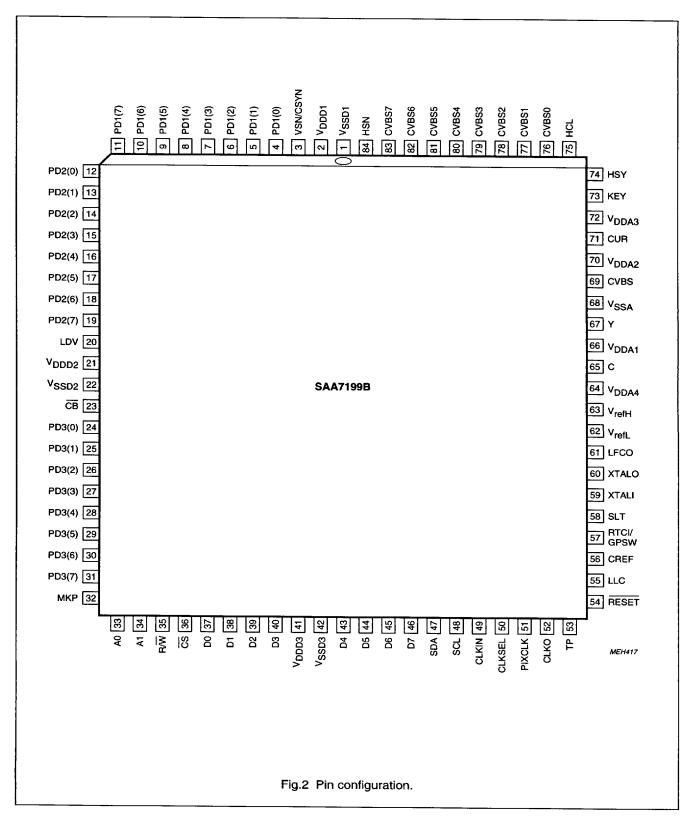

#### **PINNING**

| SYMBOL            | PIN | DESCRIPTION                                                                                                             |

|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------|

| V <sub>SSD1</sub> | 1   | digital ground 1 (0 V)                                                                                                  |

| V <sub>DDD1</sub> | 2   | digital supply 1 (5 V)                                                                                                  |

| VSN/CSYN          | 3   | vertical sync output (3-state), conditionally composite sync output; active LOW or active HIGH                          |

| PD1(0)            | 4   | data 1 input: digital signal R (red) respectively V signal; bit 0 (formats in Tables 19 to 25)                          |

| PD1(1)            | 5   | data 1 input: digital signal R (red) respectively V signal; bit 1 (formats in Tables 19 to 25)                          |

| PD1(2)            | 6   | data 1 input: digital signal R (red) respectively V signal; bit 2 (formats in Tables 19 to 25)                          |

| PD1(3)            | 7   | data 1 input: digital signal R (red) respectively V signal; bit 3 (formats in Tables 19 to 25)                          |

| PD1(4)            | 8   | data 1 input: digital signal R (red) respectively V signal; bit 4 (formats in Tables 19 to 25)                          |

| PD1(5)            | 9   | data 1 input: digital signal R (red) respectively V signal; bit 5 (formats in Tables 19 to 25)                          |

| PD1(6)            | 10  | data 1 input: digital signal R (red) respectively V signal; bit 6 (formats in Tables 19 to 25)                          |

| PD1(7)            | 11  | data 1 input: digital signal R (red) respectively V signal; bit 7 (formats in Tables 19 to 25)                          |

| PD2(0)            | 12  | data 2 input: digital signal G (green) respectively Y signal or indexed colour data; bit 0 (formats in Tables 19 to 25) |

| PD2(1)            | 13  | data 2 input: digital signal G (green) respectively Y signal or indexed colour data; bit 1 (formats in Tables 19 to 25) |

| PD2(2)            | 14  | data 2 input: digital signal G (green) respectively Y signal or indexed colour data; bit 2 (formats in Tables 19 to 25) |

| PD2(3)            | 15  | data 2 input: digital signal G (green) respectively Y signal or indexed colour data; bit 3 (formats in Tables 19 to 25) |

| PD2(4)            | 16  | data 2 input: digital signal G (green) respectively Y signal or indexed colour data; bit 4 (formats in Tables 19 to 25) |

| PD2(5)            | 17  | data 2 input: digital signal G (green) respectively Y signal or indexed colour data; bit 5 (formats in Tables 19 to 25) |

| PD2(6)            | 18  | data 2 input: digital signal G (green) respectively Y signal or indexed colour data; bit 6 (formats in Tables 19 to 25) |

| PD2(7)            | 19  | data 2 input: digital signal G (green) respectively Y signal or indexed colour data; bit 7 (formats in Tables 19 to 25) |

| LDV               | 20  | load data clock input signal to input interface (samples PDn(7 to 0), CB, MPK, KEY and RTCI)                            |

| $V_{DDD2}$        | 21  | digital supply 2 (5 V)                                                                                                  |

| V <sub>SSD2</sub> | 22  | digital ground 2 (0 V)                                                                                                  |

| СВ                | 23  | composite blanking input; active LOW                                                                                    |

| PD3(0)            | 24  | data 3 input: digital signal B (blue) respectively U signal; bit 0 (formats in Tables 19 to 25)                         |

| PD3(1)            | 25  | data 3 input: digital signal B (blue) respectively U signal; bit 1 (formats in Tables 19 to 25)                         |

| PD3(2)            | 26  | data 3 input: digital signal B (blue) respectively U signal; bit 2 (formats in Tables 19 to 25)                         |

| PD3(3)            | 27  | data 3 input: digital signal B (blue) respectively U signal; bit 3 (formats in Tables 19 to 25)                         |

| PD3(4)            | 28  | data 3 input: digital signal B (blue) respectively U signal; bit 4 (formats in Tables 19 to 25)                         |

| PD3(5)            | 29  | data 3 input: digital signal B (blue) respectively U signal; bit 5 (formats in Tables 19 to 25)                         |

| PD3(6)            | 30  | data 3 input: digital signal B (blue) respectively U signal; bit 6 (formats in Tables 19 to 25)                         |

| PD3(7)            | 31  | data 3 input: digital signal B (blue) respectively U signal; bit 7 (formats in Tables 19 to 25)                         |

| MPK               | 32  | multi-purpose key input; active HIGH                                                                                    |

| A0                | 33  | subaddress bit A0 input for microcontroller access (Table 3)                                                            |

1996 Sep 27

4

**= 7110826 0109320 425 ==**

**SAA7199B**

| SYMBOL            | PIN | DESCRIPTION                                                                                                                                      |  |  |  |  |  |

|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| A1                | 34  | subaddress bit A1 input for microcontroller access (Table 3)                                                                                     |  |  |  |  |  |

| R/W               | 35  | read/write not input signal from microcontroller                                                                                                 |  |  |  |  |  |

| <del>CS</del>     | 36  | chip select input for parallel interface; active LOW                                                                                             |  |  |  |  |  |

| D0                | 37  | bidirectional port from/to microcontroller; bit D0                                                                                               |  |  |  |  |  |

| D1                | 38  | bidirectional port from/to microcontroller; bit D1                                                                                               |  |  |  |  |  |

| D2                | 39  | bidirectional port from/to microcontroller; bit D2                                                                                               |  |  |  |  |  |

| D3                | 40  | bidirectional port from/to microcontroller; bit D3                                                                                               |  |  |  |  |  |

| V <sub>DDD3</sub> | 41  | digital supply 3 (5 V)                                                                                                                           |  |  |  |  |  |

| V <sub>SSD3</sub> | 42  | digital ground 3                                                                                                                                 |  |  |  |  |  |

| D4                | 43  | bidirectional port from/to microcontroller; bit D4                                                                                               |  |  |  |  |  |

| D5                | 44  | bidirectional port from/to microcontroller; bit D5                                                                                               |  |  |  |  |  |

| D6                | 45  | bidirectional port from/to microcontroller; bit D6                                                                                               |  |  |  |  |  |

| D7                | 46  | bidirectional port from/to microcontroller; bit D7                                                                                               |  |  |  |  |  |

| SDA               | 47  | I <sup>2</sup> C-bus data input/output                                                                                                           |  |  |  |  |  |

| SCL               | 48  | I <sup>2</sup> C-bus clock input                                                                                                                 |  |  |  |  |  |

| CLKIN             | 49  | external clock signal input (maximum frequency 60 MHz)                                                                                           |  |  |  |  |  |

| CLKSEL            | 50  | clock source select input                                                                                                                        |  |  |  |  |  |

| PIXCLK            | 51  | CLKO/2 or conditionally CLKO output signal                                                                                                       |  |  |  |  |  |

| CLKO              | 52  | selected clock output signal (LLC or CLKIN)                                                                                                      |  |  |  |  |  |

| TP                | 53  | test pin; connected to ground                                                                                                                    |  |  |  |  |  |

| RESET             | 54  | reset input; active LOW                                                                                                                          |  |  |  |  |  |

| LLC               | 55  | line-locked clock input signal from external clock generation circuit (CGC)                                                                      |  |  |  |  |  |

| CREF              | 56  | clock qualifier input of external CGC                                                                                                            |  |  |  |  |  |

| GPSW/RTCI         | 57  | general purpose switch output (set via I <sup>2</sup> C-bus or MPU-bus); real time control input, defined by I <sup>2</sup> C or MPU programming |  |  |  |  |  |

| SLT               | 58  | GENLOCK output flag (3-state): HIGH = sync lost in GENLOCK mode; LOW = otherwise                                                                 |  |  |  |  |  |

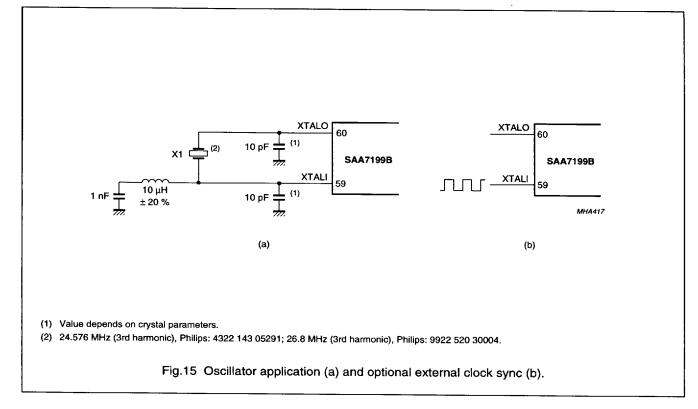

| XTALI             | 59  | crystal oscillator input (26.8 or 24.576 MHz)                                                                                                    |  |  |  |  |  |

| XTALO             | 60  | crystal oscillator output                                                                                                                        |  |  |  |  |  |

| LFCO              | 61  | line frequency control output signal for external CGC                                                                                            |  |  |  |  |  |

| V <sub>refL</sub> | 62  | reference voltage LOW of DACs (resistor chains)                                                                                                  |  |  |  |  |  |

| $V_{\text{refH}}$ | 63  | reference voltage HIGH of DACs (resistor chains)                                                                                                 |  |  |  |  |  |

| V <sub>DDA4</sub> | 64  | analog supply 4 for resistor chains of the DACs (5 V)                                                                                            |  |  |  |  |  |

| С                 | 65  | chrominance analog output signal                                                                                                                 |  |  |  |  |  |

| $V_{DDA1}$        | 66  | analog supply 1 for output buffer amplifier of DAC1 (5 V)                                                                                        |  |  |  |  |  |

| Υ                 | 67  | luminance analog output signal                                                                                                                   |  |  |  |  |  |

| V <sub>SSA</sub>  | 68  | analog ground (0 V)                                                                                                                              |  |  |  |  |  |

| CVBS              | 69  | CVBS analog output signal                                                                                                                        |  |  |  |  |  |

| V <sub>DDA2</sub> | 70  | analog supply 2 for output buffer amplifier of DAC2 (5 V)                                                                                        |  |  |  |  |  |

| CUR               | 71  | current input for analog output buffers                                                                                                          |  |  |  |  |  |

| V <sub>DDA3</sub> | 72  | analog supply 3 for output buffer amplifier of DAC3 (5 V)                                                                                        |  |  |  |  |  |

| KEY               | 73  | key input signal to insert CVBS input signal into encoded CVBS output signal; active HIGH                                                        |  |  |  |  |  |

1996 Sep 27

5

**. 7110826 0109321 361**

**SAA7199B**

| SYMBOL | PIN | DESCRIPTION                                                                                                      |  |

|--------|-----|------------------------------------------------------------------------------------------------------------------|--|

| HSY    | 74  | horizontal sync indicator output signal; active HIGH (3-state output to ADC)                                     |  |

| HCL    | 75  | horizontal clamping output; active HIGH (3-state output)                                                         |  |

| CVBS0  | 76  | digital CVBS input signal; bit 0                                                                                 |  |

| CVBS1  | 77  | digital CVBS input signal; bit 1                                                                                 |  |

| CVBS2  | 78  | digital CVBS input signal; bit 2                                                                                 |  |

| CVBS3  | 79  | digital CVBS input signal; bit 3                                                                                 |  |

| CVBS4  | 80  | digital CVBS input signal; bit 4                                                                                 |  |

| CVBS5  | 81  | digital CVBS input signal; bit 5                                                                                 |  |

| CVBS6  | 82  | digital CVBS input signal; bit 6                                                                                 |  |

| CVBS7  | 83  | digital CVBS input signal; bit 7                                                                                 |  |

| HSN    | 84  | horizontal sync output; active LOW or active HIGH for 60/66/72 × PIXCLK at 12.27/13.5/14.75 MHz (3-state output) |  |

**SAA7199B**

1996 Sep 27

7

**■ 7110826 0109323 134 ■**

**SAA7199B**

#### **FUNCTIONAL DESCRIPTION**

The SAA7199B is a digital video encoder that translates digital RGB, YUV or 8-bit indexed colour signals into the analog PAL/NTSC output signals Y (luminance), C (4.43/3.58 MHz chrominance) and CVBS (composite signal including sync).

Four different modes are selectable (Table 18):

Stand-alone mode (horizontal and vertical timings are generated)

Slave mode (stand-alone unit that accepts external horizontal and vertical timing), and optional real time information for subcarrier/clock from a digital colour decoder

GENLOCK mode (GENLOCK capabilities are achieved in conjunction with determined ICs)

Test mode (only clock signal is required).

The input data rate (pixel sequence) has an integer relationship to the number of horizontal clock cycles (Table 1). A sufficient stable external clock signal ensures correct encoding. The generated clock frequency in the GENLOCK mode may deviate by  $\pm 7\%$  depending on the reference signal which is corresponding to its input sync signal. The clock will be nominal in the GENLOCK mode when the reference signal is absent (nominal with crystal oscillator accuracy for TV time constants, and nominal  $\pm 1.4\%$  for VCR time constants).

The on-chip colour conversion matrix provides "CCIR 601" code-compatible transcoding of RGB to YUV data.

RGB data out of bounds, with respect to "CCIR 601" specification, can be clipped to prevent over-loading of the colour modulator. RGB data input can be either in linear colour space or in gamma-corrected colour space.

YUV data must be gamma-corrected in accordance with "CCIR 601". This circuit operates primarily in a 24-bit colour space  $(3 \times 8$ -bit) but can also accommodate different data formats (4:1:1,4:2:2 and 4:4:4) plus 8-bit indexed pseudo-colour space operations (FMT-bits in Table 8).

RGB CLUTs on-chip provide gamma-correction and/or other CLUT functions. They consist of programmable tables to be loaded independently, and they generate 24-bit gamma-corrected output signals from 24-bit data of one of the input formats or from 8-bit indexed pseudo-colour data.

Required modulation is performed. The digital YUV data is encoded in accordance with standards "RS-170A" (composite NTSC) and "CCIR 624-4" (composite PAL-B/G). S-video output signal is available (Y/C) also some sub-standard output signals (STD-bits in Table 12).

A 7.5 IRE set-up level is automatically selected in the 60 Hz mode, but not selected in the 50 Hz mode.

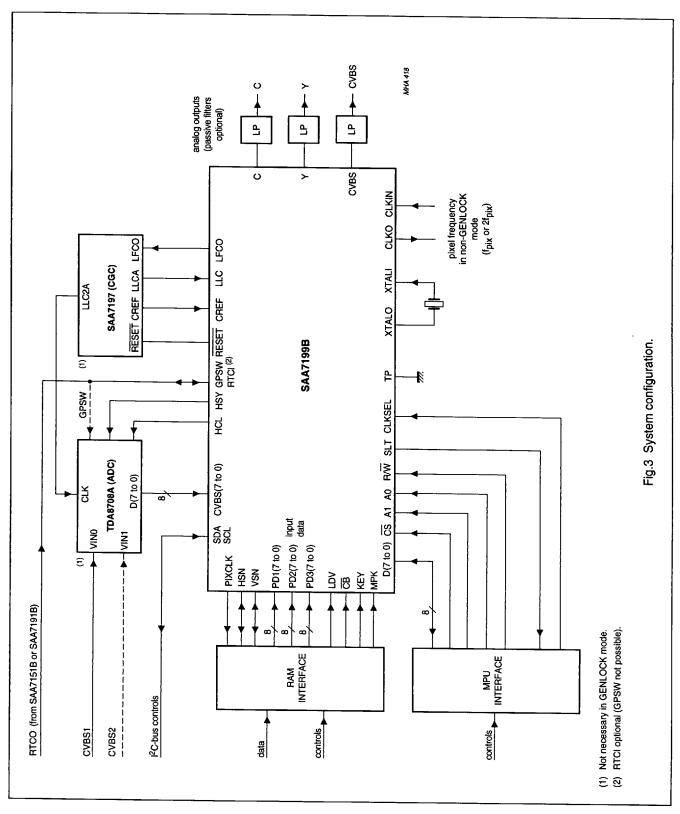

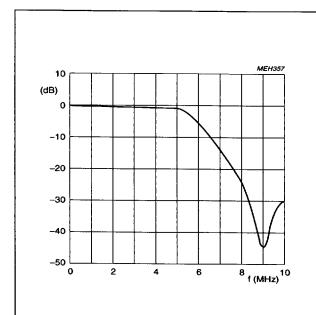

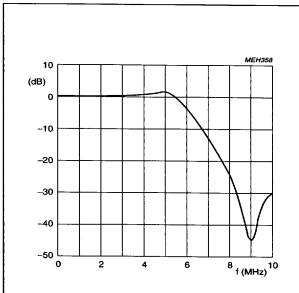

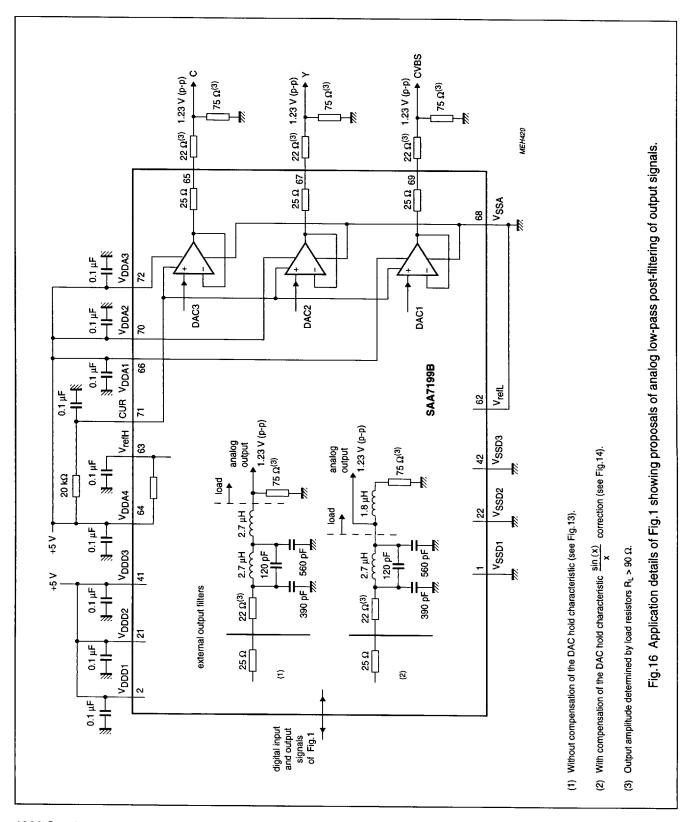

The analog signal outputs can drive directly into terminated 75  $\Omega$  coaxial lines, a passive external filter is recommended (Figs 3, 13 and 14). Analog post-filtering is required (LP in Fig.3).

GENLOCK to an external reference signal is achieved by addition of a video ADC and a clock generator combination. Thus, the system is enabled to lock on a stable video source or to a stable VCR source (normal playback). The SAA7199B, the ADC and the clock generator combination (Fig.3) form a control loop achieving a highly stable line-locked clock. The clock has to be generated by a crystal oscillator without this availability. The GENLOCK mode is not available in a single device set-up.

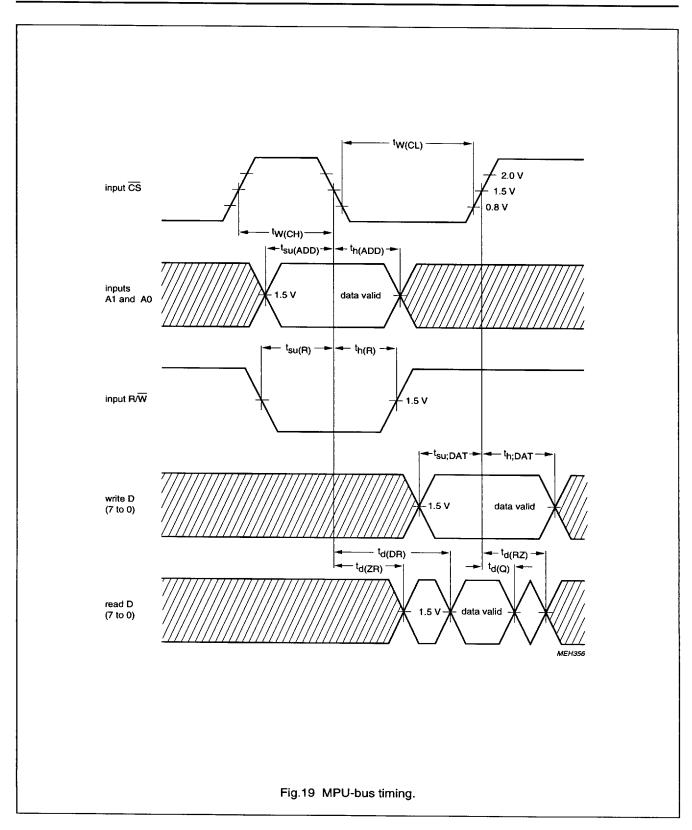

#### Control interface

The SAA7199B supports a standard parallel MPU interface and the serial I<sup>2</sup>C-bus interface. The MPU has direct access to internal control registers and colour tables. Update is possible at any time, excluding coincident internal reading and external writing of the same cell (the current pixel value could be destroyed).

The two interfaces of Table 2 are selected automatically. However, the  $I^2C$ -bus control is inactive when the MPU interface is selected by  $\overline{CS}$  = LOW. No simultaneous access may occur.  $I^2C$ -bus and MPU control complement each other and have access to common registers controlled via a common internal bus. The programmer can use virtually identical programs.

The internal memory space is devided into the look-up table and the control table, each with its own 8-bit address register used as a pointer for specific location. This address register is provided with auto-incrementation and can be written by only one addressing.

The look-up table contains three banks of 256 bytes. Therefore, each read or write cycle must access all three banks in a pre-determined order. The support logic is part of the control interface.

1996 Sep 27

8

7110826 0109324 070 🚥

**SAA7199B**

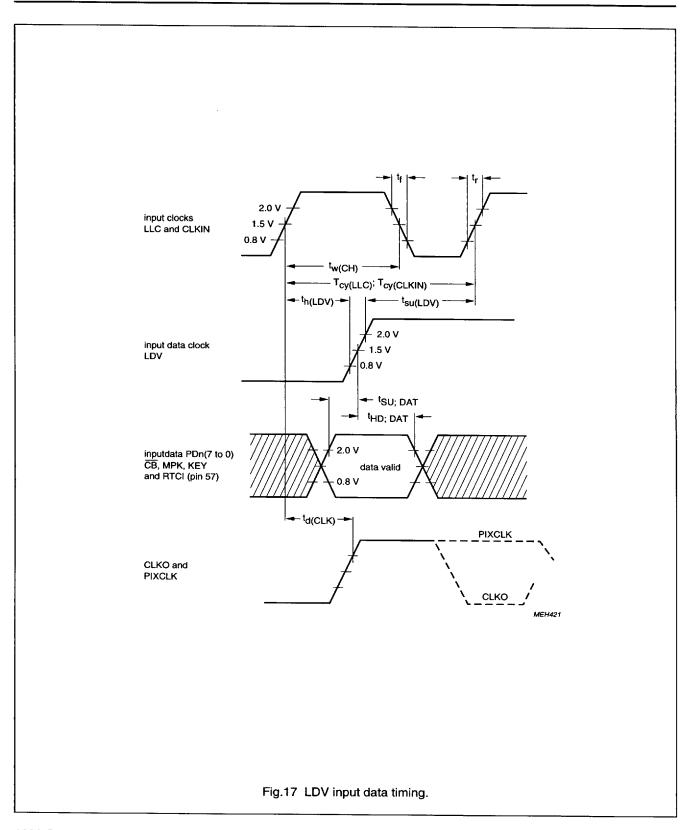

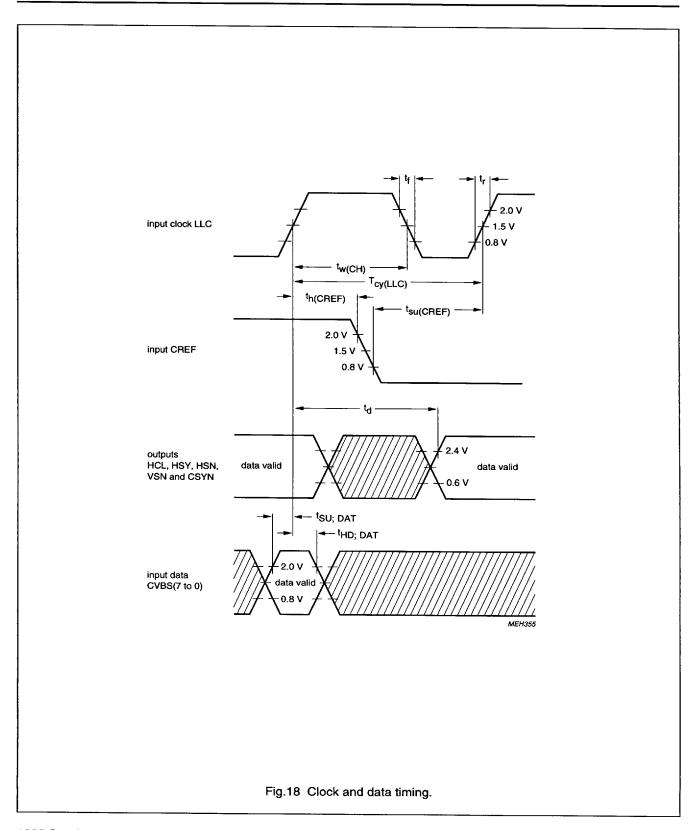

#### Timing (see Fig.3)

The reference to generate internal clocks from LLC in GENLOCK operation with SAA7197 is CREF

$$CREF = \frac{LLC}{2}$$

.

In this event input CLKSEL is HIGH and the SRC-bit = 1.

In non-GENLOCK operation the signal from CLKIN is used and LDV is clock reference (input CLKSEL = 0; SCR-bit = CPR-bit = 0).

Pins LLC and CLKIN are tied together when no switching between LLC and CLKIN is applied. In Fig.3 it is assumed that LLC and CLKIN are double the pixel clock frequency of CREF and LDV respectively.

CREF must be at the same frequency (or constant HIGH or LOW) when LLC is at pixel clock frequency. CPR-bit = 1 if CLKIN is at pixel clock frequency.

The buffered CLKO signal is always delayed. LLC or CLKIN signals are in accordance with CLKSEL.

#### Mapping

The method of mapping external control signals on to the internal bus is simple. The MPU-bus contains the signals as shown in Table 4 (names in chip-internal nomenclature).

#### Bit allocation

The Bit Allocation Map (BAM) shows the individual control signals, used to control the different operational modes of the circuit. The I<sup>2</sup>C-bus is normally used for control. The SAA7199B also has an MPU-bus interface for direct microcontroller connection. The BAM shown in Table 6 resembles the I<sup>2</sup>C-bus type but can be also used for the parallel bus; the control registers are indexed from 00H to 0FH. Auto-incrementation is applied.

#### Digital-to-analog converters

The converters use a combination of resistor chains with low-impedance output buffers. The bottom output voltage is 200 mV to reduce integral non-linearity errors. The analog signal, without load on output pin, is between 0.2 and 2.2 V. Figure 16 shows the application for 1.23 V/75  $\Omega$  outputs, using the serial 25 + 22  $\Omega$  resistors.

Each digital-to-analog converter has its own supply pin for the purpose of decoupling.  $V_{DDA4}$  is the supply voltage for the resistor chains of the three DACs. The accuracy of this supply voltage directly influences the output amplitudes. The current CUR into pin 71 is 0.3 mA ( $V_{DDA4}=5\ V;$   $R_{64-71}=20\ k\Omega);$  a larger current improves the bandwidth but increases the integral non-linearity.

Table 1 Pixel relationships

| ACTIVE PIXELS PER LINE | FIELD RATE<br>(Hz) | MULTIPLES OF LINE FREQUENCY | PIXCLK OUTPUT SIGNAL (MHz) | CRYSTAL (MHz) |

|------------------------|--------------------|-----------------------------|----------------------------|---------------|

| 640 (square)           | 60                 | 780                         | 12.27                      | 26.8          |

| 720                    | 60                 | 858                         | 13.5                       | 24.576        |

| 768                    | 50                 | 944                         | 14.75                      | 26.8          |

| 720                    | 50                 | 864                         | 13.5                       | 24.576        |

Table 2 Access to the control interface

| SYMBOL | DESCRIPTION                                               |  |  |  |  |  |

|--------|-----------------------------------------------------------|--|--|--|--|--|

| SDA    | l <sup>2</sup> C-bus serial data line (bidirectional)     |  |  |  |  |  |

| SCL    | I <sup>2</sup> C-bus clock line                           |  |  |  |  |  |

| A1, A0 | MPU-bus address inputs                                    |  |  |  |  |  |

| R/W    | read/write control input                                  |  |  |  |  |  |

| CS     | chip select input; I <sup>2</sup> C-bus disabled when LOW |  |  |  |  |  |

| GPSW   | general purpose switch output (bit of control register)   |  |  |  |  |  |

| RESET  | reset input signal; active-LOW                            |  |  |  |  |  |

1996 Sep 27

9

7110826 0109325 TO? 🖿

**SAA7199B**

Table 3 Address assignment

| ADDRES | SS INPUTS | 120 DUG GUDADDDEGG              |                                               |  |  |  |

|--------|-----------|---------------------------------|-----------------------------------------------|--|--|--|

| A1     | A0        | I <sup>2</sup> C-BUS SUBADDRESS | SELECTION                                     |  |  |  |

| 0      | 0         | 00                              | ADR-CLUT (address register of look-up tables) |  |  |  |

| 0      | 1         | 01                              | DATA-CLUT                                     |  |  |  |

| 1      | 0         | 02                              | ADR-CTRL (index register of control table)    |  |  |  |

| 1      | 1         | 03                              | DATA-CTRL                                     |  |  |  |

Table 4 Signals on the internal bus

| SYMBOL         | DESCRIPTION                                                        |  |  |  |

|----------------|--------------------------------------------------------------------|--|--|--|

| R/W            | select read/write (read = 1; write = 0)                            |  |  |  |

| C/T            | control table/look-up table (control table = 1; look-up table = 0) |  |  |  |

| D/Ā            | select data/address (data = 1; address = 0)                        |  |  |  |

| DI/DO (0 to 7) | data bus on port inputs/outputs D7 to D0                           |  |  |  |

| EN             | enable from control interface to synchronize data transfer         |  |  |  |

Table 5 Signals on the internal bus

| INTERNAL PARALLEL BUS | PARALLEL INTERFACE | I <sup>2</sup> C-BUS INTERFACE                                                        |  |  |  |

|-----------------------|--------------------|---------------------------------------------------------------------------------------|--|--|--|

| R/W                   | R/W (pin 35)       | LSB of slave address byte (read = HIGH; write = LOW)                                  |  |  |  |

| C/T                   | A1 (pin 34)        | X 4 subaddresses after decoding                                                       |  |  |  |

| A∕T                   | A0 (pin 33)        | X 4 subaddresses after decoding                                                       |  |  |  |

| DI/DO (0 to 7)        | D7 to D0           | data bits D7 to D0 for each subaddress                                                |  |  |  |

| EN                    | CS and R/W         | enable by every 9th clock of sample of SCL (control of serial-to-parallel conversion) |  |  |  |

**SAA7199B**

1996 Sep 27

11 7110826 0109327 88T **=**

**SAA7199B**

Table 6 Bit allocation map (I<sup>2</sup>C-bus access in Table 17)

| INDEX         |                   | DATA BYTE |        |       |         |       |       |                     |              |                                              |  |

|---------------|-------------------|-----------|--------|-------|---------|-------|-------|---------------------|--------------|----------------------------------------------|--|

| BINARY        | HEX               | D7        | D6     | D5    | D4      | D3    | D2    | D1                  | D0           | DF <sup>(1)</sup>                            |  |

| Input process | sing              |           |        |       |         |       | ·     |                     | <u> </u>     | <u> </u>                                     |  |

| 0000 0000     | 00                | VTBY      | FMT2   | FMT1  | FMT0    | SCBW  | CCIR  | MOD1                | MOD0         | 5C                                           |  |

| 0000 0001     | 01                | TRER7     | TRER6  | TRER5 | TRER4   | TRER3 | TRER2 | TRER1               | TRER0        | XX                                           |  |

| 0000 0010     | 02                | TREG7     | TREG6  | TREG5 | TREG4   | TREG3 | TREG2 | TREG1               | TREG0        | XX                                           |  |

| 0000 0011     | 03                | TREB7     | TREB6  | TREB5 | TREB4   | TREB3 | TREB2 | TREB1               | TREB0        | XX                                           |  |

| Sync process  | sing              |           |        |       | •       |       |       | ·                   | <u></u> .    | <u> </u>                                     |  |

| 0000 0100     | 04                | SYSEL1    | SYSEL0 | SCEN  | VTRC    | NINT  | HPLL  | HLCK <sup>(2)</sup> | OEF(2)       | 10                                           |  |

| 0000 0101     | 05                | 0         | 0      | GDC5  | GDC4    | GDC3  | GDC2  | GDC1                | GDC0         | 21                                           |  |

| 0000 0110     | 06                | IDEL7     | IDEL6  | IDEL5 | IDEL4   | IDEL3 | IDEL2 | IDEL1               | IDELO        | 52                                           |  |

| 0000 0111     | 07                | 0         | 0      | PSO5  | PSO4    | PSO3  | PSO2  | PSO1                | PSO0         | 32                                           |  |

| Control, cloc | k and out         | put forma | tter   |       |         |       | •     |                     | <del> </del> | <u>.                                    </u> |  |

| 0000 1000     | 08                | DD        | KEYE   | SRC   | CPR     | сокі  | IM    | GPSW                | SRSN         | 64                                           |  |

| 0000 1001     | 09                | 0         | BAME   | MPKC1 | MPKC0   | IEPI  | RTSC  | RTIN                | RTCE         | 02                                           |  |

| 0000 1010(3)  | 0A <sup>(3)</sup> | 0         | 0      | 0     | 0       | 0     | 0     | 0                   | 0            | 00                                           |  |

| 0000 1011(3)  | 0B <sup>(3)</sup> | 0         | 0      | 0     | 0       | 0     | 0     | 0                   | 0            | 00                                           |  |

| Encoder con   | trol              |           |        |       | •       |       |       |                     | <u> </u>     |                                              |  |

| 0000 1100     | 0C                | CHPS7     | CHPS6  | CHPS5 | CHPS4   | CHPS3 | CHPS2 | CHPS1               | CHPS0        | XX <sup>(4)</sup>                            |  |

| 0000 1101     | 0D                | FSC07     | FSCO6  | FSCO5 | FSCO4   | FSCO3 | FSCO2 | FSCO1               | FSCO0        | 00                                           |  |

| 0000 1110     | 0E                | 0         | 0      | 0     | CLCK(2) | STD3  | STD2  | STD1                | STD0         | 0C                                           |  |

| 0000 1111(3)  | 0F <sup>(3)</sup> | 0         | 0      | 0     | 0       | 0     | 0     | 0                   | 0            |                                              |  |

#### **Notes**

- 1. DF is the default value for a typical programming example: GENLOCK mode for a VCR; non-gamma-corrected RGB data (real time keying is possible). SLT will be set if there is no horizontal lock.NTSC-M standard with normal colour bandwidth and 12.2727 MHz pixel rate. CSYN signal will be provided, arriving 8 pixel clocks earlier, to compensate pipeline delay in the previous RAM interface. The encoded CVBS is 12 clocks earlier than the CVBS reference on the input of the previous ADC. The CLUTs are bypassed at MPK = HIGH in real time.

- 2. Read only bits.

- 3. Reserved.

- 4. Adjust as required.

**SAA7199B**

Table 7 Function of registers bits of Table 6

| BIT                          | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Index 00 VTBY                | video look-up table by-pass: 0 = not bypassed; 1 = bypassed (logically OR-ed with MPK)                                                                                                                                                                                                                                                                                                                         |

| FMT2 to FMT0                 | input formats see Table 8                                                                                                                                                                                                                                                                                                                                                                                      |

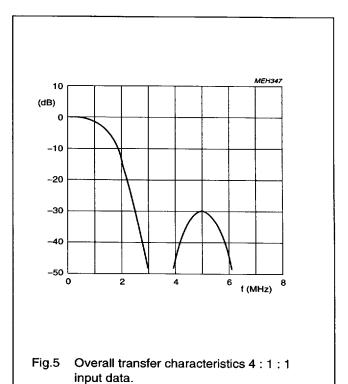

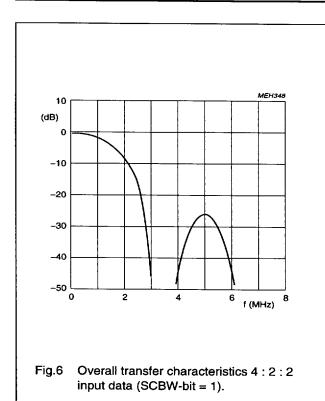

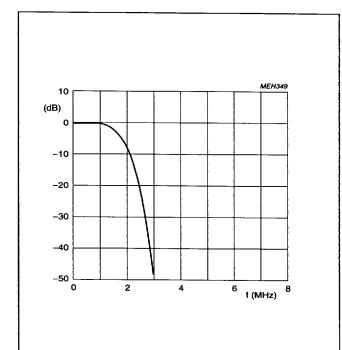

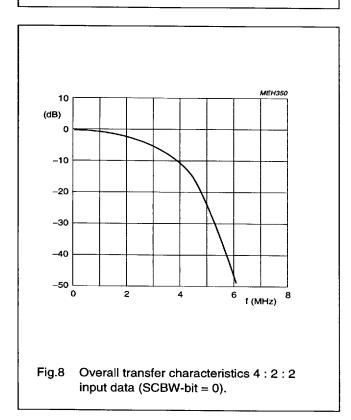

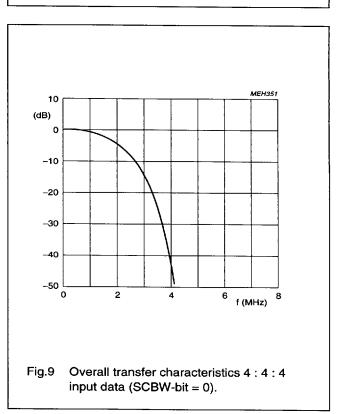

| SCBW                         | chrominance bandwidth: 0 = enhanced; 1 = standard                                                                                                                                                                                                                                                                                                                                                              |

| CCIR                         | select level: 0 = DMSD2 levels; 1 = CCIR levels                                                                                                                                                                                                                                                                                                                                                                |

| MOD1 to MOD0                 | select mode see Table 9                                                                                                                                                                                                                                                                                                                                                                                        |

| Index 01<br>TRER7 to TRER0   | test register red (read/write via MPU-bus; write only via I <sup>2</sup> C-bus)                                                                                                                                                                                                                                                                                                                                |

| Index 02<br>TREG7 to TREG0   | test register green (read/write via MPU-bus; write only via I <sup>2</sup> C-bus)                                                                                                                                                                                                                                                                                                                              |

| Index 03<br>TREB7 to TREB0   | test register blue (read/write via MPU-bus; write only via I <sup>2</sup> C-bus)                                                                                                                                                                                                                                                                                                                               |

| Index 04<br>SYSEL1 to SYSEL0 | sync select see Table 10                                                                                                                                                                                                                                                                                                                                                                                       |

| SCEN                         | sync/clamping (HSY/HCL) enable: 0 = disabled (set to HIGH); 1 = enabled                                                                                                                                                                                                                                                                                                                                        |

| VTRC                         | select TV/VTR mode: 0 = TV mode (slow); 1 = VTR mode (fast)                                                                                                                                                                                                                                                                                                                                                    |

| NINT                         | select interlace of encoded signal: 0 = interlaced (262.5/262.5 or 312.5/312.5);<br>1 = non-interlaced (262/262 or 312/312 in modes 1 and 3 only)                                                                                                                                                                                                                                                              |

| HPLL                         | select horizontal lock: 0 = lock enabled; 1 = lock disabled (crystal reference)                                                                                                                                                                                                                                                                                                                                |

| OEF                          | status bit field organization (to be read): 0 = even field; 1 = odd field                                                                                                                                                                                                                                                                                                                                      |

| HLCK                         | status bit sync indication (to be read): 0 = locked to external sync; 1 = external sync lost                                                                                                                                                                                                                                                                                                                   |

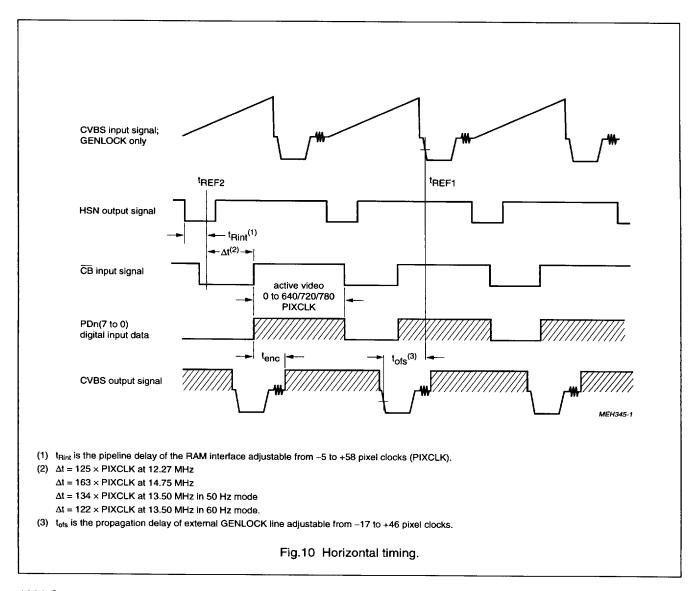

| Index 05<br>GDC5 to GDC0     | GENLOCK delay compensation; note 1: data 00 to 3F equals timing of CVBS output signal which is $(46 - \text{GDC})$ pixel clocks = $t_{\text{ofs}}$ earlier with respect to reference point $t_{\text{REF1}}$ . $(t_{\text{REF1}}$ corresponds to the falling edge of the horizontal sync pulse of CVBS input signal; $t_{\text{ofs}}$ is designated for propagation delay of external GENLOCK source, Fig.10). |

| Index 06<br>IDEL7 to IDEL0   | increment delay: update of line-locked clock frequency (Table 6, data '43' hex recommended)                                                                                                                                                                                                                                                                                                                    |

| Index 07<br>PSO7 to PSO0     | Phase sync in output signal, note 1: data 00 to 3F equals to active slope of HSN, VSN/CSYN is $(58 - PSO)$ pixel clocks = $t_{Rint}$ earlier with respect to reference point $t_{REF2}$ ( $t_{REF2}$ corresponds to $PSO = 58$ ; $t_{Rint}$ is designated for pipeline delay of the feeding RAM interface, Fig.10).                                                                                            |

| Index 08 DD                  | digital video encoder disable: 0 = enabled; 1 = disabled                                                                                                                                                                                                                                                                                                                                                       |

| KEYE                         | keying enable: 0 = disabled; 1 = enabled (logically AND-connected with KEY)                                                                                                                                                                                                                                                                                                                                    |

| SRCC                         | clock source: 0 = external system clock; 1 = DTV2 system clock                                                                                                                                                                                                                                                                                                                                                 |

| CPR                          | clock phase reference: 0 = LDV is input (pin 20); 1 = LDV is not                                                                                                                                                                                                                                                                                                                                               |

| СОКІ                         | colour-killer: 0 = colour on; 1 = colour off (subcarrier is switched off)                                                                                                                                                                                                                                                                                                                                      |

| IM                           | interrupt mask: 1 = interrupt not masked at sync lost (pin 58) 0 = interrupt masked at sync lost (pin 58)                                                                                                                                                                                                                                                                                                      |

| GPSW                         | general purpose switch at bit RTIN = 1: 0 = pin 57 LOW; 1 = pin 57 HIGH                                                                                                                                                                                                                                                                                                                                        |

| SRSN                         | software reset: 0 = no reset; 1 = reset (see "Reset" procedure)                                                                                                                                                                                                                                                                                                                                                |

| Index 09 BAME                | Burst amplitude indication: 0 = burst amplitude measurement is overridden; colour lock always assumed; 1 = burst amplitude is used to control the CLCK status bit, recommended for reference signal without subcarrier burst (pure black and white) in order to avoid PLL hunting.                                                                                                                             |

| MPKC1 to MPKC0               | multipurpose key control: with MKP = LOW (pin 32) all functions are as given by software programming; MKP = HIGH sets in real time with respect to PDn (7 to 0); functions see Table 11                                                                                                                                                                                                                        |

1996 Sep 27

13

**7110826 0109329** 652 **\*\*\***

**SAA7199B**

| BIT                        | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IEPI                       | polarity of external PAL-ID signal (H/2 signal) from RTCl input (pin 57): 0 = not inverted; 1 = inverted                                                                                                                                                                                                                                                                                                                                                                     |

| RTSC                       | Real time select control: 0 = real time control HPLL increment is selected, which means, information concerning actual clock frequency from the digital colour decoder is received (SAA7151B or SAA7191B); the corresponding subcarrier frequency is calculated; 1 = real time control FSC increment with PAL-ID is selected, which means, information concerning actual subcarrier frequency and PAL-ID from the digital colour decoder is received (SAA7151B or SAA7191B). |

| RTIN                       | select real time control input: 0 = pin 57 is input for RTCI signal; 1 = pin 57 is port output GPSW                                                                                                                                                                                                                                                                                                                                                                          |

| RTCE                       | real time control enabled: 0 = disabled; 1 = enabled (RTIN = 0)                                                                                                                                                                                                                                                                                                                                                                                                              |

| Index 0C<br>CHPS7 to CHPS0 | phase adjustment between chrominance output signal and reference: 00 to FF equals 0 to 358.59375 degrees in steps of 1.40625 degrees                                                                                                                                                                                                                                                                                                                                         |

| Index 0D<br>FSC7 to FSC0   | fine adjustment of subcarrier frequency in non-GENLOCK modes: 00 to 7F increasing and FF to 80 decreasing equal approximately to $450 \times 10^{-6}$ of the subcarrier frequency in 256 steps                                                                                                                                                                                                                                                                               |

| Index 0E CLCK              | lock to external chrominance (to be read): 0 = possible; 1 = not possible                                                                                                                                                                                                                                                                                                                                                                                                    |

| STD3 to STD0               | colour encoding standards; see Table 12                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| _                          | status bits to be read via I <sup>2</sup> C-bus: see Table 15                                                                                                                                                                                                                                                                                                                                                                                                                |

| _                          | status bits to be read by microcontroller: all registers from 00 up to 0F can be read via MPU-bus, read only bits are OEF, HCLK (index 04) and CLCK (index 0E)                                                                                                                                                                                                                                                                                                               |

#### Note

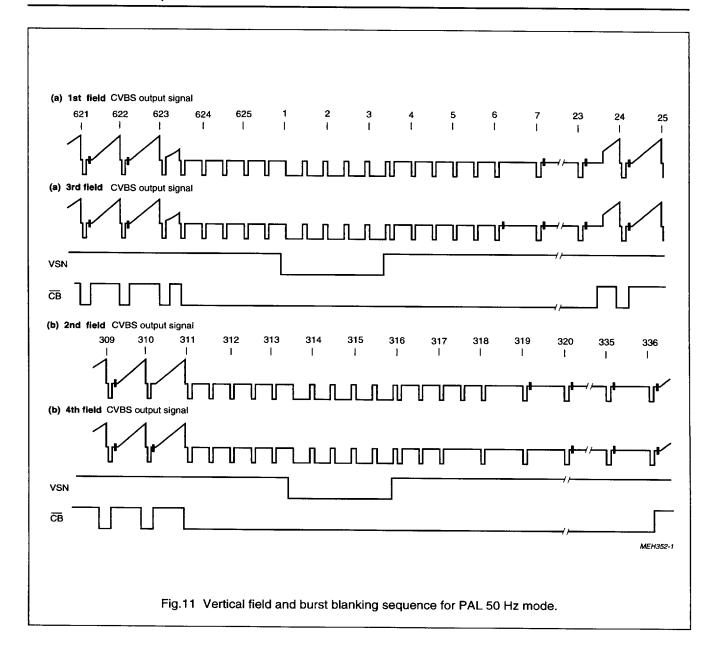

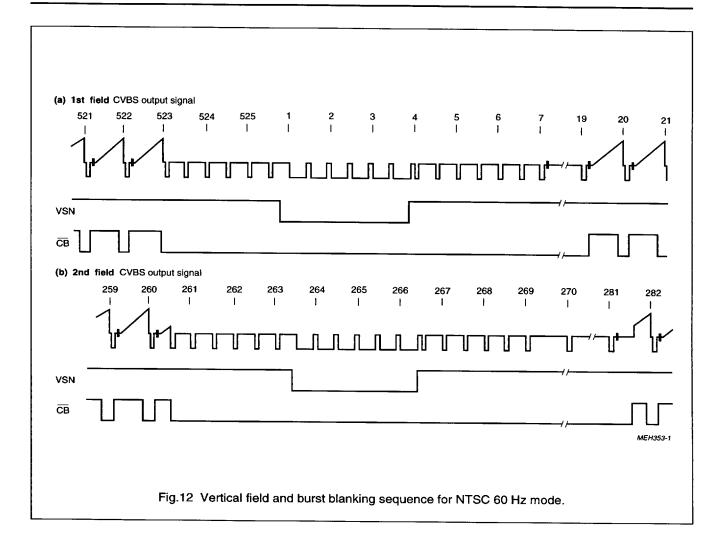

1. Field blanking (Figs 11 and 12): normally, video to be encoded should not become active after the active edge of VSN or CSYN before line 22.5 at 50 Hz (line 18 at 60 Hz). Total internal field blanking is 11 lines at 50 Hz (13 lines at 60 Hz).

Table 8 Input formats

| FMT2 | FMT1 | FMT0 | FORMAT                             |                     |  |  |

|------|------|------|------------------------------------|---------------------|--|--|

| 0    | 0    | 0    | YUV 4:1:1 format; DMSD2 compatible |                     |  |  |

| 0    | 0    | 1    | YUV 4:1:1 format; customized       |                     |  |  |

| 0    | 1    | 0    | YUV 4:2:2 format; DMSD2 compatible |                     |  |  |

| 0    | 1    | 1    | YUV 4:2:2 format; customized       |                     |  |  |

| 1    | 0    | 0    | YUV 4: 4: 4 format                 |                     |  |  |

| 1    | 0    | 1    | RGB 4 : 4 : 4 format               |                     |  |  |

| 1    | 1    | 0    | reserved                           |                     |  |  |

| 1    | 1    | 1    | 8-bit indexed colour               | -bit indexed colour |  |  |

Table 9 Select mode

| MOD1 | MOD0 |                  | MODE |  |

|------|------|------------------|------|--|

| 0    | 0    | GENLOCK mode     |      |  |

| 0    | 1    | stand alone mode |      |  |

| 1    | 0    | slave mode       |      |  |

| 1    | 1    | test mode        |      |  |

1996 Sep 27

14

**=** 7110826 0109330 374 **=**

**SAA7199B**

Table 10 Sync select

| SYSEL1 | SYSEL0 | SYNCHRONIZED FROM                        |

|--------|--------|------------------------------------------|

| 0      | 0      | CSYN (active LOW; pin 3)                 |

| 0      | 1      | HSN and VSN (active LOW; pins 84 and 3)  |

| 1      | 0      | CSYN (active HIGH; pin 3)                |

| 1      | 1      | HSN and VSN (active HIGH; pins 84 and 3) |

#### Table 11 Multi-purpose key control

| SET B | Y BITS | IN FUNCTION BLOCKS INPUT                |                              |                      | LEVEL<br>MATCHING    |  |

|-------|--------|-----------------------------------------|------------------------------|----------------------|----------------------|--|

| MPKC1 | MPKC0  | FORMATTER                               | CLUTs                        | MATRIX               |                      |  |

| 0     | 0      | control via CCIR bit and FMT bits       | bypass                       | control via FMT bits | control via CCIR bit |  |

| О     | 1      | format 5 (RGB) CCIR level               | active,<br>no indexed colour | active               | CCIR level           |  |

| 1     | х      | format 7 (indexed colour)<br>CCIR level | active,<br>no indexed colour | active               | CCIR level           |  |

Table 12 Colour encoding standards

| STD3 | STD2 | STD1 | STD0 | STANDARD                             |

|------|------|------|------|--------------------------------------|

| 0    | 0    | 0    | 0    | NTSC 4.43; 60 Hz; SQP (12.27 MHz)    |

| 0    | 0    | 0    | 1    | NTSC 4.43; 50 Hz; SQP (14.75 MHz)    |

| 0    | 0    | 1    | 0    | PAL-B/G 4.43; 50 Hz; SQP (14.75 MHz) |

| 0    | 0    | 1    | 1    | NTSC 4.43; 60 Hz; CCIR (13.5 MHz)    |

| 0    | 1    | 0    | 0    | NTSC 4.43; 50 Hz; CCIR (13.5 MHz)    |

| 0    | 1    | 0    | 1    | PAL-B/G 4.43; 50 Hz; CCIR (13.5 MHz) |

| 0    | 1    | 1    | 0    | reserved                             |

| 0    | 1    | 1    | 1    | reserved                             |

| 1    | 0    | 0    | 0    | PAL-M; 60 Hz; SQP (12.27 MHz)        |

| 1    | 0    | 0    | 1    | PAL-M; 60 Hz; CCIR (13.5 MHz)        |

| 1    | 0    | 1    | 0    | PAL-N; 50 Hz; CCIR (13.5 MHz)        |

| 1    | 0    | 1    | 1    | PAL-N; 50 Hz; SQP (14.75 MHz)        |

| 1    | 1    | 0    | 0    | NTSC-M; 60 Hz; SQP (12.27 MHz)       |

| 1    | 1    | 0    | 1    | NTSC-M; 60 Hz; CCIR (13.5 MHz)       |

| 1    | 1    | 1    | 0    | reserved                             |

| 1    | 1    | 1    | 1    | reserved                             |

#### Colour look-up tables (CLUTs)

The CLUTs consist of RAM tables. The RAM tables can be loaded with X = 0 to 255 in accordance with equation 1 for the signals R, G and B. Gamma-correction (pre-distortion) by the following equation:

Y = NINT (b + a × X1<sup>1/g</sup>); Y(X ≤ 16) = 16; Y(X ≥ 235) = 235 (equation 1) with g = 2.2: a =

$$\frac{219}{235^{-2.2} - 16^{-2.2}}$$

; b = 16 - a × 16<sup>-2.2</sup>

The RAM tables are loaded via MPU-bus or via I<sup>2</sup>C-bus (Table 17).

1996 Sep 27

15

. 177095P 0704337 500 🖿

**SAA7199B**

#### I<sup>2</sup>C-bus format

Table 13 I<sup>2</sup>C-bus address; see Table 14

| s | SLAVE ADDRESS | ACK | SUBADDRESS | ACK | DATA 0 | ACK |   | DATA n | ACK           | Р | 1  |

|---|---------------|-----|------------|-----|--------|-----|---|--------|---------------|---|----|

|   |               | L.  |            |     |        |     | ř |        | / . · · · · · |   | F. |

#### Table 14 Explanation of Table 13

| PART                | DESCRIPTION                         |                                       |  |  |  |

|---------------------|-------------------------------------|---------------------------------------|--|--|--|

| S                   | START condition                     |                                       |  |  |  |

| Slave address       | 1 0 1 1 0 0 0 X (note 1)            | · · · · · · · · · · · · · · · · · · · |  |  |  |

| ACK                 | acknowledge, generated by the slave | <del></del>                           |  |  |  |

| Subaddress (note 2) | subaddress byte (Table 17)          | <del></del>                           |  |  |  |

| DATA                | data byte (Table 6)                 |                                       |  |  |  |

|                     | continued data bytes and ACKs       |                                       |  |  |  |

| P                   | STOP condition                      |                                       |  |  |  |

#### **Notes**

- 1. X is the read/write control bit; X = 0 is order to write (the circuit is slave receiver); X = 1 is order to read (the circuit is slave transmitter).

- 2. If more than 1 byte DATA is transmitted, then auto-increment of the subaddress is performed.

#### **Table 15** I<sup>2</sup>C-bus status byte (address byte B1)

| FUNCTION    |    |    |    | STATU | JS BYTE |     |      |      |

|-------------|----|----|----|-------|---------|-----|------|------|

| - FONCTION  | D7 | D6 | D5 | D4    | D3      | D2  | D1   | D0   |

| Read status | 0  | 0  | 0  | 0     | FFOS    | OEF | CLCK | HLCK |

#### Table 16 Function of the bits in Table 15

| BIT  | FUNCTION                                                                                                                                      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| FFOS | first field of sequence: 0 = false; 1 = first of 4 fields for NTSC (first of 8 fields for PAL). FFOS is not valid for non-interlaced signals. |

| OEF  | field organization: 0 = even field; 1 = odd field                                                                                             |

| CLCK | lock to external chrominance: 0 = possible; 1 = not possible                                                                                  |

| HLCK | sync indication: 0 = locked to external sync; 1 = external sync lost                                                                          |

#### Table 17 I<sup>2</sup>C-bus write bytes (address byte B0)

| ACCESS            |                 | DESCRIPTION OF BYTE                                                                          |                                  |                                                    |  |  |  |

|-------------------|-----------------|----------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------|--|--|--|

| Control registers | address byte B0 | ddress byte B0 subaddress byte 02 index byte (00 to 0F); Table 6 data bytes (auto-increment) |                                  |                                                    |  |  |  |

| CLUTs registers   | address byte B0 | subaddress byte 00                                                                           | CLUT address bytes<br>(00 to FF) | 3 data bytes for one RGB sequence (auto-increment) |  |  |  |

1996 Sep 27

16

🖿 7110826 0109332 147 🖿

**SAA7199B**

#### Modes of the SAA7199B

Table 18 The four different modes of the SAA7199B

| MODE        | DESCRIPTION                                                                                                                                                                                                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stand alone | The SAA7199B receives a line-locked clock CLKIN and generates CSYN or HSN/VSN output signals, which trigger the RGB or the YUV source signal to provide data and composite blanking CB.                                                                                                                                               |

| Slave       | The SAA7199B receives the line-locked clock CLKIN, CSYN or HSN/VSN, CB and data from an RGB or YUV source. The sync inputs are edge-sensitive; their minimum active length is 1 PIXCLK. A real time control signal RTCI is received from a digital colour decoder as an option.                                                       |

| GENLOCK     | Horizontal and vertical sync plus colour are locked on a received CVBS reference signal. The CVBS reference signal also generates a line-locked clock by the SAA7197 clock generator. Auxiliary signals HCL and HSY plus CSYN or HSN/VSN are generated to trigger the RGB or the YUV source providing data and composite blanking CB. |

| Test        | Similar to stand alone mode, but the contents of the test registers TRER, TREG and TREB consists of data to be encoded. VSN/CSYN and HSN outputs are in 3-state condition.                                                                                                                                                            |

RELATIONSHIP BETWEEN HORIZONTAL FREQUENCY AND COLOUR SUBCARRIER FREQUENCY IN NON-GENLOCK MODE

1. Internal subcarrier frequency with n = integer

PAL:  $f_{SC} = f_H (n/4 + 1/625)$  respectively  $f_H (n/4 + 1/525)$

NTSC:  $f_{SC} = f_H (n/2)$

Necessary conditions: non-GENLOCK mode; RTCE = 0, FSCO = 00H; phase coupling of the two frequencies is given by a definite phase reset every 8th field at PAL (4th field at NTSC).

FSCO  $\neq$  00H adjusts the subcarrier frequency, phase reset is disabled and phase between  $f_{SC}$  and  $f_{H}$  is not constant.

2. External subcarrier frequency

f<sub>SC</sub> is given by RTCI real time input from a digital colour decoder

Necessary conditions: Slave mode; RTCE = 1, RTSC = 1. The 8th respectively 4th field reset is enabled at FSCO = 00H (disabled at FSCO  $\neq$  00H). The subcarrier frequency is not influenced by FSCO bits, but is given by real time increment.

3. External HPLL increment

$f_{SC}$  is calculated by RTCI real time input signal from a digital colour decoder. The frequency of  $f_{SC}$  depends on the absolute crystal frequency value used by the digital colour decoder.

Necessary conditions: Slave mode; RTCE = 1, RTSC = 0. The 8th respectively 4th field reset is enabled at FSCO = 00H (disabled at FSCO  $\neq$  00H). The subcarrier frequency is influenced by FSCO bits.

The absolute phase relationship between sync and subcarrier (colour burst output) can be influenced in all three events by CHPS7 to CHPS0 register byte (index 0C).

**SAA7199B**

#### **Data input formats**

One clock cycle equals 12.27 MHz, 13.5 MHz or 14.75 MHz; Cb = (B - Y) equals U; Cr = (R - Y) equals V; (n) = number of pixels.

Table 19 Format 0; DMSD2 compatible YUV 4:1:1 format (FMT-bits in index 00 = 000)

| INPUT       |          | CLOCK CYCLE (PIXEL SEQUENCE) |        |        |        |        |        |        |  |  |  |  |

|-------------|----------|------------------------------|--------|--------|--------|--------|--------|--------|--|--|--|--|

| SIGNAL      | 0        | 1                            | 2      | 3      | 4      | 5      | 6      | 7      |  |  |  |  |

| PD2(7 to 0) | Y(0)     | Y(1)                         | Y(2)   | Y(3)   | Y(4)   | Y(5)   | Y(6)   | Y(7)   |  |  |  |  |

| PD3(7)      | Cb7(0)   | Cb5(0)                       | Cb3(0) | Cb1(0) | Cb7(4) | Cb5(4) | Cb3(4) | Cb1(4) |  |  |  |  |

| PD3(6)      | Cb6(0)   | Cb4(0)                       | Cb2(0) | Cb0(0) | Cb6(4) | Cb4(4) | Cb2(4) | Cb0(4) |  |  |  |  |

| PD3(5)      | Cr7(0)   | Cr5(0)                       | Cr3(0) | Cr1(0) | Cr7(4) | Cr5(4) | Cr3(4) | Cr1(4) |  |  |  |  |

| PD3(4)      | Cr6(0)   | Cr4(0)                       | Cr2(0) | Cr0(0) | Cr6(4) | Cr4(4) | Cr2(4) | Cr0(4) |  |  |  |  |

| PD3(3 to 0) |          | not used                     |        |        |        |        |        |        |  |  |  |  |

| PD1(7 to 0) | not used |                              |        |        |        |        |        |        |  |  |  |  |

Table 20 Format 1; customized YUV 4:1:1 format (FMT-bits in index 00 = 001)

| INPUT       |        |      | CLO    | OCK CYCLE | (PIXEL SEQ | CLOCK CYCLE (PIXEL SEQUENCE) |        |      |  |  |  |  |  |  |  |  |

|-------------|--------|------|--------|-----------|------------|------------------------------|--------|------|--|--|--|--|--|--|--|--|

| SIGNAL      | 0      | 1    | 2      | 3         | 4          | 5                            | 6      | 7    |  |  |  |  |  |  |  |  |

| PD2(7 to 0) | Y(0)   | Y(1) | Y(2)   | Y(3)      | Y(4)       | Y(5)                         | Y(6)   | Y(7) |  |  |  |  |  |  |  |  |

| PD3(7)      | Cb7(0) | _    | Cr7(0) | _         | Cb7(4)     | _                            | Cr7(4) |      |  |  |  |  |  |  |  |  |

| PD3(6)      | Cb6(0) | _    | Cr6(0) |           | Cb6(4)     | _                            | Cr6(4) | _    |  |  |  |  |  |  |  |  |

| PD3(5)      | Cb5(0) | _    | Cr5(0) | _         | Cb5(4)     | _                            | Cr5(4) |      |  |  |  |  |  |  |  |  |

| PD3(4)      | Cb4(0) | -    | Cr4(0) |           | Cb4(4)     |                              | Cr4(4) | _    |  |  |  |  |  |  |  |  |

| PD3(3)      | Cb3(0) | _    | Cr3(0) | _         | Cb3(4)     | _                            | Cr3(4) | _    |  |  |  |  |  |  |  |  |

| PD3(2)      | Cb2(0) | _    | Cr2(0) | _         | Cb2(4)     |                              | Cr2(4) |      |  |  |  |  |  |  |  |  |

| PD3(1)      | Cb1(0) | _    | Cr1(0) | _         | Cb1(4)     | <b> </b> -                   | Cr1(4) |      |  |  |  |  |  |  |  |  |

| PD3(0)      | Cb0(0) | _    | Cr0(0) | _         | Cb0(4)     | _                            | Cr0(4) | _    |  |  |  |  |  |  |  |  |

| PD1(7 to 0) |        |      |        | n         | ot used    | <u> </u>                     | t      |      |  |  |  |  |  |  |  |  |

**SAA7199B**

Table 21 Format 2; DMSD2 compatible YUV 4:2:2 format (FMT-bits in index 00 = 010)

| INPUT       |        |          | CLO    | OCK CYCLE | (PIXEL SEQ | UENCE) |        | ·      |  |  |

|-------------|--------|----------|--------|-----------|------------|--------|--------|--------|--|--|

| SIGNAL      | 0      | 1        | 2      | 3         | 4          | 5      | 6      | 7      |  |  |

| PD2(7 to 0) | Y(0)   | Y(1)     | Y(2)   | Y(3)      | Y(4)       | Y(5)   | Y(6)   | Y(7)   |  |  |

| PD3(7)      | Cb7(0) | Cr7(0)   | Cb7(2) | Cr7(2)    | Cb7(4)     | Cr7(4) | Cb7(6) | Cr7(6) |  |  |

| PD3(6)      | Cb6(0) | Cr6(0)   | Cb6(2) | Cr6(2)    | Cb6(4)     | Cr6(4) | Cb6(6) | Cr6(6) |  |  |

| PD3(5)      | Cb5(0) | Cr5(0)   | Cb5(2) | Cr5(2)    | Cb5(4)     | Cr5(4) | Cb5(6) | Cr5(6) |  |  |

| PD3(4)      | Cb4(0) | Cr4(0)   | Cb4(2) | Cr4(2)    | Cb4(4)     | Cr4(4) | Cb4(6) | Cr4(6) |  |  |

| PD3(3)      | Cb3(0) | Cr3(0)   | Cb3(2) | Cr3(2)    | Cb3(4)     | Cr3(4) | Cb3(6) | Cr3(6) |  |  |

| PD3(2)      | Cb2(0) | Cr2(0)   | Cb2(2) | Cr2(2)    | Cb2(4)     | Cr2(4) | Cb2(6) | Cr2(6) |  |  |

| PD3(1)      | Cb1(0) | Cr1(0)   | Cb1(2) | Cr1(2)    | Cb1(4)     | Cr1(4) | Cb1(6) | Cr1(6) |  |  |

| PD3(0)      | Cb0(0) | Cr0(0)   | Cb0(2) | Cr0(2)    | Cb0(4)     | Cr0(4) | Cb0(6) | Cr0(6) |  |  |

| PD1(7 to 0) |        | not used |        |           |            |        |        |        |  |  |

Table 22 Format 3; customized YUV 4:2:2 format (FMT-bits in index 00 = 011)

| INPUT       |       | CLOCK CYCLE (PIXEL SEQUENCE) |       |      |       |      |       |      |  |  |  |  |

|-------------|-------|------------------------------|-------|------|-------|------|-------|------|--|--|--|--|

| SIGNAL      | 0     | 1                            | 2     | 3    | 4     | 5    | 6     | 7    |  |  |  |  |

| PD2(7 to 0) | Y(0)  | Y(1)                         | Y(2)  | Y(3) | Y(4)  | Y(5) | Y(6)  | Y(7) |  |  |  |  |

| PD3(7 to 0) | Cb(0) | _                            | Cb(2) | -    | Cb(4) | _    | Cb(6) | _    |  |  |  |  |

| PD1(7 to 0) | Cr(0) | -                            | Cr(2) | _    | Cr(4) | _    | Cr(6) | -    |  |  |  |  |

**Table 23** Format 4; YUV 4 : 4 : 4 format (FMT-bits in index 00 = 100)

| INPUT       |       | CLOCK CYCLE (PIXEL SEQUENCE) |       |       |       |       |       |       |  |  |  |  |  |

|-------------|-------|------------------------------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

| SIGNAL      | 0     | 1                            | 2     | 3     | 4     | 5     | 6     | 7     |  |  |  |  |  |

| PD2(7 to 0) | Y(0)  | Y(1)                         | Y(2)  | Y(3)  | Y(4)  | Y(5)  | Y(6)  | Y(7)  |  |  |  |  |  |

| PD3(7 to 0) | Cb(0) | Cb(1)                        | Cb(2) | Cb(3) | Cb(4) | Cb(5) | Cb(6) | Cb(7) |  |  |  |  |  |

| PD1(7 to 0) | Cr(0) | Cr(1)                        | Cr(2) | Cr(3) | Cr(4) | Cr(5) | Cr(6) | Cr(7) |  |  |  |  |  |

**Table 24** Format 5; RGB 4 : 4 : 4 format (FMT-bits in index 00 = 101)

| INPUT       |      | CLOCK CYCLE (PIXEL SEQUENCE) |      |      |      |      |      |      |  |  |  |  |  |

|-------------|------|------------------------------|------|------|------|------|------|------|--|--|--|--|--|

| SIGNAL      | 0    | 1                            | 2    | 3    | 4    | 5    | 6    | 7    |  |  |  |  |  |

| PD2(7 to 0) | R(0) | R(1)                         | R(2) | R(3) | R(4) | R(5) | R(6) | R(7) |  |  |  |  |  |

| PD3(7 to 0) | G(0) | G(1)                         | G(2) | G(3) | G(4) | G(5) | G(6) | G(7) |  |  |  |  |  |

| PD1(7 to 0) | B(0) | B(1)                         | B(2) | B(3) | B(4) | B(5) | B(6) | B(7) |  |  |  |  |  |

Table 25 Format 7; indexed colour format (FMT-bits in index 00 = 111), input codes 0 to 255 are allowed, output code of CLUTs should preferably be the same as given in format 5

| INPUT<br>SIGNAL |        | CLOCK CYCLE (PIXEL SEQUENCE) |        |        |        |        |        |        |  |  |  |  |  |

|-----------------|--------|------------------------------|--------|--------|--------|--------|--------|--------|--|--|--|--|--|

|                 | 0      | 1                            | 2      | 3      | 4      | 5      | 6      | 7      |  |  |  |  |  |

| PD2(7 to 0)     | INC(0) | INC(1)                       | INC(2) | INC(3) | INC(4) | INC(5) | INC(6) | INC(7) |  |  |  |  |  |

1996 Sep 27

19

**7110826 0109335 956**

**SAA7199B**

**Table 26** Input data levels for formats 0 to 4 and 5; EBU colour bar; 100% white equals 100 IRE intensity, 5% colour saturation for formats 1 to 4, 100% for format 5

| INPUT<br>CHANNEL | LEVEL       | DIGITAL LEVEL | CODE             | CCRIR-BIT | FORMAT |  |

|------------------|-------------|---------------|------------------|-----------|--------|--|

| Υ                | 0 IRE       | 12            | offset binary    | 0         | 0 to 4 |  |

|                  | 100 IRE     | 230           | 1                |           |        |  |

| Cb               | bottom peak | -101          | two's complement | 0         | 0 to 4 |  |

|                  | colourless  | 0             | 1                |           | •      |  |

|                  | top peak    | 100           | 1                |           |        |  |

| Cr               | bottom peak | -106          | two's complement | 0         | 0 to 4 |  |

|                  | colourless  | 0             | 1                |           |        |  |

|                  | top peak    | 105           | 1                |           |        |  |

| Υ                | 0 IRE       | 16            | offset binary    | 1         | 0 to 4 |  |

|                  | 100 IRE     | 235           | 1                |           |        |  |

| Cb               | bottom peak | 44            | offset binary    | 1         | 0 to 4 |  |

|                  | colourless  | 128           | 1                |           |        |  |

|                  | top peak    | 212           |                  |           |        |  |

| Cr               | bottom peak | 44            | offset binary    | 1         | 0 to 4 |  |

|                  | colourless  | 128           | 1                |           |        |  |

|                  | top peak    | 212           | 1                |           |        |  |

| R, G and B       | 0 IRE       | 16            | offset binary    | 1         | 5      |  |

|                  | 100 IRE     | 235           | 1                |           | }      |  |

#### **GENLOCK INPUT DATA**

Table 27 Format 7; CVBS GENLOCK input data format has an 8-bit word length, the input data comes from an analog-to-digital converter (TDA8708) with gain controlled and clamped CVBS or VBS signals

| INPUT        |                           |           | CLO     | CK CYCLE (                        | E (PIXEL SEQUENCE)                              |                                   |         |         |  |  |

|--------------|---------------------------|-----------|---------|-----------------------------------|-------------------------------------------------|-----------------------------------|---------|---------|--|--|

| SIGNAL       | 0                         | 1         | 2       | 3                                 | 4                                               | 5                                 | 6       | 7       |  |  |

| CVBS(7-0)    | CVBS(0)                   | CVBS(1)   | CVBS(2) | CVBS(3)                           | CVBS(4)                                         | CVBS(5)                           | CVBS(6) | CVBS(7) |  |  |

| Conditions   | of CVBS inp               | ut signal |         | two's complement representation   |                                                 |                                   |         |         |  |  |