# *TruePHY™* ET1011 Gigabit Ethernet Transceiver

#### **Features**

- 10Base-T, 100Base-TX, and 1000Base-T gigabit Ethernet transceiver:

- 0.13 µm process

- 128-pin TQFP:

- □ RGMII, GMII, MII, RTBI, and TBI interfaces to MAC or switch

- 68-pin MLCC:

- □ RGMII and RTBI interfaces to MAC or switch

- Low power consumption:

- Less than 750 mW in 1000Base-T mode

- Advanced power management

- ACPI compliant wake-on-LAN support

- Oversampling architecture to improve signal integrity and SNR

- Optimized, extended performance echo and NEXT filters

- All digital baseline wander correction

- Digital PGA control

- On-chip diagnostic support

- Automatic speed negotiation

- Automatic speed downshift

- Single supply 3.3 V or 2.5 V operation:

- On-chip regulator controllers

- 3.3 V or 2.5 V digital I/O

- 1.0 V core power supplies

- 1.8 V or 2.5 V for transformer center tap

- JTAG

## Introduction

Agere Systems ET1011 is a gigabit Ethernet transceiver fabricated on a single CMOS chip. Packaged in either a 128-pin TQFP or a 68-pin MLCC, the ET1011 is built on 0.13 µm technology for low power consumption and application in server and desktop NIC cards. It features single power supply operation using on-chip regulator controllers. The 10/100/1000Base-T device is fully compliant with *IEEE*® 802.3, 802.3u, and 802.3ab standards.

The ET1011 uses an oversampling architecture to gather more signal energy from the communication channel than possible with traditional architectures. The additional signal energy or analog complexity transfers into the digital domain. The result is an analog front end that delivers robust operation, reduced cost, and lower power consumption than traditional architectures.

Using oversampling has allowed for the implementation of a fractionally spaced equalizer, which provides better equalization and has greater immunity to timing jitter, resulting in better signal-to-noise ratio (SNR) and thus improved BER. In addition, advanced timing algorithms are used to enable operation over a wider range of cabling plants.

# **Table of Contents**

| Contents                                                            | Page | Contents                                       | Page  |

|---------------------------------------------------------------------|------|------------------------------------------------|-------|

| Features                                                            | 1    | Clock Timing                                   | 74    |

| Introduction                                                        | 1    | JTAG Timing                                    |       |

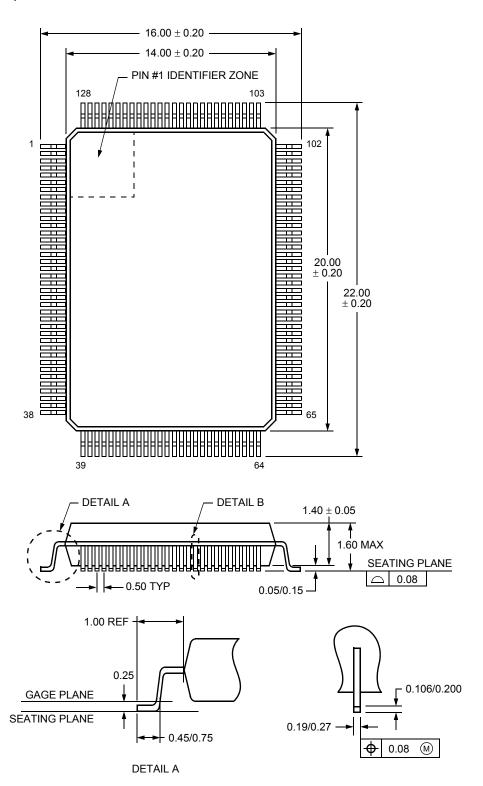

| Functional Description                                              | 4    | Package Diagram, 128-Pin TQFP                  |       |

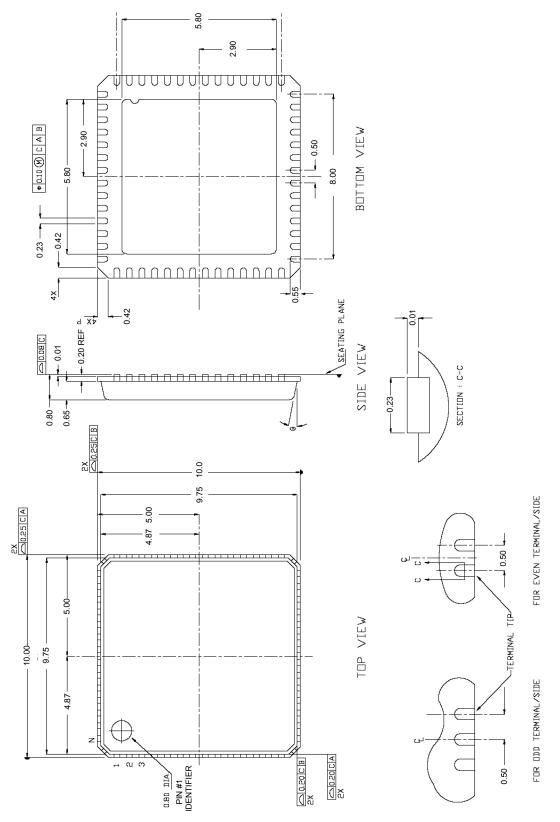

| Oversampling Architecture                                           |      | Package Diagram, 68-Pin MLCC                   |       |

| Automatic Speed Downshift                                           |      | Ordering Information                           |       |

| Transmit Functions                                                  |      | Related Product Documentation                  |       |

| Receive Functions                                                   |      |                                                |       |

| Autonegotiation                                                     |      |                                                |       |

| Carrier Sense (128-pin TQFP only)                                   |      | Table                                          | Page  |

| Link Monitor                                                        |      |                                                | •     |

| Loopback Mode                                                       |      | Table 1. Agere Systems ET1011 Device Signal    | ls    |

| Digital Loopback                                                    |      | by Interface, 128-Pin TQFP                     |       |

| Analog Loopback                                                     |      | and 68-Pin MLCC                                | 14    |

| LEDs                                                                |      | Table 2. Multiplexed Signals on the ET1011     | 19    |

| Resetting the ET1011                                                |      | Table 3. GMII Signal Description (1000Base-T   | Mode) |

| Low-Power Modes                                                     |      | (128-pin TQFP Only)                            | 21    |

| Pin Information                                                     |      | Table 4. RGMII Signal Description              |       |

| Pin Diagram, 128-Pin TQFP                                           |      | (1000Base-T Mode)                              | 22    |

| Pin Diagram, 68-Pin MLCC                                            |      | Table 5. MII Interface (100Base-TX and 10Base  |       |

| Pin Descriptions, 128-Pin TQFP and                                  | 13   | (128-pin TQFP Only)                            |       |

| 68-Pin MLCC                                                         | 1.1  | Table 6. Ten-Bit Interface (1000Base-T)        |       |

| Hardware Interfaces                                                 |      | (128-pin TQFP Only)                            | 24    |

| MAC Interface                                                       |      | Table 7. RTBI Signal Description               |       |

|                                                                     |      | (1000Base-T Mode)                              | 25    |

| Management Interface                                                |      | Table 8. Management Frame Structure            |       |

| Configuration InterfaceLEDs Interface                               |      | Table 9. Management Interface                  |       |

|                                                                     | 32   | Table 10. Autonegotiation Modes                |       |

| Media-Dependent Interface: Transformer Interface                    | 24   | Table 11. Master/Slave Preference              |       |

|                                                                     |      | Table 12. MDI/MDI-X Configuration              |       |

| Clocking and Reset                                                  |      | Table 13. Configuration Signals                |       |

| JTAG                                                                |      | Table 14. LED                                  |       |

| Regulator Control                                                   |      | Table 15. Transformer Interface Signals        |       |

| Power, Ground, and No Connect                                       |      | Table 16. Clocking and Reset                   |       |

| Cable Diagnostics                                                   |      | Table 17. JTAG Test Interface                  |       |

| Register Description                                                |      | Table 18. Regulator Control Interface          |       |

| Register Address Map Electrical Specifications                      |      | Table 19. Supply Voltage Combinations          |       |

| •                                                                   |      | Table 20. Power, Ground, and No Connect        |       |

| Absolute Maximum Ratings                                            |      | Table 21. Cable Diagnostic Functions           |       |

| Recommended Operating Conditions  Device Electrical Characteristics |      | Table 22. Register Address Map                 |       |

|                                                                     |      | Table 23. Register Type Definition             |       |

| Timing Specification                                                | 02   | Table 24. Control Register—Address 0           |       |

| GMII 1000Base-T Transmit Timing                                     | 62   | Table 25. Status Register—Address 1            |       |

| (128-pin TQFP only)                                                 | 02   | Table 26. PHY Identifier Register 1—Address 2  |       |

| GMII 1000Base-T Receive Timing                                      | 62   | Table 27. PHY Identifier Register 2—Address 3  |       |

| (128-pin TQFP only)<br>RGMII 1000Base-T Transmit Timing             |      | Table 28. Autonegotiation Advertisement        | _     |

| •                                                                   |      | Register—Address 4                             | 43    |

| RGMII 1000Base-T Receive Timing                                     |      | Table 29. Autonegotiation Link Partner Ability |       |

| MII 100Base-TX Transmit Timing                                      |      | Register—Address 5                             | 44    |

| MII 100Base-TX Receive Timing                                       |      | Table 30. Autonegotiation Expansion Register-  |       |

| MII 10Base-T Transmit Timing                                        |      | Address 6                                      |       |

| MII 10Base-T Receive Timing                                         |      |                                                |       |

| Serial Management Interface Timing                                  |      |                                                |       |

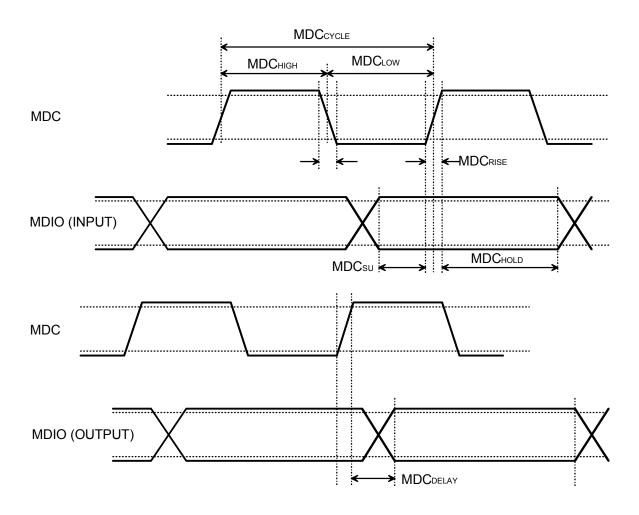

| Reset Timing                                                        | 13   |                                                |       |

# Table of Contents (continued)

| Table     | P                                                                 | age  | Table                  | F                                                                | Page     |

|-----------|-------------------------------------------------------------------|------|------------------------|------------------------------------------------------------------|----------|

| Table 31. | Autonegotiation Next Page Transmit                                |      | Table 67.              | Reset Timing                                                     | 73       |

|           | Register—Address 7                                                | 45   | Table 68.              | Clock Timing                                                     | 74       |

| Table 32. | Link Partner Next Page Register—                                  |      |                        | TAG Timing                                                       |          |

|           | Address 8                                                         | 46   |                        | Chip Set Names and Part Numbers                                  |          |

| Table 33. | 1000 Base-T Control Register—                                     |      | Table 71.              | Related Product Documentation                                    | 78       |

|           | Address 9                                                         | 47   |                        |                                                                  |          |

| Table 34. | 1000Base-T Status Register—                                       |      | F:                     | -                                                                | <b>3</b> |

| T.I. 05   | Address 10                                                        | 48   | Figure                 | ·                                                                | Page     |

| Table 35. | Reserved Registers—                                               | 40   | F:                     | ET4044 Disab Disamen                                             | 4        |

| Table 26  | Addresses 11—14                                                   | 49   | Figure 1.              | ET1011 Block Diagram                                             |          |

| Table 36. | Extended Status Register—                                         | 40   | Figure 2.              | Loopback Functionality                                           |          |

| Table 27  | Address 15 Reserved Registers—Addresses 16—1                      |      | Figure 3.              | Digital Loopback                                                 |          |

|           |                                                                   | 0.49 | Figure 4.<br>Figure 5. | Replica Analog Loopback                                          |          |

| Table 30. | Loopback Control Register— Address 19                             | 50   | Figure 5.              | Line Driver Analog Loopback<br>Pin Diagram for ET1011 in 128-Pin | 10       |

| Tahla 30  | Reserved Registers—Address 20                                     |      | i igui e o.            | TQFP Package (Top View)                                          | 12       |

|           | Management Interface (MI) Control                                 | 0 1  | Figure 7.              | Pin Diagram for ET1011 in 68-Pin ML0                             |          |

| Table 40. | Register—Address 21                                               | 51   | rigure 7.              | Package (Top View)                                               |          |

| Table 41  | PHY Configuration Register—                                       | 0 1  | Figure 8.              | ET1011 Gigabit Ethernet Card                                     | 10       |

| Tuble 41. | Address 22                                                        | 52   | r igure o.             | Block Diagram                                                    | 20       |

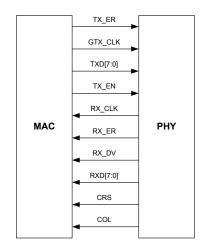

| Table 42  | PHY Control Register—Address 23                                   |      | Figure 9               | GMII MAC-PHY Signals                                             |          |

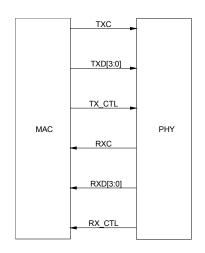

|           | Interrupt Mask Register—Address 24                                |      |                        | RGMII MAC-PHY Signals                                            |          |

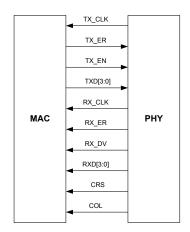

|           | Interrupt Status Register—Address 25 .                            |      |                        | MII Signals                                                      |          |

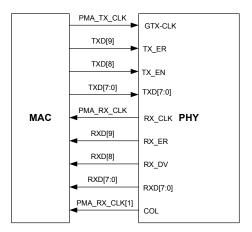

|           | PHY Status Register—Address 26                                    |      |                        | . Ten-Bit Interface                                              |          |

|           | LED Control Register 1—Address 27                                 |      |                        | . Reduced Ten-Bit Interface                                      |          |

|           | LED Control Register 2—Address 28                                 |      | -                      | . GMII 1000Base-T Transmit Timing                                |          |

|           | Reserved Registers—Addresses 29—3                                 |      | -                      | . GMII 1000Base-T Receive Timing                                 |          |

| Table 49. | Absolute Maximum Ratings                                          | 50   | Figure 16.             | . RGMII 1000Base-T Transmit Timing—                              | -        |

| Table 50. | Recommended Operating Conditions                                  | 59   |                        | Trace Delay                                                      | 64       |

| Table 51. | Device Characteristics—3.3V Digital                               |      | Figure 17.             | . RGMII 1000Base-T Transmit Timing—                              | -        |

|           | I/O Supply (DVDDIO)                                               | 60   |                        | Internal Delay                                                   |          |

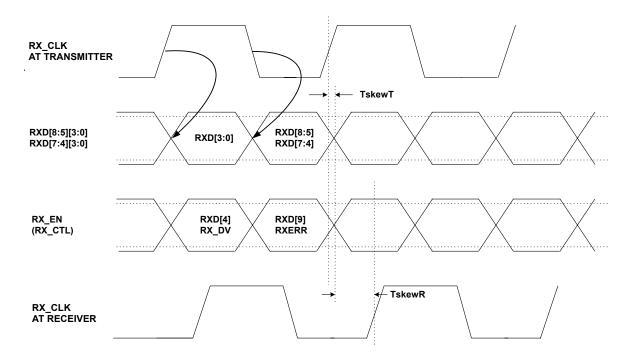

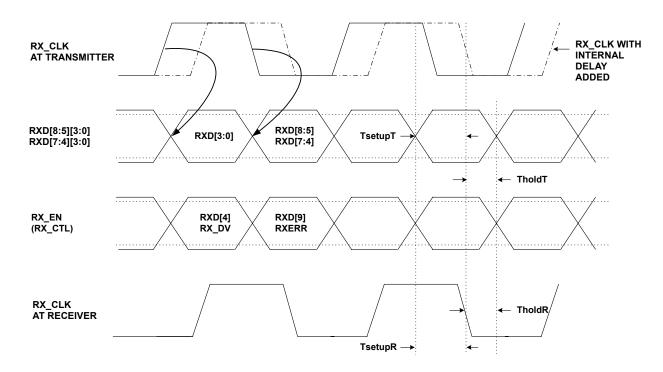

| Table 52. | Device Characteristics—2.5 V Digital                              |      | Figure 18.             | . RGMII 1000Base-T Receive Timing—                               |          |

|           | I/O Supply (DVDDIO)                                               | 60   |                        | Trace Delay                                                      |          |

| Table 53. | Current Consumption GMII/RGMII                                    |      | Figure 19.             | . RGMII 1000Base-T Receive Timing—                               |          |

|           | 1000Base-T                                                        | 61   |                        | Internal Delay                                                   |          |

| Table 54. | Current Consumption MII/RMII                                      |      | -                      | MII 100Base-TX Transmit Timing                                   |          |

| <b>.</b>  | 100Base-TX                                                        | 61   |                        | MII 100Base-TX Receive Timing                                    |          |

| Table 55. | Current Consumption MII/RMII                                      | 04   | •                      | MII 10Base-T Transmit Timing                                     |          |

| Table F6  | 10Base-T                                                          |      | -                      | MII 10Base-T Receive Timing                                      |          |

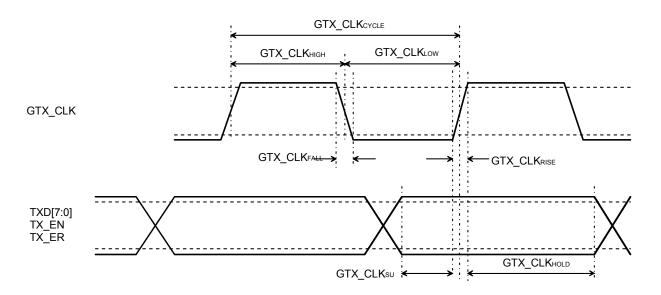

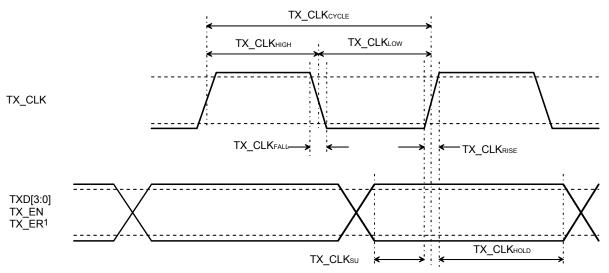

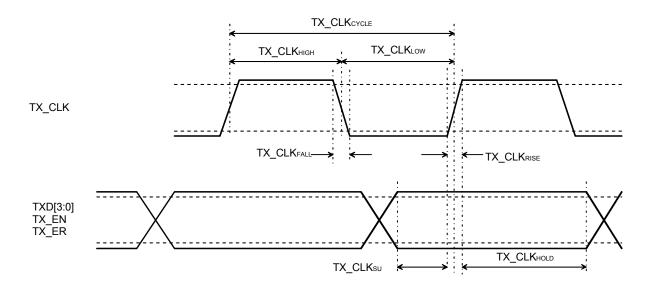

|           | GMII 1000Base-T Transmit Timing                                   |      |                        | Serial Management Interface Timing .                             |          |

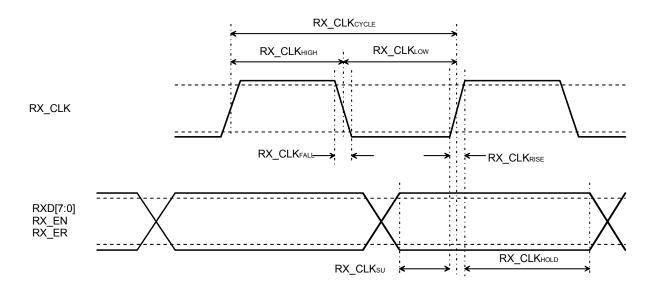

|           | GMII 1000Base-T Receive Timing                                    |      |                        | Reset Timing  Clock Timing                                       |          |

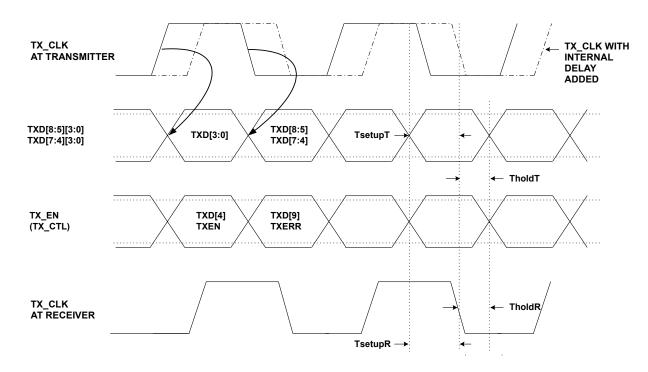

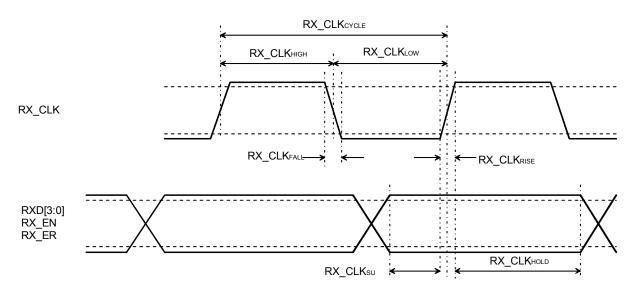

|           | RGMII 1000Base-T Transmit Timing RGMII 1000Base-T Transmit Timing |      |                        | JTAG Timing                                                      |          |

|           | RGMII 1000Base-T Transmit Timing                                  |      | rigule 27.             | . JIAG IIIIIII                                                   | 13       |

|           | RGMII 1000Base-T Receive Timing                                   |      |                        |                                                                  |          |

|           | MII 100Base-TX Transmit Timing                                    |      |                        |                                                                  |          |

|           | MII 100Base-TX Receive Timing                                     |      |                        |                                                                  |          |

|           | MII 10Base-T Transmit Timing                                      |      |                        |                                                                  |          |

|           | MII 10Base-T Receive Timing                                       |      |                        |                                                                  |          |

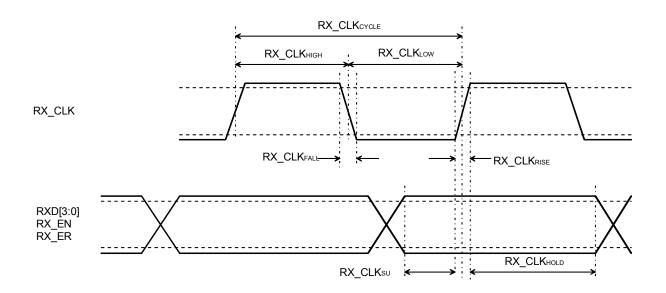

|           | Serial Management Interface Timing                                |      |                        |                                                                  |          |

|           | 5                                                                 | _    |                        |                                                                  |          |

# **Functional Description**

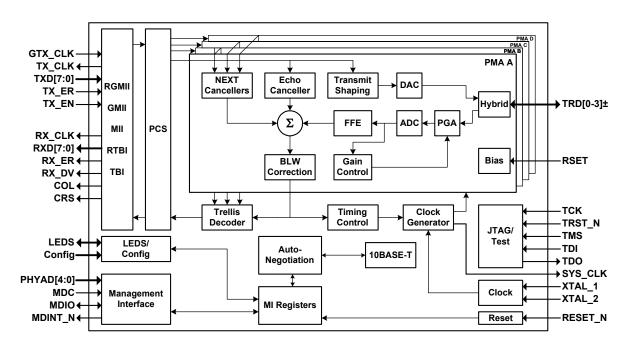

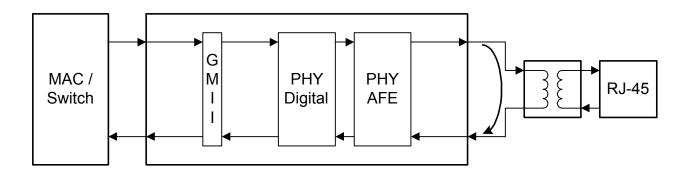

Agere Systems ET1011 is a gigabit Ethernet transceiver that simultaneously transmits and receives on each of the four UTP pairs of category 5 cable (signal dimensions or channels A, B, C, and D) at 125 Msymbols/s using five-level pulse amplitude modulation (PAM). Figure 1 is a block diagram of its basic configuration.

Figure 1. ET1011 Block Diagram

### Oversampling Architecture

The ET1011 architecture uses oversampling techniques to sample at two times the symbol rate. A fractionally spaced feed forward equalizer (FFE) adapts to remove intersymbol interference (ISI) and to shape the spectrum of the received signal to maximize the (SNR) at the trellis decoder input. The FFE equalizes the channel to a fixed target response. Oversampling enables the use of a fractionally spaced equalizer (FSE) structure for the FFE, resulting in symbol rate clocking for both the FFE and the rest of the receiver. This provides robust operation and substantial power savings.

#### **Automatic Speed Downshift**

Automatic speed downshift is an enhanced feature of autonegotiation that allows the ET1011 to:

- Fallback in speed, based on cabling conditions or link partner abilities.

- Operate over CAT-3 cabling (in 10Base-T mode).

- Operate over two-pair CAT-5 cabling (in 100Base-TX mode).

For speed fallback, the ET1011 first tries to autonegotiate by advertising 1000Base-T capability. After a number of failed attempts to bring up the link, the ET1011 falls back to advertising 100Base-TX and restarts the autonegotiation process. This process continues through all speeds down to 10Base-T. At this point, there are no lower speeds to try and so the host enables all technologies and starts again.

PHY configuration register, address 22, bits 11and 10 enable automatic speed downshift and specifies if fall-back to 10Base-T is allowed. PHY control register, address 23, bits 11and 12 specify the number of failed attempts before downshift (programmable to 1, 2, 3, or 4 attempts).

#### **Transmit Functions**

#### 1000Base-T Encoder

In 1000Base-T mode, the ET1011 translates 8-bit data from the MAC interfaces into a code group of four quinary symbols that are then transmitted by the PMA as 4D five-level PAM signals over the four pairs of CAT-5 cable.

#### 100Base-TX Encoder

In 100Base-TX mode, 4-bit data from the media independent interface (MII) is 4B/5B encoded to output 5-bit serial data at 125 MHz. The bit stream is sent to a scrambler, and then encoded to a three-level MLT3 sequence that is then transmitted by the PMA.

#### 10Base-T Encoder

In 10Base-T mode, the ET1011 transmits and receives Manchester-encoded data.

## **Receive Functions**

## Decoder 1000Base-T

In 1000Base-T mode, the PMA recovers the 4D PAM signals after compensating for the cabling conditions. The resulting code group is decoded to 8-bit data. Data stream delimiters are translated appropriately, and the data is output to the receive data pins of the MAC interfaces. The GMII receive error signal is asserted when invalid code groups are detected in the data stream.

#### **Decoder 100Base-TX**

In 100Base-TX mode, the PMA recovers the three-level MLT3 sequence that is descrambled and 5B/4B decoded to 4-bit data. This is output to the MII receive data pins after data stream delimiters have been translated appropriately. The MII receive error signal is asserted when invalid code groups are detected in the data stream.

#### Decoder 10Base-T

In 10Base-T mode, the ET1011 decodes the Manchester-encoded received signal.

#### Hybrid

The hybrid subtracts the transmitted signal from the input signal allowing full-duplex operation on each of the twisted-pair cables.

### **Programmable Gain Amplifier (PGA)**

The PGA operates on the received signal in the analog domain prior to the analog-to-digital converter (ADC). The gain control module monitors the signal at the output of the ADC in the digital domain to control the PGA. It implements a gain that maximizes the signal at the ADC while ensuring that no hard clipping occurs.

#### **Clock Generator**

A clock generator circuit uses the 25 MHz input clock signal and a phase-locked loop (PLL) circuit to generate all the required internal analog and digital clocks. A 125 MHz system clock is also generated and is available as an output clock.

#### **Analog-to-Digital Converter**

The ADC operates at 250 MHz oversampling at twice the symbol rate in 1000Base-T and 100Base-TX. This enables innovative timing recovery and fractional skew correction and has allowed transfer of analog complexity to the digital domain.

## **Timing Recovery/Generation**

The timing recovery and generator block creates transmit and receive clocks for all modes of operation. In transmit mode, the 10Base-T and 100Base-TX modes use the 25 MHz clock input. While in receive mode, the input clock is locked to the receive data stream. 1000Base-T is implemented using a master-slave timing scheme, where the master transmit and receive are locked to the 25 MHz clock input, and the slave acquires timing information from the receive data stream. Timing recovery is accomplished by first acquiring lock on one channel and then making use of the constant phase relationship between channels to lock on the other pairs, resulting in a simplified PLL architecture. Timing shifts due to changing environmental conditions are tracked by the ET1011.

## **Adaptive Fractionally Spaced Equalizer**

The ET1011's unique oversampling architecture employs an FSE in place of the traditional FFE structure. This results in robust equalization of the communications channel, which translates to superior bit error rate (BER) performance over the widest variety of worst-case cabling scenarios. The all-digital equalizer automatically adapts to changing conditions.

#### **Echo and Crosstalk Cancellers**

Since the four twisted pairs are bundled together and not insulated from each other in Gigabit Ethernet, each of the transmitted signals is coupled onto the three other cables and is seen at the receiver as near-end crosstalk (NEXT). A hybrid circuit is used to transmit and receive simultaneously on each pair. If the transmitter is not perfectly matched to the line, a signal component will be reflected back as an echo. Reflections can also occur at other connectors or cable imperfections. The ET1011 cancels echo and NEXT by subtracting an estimate of these signals from the equalizer output.

### **Baseline Wander Correction**

A known issue for 1000Base-T and 100Base-TX is that the transformer attenuates at low frequencies. As a result, when a large number of symbols of the same sign are transmitted consecutively, the signal at the receiver gradually dies away. This effect is called baseline wander. By employing a circuit that continuously monitors and compensates for this effect, the probability of encountering a receive symbol error is reduced.

#### Autonegotiation

Autonegotiation is implemented in accordance with *IEEE* 802.3. The device supports 10Base-T, 100Base-TX, and 1000Base-T and can autonegotiate between them in either half- or full-duplex mode. It can also parallel detect 10Base-T or 100Base-TX. If autonegotiation is disabled, a 10Base-T or 100Base-TX link can be manually selected via the *IEEE* MII registers.

#### **Pair Skew Correction**

In gigabit Ethernet, pair skew (timing differences between pairs of cable) can result from differences in length or manufacturing variations between the four individual twisted-pair cables. The ET1011 automatically corrects for both integer and fractional symbol timing differences between pairs.

#### **Automatic MDI Crossover**

During autonegotiation, the ET1011 automatically detects and sets the required MDI configuration so that the remote transmitter is connected to the local receiver and vice versa. This eliminates the need for crossover cables or crosswired (MDIX) ports. If the remote device also implements automatic MDI crossover, and/or the crossover is implemented in the cable, the crossover algorithm ensures that only one element implements the required crossover.

## **Polarity Inversion Correction**

In addition to automatic MDI crossover that is necessary for autonegotiation, 10Base-T, and 100Base-TX operation, the ET1011 automatically corrects crossover of the additional two pairs used in 1000Base-T. Polarity inversion on all pairs is also corrected. Both of these effects may arise if the cabling has been incorrectly wired.

## Carrier Sense (128-pin TQFP only)

The carrier sense signal (CRS) of the MAC interface is asserted by the ET1011 whenever the receive medium is nonidle. In half-duplex mode, CRS may also be asserted when the transmit medium is nonidle. The CRS may be enabled on transmit in half-duplex mode by writing to the PHY configuration register, address 22, bit 15.

#### **Link Monitor**

#### 1000Base-T

Once 1000Base-T is autonegotiated and the link is established, both link partners continuously monitor their local receiver status. If the master device determines a problem with its receiver, it signals the slave and both devices cease transmitting data but transmit IDLE. If the master retrains its receiver within 750 ms, then normal operation recommences. Otherwise, both devices restart autonegotiation.

If the slave device determines a problem with its receiver, it ceases transmitting and expects the master to transmit the IDLE sequence. If the slave retrains its receiver within 350 ms, normal operation recommences when the master signals that its receiver is ready. If either receiver fails to reacquire, then autonegotiation is restarted.

#### 100Base-TX

In 100Base-TX mode, the ET1011 monitors the link and determines the link quality based on signal energy, mean square error and scrambler lock. If the link quality is deemed insufficient, transmit and receive data are disabled. If the link had been autonegotiated then control is handed back to autonegotiation. If the link had been manually set, the 100Base-TX receiver is retrained, and the transmitter is set to transmit idle. Once the link quality has been recovered, data transmit and receive are enabled.

#### 10Base-T

In 10Base-T mode, the ET1011 monitors the link and determines the link quality based on the presence of valid link pulses. If the link is deemed to have failed and the link had been autonegotiated, then control is handed back to autonegotiation. If the link had been manually set, the ET1011 continues to try to reestablish the link.

## **Loopback Mode**

Enabling loopback mode allows in-circuit testing of the ET1011's digital and analog data path.

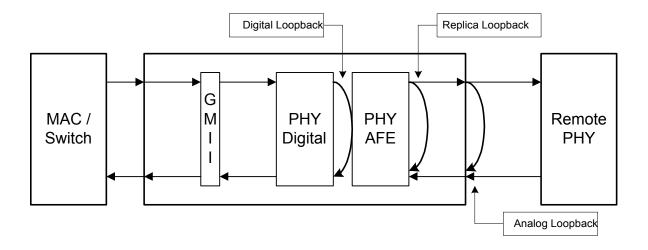

The ET1011 provides several options for loopback that test and verify various functional blocks within the PHY. These are digital loopback and analog loopback. Figure 2 is a block diagram that shows the PHY loopback functionality.

Figure 2. Loopback Functionality

The loopback mode is selected by setting the respective bit in the PHY loopback control register (MII register address 19, bits 9:15). The default loopback mode is digital MII loopback. Loopback is enabled by writing to the PHY control register, address 0, bit 14.

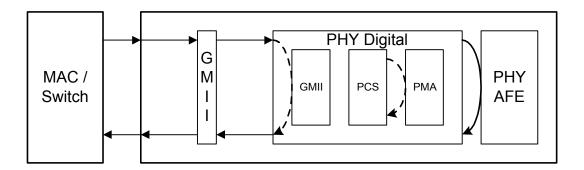

## **Digital Loopback**

Digital loopback provides the ability to loop the transmitted data back to the receiver at various internal points between the MAC interface and the analog front end (AFE) circuitry. The point at which the data is looped back is selected using the loopback control register (address 19) with the following options being available: MII, PCS, PMD and all digital. Selecting the MII option gives a simple loopback with minimal latency where the data is looped back directly at the media-independent interface. This loopback is currently set as the default, but it should be noted that it only exercises a small percentage of the PHY circuitry. When the all digital option is selected, the transmitted data is looped back at the interface between the digital and the analog circuitry, thereby exercising a high percentage of the digital logic. The PCS and PMD options represent intermediate points between the two extremes. Figure 3 shows a block diagram of digital loopback.

Figure 3. Digital Loopback

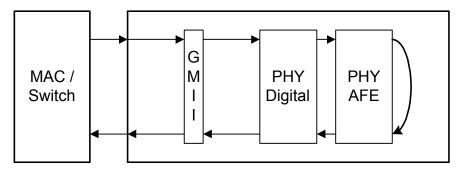

## **Analog Loopback**

Analog loopback provides the ability to loop the transmitted signal back to the receiver within the AFE. The point at which the signal is looped back is selected using the loopback control register with the following options being provided: replica and line driver.

Selecting the replica option causes the transmitted signal to be looped back through the replica generation circuitry of the on-chip hybrid, thereby allowing most of the digital and analog circuitry to be exercised. This loopback mode may be used even when the device is connected to a network because nothing is transmitted to or received from the MDI in this case.

The most thorough loopback test available without the cooperation of a link partner is provided by selecting the line driver option where the PHY transmits to and receives from the MDI. However, in general, this loopback may not be used when the device is connected to a network because it could cause an unanticipated response from the link partner. Figure 4 shows a block diagram of replica analog loopback and Figure 5 shows a block diagram of line driver analog loopback.

Figure 4. Replica Analog Loopback

Figure 5. Line Driver Analog Loopback

#### **LEDs**

Seven status LEDs are provided. These can be used to indicate speed of operation, duplex mode, link status, etc. There is a very high degree of programmability allowed. Hence, the LEDs can be programmed to different status functions from their default value, or they can be controlled directly from the MII register interface. The LED signal pins can also be used for general-purpose I/O if not needed for LED indication.

Note: The 68-pin MLCC has only two LEDs. Both can be programmed through MII register 28 to provide all speed indications as well as link and activity indications.

## Resetting the ET1011

The ET1011 provides the ability to reset the device by hardware (pin RESET\_N) or via software through the management interface. A hardware reset is accomplished by driving the active-low pin RESET\_N to 0 volts for a minimum of 1  $\mu$ s. The configuration pins and the physical address configuration are read during a hardware reset.

A software reset is accomplished by setting bit 15 of the control register (MII register address 0 bit 15). The configuration pins and the physical address configuration are not read during software reset.

#### **Low-Power Modes**

The ET1011 supports a number of powerdown modes.

## **Hardware Powerdown Mode**

Hardware powerdown is entered when the COMA signal is driven high. In hardware powerdown, all PHY functions (analog and digital) are disabled. During hardware powerdown, SYS\_CLK is not available and the MII registers are not accessible.

At exit from hardware powerdown, the ET1011 does the following:

- Initializes all analog circuits including the PLL.

- Initializes all digital logic and state machines.

- Reads and latches the PHY address pins.

- Initializes all MII registers to their default values (H/W configuration pins are reread).

#### **Software Powerdown Mode**

Software powerdown is entered when bit 11 of the control register (MII register address 0 bit 11) is set. In software powerdown, all PHY functions except the serial management interface and clock circuitry are disabled. The MII registers can be read or written. If the system clock output is enabled (MII register address 22 bit 4), the 125 MHz system clock will still be available for use by the MAC on pin SYS\_CLK.

At exit from software powerdown, the ET1011 does the following:

■ Initializes all digital logic and state machines.

**Note:** At exit from software powerdown, the H/W configuration pins and the PHY address pins are not reread and the MII registers are not reset to their default values. These operations are only done during reset or recovery from hardware powerdown.

#### Wake-On-LAN Powerdown Mode

ACPI power consumption compliant Wake-On-LAN mode is implemented on the ET1011 by using the *IEEE* standard MII registers to put the PHY into 10Base-T or 100Base-TX modes. Clearing the advertisement of 1000Base-T (MII register address 9 bits 8, 9) and setting the desired 10Base-T and 100Base-TX advertisement (MII register address 4 bits 5-8) activates this feature. This must be followed by an autonegotiation restart via the control register (MII register address 0 bit 9).

## **Low-Power Energy-Detect Mode**

When COMA is asserted, low-power energy-detect (LPED) mode is enabled if LPED\_EN\_N is low. In this mode, the PHY monitors the cable for energy. If energy is detected, the MDINT\_N pin is asserted. The PHY exits from LPED mode when COMA is deasserted.

## **Pin Information**

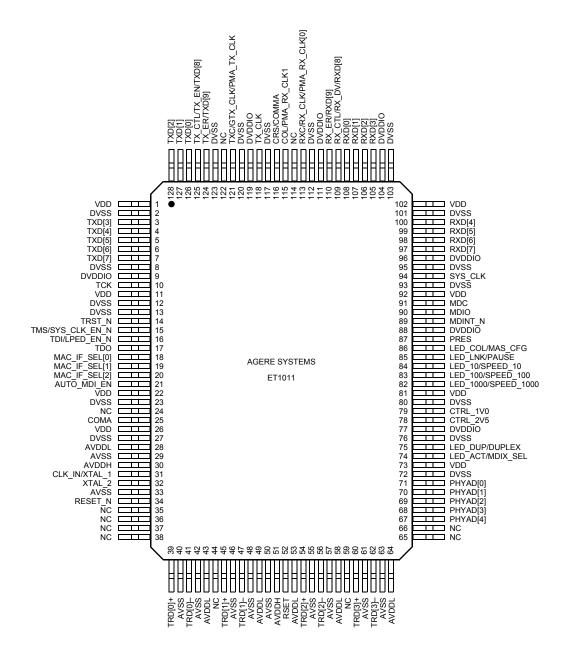

## Pin Diagram, 128-Pin TQFP

Figure 6. Pin Diagram for ET1011 in 128-Pin TQFP Package (Top View)

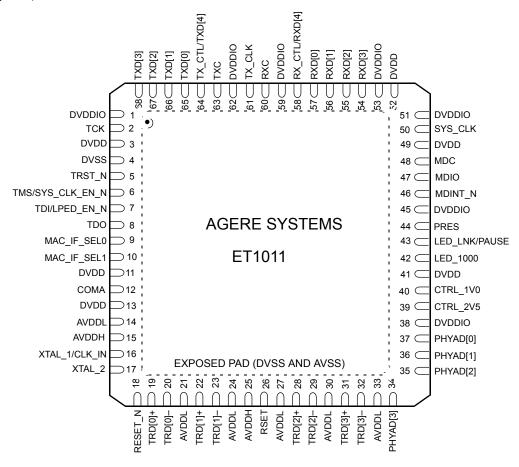

## Pin Diagram, 68-Pin MLCC

Figure 7. Pin Diagram for ET1011 in 68-Pin MLCC Package (Top View)

# Pin Descriptions, 128-Pin TQFP and 68-Pin MLCC

Table 1. Agere Systems ET1011 Device Signals by Interface, 128-Pin TQFP and 68-Pin MLCC

| Name       | Description            | Pad<br>Type | Hyst./<br>Open-<br>Drain | Internal<br>Pull-Up/<br>Pull-Down | 3-State | Analog | Pin #<br>128-TQFP                         | Pin #<br>68-MLCC  |

|------------|------------------------|-------------|--------------------------|-----------------------------------|---------|--------|-------------------------------------------|-------------------|

| MAC: GMII- | -Gigabit Media Indepe  | ndent       | Interface (12            | 8-pin TQFP                        | only)   |        |                                           |                   |

| GTX_CLK    | GMII transmit clock    | ı           | Н                        | <u> </u>                          | _       | _      | 121                                       | _                 |

| TX_ER      | Transmit error         | I           | Н                        | _                                 | _       | _      | 124                                       | _                 |

| TX_EN      | Transmit enable        | I           | Н                        | _                                 | _       | _      | 125                                       | _                 |

| TXD[7:0]   | Transmit data bits     | I           | Н                        | _                                 | _       | _      | 126, 127, 128,<br>3, 4, 5, 6, 7           | _                 |

| RX_CLK     | Receive clock          | 0           | _                        | _                                 | Z       |        | 113                                       | _                 |

| RX_ER      | Receive error          | 0           | _                        | _                                 | Z       | _      | 110                                       | _                 |

| RX_DV      | Receive data valid     | 0           | _                        | _                                 | Z       | _      | 109                                       | _                 |

| RXD[7:0]   | Receive data bits      | 0           | _                        | _                                 | Z       | —      | 108, 107, 106,<br>105, 100, 99,<br>98, 97 | _                 |

| CRS        | Carrier sense          | 0           | _                        | _                                 | Z       | _      | 116                                       | _                 |

| COL        | Collision detect       | 0           | _                        | _                                 | Z       |        | 115                                       | _                 |

| MAC: RGMI  | I—Reduced Gigabit Me   | edia Ind    | dependent li             | nterface                          |         |        |                                           |                   |

| TXC        | RGMII transmit clock   | ı           | Н                        | <u> </u>                          | _       | _      | 121                                       | 63                |

| TXD[3:0]   | Transmit data bits     | I           | Н                        | _                                 | _       | _      | 126, 127,<br>128, 3                       | 68, 67,<br>66, 65 |

| TX_CTL     | Transmit control       | ı           | Н                        | _                                 | _       |        | 125                                       | 64                |

| RXC        | Receive clock          | 0           | _                        | _                                 | Z       | _      | 113                                       | 60                |

| RXD[3:0]   | Receive data bits      | 0           | —                        | _                                 | Z       | _      | 108, 107,<br>106, 105                     | 54, 55,<br>56, 57 |

| RX_CTL     | Receive control        | 0           | _                        | _                                 | Z       | _      | 109                                       | 58                |

| MAC: MII—N | Media Independent Inte | erface (    | (128-pin TQI             | P only)                           |         |        |                                           | •                 |

| TX_CLK     | MII transmit clock     | 0           |                          | _                                 | Z       | _      | 118                                       | _                 |

| TX_ER      | Transmit error         | I           | Н                        | _                                 | _       | _      | 124                                       | _                 |

| TX_EN      | Transmit enable        | I           | Н                        | _                                 | _       | _      | 125                                       | _                 |

| TXD[3:0]   | Transmit data bits     | I           | Н                        | _                                 | _       | _      | 126, 127,<br>128, 3                       | _                 |

| RX_CLK     | Receive clock          | 0           | _                        | _                                 | Z       | _      | 113                                       | _                 |

| RX_ER      |                        |             | _                        | _                                 | Z       | _      | 110                                       | _                 |

| RX_DV      | Receive data valid     | 0           | _                        |                                   | Z       | _      | 109                                       | _                 |

| RXD[3:0]   | Receive data bits      | 0           | _                        | _                                 | Z       | _      | 108, 107,<br>106, 105                     |                   |

| CRS        | Carrier sense          | 0           | _                        | _                                 | Z       | _      | 116                                       | _                 |

| COL        | Collision detect       | 0           | _                        | _                                 | Z       | _      | 115                                       | _                 |

# Pin Descriptions, 128-Pin TQFP and 68-Pin MLCC (continued)

Table 1. Agere Systems ET1011 Device Signals by Interface, 128-Pin TQFP and 68-Pin MLCC (continued)

| Name             | Description               | Pad<br>Type | Hyst./<br>Open-<br>Drain | Internal<br>Pull-Up/<br>Pull-Down | 3-State | Analog | Pin #<br>128-TQFP                                      | Pin #<br>68-MLCC        |

|------------------|---------------------------|-------------|--------------------------|-----------------------------------|---------|--------|--------------------------------------------------------|-------------------------|

| MAC: TBI—Ten-B   | it Interface (128-pin T   | QFP or      | ıly)                     |                                   |         |        |                                                        |                         |

| PMA_ TX_CLK      | TBI transmit clock        | I           | Н                        | _                                 | _       | _      | 121                                                    | _                       |

| TXD[9:0]         | Transmit data bits        | I           | Н                        | _                                 | _       | _      | 126, 127,<br>128, 3, 4, 5,<br>6, 7, 125, 124           | _                       |

| PMA_RX_CLK[0]    | TBI receive clock         | 0           | _                        | _                                 | Z       | _      | 113                                                    | _                       |

| RXD[9:0]         | Receive data bits         | 0           |                          | _                                 | Z       |        | 108, 107,<br>106, 105,<br>100, 99, 98,<br>97, 109, 110 | 1                       |

| PMA_RX_ CLK[1]   |                           | 0           | _                        | _                                 | Z       |        | 115                                                    |                         |

| COMMA            | MA Valid comma detect     |             | Н                        | _                                 | _       | _      | 116                                                    | _                       |

| MAC: RTBI—Red    | uced Ten-Bit Interface    |             |                          |                                   |         |        |                                                        |                         |

| TXC              | RTBI transmit clock       | ı           | Н                        | _                                 | _       | _      | 121                                                    | 63                      |

| TXD[4:0]         | Transmit data bits        | I           | Н                        | _                                 | _       | _      | 4, 3, 128,<br>127, 126                                 | 68, 67,<br>66, 65<br>64 |

| RXC              | RTBI receive clock        | 0           | _                        | _                                 | Z       | _      | 113                                                    | 60                      |

| RXD[4:0]         | Receive data bits         | 0           | _                        | _                                 | Z       | _      | 108, 107,<br>106, 105, 109                             | 58, 54, 55,<br>56, 57   |

| MDI: Transformer | Interface                 | •           |                          | •                                 |         |        |                                                        |                         |

| TRD[0]+          | Transmit and receive      | I/O         | _                        | _                                 | _       | Α      | 39                                                     | 19                      |

| TRD[0]-          | differential pair         |             |                          |                                   |         |        | 41                                                     | 20                      |

| TRD[1]+          | Transmit and receive      | I/O         | _                        | _                                 | _       | Α      | 45                                                     | 22                      |

| TRD[1]-          | differential pair         |             |                          |                                   |         |        | 47                                                     | 23                      |

| TRD[2]+          | Transmit and receive      | I/O         | _                        | _                                 | _       | Α      | 54                                                     | 28                      |

| TRD[2]-          | differential pair         |             |                          |                                   |         |        | 56                                                     | 29                      |

| TRD[3]+          | Transmit and receive      | I/O         | _                        | _                                 | _       | Α      | 60                                                     | 31                      |

| TRD[3]-          | differential pair         |             |                          |                                   |         |        | 62                                                     | 32                      |

| RSET             | Analog reference resistor | I/O         | _                        | _                                 | _       | Α      | 52                                                     | 26                      |

# Pin Descriptions, 128-Pin TQFP and 68-Pin MLCC (continued)

Table 1. Agere Systems ET1011 Device Signals by Interface, 128-Pin TQFP and 68-Pin MLCC (continued)

| Name                       | Description                        | Pad<br>Type | Hyst./<br>Open-<br>Drain | Internal<br>Pull-Up/<br>Pull-Down | 3-State | Analog   | Pin #<br>128-<br>TQFP    | Pin #<br>68-<br>MLCC       |

|----------------------------|------------------------------------|-------------|--------------------------|-----------------------------------|---------|----------|--------------------------|----------------------------|

| Management Inte            | rface                              |             |                          |                                   |         |          |                          |                            |

| PHYAD[4:0]                 | PHY address 4—1<br>PHY address 0   | I           | _                        | Pull-down<br>Pull-up              | _       | <u> </u> | 70, 71,<br>69, 68,<br>67 | 34, 35,<br>36, 37<br>PHYAD |

| MDC                        | Management interface clock         | I           | _                        | Pull-down                         | _       | _        | 91                       | [3:0]<br>48                |

| MDIO                       | Management data I/O                | I/O         | _                        | Pull-up                           | _       | _        | 90                       | 47                         |

| MDINT_N                    | Management interface interrupt     | 0           | OD                       |                                   | _       | _        | 89                       | 46                         |

| Configuration <sup>1</sup> |                                    |             |                          |                                   |         |          |                          |                            |

| SPEED_1000                 | 1000Base-T speed select            |             | _                        | Pull-up                           | _       | _        | 82                       | _                          |

| SPEED_100                  | 100Base-TX speed select            |             | _                        | Pull-up                           | _       | _        | 83                       | _                          |

| SPEED_10                   | 10Base-T speed select              |             | _                        | Pull-up                           | _       | _        | 84                       | _                          |

| DUPLEX                     | Half- or full-duplex configuration |             |                          | Pull-up                           |         |          | 75                       | _                          |

| AUTO_MDI_EN                | Auto-MDI detection enable          | I           |                          | Pull-up                           | _       | _        | 21                       | _                          |

| MDIX_SEL                   | MDI/MDI-X autodetection            | I           |                          | Pull-down                         | _       | _        | 74                       | _                          |

| MAS_CFG                    | Master slave configuration         | I           | _                        | Pull-down                         | _       |          | 86                       | _                          |

| PAUSE                      | Pause mode                         |             |                          | Pull-down                         | _       | _        | 85                       | 43                         |

| MAC_IF_SEL[1]              | MAC interface select 1             | I           |                          | Pull-down                         | _       |          | 19                       | 10                         |

| MAC_IF_SEL[2]              | MAC interface select 2             |             |                          | Pull-down                         |         |          | 20                       | _                          |

| SYS_CLK_EN_N               | System clock enable                | Ι           | _                        | Pull-up                           | _       |          | 15                       | 6                          |

| LPED_EN_N                  | Low power energy detection enable  | Ι           | _                        | Pull-up                           | _       | _        | 16                       | 7                          |

| PRES                       | Precision resistor                 |             | _                        | _                                 | _       | _        | 87                       | 44                         |

<sup>1.</sup> Configuration signals are multiplexed with the LED controls. During a reset, the status of the configuration pins are latched and used to set the configuration and later to select the polarity to drive the LEDs.

# Pin Descriptions, 128-Pin TQFP and 68-Pin MLCC (continued)

Table 1. Agere Systems ET1011 Device Signals by Interface, 128-Pin TQFP and 68-Pin MLCC (continued)

| Name          | Description Pad Hyst./ Internal 3-State A<br>Type Open- Pull-Up/<br>Drain Pull-Down |     | Analog | Pin #<br>128-TQFP | Pin #<br>68-MLCC |   |    |    |

|---------------|-------------------------------------------------------------------------------------|-----|--------|-------------------|------------------|---|----|----|

| LED Interface | •                                                                                   |     |        |                   |                  |   |    |    |

| LED_1000      | 1000Base-T LED                                                                      | 0   | _      | Pull-up           | _                | _ | 82 | 42 |

| LED_100       | 100Base-TX LED                                                                      | 0   | _      | Pull-up           | _                | _ | 83 | _  |

| LED_10        | 10Base-T LED                                                                        | 0   | _      | Pull-up           | _                | _ | 84 | _  |

| LED_DUP       | Duplex LED                                                                          | 0   | _      | Pull-up           | _                | _ | 75 | _  |

| LED_LNK       | Link established LED                                                                | 0   | _      | Pull-down         | _                | _ | 85 | 43 |

| LED_COL       | Collision LED                                                                       | 0   | _      | Pull-down         | _                | _ | 86 | _  |

| LED_ACT       | Transmit and receive activity                                                       | 0   | _      | Pull-down         | _                |   | 74 | _  |

| JTAG          |                                                                                     |     |        |                   |                  |   |    |    |

| TCK           | Test clock                                                                          | I   | _      | _                 | _                | _ | 10 | 2  |

| TRST_N        | Test reset                                                                          | I   | Η      | Pull-down         | _                | _ | 14 | 5  |

| TMS           | Test mode select                                                                    | I   | _      | Pull-up           | _                | _ | 15 | 6  |

| TDI           | Test data input                                                                     | ı   | _      | Pull-up           | _                | _ | 16 | 7  |

| TDO           | Test data output                                                                    | 0   | _      | Pull-up           | _                | _ | 17 | 8  |

| Clocking and  | Reset                                                                               |     |        |                   |                  |   |    |    |

| CLK_IN        | Reference clock input                                                               | I/O | _      | _                 |                  | Α | 31 | 16 |

| XTAL_1        | Reference crystal input                                                             | I/O |        | _                 | _                | Α | 31 | 16 |

| XTAL_2        | Reference crystal                                                                   | I/O |        | _                 | _                | Α | 32 | 17 |

| SYS_CLK       | System clock                                                                        | 0   | _      | _                 | _                | _ | 94 | 50 |

| RESET_N       | Reset                                                                               | ı   | _      | _                 | _                | _ | 34 | 18 |

| COMA          | Hardware powerdown                                                                  | I   | _      | Pull-down         | _                | _ | 25 | 12 |

| Regulator Co  | ntrol                                                                               |     |        |                   |                  |   |    |    |

| CTRL_1V0      | Regulator control 1.0 V                                                             | 0   | _      | _                 | _                | Α | 79 | 40 |

| CTRL_2V5      | Regulator control 2.5 V                                                             | 0   | _      | _                 | _                | Α | 78 | 39 |

<sup>1.</sup> Configuration signals are multiplexed with the LED controls. During a reset, the status of the configuration pins are latched and used to set the configuration and later to select the polarity to drive the LEDs.

# Pin Descriptions, 128-Pin TQFP and 68-Pin MLCC (continued)

Table 1. Agere Systems ET1011 Device Signals by Interface, 128-Pin TQFP and 68-Pin MLCC (continued)

| Name              | Description                       | Pad<br>Type | Hyst./<br>Open-<br>Drain | Internal<br>Pull-Up/<br>Pull-Down | 3-State | Analog | Pin #<br>128-TQFP                                                                     | Pin #<br>68-MLCC                |

|-------------------|-----------------------------------|-------------|--------------------------|-----------------------------------|---------|--------|---------------------------------------------------------------------------------------|---------------------------------|

| Power, Grou       | ind, and No Connect               |             |                          |                                   |         |        |                                                                                       |                                 |

| DVDDIO            | Digital I/O 2.5 V or 3.3 V supply | VDD         | _                        | _                                 | _       | _      | 9, 77, 88, 96,<br>104, 111, 119                                                       | 1, 38, 45,<br>51, 53, 59,<br>62 |

| VDD               | Digital core 1.0 V supply         | VDD         | _                        | _                                 |         | _      | 1, 11, 22, 26,<br>73, 81, 92, 102                                                     | 3, 11, 13,<br>41, 49, 52        |

| DVSS <sup>2</sup> | Digital ground                    | Vss         | _                        | _                                 | _       | _      | 2, 4, 8, 12, 13,<br>23, 27, 72, 76,<br>80, 93, 95,<br>101, 103, 112,<br>117, 120, 123 | 4                               |

| AVDDH             | Analog power 2.5 V                | VDD         | _                        | _                                 | _       | _      | 30, 51                                                                                | 15, 25                          |

| AVDDL             | Analog power 1.0 V                | VDD         | _                        | _                                 | _       | _      | 28, 43, 49,<br>53, 58, 64                                                             | 14, 21, 24,<br>27, 30, 33       |

| AVSS <sup>2</sup> | Analog ground                     | Vss         |                          | _                                 | _       | _      | 29, 33, 40, 42,<br>46, 48, 50, 55,<br>57, 61, 63                                      | _                               |

| NC                | Reserved—do not connect           | _           |                          | _                                 | _       | _      | 24, 35, 36, 37,<br>38, 44, 59, 65,<br>66, 114, 122                                    | _                               |

<sup>1.</sup> Configuration signals are multiplexed with the LED controls. During a reset, the status of the configuration pins are latched and used to set the configuration and later to select the polarity to drive the LEDs.

<sup>2.</sup> For the 68-MLCC, all AVss and DVss pins share a common ground pin (pad) in the center of the device.

# Pin Descriptions, 128-Pin TQFP and 68-Pin MLCC (continued)

Table 2. Multiplexed Signals on the ET1011

| Default         | Pin #<br>128-TQFP | Pin #<br>68-MLCC | Alternate                  |

|-----------------|-------------------|------------------|----------------------------|

| COL             | 115               | _                | COL <sup>1, 6</sup>        |

|                 |                   |                  | PMA_RX_CLK[1] <sup>2</sup> |

| CRS             | 116               |                  | CRS <sup>1, 6</sup>        |

|                 |                   |                  | COMMA <sup>2</sup>         |

| GTX_CLK         | 121               | _                | GTX_CLK <sup>1</sup>       |

|                 |                   |                  | PMA_TX_CLK <sup>2</sup>    |

|                 |                   |                  | TXC <sup>3, 4</sup>        |

| LED_ACT         | 74                | _                | LED_ACT                    |

|                 |                   |                  | MDIX_SEL <sup>5</sup>      |

| LED_COL         | 86                | _                | LED_COL                    |

|                 |                   |                  | MAS_CFG <sup>5</sup>       |

| LED_DUP         | 75                | _                | LED_DUP                    |

|                 |                   |                  | DUPLEX <sup>5</sup>        |

| LED_LNK         | 85                | _                | LED_LNK                    |

| _               |                   |                  | PAUSE <sup>5</sup>         |

| LED_1000        | 82                | _                | LED_1000                   |

| _               |                   |                  | SPEED_1000 <sup>5</sup>    |

| LED_100         | 83                | _                | LED_100                    |

|                 |                   |                  | SPEED 100 <sup>5</sup>     |

| LED_10          | 84                | _                | LED_10                     |

| _               |                   |                  | SPEED 10 <sup>5</sup>      |

| RX_CLK          | 113               | _                | RX CLK <sup>1, 6</sup>     |

| _               |                   |                  | PMA_RX_CLK[0] <sup>2</sup> |

|                 |                   |                  | RXC <sup>3, 4</sup>        |

| RX_ER           | 110               | _                | RX ER <sup>1, 6</sup>      |

| _               |                   |                  | RXD[9] <sup>2</sup>        |

| RX_DV           | 109               |                  | RX DV <sup>1, 6</sup>      |

| _               |                   |                  | RXD[8] <sup>2</sup>        |

|                 |                   |                  | RX_CTL <sup>3</sup>        |

| TDI             | 16                | 7                | TDI                        |

|                 |                   |                  | LPED_EN_N <sup>5</sup>     |

| TMS             | 15                | 6                | TMS                        |

|                 |                   |                  | SYS CLK EN N <sup>5</sup>  |

| TX_ER           | 124               | _                | TX_ER <sup>1, 6</sup>      |

| _               |                   |                  | TXD[9] <sup>2</sup>        |

| TX_EN           | 125               | _                | TX_EN <sup>1, 6</sup>      |

| _               | -                 |                  | TXD[8] <sup>2</sup>        |

| XTAL_1          | 31                | 16               | XTAL_1                     |

| · <del></del> · |                   | . •              | CLK_IN                     |

<sup>1.</sup> GMII signal.

RTBI signal.

<sup>2.</sup> TBI signal.

<sup>5.</sup> Reset/configuration signal.

<sup>3.</sup> RGMII signal.

<sup>6.</sup> MII signal.

## **Hardware Interfaces**

The following hardware interfaces are included on the ET1011 gigabit Ethernet transceiver:

- MAC interfaces:

- GMII (128-pin TQFP only)

- RGMII

- MII (128-pin TQFP only)

- TBI (128-pin TQFP only)

- RTBI

- Media dependent interface

- Management interface

- Configuration interface

- LED interface

- Clock and reset signals

- JTAG interface

- Regulator control

- Power and ground signals

Several of the pins of the MAC interface are multiplexed, but they are designed to be interchangeable so that the device can change the MAC interface once the transmission capabilities (1000Base-T, 100Base-TX, and 10Base-T) are established.

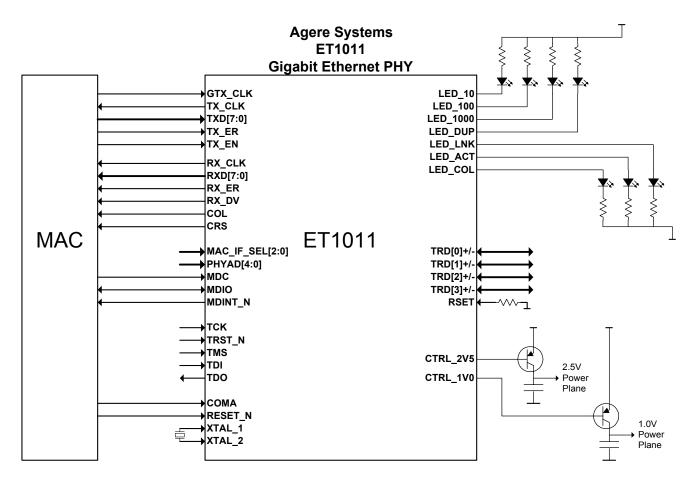

The following diagram shows the various interfaces on each ET1011 and how they connect to the MAC and other support devices in a typical application.

Figure 8. ET1011 Gigabit Ethernet Card Block Diagram

## **MAC Interface**

The ET1011 supports RGMII, GMII, MII, RTBI, and TBI interfaces to the MAC. The MAC interface mode is selected via the hardware configuration pins, MAC\_IF\_SEL[2:0].

# Gigabit Media Independent Interface (GMII) (128-pin TQFP only)

The GMII is fully compliant with *IEEE* 802.3 clause 35. The GMII interface mode is selected by setting the hardware configuration pins MAC\_IF\_SEL[2:0] = 000.

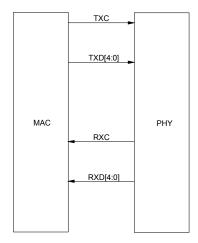

Figure 9. GMII MAC-PHY Signals

Table 3. GMII Signal Description (1000Base-T Mode) (128-pin TQFP Only)

| Pin Name | Pin #<br>128 TQFP                            | Pin Description        | Functional Description                                                                                                                                                                                                                                                                                                            |

|----------|----------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GTX_CLK  | 121                                          | Transmit clock         | The MAC drives this 125 MHz clock signal that is held low during autonegotiation or when operating in modes other than 1000Base-T.                                                                                                                                                                                                |

| TX_ER    | 124                                          | Transmit error         | The MAC drives this signal high to indicate a transmit coding error.                                                                                                                                                                                                                                                              |

| TX_EN    | 125                                          | Transmit enable        | The MAC drives this signal high to indicate that data is available on the transmit data bus.                                                                                                                                                                                                                                      |

| TXD[7:0] | 126, 127,<br>128, 3, 4,<br>5, 6, 7           | Transmit data bits 7—0 | The MAC transmits data synchronized with RX_CLK to the ET1011 for transmission on the media dependent (transformer) interface.                                                                                                                                                                                                    |

| RX_CLK   | 113                                          | Receive clock          | The ET1011 generates a 125 MHz clock to synchronize receive data.                                                                                                                                                                                                                                                                 |

| RX_ER    | 110                                          | Receive error          | The ET1011 drives RX_ER to indicate that an error was detected in the frame that was received and is being transmitted to the MAC.                                                                                                                                                                                                |

| RX_DV    | 109                                          | Receive data valid     | The ET1011 drives RX_DV to indicate that it is sending recovered and decoded data to the MAC.                                                                                                                                                                                                                                     |

| RXD[7:0] | 108, 107,<br>106, 105,<br>100, 99,<br>98, 97 | Receive data           | The ET1011 transmits data that is synchronized with RX_CLK to the MAC.                                                                                                                                                                                                                                                            |

| CRS      | 116                                          | Carrier sense          | The carrier sense signal (CRS) of the MAC interface is asserted by the ET1011 whenever the receive medium is nonidle. In half-duplex mode, CRS may also be asserted when the transmit medium is nonidle. The CRS may be enabled on transmit in half-duplex mode by writing to the PHY configuration register, address 22, bit 15. |

| COL      | 115                                          | Collision detect       | In 10Base-T, 100Base-TX, and 1000Base-T half-duplex modes, COL is asserted when both transmit and receive media are nonidle.                                                                                                                                                                                                      |

# Reduced Gigabit Media Independent Interface (RGMII)

The RGMII interface is fully compliant with the RGMII Rev. 1.3 specification. The RGMII interface mode is selected by setting the hardware configuration pins MAC\_IF\_SEL[2:0] = 100 (trace delay) or 110 (DLL delay).

Figure 10. RGMII MAC-PHY Signals

Table 4. RGMII Signal Description (1000Base-T Mode)

| Pin Name | Pin #<br>128-TQFP      | Pin #<br>68-MLCC  | Pin Description    | Functional Description                                                                                                                                                                                                                       |

|----------|------------------------|-------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXC      | 121                    | 63                | Transmit clock     | The MAC drives this 125 MHz clock signal that is held low during autonegotiation or when operating in modes other than 1000Base-T. To obtain the 1 gigabit transmission rate, the MAC uses both the positive and negative clock transitions. |

| TXD[3:0] | 126, 127,<br>128, 3    | 68, 67,<br>66, 65 | Transmit data bits | The MAC transmits data synchronized with RX_CLK to the ET1011 for transmission on the media dependent (transformer) interface. The MAC sends data in two 4-bit nibbles.                                                                      |

| TX_CTL   | 125                    | 64                | Transmit control   | The MAC transmits control signals across this line (TX_ER and TX_EN). The MAC transmits TX_EN¹ on a positive transition of TXC and TX_EN and TX_ER¹ on the negative transition of TXC.                                                       |

| RXC      | 113                    | 60                | Receive clock      | The ET1011 generates a 125 MHz clock to synchronize receive data. To obtain the 1 gigabit transmission rate, the ET1011 uses both the positive and negative clock transitions.                                                               |

| RXD[3:0] | 108, 107,<br>106, 105, | 54, 55,<br>56, 57 | Receive data       | The ET1011 transmits data that is synchronized with RX_CLK to the MAC. The ET1011 sends data in two 4-bit nibbles.                                                                                                                           |

| RX_CTL   | 109                    | 58                | Receive control    | The ET1011 transmits control signals across this line (RX_ER and RX_EN). The ET1011 transmits RX_DV¹ on a positive transition of RXC and RX_EN¹ and RX_ER¹ on the negative transition of TXC.                                                |

<sup>1.</sup> Reference the GMII interface for description of the following parameters: TX\_EN, TX\_ER, RX\_DV, RX\_EN, and RX\_ER.

# Media Independent Interface (MII) (128-pin TQFP only)

The MII is fully compliant with *IEEE* 802.3 clause 22. The MII interface mode is selected by setting the hardware configuration pins MAC\_IF\_SEL[2:0] = 000.

In 100Base-TX and 10Base-T mode, the RXD[7:4] pins are driven low by the ET1011 and the TXD[7:4] pins are ignored. They should not be left floating but should be set either high or low. In the MII interface mode, the GTX\_CLK pin may be held low.

An alternative to the standard MII is provided when operating in 10Base-T or 100Base-TX mode by setting hardware configuration pins MAC\_IF\_SEL[2:0] = 010. In this alternative interface, the MAC provides a reference clock at 2.5 MHz or

25 MHz at the GTX\_CLK pin. The ET1011 then uses a FIFO to resynchronize data presented synchronously with this reference clock.

Figure 11. MII Signals

Table 5. MII Interface (100Base-TX and 10Base-T) (128-pin TQFP Only)

| Pin Name | Pin #<br>128 TQFP     | Pin<br>Description       | Functional Description                                                                                                                                                                                                                                                                                                            |

|----------|-----------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_CLK   | 118                   | Transmit clock           | In 100Base-TX mode, the ET1011 generates 25 MHz reference clocks and in 10Base-T mode provides 2.5 MHz reference clocks.  MAC_IF_SEL[2:0] = 000—this is default behavior.                                                                                                                                                         |

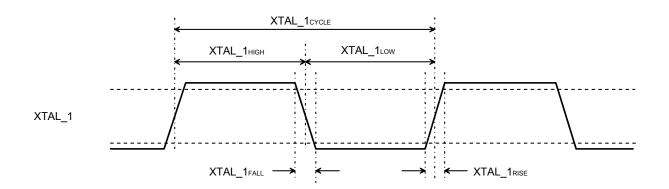

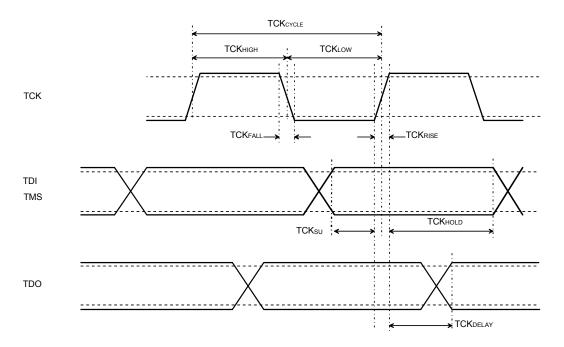

| GTX_CLK  | 121                   | Alternate transmit clock | In 100Base-TX mode, the MAC generates the 25 MHz reference clock and in 10Base-T mode provides a 2.5 MHz reference clock.  MAC_IF_SEL[2:0] = 010.                                                                                                                                                                                 |