## Parallel Fiber Optic Transceiver (4 + 4) x 3.125 Gbps

**Data Sheet**

January 2006

#### **Features**

- Compatible with POP4 MSA usage

- 4 Transmit channels and 4 Receive channels

- Data rate up to 3.125 Gbps per channel

- 850 nm VCSEL array

- Data I/O is CML compatible

- Link reach with 50/125 μm 500 MHz. km fiber, 300-m and 90-m at 2.5 and 3.125-Gbps, respectively

#### **Ordering Information**

ZL60304MJDA Transceiver

Additional heatsink and EMI shield options are available upon request

0°C to +80°C

- Channel BER better than 10<sup>-12</sup>

- Industry standard MPO/MTP™ ribbon fiber connector interface

- Pluggable MegArray<sup>®</sup> connector

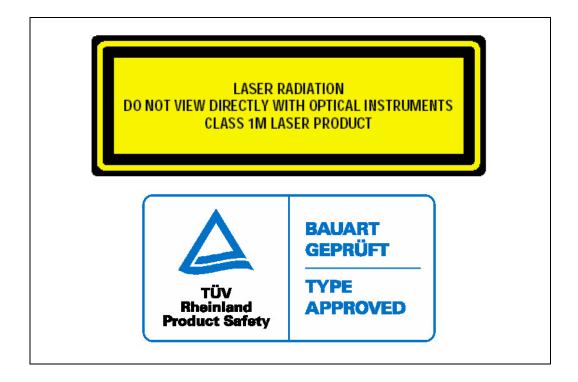

- Laser class 1 M IEC 60825-1:2001 compliant

- Low power consumption, < 1 W</li>

- Power supply 3.3 V

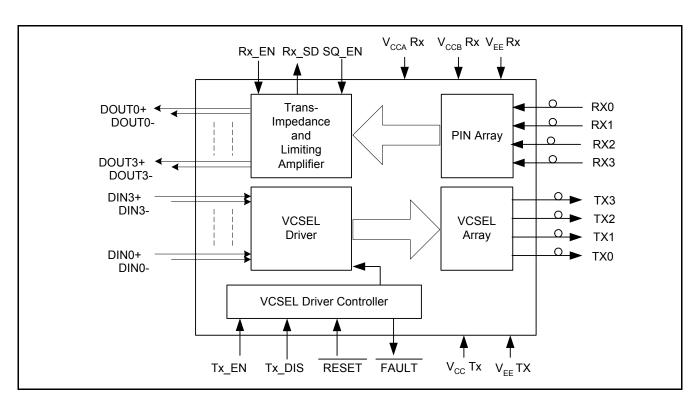

Figure 1 - Transceiver Block Diagram

#### **Applications**

- · High-speed interconnects within and between switches, routers and transport equipment

- Server-Server Clusters, Super-computing interconnections

- InfiniBand™ 4x-SX compliant

- Fibre Channel connections

- · XAUI based interconnections

- · Proprietary backplanes

- Interconnects rack-to-rack, shelf-to-shelf, board-to-board, board-to-optical backplane

#### **Description**

The ZL60304 is a very high-speed transceiver for parallel fiber applications. This transceiver performs E/O and O/E conversions for data transmission over multimode fiber ribbon.

The ZL60304 provides an effective solution for XAUI transmission of optical fibre, providing advantages in terms of power consumption, edge and board density over competing solutions.

The transmit section converts parallel electrical input signals via a laser driver and a VCSEL array into parallel optical output signals at a wavelength of 850 nm.

The receive section converts parallel optical input signals via a PIN photodiode array and a transimpedance and limiting amplifier, into electrical output signals.

The module is fitted with two pluggable industry-standard connectors. For the electrical interface, a 100 position FCI MegArray<sup>®</sup> receptacle (FCI PN: 84513-101) is used. For the optical interface, an industry-standard MTP<sup>TM</sup>(MPO) connector is used, which is compliant with IEC 61754-7. This provides ease of assembly on the host board and enables provisioning of bandwidth on demand.

# ZL60304

# **Table of Contents**

| eatures                                            | . 1 |

|----------------------------------------------------|-----|

| pplications                                        | . 2 |

| escription                                         |     |

| bsolute Maximum Ratings                            |     |

| ecommended Operating Conditions                    |     |

| ransmitter Specifications                          | . 5 |

| Transmitter Control and Status Signal Requirements | . 7 |

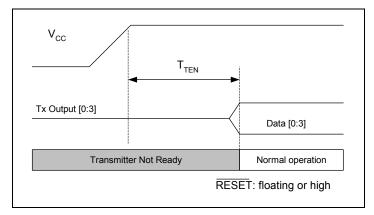

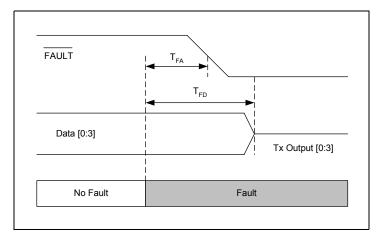

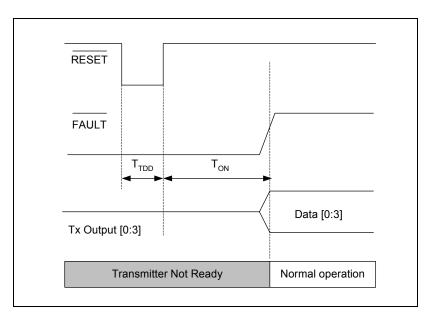

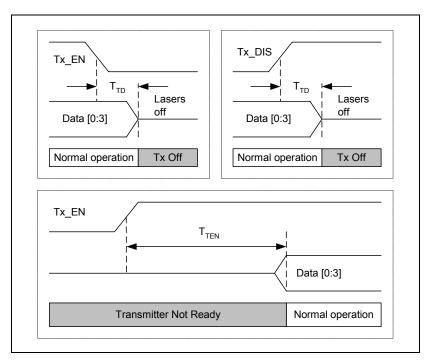

| Transmitter Control and Status Timing Diagrams     | . 8 |

| eceiver Specifications                             | 10  |

| Receiver Status Signal                             | 11  |

| Receiver Status Timing Diagrams                    | 11  |

| ransceiver Module Signals                          | 12  |

| Transceiver Pin Description                        | 13  |

| andling Instructions                               | 14  |

| Cleaning the Optical Interface                     | 14  |

| Connectors                                         |     |

| ESD Handling                                       | 14  |

| ink Reach                                          |     |

| Link Model Parameters                              |     |

| lectrical Interface - Application Examples         | 16  |

| rademarks                                          | 16  |

#### **Absolute Maximum Ratings**

Not necessarily applied together. Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

| Parameter                                         | Symbol           | Min. | Max.                  | Unit |

|---------------------------------------------------|------------------|------|-----------------------|------|

| Supply voltage                                    | V <sub>CC</sub>  | -0.3 | 4.0                   | V    |

| Differential input voltage amplitude <sup>1</sup> | ΔV               |      | 2.4                   | V    |

| Voltage on any pin                                | V <sub>PIN</sub> | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| Relative humidity (non-condensing)                | M <sub>OS</sub>  | 5    | 95                    | %    |

| Storage temperature                               | T <sub>STG</sub> | -40  | 100                   | °C   |

| ESD resistance                                    | V <sub>ESD</sub> |      | ±1                    | kV   |

<sup>1.</sup> Differential input voltage amplitude are peak to peak values.

### **Recommended Operating Conditions**

| Parameter                                    | Symbol            | Min.  | Max.  | Unit              |

|----------------------------------------------|-------------------|-------|-------|-------------------|

| Power supply voltage                         | V <sub>CC</sub>   | 3.135 | 3.465 | V                 |

| Operating case temperature                   | T <sub>CASE</sub> | 0     | 80    | °C                |

| Signalling rate (per channel) <sup>1</sup>   | f <sub>D</sub>    | 1.0   | 3.125 | Gbps              |

| Link distance <sup>2</sup>                   | LD                | 2     |       | m                 |

| Data I/O DC blocking capacitors <sup>3</sup> | C <sub>BLK</sub>  | 100   |       | nF                |

| Power supply noise <sup>4</sup>              | V <sub>NPS</sub>  |       | 200   | mV <sub>p-p</sub> |

- Data patterns are to have maximum run lengths and DC balance shifts no worse than that of a Pseudo Random Bit Sequence of length 2<sup>23</sup>-1 (PRBS-23). Information on lower bit rates and longer run lengths are available on request.

- 2. For maximum distance, see Table 4.

- 3. For AC-coupling, DC blocking capacitors external to the module with a minimum value of 100 nF is recommended.

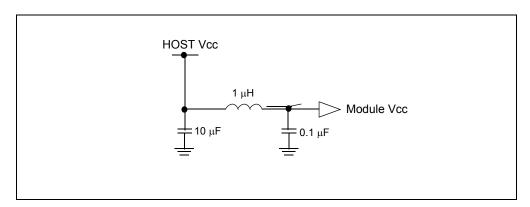

- 4. Power supply noise is defined at the supply side of the recommended filter for all V<sub>CC</sub> supplies over the frequency range of 500 Hz to 3200 MHz with the recommended power supply filter in place.

Figure 2 - Recommended Power Supply Filter

## **Transmitter Specifications**

All parameters apply over "Recommended Operating Conditions" on page 4, unless otherwise stated.

| Parameter                                                        | Symbol                | Min. | Max.  | Unit              |

|------------------------------------------------------------------|-----------------------|------|-------|-------------------|

| Optical Parameters                                               |                       |      |       |                   |

| Launch power (50/125 mm MMF) <sup>1</sup>                        | P <sub>OUT</sub>      | -8   | -2    | dBm               |

| Extinguished output power                                        | P <sub>OFF</sub>      |      | -30   | dBm               |

| Extinction ratio                                                 | ER                    | 6    |       | dB                |

| Optical modulation amplitude <sup>2</sup>                        | OMA                   | 0.19 |       | mW                |

| Center wavelength                                                | λ <sub>C</sub>        | 830  | 860   | nm                |

| Spectral width <sup>3</sup>                                      | Δλ                    |      | 0.85  | nm <sub>rms</sub> |

| Relative intensity noise OMA                                     | RIN <sub>12</sub> OMA |      | -120  | dB/Hz             |

| Optical output rise time (20 - 80%)                              | t <sub>RO</sub>       |      | 150   | ps                |

| Optical output fall time (20 - 80%)                              | t <sub>FO</sub>       |      | 150   | ps                |

| Total jitter contributed (peak to peak) <sup>4</sup>             | TJ                    |      | 0.30  | UI                |

| Deterministic jitter contributed (peak to peak) <sup>4, 5</sup>  | DJ                    |      | 0.125 | UI                |

| Channel to channel skew <sup>6</sup>                             | t <sub>SK</sub>       |      | 150   | ps                |

| Electrical Parameters                                            |                       |      |       |                   |

| Power dissipation                                                | P <sub>D</sub>        |      | 500   | mW                |

| Supply current                                                   | I <sub>CC</sub>       |      | 150   | mA                |

| Differential input voltage amplitude (peak to peak) <sup>7</sup> | $\Delta V_{IN}$       | 200  | 1600  | mV <sub>p-p</sub> |

| Differential input impedance <sup>8</sup>                        | Z <sub>IN</sub>       | 80   | 120   | Ω                 |

| Electrical input rise time (20 - 80%)                            | t <sub>RE</sub>       |      | 140   | ps                |

| Electrical input fall time (20 - 80%)                            | t <sub>FE</sub>       |      | 140   | ps                |

- 1. The average output optical power is compliant with IEC 60825-1 Amendment 2, Class 1M Accessible Emission Limits.

- 2. Informative. Corresponds to  $P_{OUT}$  = -8 dBm and ER = 6 dB.

- 3. Spectral width is measured as defined in EIA/TIA-455-127 Spectral Characterization of Multimode Laser Diodes.

- 4. Total jitter is TP2 TP1 as defined in IEEE 802.3 clause 38.6 (Gigabit Ethernet).

- 5. Deterministic jitter is informative. Combined random and deterministic jitter should be no higher than stated total jitter.

- 6. Channel skew is defined for the condition of equal amplitude, zero ps skew signals applied to the transmitter inputs.

- 7. Differential input voltage is defined as the peak to peak value of the differential voltage between DIN+ and DIN-. Data inputs are CML compatible.

- 8. Differential input impedance is measured between DIN+ and DIN-.

Classified in accordance with IEC 60825-1/A2:2001, IEC 60825-2: 2000

Class 1M Laser Product

Emitted wavelength: 840 nm

#### **Transmitter Control and Status Signal Requirements**

The following table shows the timing relationships of the status and control signals of the transmit section.

| Parameter                                 | Symbol           | Min.               | Тур. | Max.                 | Unit |

|-------------------------------------------|------------------|--------------------|------|----------------------|------|

| Control input voltage high <sup>1</sup>   | V <sub>IH</sub>  | 0.6V <sub>CC</sub> |      | V <sub>CC</sub> +0.5 | V    |

| Control input voltage low                 | V <sub>IL</sub>  | -0.5               |      | 0.2V <sub>CC</sub>   | V    |

| Control pull-up resistor <sup>2</sup>     | R <sub>PU</sub>  | 20                 |      | 50                   | kΩ   |

| Control pull-down resistor <sup>3</sup>   | R <sub>PD1</sub> |                    | 10   |                      | kΩ   |

| Status output voltage low <sup>4, 5</sup> | V <sub>OL</sub>  |                    |      | 0.5                  | V    |

| Status pull-down resistor <sup>4</sup>    | R <sub>PD2</sub> |                    | 10   |                      | kΩ   |

| FAULT assert time                         | T <sub>FA</sub>  |                    |      | 100                  | μS   |

| FAULT lasers off                          | T <sub>FD</sub>  |                    |      | 100                  | μS   |

| RESET duration                            | T <sub>TDD</sub> | 10                 |      |                      | μS   |

| RESET assert time                         | T <sub>OFF</sub> |                    | 5    | 10                   | μS   |

| RESET de-assert time                      | T <sub>ON</sub>  |                    |      | 100                  | ms   |

| Tx_EN assert time                         | T <sub>TEN</sub> |                    |      | 1                    | ms   |

| Tx_EN de-assert time                      | T <sub>TD</sub>  |                    | 5    | 10                   | μS   |

| Tx_DIS assert time                        | T <sub>TD</sub>  |                    | 5    | 10                   | μS   |

| Tx_DIS de-assert time                     | T <sub>TEN</sub> |                    |      | 1                    | ms   |

<sup>1.</sup> Applies to control signals RESET, Tx\_DIS and Tx\_EN.

<sup>2.</sup> Applies to control signals RESET and Tx\_EN. Internal pull-up resistor.

<sup>3.</sup> Applies to control signal Tx\_DIS. Internal pull-down resistor.

<sup>4.</sup> Applies to status signal  $\overline{\text{FAULT}}.$  Internal pull-down to  $\text{V}_{\text{EE}}.$

<sup>5.</sup> With status output sink current max. 2 mA.

#### **Transmitter Control and Status Timing Diagrams**

The following figures show the timing relationships of the status and control signals of the transmit section.

Figure 3 - Transmitter Power-up Sequence

Figure 4 - Transmitter Fault Signal Timing Diagram

Figure 5 - Transmitter Reset Signal Timing Diagram

Figure 6 - Transmitter Enable and Disable Timing Diagram

|            | Tx_DIS High          | Tx_DIS Low           |

|------------|----------------------|----------------------|

| Tx_EN High | Transmitter disabled | Normal operation     |

| Tx_EN Low  | Transmitter disabled | Transmitter disabled |

Table 1 - TruthTable for Transmitter Operation (Pre-condition: RESET floating or HIGH)

#### **Receiver Specifications**

All parameters apply over "Recommended Operating Conditions" on page 4, unless otherwise stated.

| Parameter                                                         | Symbol           | Min. | Max.  | Unit       |

|-------------------------------------------------------------------|------------------|------|-------|------------|

| Optical Parameters                                                |                  |      |       |            |

| Unstressed receiver sensitivity <sup>1</sup>                      | P <sub>IN</sub>  | -14  | -2    | dBm        |

| Center wavelength                                                 | λ <sub>C</sub>   | 830  | 860   | nm         |

| Return loss <sup>2</sup>                                          | RL               | 12   |       | dB         |

| Stressed receiver sensitivity <sup>3</sup>                        | P <sub>SS</sub>  |      | -10.9 | dBm        |

| Total link jitter contribution <sup>4</sup>                       | $TJ_L$           |      | 0.50  | UI         |

| Deterministic link jitter contribution <sup>5</sup>               | $DJ_L$           |      | 0.20  | UI         |

| Channel to channel skew <sup>6</sup>                              | t <sub>SK</sub>  |      | 150   | ps         |

| Signal detect assert                                              | P <sub>SA</sub>  |      | -16   | dBm        |

| Signal detect de-assert                                           | P <sub>SD</sub>  | -31  |       | dBm        |

| Electrical Parameters                                             |                  |      |       |            |

| Power dissipation                                                 | $P_{D}$          |      | 500   | mW         |

| Supply current                                                    | I <sub>CC</sub>  |      | 150   | mA         |

| Differential output voltage amplitude (peak to peak) <sup>7</sup> | $\Delta V_{OUT}$ | 400  | 800   | $mV_{p-p}$ |

| Output differential load impedance <sup>8</sup>                   | Z <sub>L</sub>   | 80   | 120   | Ω          |

| Electrical output rise time (20 - 80%)                            | t <sub>RE</sub>  |      | 150   | ps         |

| Electrical output fall time (20 - 80%)                            | t <sub>FE</sub>  |      | 150   | ps         |

<sup>1.</sup> Receiver sensitivity is measured using a source that does not degrade the sensitivity measurement, i.e. an ideal source. Receive sensitivity for a channel is measured for a BER of 10<sup>-12</sup> and worst case extinction ratio. P<sub>IN</sub> (Min) is measured using a fast rise/fall time source with low RIN and adjacent channel(s) operating with incident power of 6 dB above P<sub>IN</sub> (Min).

<sup>2.</sup> Return loss is measured as defined in TIA/EIA-455-107A Determination of Component Reflectance or Link/System Return Loss Using a Loss Test Set.

<sup>3.</sup> Based on specified Unstressed receiver sensitivity and Gigabit Ethernet link model, "Link Model Parameters" on page 15.

<sup>4.</sup> Total jitter is TP4-TP1 values.

<sup>5.</sup> Deterministic jitter is informative. Combined random and deterministic jitter should be no higher than stated total jitter.

<sup>6.</sup> Channel skew is defined for the condition of equal amplitude, zero ps skew signals applied to the receiver inputs.

<sup>7.</sup> Differential output voltage is defined as the peak to peak value of the differential voltage between DOUT+ and DOUT- and measured with a 100 W differential load connected between DOUT+ and DOUT-. Data outputs are CML compatible.

<sup>8.</sup> See Figure 10.

#### **Receiver Status Signal**

The following table shows the timing relationships of the status and control signals of the receive section.

| Parameter                                   | Symbol            | Min. | Тур. | Max. | Unit |

|---------------------------------------------|-------------------|------|------|------|------|

| Control input voltage high <sup>1</sup>     | V <sub>IH</sub>   | 2.0  |      |      | V    |

| Control input voltage low <sup>1</sup>      | V <sub>IL</sub>   |      |      | 0.9  | V    |

| Control input pull-up current <sup>1</sup>  | I <sub>IN</sub>   | 10   |      | 100  | μА   |

| Status output voltage low <sup>2, 3</sup>   | V <sub>OL</sub>   |      |      | 0.4  | V    |

| Status output pull-up resistor <sup>2</sup> | R <sub>PU</sub>   |      | 3.25 |      | kΩ   |

| Receiver signal detect assert time          | T <sub>SD</sub>   |      | 50   | 200  | μS   |

| Receiver signal detect de-assert time       | T <sub>LOS</sub>  |      | 50   | 200  | μS   |

| Receiver enable assert time                 | T <sub>RXEN</sub> |      | 33   |      | ms   |

| Receiver enable de-assert time              | T <sub>RXD</sub>  |      | 5    |      | μS   |

- 1. Applies to control signals Rx\_EN, SQ\_EN.

- 2. Applies to status signal Rx\_SD. Internal pull-up to V<sub>CC</sub>.

- 3. With status output sink current max 2 mA.

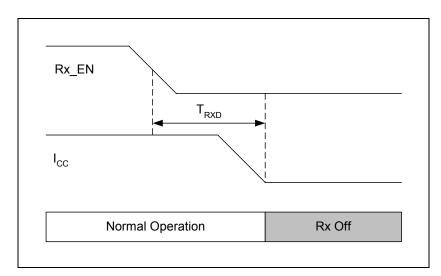

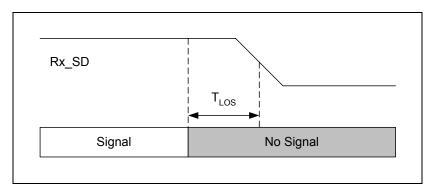

#### **Receiver Status Timing Diagrams**

The following figures show the timing relationships of the status and control signals of the receive section.

Figure 7 - Receiver Enable Signal Timing Diagram

Figure 8 - Receiver Signal Detect Timing Diagram

## **Transceiver Module Signals**

The pluggable parallel optical transceiver uses a 100 position FCI MegArray electrical connector (FCI PN: 84513-101), and an industry standard MTP™(MPO) optical receptacle compliant with IEC 61754-7.

|    | K                   | J                   | Н                   | G                  | F                  | E                  | D                  | С                  | В                  | Α                  |

|----|---------------------|---------------------|---------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| 1  | DOUT00-             | V <sub>EE</sub> Rx  | DOUT03+             | V <sub>EE</sub> Rx | V <sub>EE</sub> Rx | V <sub>EE</sub> Tx | V <sub>EE</sub> Tx | DIN03-             | V <sub>EE</sub> Tx | DIN00+             |

| 2  | DOUT00+             | V <sub>EE</sub> Rx  | DOUT03-             | V <sub>EE</sub> Rx | V <sub>EE</sub> Rx | V <sub>EE</sub> Tx | V <sub>EE</sub> Tx | DIN03+             | V <sub>EE</sub> Tx | DIN00-             |

| 3  | V <sub>EE</sub> Rx  | V <sub>EE</sub> Rx  | V <sub>EE</sub> Rx  | V <sub>EE</sub> Rx | V <sub>EE</sub> Rx | V <sub>EE</sub> Tx |

| 4  | DOUT01+             | V <sub>EE</sub> Rx  | DOUT02-             | NIC                | NIC                | NIC                | NIC                | DIN02+             | V <sub>EE</sub> Tx | DIN01-             |

| 5  | DOUT01-             | V <sub>EE</sub> Rx  | DOUT02+             | NIC                | NIC                | NIC                | NIC                | DIN02-             | V <sub>EE</sub> Tx | DIN01+             |

| 6  | V <sub>EE</sub> Rx  | V <sub>EE</sub> Rx  | V <sub>EE</sub> Rx  | NIC                | NIC                | NIC                | NIC                | V <sub>EE</sub> Tx | V <sub>EE</sub> Tx | V <sub>EE</sub> Tx |

| 7  | V <sub>CCB</sub> Rx | V <sub>CCB</sub> Rx | V <sub>CCB</sub> Rx | NIC                | NIC                | NIC                | NIC                | V <sub>CC</sub> Tx | V <sub>CC</sub> Tx | V <sub>CC</sub> Tx |

| 8  | NIC                 | DNC                 | DNC                 | DNC                | RX_EN              | TX_DIS             | TX_EN              | DNC                | DNC                | DNC                |

| 9  | NIC                 | DNC                 | DNC                 | SD                 | SQ_EN              | RESET              | FAULT              | DNC                | DNC                | DNC                |

| 10 | V <sub>CCA</sub> Rx | V <sub>CCA</sub> Rx | V <sub>EE</sub> Rx  | NIC                | NIC                | NIC                | NIC                | V <sub>EE</sub> Tx | V <sub>CC</sub> Tx | V <sub>CC</sub> Tx |

Table 2 - Transceiver Pinout Assignments (Top view, toward MPO/MTP™ connector end) (10x10 array, 1.27 mm pitch)

| Module front view - MTP key up |                            |     |     |   |   |  |   |     |     |     |     |

|--------------------------------|----------------------------|-----|-----|---|---|--|---|-----|-----|-----|-----|

| Tx0                            | Tx1                        | Tx2 | Tx3 | _ | _ |  | - | Rx3 | Rx2 | Rx1 | Rx0 |

|                                | Host printed circuit board |     |     |   |   |  |   |     |     |     |     |

**Table 3 - Transceiver Optical Channel Assignment**

#### **Transceiver Pin Description**

The transceiver module case is electrically isolated from Transmitter signal common and Receiver signal common. Connection through mounting screw holes or frontplate whichever is applicable. Make the appropriate electrical connection for EMI shield integrity.

| Signal Name         | Туре             | Description                                                                                                                                   | Comments                                                                         |

|---------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| DIN[0:3] +/-        | Data input       | Transmitter data in, channel 0 to 3                                                                                                           | Internal differential termination at 100 $\Omega$ .                              |

| V <sub>CC</sub> Tx  |                  | Transmitter power supply rail                                                                                                                 |                                                                                  |

| V <sub>EE</sub> Tx  |                  | Transmitter signal common. All transmitter voltages are referenced to this potential unless otherwise stated.                                 | Directly connect these pads to the PC board transmitter signal ground plane.     |

| TX_EN               | Control<br>input | Transmitter enable. HIGH: normal operation LOW: disable transmitter                                                                           | Active high, internal pull-up.<br>See Table 1.                                   |

| TX_DIS              | Control<br>input | Transmitter disable. HIGH: disable transmitter LOW: normal operation                                                                          | Active high, internal pull-down. See Table 1.                                    |

| FAULT               | Status<br>output | Transmitter fault. HIGH: normal operation LOW: laser fault detected on at least one channel                                                   | When active, all channels are disabled. Clear by reset signal. Internal pull-up. |

| RESET               | Control<br>input | Transmitter reset. HIGH: normal operation LOW:reset to clear fault signal                                                                     | Internal pull-up.                                                                |

| DOUT[0:3] +/-       | Data output      | Receiver data out, channel 0 to 3.                                                                                                            |                                                                                  |

| V <sub>CCA</sub> Rx |                  | PIN preamplifier power supply rail.                                                                                                           |                                                                                  |

| V <sub>CCB</sub> Rx |                  | Receiver quantizer power supply rail.                                                                                                         |                                                                                  |

| V <sub>EE</sub> Rx  |                  | Receiver signal common. All receiver voltages are referenced to this potential unless otherwise stated.                                       | Directly connect these pads to the PC board receiver signal ground plane.        |

| RX_EN               | Control<br>input | Receiver enable. HIGH: normal operation LOW: disable receiver                                                                                 | Internal pull-up.                                                                |

| RX_SD               | Status<br>output | Receiver signal detect. HIGH: valid optical input on all channels LOW: loss of signal on at least one channel                                 | Internal pull-up.                                                                |

| SQ_EN               | Control<br>input | Squelch enable. HIGH: squelch function enabled. Data OUT is squelched on any channels that have loss of signal LOW: squelch function disabled | Internal pull-up.                                                                |

| DNC                 |                  | Do not connect to any potential, including ground.                                                                                            |                                                                                  |

| NIC                 |                  | No internal connection.                                                                                                                       |                                                                                  |

$V_{CCA}$  and  $V_{CCB}$  Rx can be connected to the same power supply. However, to insure maximum receiver sensitivity and minimize the impact of noise from the power supply, it is recommended to keep the power supplies separate and to use the recommended power supply filtering network on  $V_{CCA}$ Rx, see Figure 2.

#### **Handling Instructions**

#### **Cleaning the Optical Interface**

A protective connector plug is supplied with each module. This plug should remain in place whenever a fiber cable is not inserted. This will keep the optical port free from dust or other contaminants, which may potentially degrade the optical signal. Before reattaching the connector plug to the module, visually inspect the plug and remove any contamination. If the module's optical port becomes contaminated, it can be cleaned with high-pressure nitrogen (the use of fluids, or physical contact, is not advised due to potential for damage).

Before a fiber cable connector is attached to the module, it is recommended to clean the fiber cable connector using an optical connector cleaner, or according to the cable manufacturer's instructions. It is also recommended to clean the optical port of the module with high-pressure nitrogen.

#### **Connectors**

For optimum performance, it is recommended that the number of insertions is limited to 50 for the electrical MegArray connector and 200 for the optical MPO/MTP connector.

#### **ESD Handling**

When handling the modules, precautions for ESD sensitive devices should be taken. These include use of ESD protected work areas with wrist straps, controlled work-benches, floors etc.

#### **Link Reach**

The following table lists the minimum reach distance of the pluggable parallel fiber optic transceiver for different multi-mode fiber (MMF) types and bandwidths based on the Gigabit Ethernet link model version 2.3.5. Each case allows for a maximum of 2 dB per channel connection loss for patch cables and other connectors and assumes worst case on all input parameters.

| Fiber Type           | Modal Bandwidth<br>@ 850 nm | Reach Distance<br>@ 2.5 Gbps | Reach Distance<br>@ 2.7 Gbps | Reach Distance<br>@ 3.125 Gbps |

|----------------------|-----------------------------|------------------------------|------------------------------|--------------------------------|

| [core / cladding μm] | [MHz*km]                    | [m]                          | [m]                          | [m]                            |

| 50/125 MMF           | 400                         | 260                          | 230                          | 80                             |

| 50/125 MMF           | 500                         | 300                          | 270                          | 90                             |

Table 4 - Link Reach for Different Fiber Types and Data Rates

Longer operating distance than the range specified here can be achieved using transmitters, receivers and / or cables meeting specification but performing better than worst case.

#### **Link Model Parameters**

The link reaches above have been calculated using the following link model parameters and Gigabit Ethernet link model version 2.3.5 (filename: 5pmd047.xls).

| Parameter                         | Symbol            | Value | Unit                   |

|-----------------------------------|-------------------|-------|------------------------|

| Mode partition noise k-factor     | k                 | 0.3   |                        |

| Modal noise                       | MN                | 0.3   | dB                     |

| Dispersion slope parameter        | s <sub>o</sub>    | 0.11  | ps/nm <sup>2</sup> *km |

| Wavelength of zero dispersion     | U <sub>O</sub>    | 1320  | nm                     |

| Attenuation coefficient at 850 nm | $\alpha_{\sf dB}$ | 3.5   | dB/km                  |

| Conversion factor                 | C1                | 480   | ns.MHz                 |

| Q-factor [BER 10 <sup>-12</sup> ] | Q                 | 7.04  |                        |

| TP4 eye opening                   |                   | 0.3   | UI                     |

| DCD allocation at TP3             | DCD DJ            | 0.08  | UI                     |

| RMS baseline wander S.D.          | $\sigma_{BLW}$    | 0.025 |                        |

| RIN coefficient                   | k <sub>RIN</sub>  | 0.70  |                        |

| Conversion factor                 | c_rx              | 329   | ns.MHz                 |

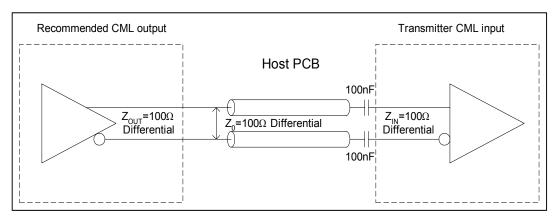

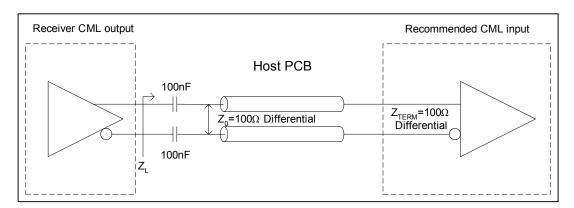

## **Electrical Interface - Application Examples**

Figure 9 - Recommended Differential CML Input Interface

Figure 10 - Recommended Differential CML Output Interface

#### **Trademarks**

Infiniband is a registered trademark of the InfiniBand Trade Association.

MTP is a registered trademark of US Conec Ltd.

The MegArray is a registered trademark of FCI.

# For more information about all Zarlink products visit our Web Site at www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE