MC33883

55 VOLTS

# Advance Information Full Bridge Pre-Driver

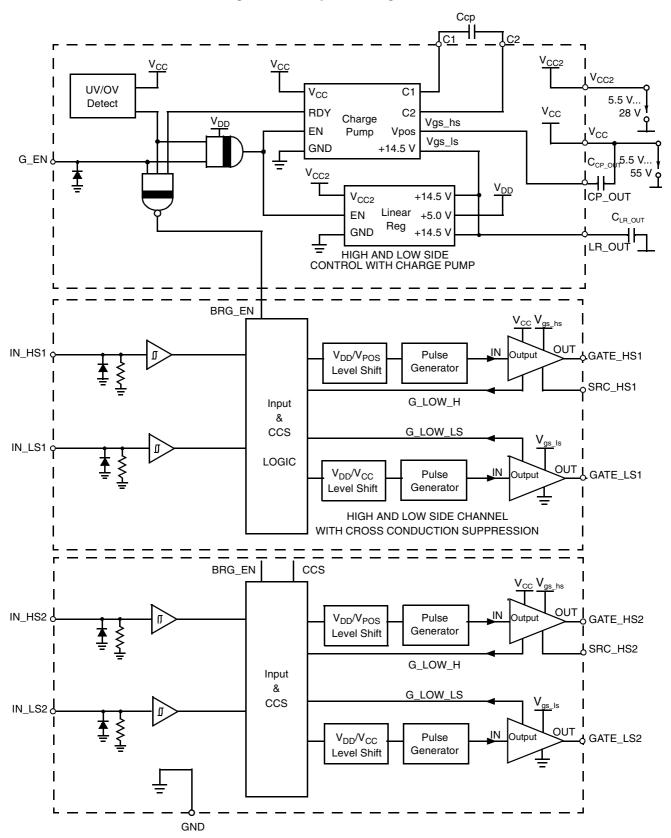

The MC33883 is a full bridge pre-driver including integrated charge pump, two independent high and low side driver channels.

The drive outputs are capable to source and sink 1 A pulse peak current. The low side channel is referenced to ground, the high side channel is floating above ground.

A linear regulator provides a maximum of 16.5V to supply the low side gate driver stages. The high side driver stages are supplied with a  $10V_{typical}$  charge pump voltage. Such built-in feature, associated to external capacitor provides a full floating high side drive.

An under- and over-voltage protection prevents erratic system operation at abnormal supply voltages. Under fault, these functions force the driver stages into off state.

The logic inputs are compatible with standard CMOS or LSTTL outputs. The input hysteresis makes the output switching time independent of the input transition time.

The global enable logic signal can be used to disable the charge pump and all the bias circuit. The net advantage is the reduction of the quiescent supply current to under  $10\mu A$ . To wake up the circuit, 5 V has to be provided at G\_EN.

- +  $V_{CC}$  Operating Voltage Range from 5.5 V up to 55 V

- V<sub>CC2</sub> Operating Voltage Range from 5.5 V up to 28 V

- Automotive Temperature Range -40°C to 125°C

- 1A Pulse Current Output Driver

- Fast PWM Capability

- Built-In Charge Pump

SEMICONDUCTOR **TECHNICAL DATA DW SUFFIX** PLASTIC PACKAGE CASE 751D-05 **PIN CONNECTIONS** (TOP VIEW) CASE 751D-05 20 **G\_EN** Vcc 1  $\cap$ C2 19 SRC\_HS<sub>2</sub> CP\_OUT 18 GATE\_HS2 SRC\_HS1 17 IN\_HS<sub>2</sub> GATE\_HS<sub>1</sub> 5 16 IN\_LS<sub>2</sub> 15 GATE\_LS<sub>2</sub> IN\_HS<sub>1</sub> 6

IN\_LS₁

GATE\_LS<sub>1</sub> 8

GND1 9

LR\_OUT 10

| ORDERING INFORMATION |                      |         |  |  |  |

|----------------------|----------------------|---------|--|--|--|

| Device               | Temperature<br>Range | Package |  |  |  |

| PC33883DW            | -40°C to +125°C      | SOIC20  |  |  |  |

This document contains information on a new product. Specifications and information herein are subject to change without notice.

14 GND2

V<sub>CC2</sub>

13 C1 12 GND\_A

11

# **DEVICE DESCRIPTION**

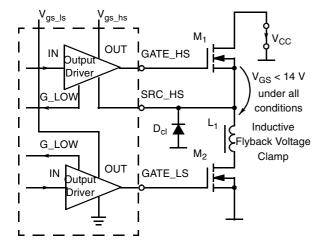

## **Figure 1: Principal Building Blocks**

ABSOLUTE MAXIMUM RATINGS: Absolute Maximum Ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to GND

| Rating                                                                                       | Symbol                                         | Min  | Max                 | Unit |

|----------------------------------------------------------------------------------------------|------------------------------------------------|------|---------------------|------|

| Supply Voltage1                                                                              | V <sub>CC</sub>                                | -0.3 | 65                  | V    |

| Supply Voltage2 (NOTE 1)                                                                     | V <sub>CC2</sub>                               | -0.3 | 35                  | V    |

| Linear Regulator Output Voltage                                                              | V <sub>LR_out</sub>                            | -0.3 | 18                  | V    |

| High Side Floating Supply Absolute Voltage                                                   | V <sub>CP_OUT</sub>                            | -0.3 | 65                  | V    |

| High Side Floating Source Voltage                                                            | V <sub>SRC_HS</sub>                            | -0.3 | 65                  | V    |

| High Side Source Current from Cpout in Switch On State                                       | ۱ <sub>S</sub>                                 |      | 250                 | mA   |

| High Side Gate Voltage                                                                       | V <sub>GATE_HS</sub>                           | -0.3 | 65                  | V    |

| High Side Gate Source Voltage                                                                | V <sub>GATE_HS</sub><br>- V <sub>SRC_HS</sub>  | -0.3 | 20                  | V    |

| High Side Floating Supply Gate Voltage                                                       | V <sub>CP_OUT</sub><br>- V <sub>GATE_</sub> HS | -0.3 | 65                  | V    |

| Low Side Output Voltage                                                                      | V <sub>GATE_LS</sub>                           | -0.3 | 17                  | V    |

| Wake up Voltage                                                                              | $V_{G_{EN}}$                                   | -0.3 | 35                  | V    |

| Logic Input Voltage                                                                          | V <sub>IN</sub>                                | -0.3 | 10                  | V    |

| Charge Pump Capacitor Voltage                                                                | V <sub>C1</sub>                                | -0.3 | V <sub>LR_OUT</sub> | V    |

| Charge Pump Capacitor Voltage                                                                | V <sub>C2</sub>                                | -0.3 | 65                  | V    |

| ESD Voltage on all Pins except the case of (Pin C2 respect to PinVcc) (HBM, 100pF, 1.5kOhms) | V <sub>ESD</sub>                               | -2.0 | 2.0                 | KV   |

| ESD Voltage (PinC2 respect to Pin Vcc)                                                       | V <sub>ESD2</sub>                              | -1.7 | 1.7                 | KV   |

| Power Dissipation and Thermal Characteristics                                                |                                                |      |                     |      |

| Maximum Power Dissipation@25°C                                                               | P <sub>D</sub>                                 |      | 1.25                | W    |

| Thermal Resistance Junction-to-Air                                                           | $R_{	extsf{	heta}JA}$                          |      | 100                 | °C/W |

| Operating Junction Temperature                                                               | ТJ                                             | -40  | +150                | °C   |

| Storage Temperature                                                                          | T <sub>stg</sub>                               | -65  | +150                | °C   |

**OPERATING CONDITIONS:** Typical values for  $T_A = 25^{\circ}$ C, Min/Max values for  $T_A = -40^{\circ}$ C to  $+125^{\circ}$ C

| Rating                                     | Symbol              | Min                | Мах                       | Unit |

|--------------------------------------------|---------------------|--------------------|---------------------------|------|

| Supply Voltage1                            | V <sub>CC</sub>     | 5.5                | 55                        | V    |

| Supply Voltage2                            | V <sub>CC2</sub>    | 5.5                | 28                        | V    |

| High Side Floating Supply Absolute Voltage | V <sub>CP_OUT</sub> | V <sub>CC</sub> +4 | V <sub>CC</sub> +11but<65 | V    |

NOTE1: VCC can sustain load dump pulse 40V, 400ms, 20hms

$\begin{array}{l} \textbf{STATIC ELECTRICAL CHARACTERISTICS} \\ \textbf{V}_{CC} = 12 \ \textbf{V}, \ \textbf{V}_{CC2} = 12 \ \textbf{V}, \ \textbf{C}_{CP} = 33 \ \textbf{nF}, \ \textbf{G}\_EN = 4.5 \ \textbf{V} \ \textbf{unless otherwise specified}. \\ \textbf{Typical values for TA} = 25^{\circ}\text{C}, \ \textbf{Min/Max values for TA} = -40^{\circ}\text{C} \ \textbf{to} + 125^{\circ}\text{C}, \ \textbf{unless otherwise specified}. \end{array}$

| Characteristics                                                                                                      | Pin #        | Symbol              | Min                       | Тур | Max              | Unit |

|----------------------------------------------------------------------------------------------------------------------|--------------|---------------------|---------------------------|-----|------------------|------|

| LOGIC SECTION                                                                                                        |              |                     |                           |     |                  |      |

| Logic "1" Input Voltage (IN_LS & IN_HS)                                                                              | 6, 7, 16, 17 | V <sub>IH</sub>     | 2.0                       |     | 10               | V    |

| Logic "0" Input Voltage (IN_LS & IN_HS)                                                                              |              | V <sub>IL</sub>     |                           |     | 0.8              | V    |

| Logic "1" Input Current Vin=5V                                                                                       | 6, 7, 16, 17 | I <sub>in+</sub>    | 200                       |     | 1000             | uA   |

| Logic "0" Input Current Vin=0V                                                                                       |              | l <sub>in-</sub>    | 200                       |     | 1000             | uA   |

| Wake Up Input Voltage (G_EN)                                                                                         | 27           | V <sub>G_EN</sub>   | 4.5                       | 5.0 | V <sub>CC2</sub> | V    |

| Wake Up Current (G_EN) $V_{G_{EN}} = 14 V$                                                                           | 27           | I <sub>G_EN</sub>   |                           | 200 | 500              | uA   |

| Wake Up Current (G_EN) $V_{G_{EN}} = 28V$                                                                            | 27           | I <sub>G_EN2</sub>  |                           |     | 1.5              | mA   |

| LINEAR REGULATOR SECTION                                                                                             |              | I                   |                           |     |                  |      |

| Linear Regulator $V_{LR\_OUT} @ V_{CC2}$ from 15.0 to 28 V, $I_{LOAD}$ from 0mA to 20mA                              | 10           | V <sub>LR_OUT</sub> | 12.5                      |     | 16.5             | V    |

| Linear Regulator<br>V <sub>LR_OUT</sub> @ I <sub>LOAD</sub> = 20mA                                                   | 10           | V <sub>LR_OUT</sub> | V <sub>CC2</sub> -<br>1.5 |     |                  | V    |

| $V_{LR\_OUT}$ @I_LOAD =20mA, $V_{CC2}$ =5.5V, $V_{CC}$ = 5.5V                                                        | 10           |                     | 4.0                       |     |                  | V    |

| CHARGE PUMP SECTION                                                                                                  |              |                     |                           |     |                  |      |

| Charge Pump Output Voltage, referenced to $V_{CC}$<br>$V_{CC}$ =12V<br>$I_{LOAD}$ = 0mA, $C_{Cpout}$ =1uF            | 3            | V <sub>CP_OUT</sub> | 7.5                       |     |                  | V    |

| Charge Pump Output Voltage, referenced to $V_{CC}$<br>$V_{CC}$ =12V<br>$I_{LOAD}$ = 7mA, $C_{Cpout}$ =1uF            | 3            | V <sub>CP_OUT</sub> | 7.0                       |     |                  | V    |

| Charge Pump Output Voltage, referenced to $V_{CC}$<br>$V_{CC2} = V_{CC} = 5.5V$<br>$I_{LOAD} = 0mA, C_{Cpout} = 1uF$ | 3            | V <sub>CP_OUT</sub> | 2.3                       |     |                  | V    |

| Charge Pump Output Voltage, referenced to $V_{CC}$<br>$V_{CC2} = V_{CC} = 5.5V$<br>$I_{LOAD} = 7mA, C_{Cpout} = 1uF$ | 3            | V <sub>CP_OUT</sub> | 1.8                       |     |                  | V    |

| Charge Pump Output Voltage, referenced to $V_{CC}$<br>$V_{CC}$ =55V<br>$I_{LOAD}$ = 0mA, $C_{Cpout}$ =1uF            | 3            | V <sub>CP_OUT</sub> | 7.5                       |     |                  | V    |

| Charge Pump Output Voltage, referenced to $V_{CC}$<br>$V_{CC}$ =55V<br>$I_{LOAD}$ = 7mA, $C_{Cpout}$ =1uF            | 3            | V <sub>CP_OUT</sub> | 7.0                       |     |                  | V    |

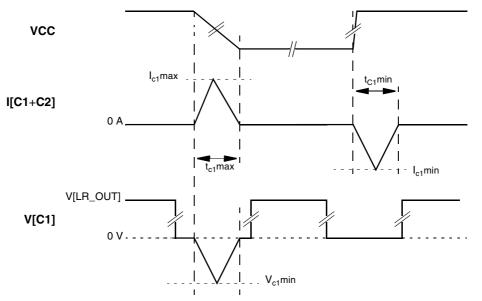

| Peak current through pin C1 under rapid changing $V_{cc}$ voltages (see Figure 5)                                    | 13           | I <sub>C1</sub>     | -2.0                      |     | 2.0              | A    |

| Minimum peak voltage at pinC1 under rapid changing V <sub>cc</sub> voltages (see Figure 5)                           | 13           | V <sub>C1</sub> min | -1.5                      |     |                  | V    |

| Characteristics                                                                                                                                                          | Pin #           | Symbol             | Min  | Тур        | Max     | Unit     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|------|------------|---------|----------|

| SUPPLY VOLTAGE SECTION                                                                                                                                                   | 11              |                    |      |            |         |          |

| Quiescent Vcc Supply Current<br>V <sub>G_EN</sub> =0V @Vcc=12V                                                                                                           | 1               |                    |      |            | 10      | uA       |

| Quiescent Vcc Supply Current<br>V <sub>G_EN</sub> =0V @Vcc=55V                                                                                                           | 1               |                    |      |            | 10      | uA       |

| Operating Vcc Supply Current<br>(@ $V_{CC}$ =55V and $V_{CC2}$ =28V)<br>(@ $V_{CC}$ =12V and $V_{CC2}$ =12V)<br>Logic imput pin inactive (high impedance)                | 1<br>1          |                    |      | 2.2<br>0.7 |         | mA<br>mA |

| Additional Operating Vcc Supply Current for EACH logic input pin active $@V_{CC}=55V$ and $V_{CC2}=28V$ . (Note1)                                                        | 1               |                    |      |            | 5       | mA       |

| Quiescent Vcc2 Supply Current $V_{G_EN}=0V$<br>@ Vcc2 = 12V                                                                                                              | 11              |                    |      |            | 5       | uA       |

| Quiescent Vcc2 Supply Current V <sub>G_EN</sub> =0V<br>@ Vcc2 = 28V                                                                                                      | 11              |                    |      |            | 5       | uA       |

| Operating Vcc2 Supply Current<br>(@ $V_{CC}$ =55V and V <sub>CC2</sub> =28V)<br>(@ $V_{CC}$ =12V and V <sub>CC2</sub> =12V)<br>Logic input pin inactive (high impedance) | 11<br>11        |                    |      |            | 10<br>9 | mA<br>mA |

| Additional Operating Vcc2 Supply Current for EACH logic input pin active $@V_{CC}=55V$ and $V_{CC2}=28V$ . (Note1)                                                       | 11              |                    |      |            | 5       | mA       |

| Under Voltage Shutdown V <sub>CC2</sub> (Note2)                                                                                                                          | 11              | UV2                | 4.0  | 5.0        | 5.5     | V        |

| Under Voltage Shutdown V <sub>CC</sub>                                                                                                                                   | 1               | UV                 | 4.0  | 5.0        | 5.5     | V        |

| Over Voltage Shutdown V <sub>CC</sub>                                                                                                                                    | 1               | OV                 | 57   | 61         | 65      | V        |

| Over Voltage Shutdown V <sub>CC2</sub>                                                                                                                                   | 11              | OV2                | 29.5 | 31         | 35      | V        |

| OUTPUT SECTION                                                                                                                                                           | 11              |                    |      | I          | I       |          |

| Output Sink Resistance (Turned off) $V_{GATE_HS} - V_{SRC_HS} = 1V$                                                                                                      | 3, 4, 5, 8, 15, | R <sub>DS</sub>    |      |            | 22.0    | Ohms     |

| Output Source Resistance (Turned on) $V_{CP_OUT} - V_{GATE_HS} = 0.1V$                                                                                                   | 18, 19          | R <sub>DS</sub>    |      |            | 22.0    | Ohms     |

| High Side Source Current from CPOUT in Switch<br>On State                                                                                                                | 4, 19           | I <sub>S</sub> max |      |            | 200     | mA       |

| Max Voltage (V <sub>GATE_HS</sub> - V <sub>SRC_HS)</sub> ,<br>INH=1, I <sub>Smax</sub> =5mA                                                                              | 4, 5, 18, 19    |                    |      |            | 18      | V        |

Note 1:Large duty cycles of the logic inputs will result in a large power dissipation within the device, that possibly could surpass the package power handling rating. Note2: Between 4.0V and 5.5V, the device can exhibt a non erroneous behaviour.

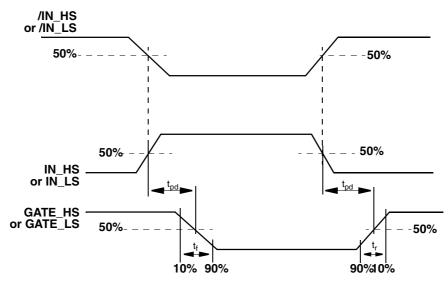

**DYNAMIC ELECTRICAL CHARACTERISTICS:**   $V_{CC} = 12 \text{ V}, V_{CC2} = 12 \text{ V}, C_{CP} = 33 \text{ nF}, G_EN = 4.5 \text{ V}$  unless otherwise specified. Typical values for TA = 25°C, Min/Max values for TA = -40°C to +125°C, unless otherwise specified

| Characteristics                                                                                       | Pin #                         | Symbol          | Min | Тур | Max | Unit |

|-------------------------------------------------------------------------------------------------------|-------------------------------|-----------------|-----|-----|-----|------|

| Prop. Delay HS and LS, C <sub>load</sub> =5nF;<br>Between 50% Input to 50% Output ( see<br>Figure 2:) | 5, 6, 7, 8, 15,<br>16, 17, 18 | t <sub>PD</sub> |     | 200 | 300 | ns   |

| Turn On Rise Time, C <sub>load</sub> =5nF ;<br>10% to 90% (NOTE 3) ( see Figure 2:)                   |                               | t <sub>r</sub>  |     | 80  | 180 | ns   |

| Turn Off Fall Time, C <sub>load</sub> =5nF ;<br>10% to 90% (NOTE 3) (seeFigure 2:)                    | 5, 8, 15, 18                  | t <sub>f</sub>  |     | 80  | 180 | ns   |

NOTE 1: Characterization only

NOTE 2: Input overdrive 1V

NOTE 3: Rise time is given by time needed to charge the gate from 1V to 10V (Vice versa for fall time)

NOTE : Cload corresponds to a capacitor between GATE\_HS and SRC\_HS for the high side and between GATE\_LS and ground for low side.

# **Figure 2: Dynamic Characteristics**

#### **DEVICE DESCRIPTION**

#### **Driver Characteristics**

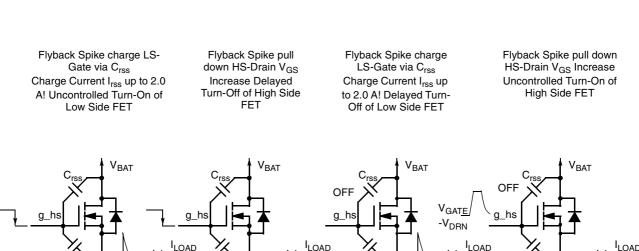

#### Turn-On:

For turn-on the current required to charge the gate source capacitor  $C_{iss}$  in the specified time can be calculated as follows: Peak Current for Rise/Fall Time (tr) and a typical PowerMos-FET Gate Charge  $\mathsf{Q}_g$

$I_P = Q_q/tr = 80nC/80 \text{ ns} \approx 1.0 \text{ A}$

#### Turn-Off:

The peak current for turn-off can be obtained in the same way as for turn-on. In addition to the dynamically current, required to turn-off or turn-on the FET, various application related switching scenarios have to be considered: The output driver sources a peak current of up to 1A for 200ns to turn on the gate. After 200ns, 100mA is provided continuously to maintain the gate charged.

The output driver sinks a peak current of up to 1A for 200ns to turn off the gate.

After 200ns, 100mA are sinked continuously to maintain the gate discharged.

In order to withstand high dV/dt spikes a low resistive path between gate and source is implemented during the off state.

Figure 3:

Driver Requirement: Low Resistive Gate-Source Path during OFF-State Driver Requirement: Low Resistive Gate Source Path during OFF-State. High Peak Sink Current Capab. Driver Requirement: High Peak Sink Current Capab. Driver Requirement: Low Resistive Gate-Source Path during OFF-State

# **Driver Supply**

The High Side(HS) Driver is supplied from the internal charge pump buffered at CP\_OUT.

The low-drop regulator provides approx. 4mA ( $f_{PWM} = 50KHz$ ) per HS gate. In case of the full bridge that means approximately 16mA, 8.0 mA for the high side and 8.0 mA for the low side.

(Note: The average current required to switch a gate with a frequency of 100KHz is:

Average Current (Charge Pump) for PWM Frq. (f<sub>PWM</sub>)

$I_{CP} = Q_g^* f_{PWM} = 80nC^*100 \text{ kHz} = 8.0\text{mA}$

A full bridge application switch only one high side and one low side at the same time.)

External capacitors on Charge Pump and on Linear Regulator are necessary to supply high peak current absorbed during switching. The Low Side Driver is supplied from built in low drop regulator.

# **Gate Protection**

The low side gate is protected by the internal linear regulator, which guarantees that  $V_{GATE\_LS}$  does not exceed the maximum  $V_{GS}$ . Especially when working with the charge pump the voltage at POS\_HS can be up to 65V. The high side gate is clamped internally, in order to avoid a  $V_{GS}$  exceeding 18V.

The Gate protection does not include a Flyback Voltage Clamp that protects the driver and the external FET from a Flyback voltage that can appear when driving inductive load.This Flyback voltage can reach high negative voltage values and needs to be clamped externally.

# Figure 4: Gate Protection & Flyback Voltage Clamp

# **TMOS Failure Protection**

All output driver stages are protected against TMOS failure conditions. If one of the external power FETs is destroyed

(Gate =  $V_{CC}$ , or Gate = Gnd) the function of the remaining output driver stages is not affected. All output drivers are short circuit protected against short circuits to ground.

#### Logic Inputs

Logic Input Voltage Range: Absolute Max : -0.3V ... 10V Wake Up Function: (G\_EN) 4.5V ... V<sub>CC2</sub>

During Wake-Up the logic is supplied from the G\_EN pin.

### Low Drop Linear Regulator

The low drop linear regulator provides the 5.0V for the logic section of the driver, the V<sub>gs\_ls</sub> buffered at LR\_OUT and the +14.5V for the charge pump, which generates the V<sub>gs\_hs</sub>.

The low drop linear regulator provides 4.0mA average current per driver stage. If typically V<sub>CC2</sub> exceeds 15.0V the output is limited to  $14.5V_{tvp}$ .

# **Charge Pump**

The charge pump generates the high side driver supply voltage (V<sub>GS HS</sub>), buffered at CP\_OUT.

$$V_{gs\_hs} = V_{CC} + V_{LR\_OUT} - 2V.$$

The average output current is  $I_{CP}$  = 4.0 mA (f\_{PWM} = 50 KHz) per output driver.

The charge pump charges an external storage capacitor, which provides the peak switching current to the high side output drivers.

**N.B.** In some applications a large dV/dt at Pin C2 due to sudden changes at  $V_{CC}$  can cause a large peak currents flowing through Pin C1.

Positive transitions at Pin C2 ;mimimum peak current :  $I_{c1}min = 2.0A$

$t_{c1}min = 600ns$  (see Figure 5:for peak description)

Negative transitions at Pin C2; maximum peak current :  $I_{c1}max = 2.0A$

t<sub>c1</sub>max = 600ns (see Figure 5 for peak description)

Current sourced by Pin C1 during a large dV/dt will result in a negative voltage at Pin 13; negative transitions at Pin C2; minimum peak voltage:  $V_{c1}min = -1.5V$

$t_{c1}$ max = 600ns (see Figure 5:for peak description)

#### **DEVICE DESCRIPTION**

Figure 5: Limits of C1 Current & Voltage with Large Values dV/dt of Vcc

#### **Over / Under Voltage Shutdown**

The under voltage protection becomes active at V<sub>CC</sub> below 5.5 V and the overvoltage protection is activated at V<sub>CC</sub> above 55 V or at V<sub>CC2</sub> above 28 V.

If the O/UV protection is activated the outputs are driven low, in order to switch off the FETs.

#### Protection

A protection against double battery and load dump spikes up to 55 V is given by V\_{CC} = 55 V.

A protection against reverse polarity is given by the external power FET with the free wheeling diodes, forming a conducting pass from ground to  $V_{CC}$ . An additional protection is not provided within the circuit.

There is a temperature shut down protection per each half bridge. It protects the circuitry against temperature damage by blocking the output drives.

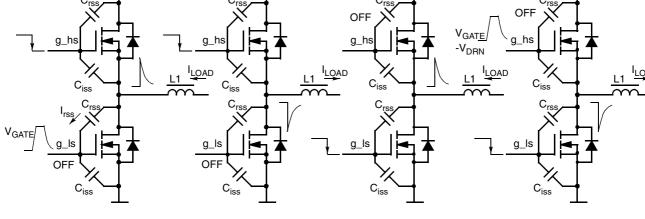

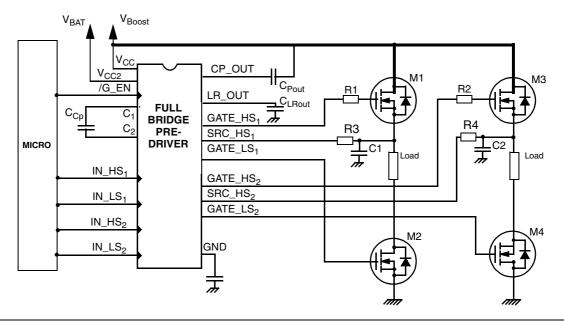

Both applications use the internal charge pump to provide the high side floating voltage. This voltage can be provided by an external source also.

The following figure shows a typical application.

It is worth noting that the supplies VBAT and Vboost may be independent, with different voltage values.

In the case of rapidly changing Vboost voltages, the large dv/dt may result in perturbations of the High Side driver such that the driver is forced into an OFF state. The addition of capaitors C1 & C2 reduces the dv/dt of the source line, consequently reducing driver perturbation.

# Figure 6: Block Diagram

| Pin | Symbol           | Pin Description           |  |  |

|-----|------------------|---------------------------|--|--|

| 1   | V <sub>CC</sub>  | Supply 1                  |  |  |

| 2   | C2               | Charge Pump Capacitor     |  |  |

| 3   | CP_OUT           | Charge Pump Out           |  |  |

| 4   | SRC_HS1          | Source 1 Output High Side |  |  |

| 5   | GATE_HS1         | Gate 1 Output High Side   |  |  |

| 6   | IN_HS1           | Pos. Input High Side 1    |  |  |

| 7   | IN_LS1           | Pos. Input High Side 1    |  |  |

| 8   | GATE_LS1         | Gate 1 Output Low Side    |  |  |

| 9   | GND1             | Ground                    |  |  |

| 10  | LR_OUT           | Linear Regulator Output   |  |  |

| 11  | V <sub>CC2</sub> | Supply 2                  |  |  |

| 12  | GND_A            | Analog Ground             |  |  |

| 13  | C1               | Charge Pump Capacitor     |  |  |

| 14  | GND2             | Ground 2                  |  |  |

| 15  | GATE_LS2         | Gate 2 Output Low Side    |  |  |

| 16  | IN_LS2           | Pos. Input Low Side 2     |  |  |

| 17  | IN_HS2           | Pos. Input High Side 2    |  |  |

| 18  | GATE_HS2         | Gate 2 Output High Side   |  |  |

| 19  | SRC_HS2          | Source 2 Output High Side |  |  |

| 20  | G_EN             | Global Enable             |  |  |

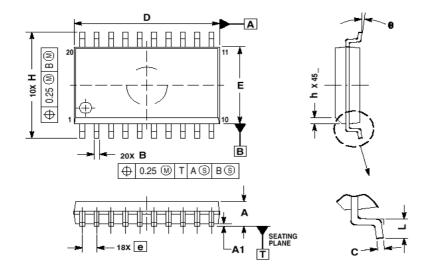

#### **Package Description**

NOTES

1. 2.

DIMENSIONS ARE IN MILLIMETERS. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994. DIMENSIONS D AND E DO NOT INCLUDE MOLD 3

DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSION. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE. DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF B DIMENSION AT MAXIMUM MATERIAL CONDITION. 5.

|     | MILLIMETERS |       |  |  |  |  |

|-----|-------------|-------|--|--|--|--|

| DIM | MIN         | MAX   |  |  |  |  |

| Α   | 2.35        | 2.65  |  |  |  |  |

| A1  | 0.10        | 0.25  |  |  |  |  |

| В   | 0.35        | 0.49  |  |  |  |  |

| С   | 0.23        | 0.32  |  |  |  |  |

| D   | 12.65       | 12.95 |  |  |  |  |

| Е   | 7.40        | 7.60  |  |  |  |  |

| е   | 1.27        | BSC   |  |  |  |  |

| н   | 10.05       | 10.55 |  |  |  |  |

| h   | 0.25        | 0.75  |  |  |  |  |

| L   | 0.50        | 0.90  |  |  |  |  |

| 9   | 0           | 7     |  |  |  |  |

CASE 751D-05 **ISSUE F**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer applications customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any application in which the failure of the Abotorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unitended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or un authorized use, even if

such claim alleges that Motorola was negligent regarding the design or manufacture of the parts. Motorola and (🕅) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Employment Opportunity/Affirmative Action Employer.

How to reach us:

USA / EUROPE / Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1-303-675-2140 or 1-800-441-2447

Technical Information Center: 1-800-521-6274

HOME PAGE: http://www.motorola.com/semiconductors

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center, 3-20-1, Minami-Azabu, Minato-ku, Tokyo 106-8573 Japan. 81-3-344-3569

ASIA / PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2, Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. 852-26668334