### **Features**

- · Seamless integration with your Synopsys Design Compiler and FPGA Compiler tools

- Powerful VHDL or Verilog design entry

- DesignWare™ library support

- Supports the FLASH370i™ family of CPLDs

- · Industry-leading synthesis for programmable logic

- 100% automatic fitting

- VHDL and Verilog post-layout timing models

- · Complete solution from design entry to programming

#### Introduction

Cypress offers powerful integrated solutions for programmable logic. The Cypress Synopsys Bolt-in Kit gives you everything to design with Cypress's UltraLogic CPLDs in one seamless device-independent design environment. It allows you to take advantage of VHDL or Verilog design entry, Synopsys' powerful Design Compiler™ or FPGA Compiler™ synthesis tools, and Cypress's industry-leading Warp™ fitting tool, and a wide variety of simulators.

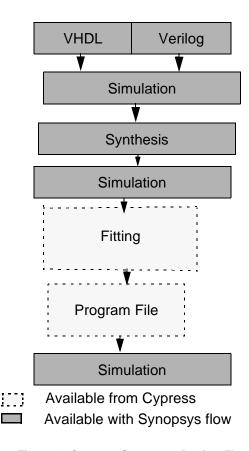

## **Functional Description**

#### **Design Entry and Pre-Synthesis Simulation**

Design with ease using VHDL or Verilog, and verify your functionality prior to synthesis in the Synopsys flow.

### **Synthesis**

Synthesize your design using Design Compiler or FPGA Comiler for any Cypress CPLD. Utilize Cypress DesignWare and Technology libraries.

## **Post-Synthesis Simulation**

Simulate your design prior to fitting within your Synopsys flow.

### **Fitting**

Easily retarget your design to different devices. The technology mapping and 100% automatic fitting tools in Warp produce optimal results in minutes.

# **Post-Fitting Simulation**

Warp outputs VHDL and Verilog timing simulation models. Verify your design with timing using your choice of Synopsys' VSS™ simulator or any other VHDL or Verilog simulator.

#### **Programming**

Warp generates JEDEC programming files for Cypress devices which can be used for in-system reprogramming (ISR™) or with various device programmers.

# Cypress Synopsys Bolt-in Kit

## **System Requirements**

#### For Sun Workstations

SPARC CPU SunOS™ 4.1.x or Solaris™ 2.5.x CD-ROM drive

#### For HP 9000 workstation (700 series)

**HP-UX™** 10.x CD-ROM drive

## **Ordering Information**

CY3146 Cypress Synopsys Bolt-in Kit includes:

CD-ROM with Bolt-in software and on-line documentation CD-ROM with Warp software and on-line documentation Warp User's Guide and Reference Manual Release Notes

VHDL for Programmable Logic Textbook

Figure 1. Cypress Synopsys Design Flow

Document #: 38-00432-B

HP-UX is a trademark of Hewlett Packard Corporation. SunOS and Solaris are trademarks of Sun Microsystems Corporation. Design Compiler, DesignWare, FPGA Compiler, and VSS are trademarks of SynopsysCorporation ISR, FLASH370i, UltraLogic, and Warp are trademarks of Cypress Semiconductor Corporation

### **Features**

- · Seamless integration with your Synopsys Design Compiler and FPGA Compiler tools

- Powerful VHDL or Verilog design entry

- DesignWare™ library support

- Supports the FLASH370i™ family of CPLDs

- · Industry-leading synthesis for programmable logic

- 100% automatic fitting

- VHDL and Verilog post-layout timing models

- · Complete solution from design entry to programming

#### Introduction

Cypress offers powerful integrated solutions for programmable logic. The Cypress Synopsys Bolt-in Kit gives you everything to design with Cypress's UltraLogic CPLDs in one seamless device-independent design environment. It allows you to take advantage of VHDL or Verilog design entry, Synopsys' powerful Design Compiler™ or FPGA Compiler™ synthesis tools, and Cypress's industry-leading Warp™ fitting tool, and a wide variety of simulators.

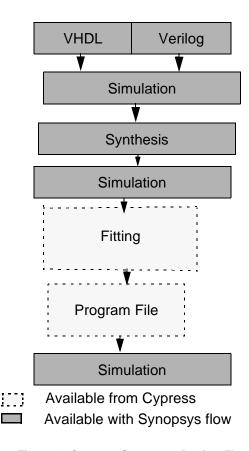

## **Functional Description**

#### **Design Entry and Pre-Synthesis Simulation**

Design with ease using VHDL or Verilog, and verify your functionality prior to synthesis in the Synopsys flow.

### **Synthesis**

Synthesize your design using Design Compiler or FPGA Comiler for any Cypress CPLD. Utilize Cypress DesignWare and Technology libraries.

## **Post-Synthesis Simulation**

Simulate your design prior to fitting within your Synopsys flow.

### **Fitting**

Easily retarget your design to different devices. The technology mapping and 100% automatic fitting tools in Warp produce optimal results in minutes.

# **Post-Fitting Simulation**

Warp outputs VHDL and Verilog timing simulation models. Verify your design with timing using your choice of Synopsys' VSS™ simulator or any other VHDL or Verilog simulator.

#### **Programming**

Warp generates JEDEC programming files for Cypress devices which can be used for in-system reprogramming (ISR™) or with various device programmers.

# Cypress Synopsys Bolt-in Kit

## **System Requirements**

#### For Sun Workstations

SPARC CPU SunOS™ 4.1.x or Solaris™ 2.5.x CD-ROM drive

#### For HP 9000 workstation (700 series)

**HP-UX™** 10.x CD-ROM drive

## **Ordering Information**

CY3146 Cypress Synopsys Bolt-in Kit includes:

CD-ROM with Bolt-in software and on-line documentation CD-ROM with Warp software and on-line documentation Warp User's Guide and Reference Manual Release Notes

VHDL for Programmable Logic Textbook

Figure 1. Cypress Synopsys Design Flow

Document #: 38-00432-B

HP-UX is a trademark of Hewlett Packard Corporation. SunOS and Solaris are trademarks of Sun Microsystems Corporation. Design Compiler, DesignWare, FPGA Compiler, and VSS are trademarks of SynopsysCorporation ISR, FLASH370i, UltraLogic, and Warp are trademarks of Cypress Semiconductor Corporation