## PM4354

## **COMET-QUAD**

# Four Channel Combined T1/E1 Transceiver/Framer

## Programmer's Guide

Proprietary and Confidential

Released

Issue 2: September, 2001

#### **Legal Information**

#### Copyright

© 2001 PMC-Sierra, Inc.

The information is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, you cannot reproduce any part of this document, in any form, without the express written consent of PMC-Sierra, Inc.

PMC-2000151 (R2)

#### **Disclaimer**

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

#### **Trademarks**

COMET-QUAD is a trademark of PMC-Sierra, Inc.

#### **Patents**

The technology discussed is protected by one or more of the following Patents:

US patent 5,973,977

Canadian patent 2,242,152

Relevant patent applications and other patents may also exist.

## **Contacting PMC-Sierra**

PMC-Sierra 8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: +1.604.415.6000 Fax: +1.604.415.6204

Document Information: document@pmc-sierra.com Corporate Information: info@pmc-sierra.com Technical Support: apps@pmc-sierra.com Web Site: <a href="http://www.pmc-sierra.com">http://www.pmc-sierra.com</a>

#### **Revision History**

| Issue No. | Issue Date        | Details of Change                                                                                                        |  |

|-----------|-------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| Issue 1   | April 2000        | Document created.                                                                                                        |  |

| Issue 2   | September<br>2001 | Rewrite initialization section and sample configurations. Also, update document according to latest datasheet (Issue 6). |  |

|           |                   | Add sections to cover programming using the software driver.                                                             |  |

## **Table of Contents**

| Le  | gal Inf | ormation  |                                                               | 2  |

|-----|---------|-----------|---------------------------------------------------------------|----|

| Со  | ntactir | ng PMC-   | Sierra                                                        | 3  |

| Tal | ole of  | Contents  |                                                               | 4  |

| Lis | t of Fi | gures     |                                                               | 8  |

| Lis | t of Ta | bles      |                                                               | 9  |

| 1   | Refe    | erences . |                                                               | 10 |

| 2   | Intro   | duction.  |                                                               | 11 |

|     | 2.1     | Scope.    |                                                               | 11 |

|     | 2.2     | Target /  | Audience                                                      | 11 |

|     | 2.3     | Numbe     | ring Conventions                                              | 11 |

|     | 2.4     | Offset (  | Conventions                                                   | 11 |

|     | 2.5     | Pseudo    | o-Code Conventions                                            | 12 |

| 3   | Reg     | ister Des | scription                                                     | 13 |

|     | 3.1     | Direct F  | Registers                                                     | 13 |

|     | 3.2     | Indirect  | t Registers                                                   | 13 |

| 4   | Prog    | grammin   | g the COMET-QUAD Using register accesses                      | 16 |

|     | 4.1     | Resetti   | ng the COMET-QUAD                                             | 17 |

|     | 4.2     | Configu   | uring the COMET-QUAD                                          | 18 |

|     |         | 4.2.1     | Select T1 or E1 Operation (Common for all four ports)         | 19 |

|     |         | 4.2.2     | Select the Crystal Clock (Common for all four ports)          | 19 |

|     |         | 4.2.3     | Select the Line Encoding                                      | 19 |

|     |         | 4.2.4     | Select the Framing Format                                     | 20 |

|     |         | 4.2.5     | Configure the Transmit Timing                                 | 21 |

|     |         | 4.2.6     | Configure the Receive Timing                                  | 23 |

|     |         | 4.2.7     | Configure the Backplane interfaces                            | 23 |

|     |         | 4.2.8     | Configure the Elastic Stores                                  | 24 |

|     |         | 4.2.9     | Configure the Jitter Attenuators                              | 24 |

|     |         | 4.2.10    | Set the RLPS Voltage Reference value                          | 25 |

|     |         | 4.2.11    | Program the RLPS Equalizer RAM table                          | 25 |

|     |         | 4.2.12    | Enable the RLPS Equalizer                                     | 25 |

|     |         | 4.2.13    | Program the Transmit Pulse Waveform                           | 26 |

|     |         | 4.2.14    | Run the XLPG Initialization Procedure                         | 26 |

|     |         | 4.2.15    | Run the RLPS Optimization routine (Common for all four ports) | 26 |

|    |       | 4.2.16   | Release the tri-states to begin transmission            | 27 |

|----|-------|----------|---------------------------------------------------------|----|

|    | 4.3   | Using    | the Per-Channel Serial Controllers                      | 28 |

|    |       | 4.3.1    | Using RPSC                                              | 28 |

|    |       | 4.3.2    | Using TPSC                                              | 30 |

|    | 4.4   | Using t  | the Signaling Extractor                                 | 32 |

|    |       | 4.4.1    | SIGX Indirect Register Access                           | 33 |

| 5  | Inter | rupts us | sing register access                                    | 35 |

|    | 5.1   | Interru  | pt Status and Interrupt Enable Bits                     | 35 |

|    | 5.2   | Interru  | pt Reference                                            | 36 |

|    | 5.3   | Interru  | pt Processing using register accesses                   | 42 |

| 6  | HDL   | .C Progr | ramming using register access                           | 45 |

|    | 6.1   | Using    | the HDLC Transmitter (TDPR) Block                       | 45 |

|    |       | 6.1.1    | TDPR Initialization                                     | 46 |

|    |       | 6.1.2    | Sending an HDLC Frame in Interrupt Driven Mode          | 47 |

|    |       | 6.1.3    | Sending an HDLC Frame in Polling Mode                   | 48 |

|    | 6.2   | Using t  | the HDLC Receiver (RDLC) Block                          | 50 |

|    |       | 6.2.1    | Initializing the HDLC Receiver                          | 50 |

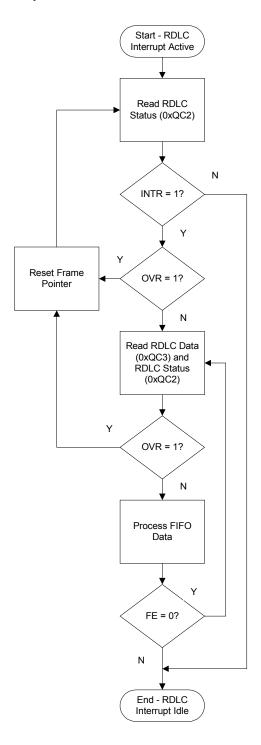

|    |       | 6.2.2    | Processing RDLC Interrupts                              | 51 |

|    |       | 6.2.3    | Receiving HDLC Frames in Polling Mode                   | 52 |

| 7  | Aları | ms usin  | g register access                                       | 53 |

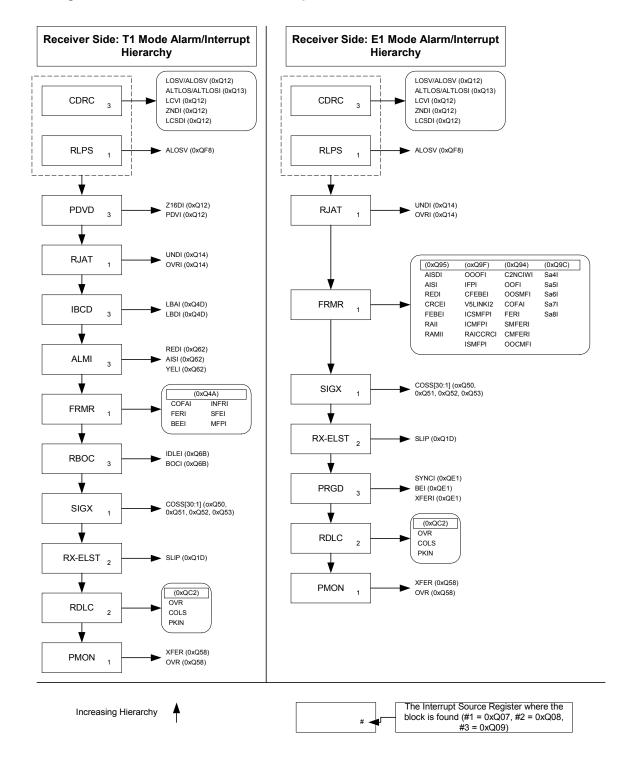

|    | 7.1   | Interru  | pt/Alarm Hierarchy                                      | 53 |

|    | 7.2   | T1 Mo    | de                                                      | 56 |

|    |       | 7.2.1    | T1 Alarm Insertion                                      | 56 |

|    |       | 7.2.2    | T1 Receiver Alarms                                      | 57 |

|    | 7.3   | E1 Mo    | de                                                      | 57 |

|    |       | 7.3.1    | E1 Alarm Insertion                                      | 57 |

|    |       | 7.3.2    | E1 Receiver Alarms                                      | 58 |

| 8  | Prog  | grammin  | ng the Pattern Generator/Detector using register access | 60 |

| 9  | Perf  | ormance  | e Monitoring using register access                      | 61 |

|    | 9.1   | Perforr  | mance Monitoring Counters                               | 61 |

|    | 9.2   | Autom    | atic Performance Monitoring                             | 62 |

| 10 | Diag  | nostics  | using register access                                   | 64 |

| 11 | Sam   | ple Cor  | nfigurations using register access                      | 65 |

|    | 11.1  | T1 Mo    | de                                                      | 65 |

|    | 11 2  | E1 Mo    | do                                                      | 67 |

|     | 11.3                                   | H-MVIF   | P Mode                                                           | 68         |  |  |

|-----|----------------------------------------|----------|------------------------------------------------------------------|------------|--|--|

| 12  | Devi                                   | ce Drive | r Description                                                    | 71         |  |  |

| 13  | Prog                                   | rammin   | g the COMET-QUAD Using the driver                                | 73         |  |  |

|     | 13.1                                   | Resetti  | ng the COMET-QUAD using the driver                               | 73         |  |  |

|     | 13.2                                   | Configu  | uring the COMET-QUAD using the driver                            | 73         |  |  |

|     |                                        | 13.2.1   | Select T1 or E1 Operation using the driver (Common for all four  | r ports)73 |  |  |

|     |                                        | 13.2.2   | Select the Crystal Clock using the driver (Common for all four p | oorts).73  |  |  |

|     |                                        | 13.2.3   | Select the Line Decoding/Encoding using the driver               | 74         |  |  |

|     |                                        | 13.2.4   | Select the Framing Format using the driver                       | 75         |  |  |

|     |                                        | 13.2.5   | Configure the Transmit Timing using the driver                   | 79         |  |  |

|     |                                        | 13.2.6   | Configure the Receive Timing using the driver                    | 79         |  |  |

|     |                                        | 13.2.7   | Configure the Backplane interfaces using the driver              | 79         |  |  |

|     |                                        | 13.2.8   | Configure the Elastic Stores using the driver                    | 83         |  |  |

|     |                                        | 13.2.9   | Configure the Jitter Attenuators using the driver                | 84         |  |  |

|     |                                        | 13.2.10  | Set the RLPS Voltage Reference value using the driver            | 86         |  |  |

|     |                                        | 13.2.11  | Program the RLPS Equalizer RAM table using the driver            | 87         |  |  |

|     |                                        | 13.2.12  | Enable the RLPS Equalizer using the driver                       | 89         |  |  |

|     |                                        | 13.2.13  | Program the Transmit Pulse Waveform using the driver             | 89         |  |  |

|     |                                        | 13.2.14  | Run the XLPG Initialization Procedure using the driver           | 90         |  |  |

|     |                                        | 13.2.15  | Run the RLPS Optimization routine using the driver               | 90         |  |  |

|     |                                        | 13.2.16  | Release the tri-states to begin transmission using the driver    | 91         |  |  |

|     | 13.3                                   | Using t  | he Per-Channel Serial Controllers with the driver                | 91         |  |  |

|     |                                        | 13.3.1   | Using RPSC with the driver                                       | 91         |  |  |

|     |                                        | 13.3.2   | Using TPSC with the driver                                       | 92         |  |  |

|     | 13.4                                   | Using t  | he Signaling Extractor with the driver                           | 94         |  |  |

| 14  | Inter                                  | rupt Pro | cessing using the driver                                         | 96         |  |  |

| 15  | HDL                                    | C Progra | amming using the driver                                          | 97         |  |  |

|     | 15.1                                   | Using t  | he HDLC Transmitter with the driver                              | 97         |  |  |

|     | 15.2                                   | Using t  | he HDLC Receiver with the driver                                 | 100        |  |  |

| 16  | Aları                                  | ns using | the driver                                                       | 103        |  |  |

| 17  | Prog                                   | rammin   | g the Pattern Generator/Detector with the Driver                 | 105        |  |  |

| 18  | Performance Monitoring with the Driver |          |                                                                  |            |  |  |

| 19  | Diag                                   | nostics  | with the Driver                                                  | 111        |  |  |

| 20  | Sam                                    | ple Con  | figuration with the Driver                                       | 113        |  |  |

| Not | -es                                    |          |                                                                  | 129        |  |  |

## **List of Figures**

| Figure 1 | Software State Diagram of the COMET-QUAD                                                        | 17  |

|----------|-------------------------------------------------------------------------------------------------|-----|

| Figure 2 | COMET-QUAD Interrupt Status Register Hierarchy                                                  | 35  |

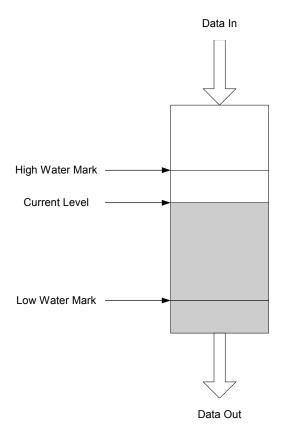

| Figure 3 | TDPR FIFO                                                                                       | 46  |

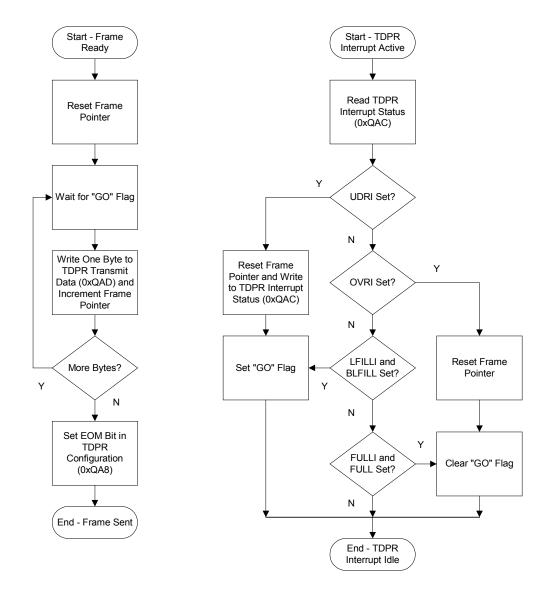

| Figure 4 | HDLC Frame Transmit Routine (left) and TDPR Interrupt Routine (right) for Interrupt Driven Mode | 47  |

| Figure 5 | HDLC Frame Transmit Routine for Polling Mode                                                    | 49  |

| Figure 6 | RDLC Interrupt Routine                                                                          | 51  |

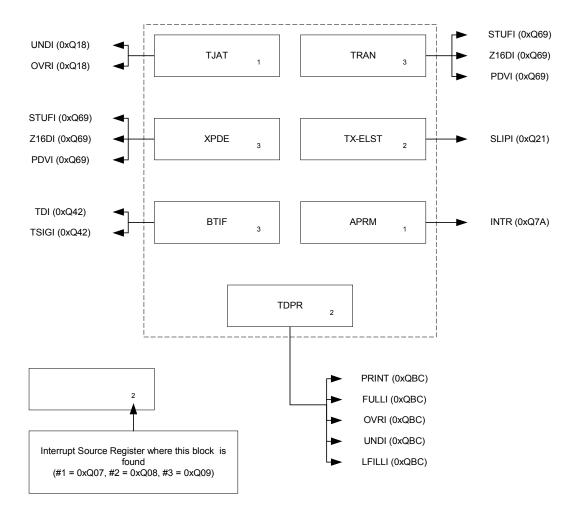

| Figure 7 | Transmitter Alarms and Interrupts                                                               | 54  |

| Figure 8 | Receiver alarms and Interrupts for T1 and E1                                                    | 55  |

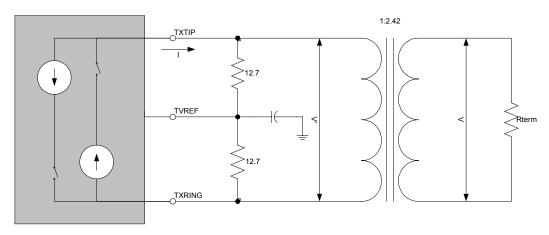

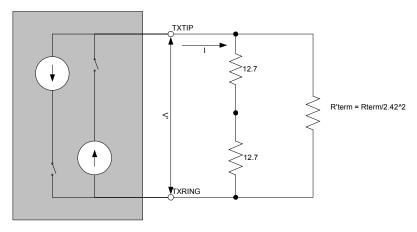

| Figure 9 | The Transmit Circuit of COMET-QUAD (top) and its Norton Equivalent (bottom)                     | 126 |

## **List of Tables**

| Table 1: Location of PCCE and IND Bits                                   | 14   |

|--------------------------------------------------------------------------|------|

| Table 2: Indirect Access Registers                                       | 15   |

| Table 3: XCLK Frequencies                                                | 19   |

| Table 4: T1 Framing Modes                                                | 20   |

| Table 5: E1 Framing Modes                                                | 21   |

| Table 6: Transmit Timing configurations                                  | 22   |

| Table 7: Backplane rates                                                 | 23   |

| Table 8: Relevant Bits for Specifying Period of Frame Pulse              | . 24 |

| Table 9: Jitter Attenuator N1 and N2 values                              | 24   |

| Table 10: Write Sequence for RLPS Optimization Routine                   | 27   |

| Table 11: Control Bits for the PCM Data Control byte                     | 28   |

| Table 12: Control Bits for the PCM Data Control byte                     | 31   |

| Table 13: Interrupt Reference                                            | 36   |

| Table 14: Cases to Ignore Transmitter Interrupts / Alarms                | 53   |

| Table 15: Cases to Ignore Receiver Interrupt / Alarms                    | 53   |

| Table 16: Transmit Alarm Insertion (T1 Mode)                             | . 56 |

| Table 17: Drop Alarm Insertion (T1 Mode)                                 | . 56 |

| Table 18: Receiver Alarms ( T1 Mode )                                    | 57   |

| Table 19: Transmit Alarm Insertion ( E1 mode )                           | 58   |

| Table 20: Drop Alarm Insertion ( E1 mode )                               | 58   |

| Table 21: Receiver Alarms ( E1 mode )                                    | 58   |

| Table 22: PRBS Pattern Select                                            | 60   |

| Table 23 : PMON registers for T1 mode                                    | 61   |

| Table 24: PMON Registers for E1 mode                                     | 62   |

| Table 25: Performance Report Message Structure and Contents              | 62   |

| Table 26: Performance Report Message Structure Notes                     | 63   |

| Table 27: Performance Report Message Contents                            | 63   |

| Table 28: Sample Configuration for T1 ESF mode, with B8ZS line encoding  |      |

| Table 29: Sample Configuration for E1 CRC-MF, with HDB3 line encoding    | 67   |

| Table 30: Sample Configuration for E1 with an H-MVIP backplane interface | 68   |

#### 1 References

- PMC-1990315, PMC-Sierra, Inc., "PM4354 COMET-QUAD Four Channel Combined E1/T1 Transceiver/Framer Data Sheet", May 2001, Issue 6.

- PMC-1970624, PMC-Sierra, Inc., "PM4351 COMET Combined E1/T1 Transceiver Standard Product Data Sheet", July 1999, Issue 8.

- PMC-1990615, PMC-Sierra, Inc., "PM4351 COMET Programmer's GUIDE", December 1999, Issue 3.

#### 2 Introduction

#### 2.1 Scope

This document introduces the reader to the programmable features of the COMET-QUAD by providing the application interface accesses and the corresponding register accesses necessary to configure the COMET-QUAD. The document provides pseudo-code, flow charts, figures and tables necessary to program real-time operation of the COMET-QUAD chip. This document is essentially made up of two parts that mirror each other. The first part gives details on how to program the device using register access, and the second part gives details on how to program the device using the device driver.

The COMET-QUAD Programmer's Guide is a supplement to the COMET-QUAD Data Sheet (PMC-1990315). Due to the large number of configurations the COMET-QUAD can have, it is impossible to cover all configuration aspects of the chip. Please contact a PMC-Sierra Applications Engineer for information not covered in this document.

Although every effort has been taken to ensure the consistency between this document and the COMET-QUAD Data Sheet, some discrepancies may occur. In case of inconsistencies between this document and the COMET-QUAD Data Sheet the information in the data sheet should be considered accurate and take precedence over information provided in this document.

#### 2.2 Target Audience

This document is prepared for engineers that design-in the COMET-QUAD chip and need a quick reference on how to program the COMET-QUAD. Some prior knowledge of T1, E1 and J1 framing technologies, as well as some knowledge of C programming language and computer operation is necessary to fully understand this document.

#### 2.3 Numbering Conventions

The following numbering conventions are used throughout this document:

Binary 1010B, 011

Decimal 129, 6, 12

Hexadecimal 0x1FE2, 09FH

#### 2.4 Offset Conventions

COMET-QUAD has four "quadrants" (ports) with identical characteristics. Each quadrant is equipped with the same set of registers shifted by the offset of 0x100, starting with offset 0x000 for the first quadrant, and ending with offset 0x300 for the fourth quadrant. In this document, the registers are referred to in two ways:

• Explicitly, by stating the register explicit hexadecimal address, and

• Implicitly, by stating the quadrant symbol 'Q' and the hexadecimal address of the corresponding register in the first quadrant.

The following is an example of explicit and implicit register notation:

Explicit 0x211, 0C0HImplicit 0xQ11, QC0H

Explicit notation is used throughout this document to refer to an instance of the register in a particular quadrant, while implicit notation is used to refer to all four register instances in each of the quadrants.

#### 2.5 Pseudo-Code Conventions

The pseudo-code in this document is shown in a C-like syntax. The code segments are not by any means compile-ready and are provided for reader's reference in order to understand a particular procedure or concept. However, the procedures were intended to be a good basis for programming the COMET-QUAD.

## 3 Register Description

Unless otherwise specified, COMET-QUAD registers are shown in this document using the convention **REGISTER\_NAME**(register address).

All register accesses are shown in this document as:

```

READ_REG(<address>);

WRITE REG(<address>, <value>);

```

whereby <address> is the register address from the data sheet and <value> is the data written to a register.

The COMET-QUAD registers have the following characteristics:

- All values written into unused register bits should be written with logic 0 unless otherwise stated, ensuring software compatibility with future versions of the product. Reading back unused bits can produce either logic one or a logic zero; hence, unused register bits should be masked off by software during a register read access.

- Certain register bits are reserved. To ensure that the COMET-QUAD operates as intended, reserved register bits must only be written with their default values unless otherwise stated in the datasheet.

The COMET-QUAD has 2 types of register spaces - the direct registers, which are accessed directly by the microprocessor bus interface of the COMET-QUAD, and the "indirect" registers which are accessed via assigned normal-mode buffer registers.

#### 3.1 Direct Registers

Direct registers configure the operation of the COMET-QUAD. The registers have offsets between 0xQ00 and 0xQFF inclusive. The reader should refer to the COMET-QUAD Data Sheet [ ] for the default values of these registers.

#### 3.2 Indirect Registers

The indirect registers are for per-channel control, which is normally disabled by default, on power-up. The PCCE bit in the corresponding per-channel block must be set to enable per channel control.

The "IND" bit in the corresponding per-channel block must be set before the software can access indirect registers. On power-up or software reset, this bit is clear. See Table 1 for the location of the PCCE and IND bits for each per-channel block.

Table 1: Location of PCCE and IND Bits

| Bits         | Register Number |       |       |  |

|--------------|-----------------|-------|-------|--|

| Dits         | TPSC            | RPSC  | SIGX  |  |

| PCCE and IND | 0xQ6C           | 0xQ70 | 0xQ50 |  |

Once the "IND" bit is set, the indirect registers can be accessed via the address and data buffer registers. The following pseudo code shows how to read from and write to an indirect register. See Table 2 for explanation of pseudo code register names.

```

#define MAX BUSY READ

0x5

#define BIT BUSY

0x80

/** to read an indirect register: **/

int ReadIndirectReg(int offset, unsigned char &value)

int i;

WRITE REG(REG CHANNEL INDIRECT ADDRESS, (offset | 0x80));

for (i = 0; i < MAX BUSY READ; i++)

value = READ REG(REG MICRO ACCESS STATUS);

if ((value & BIT BUSY) == 0)

{

value =

READ REG(REG CHANNEL INDIRECT DATA BUFFER);

return SUCCESS;

}

return FAILURE;

}

/** to write to an indirect register: **/

int WriteIndirectReg(int offset, unsigned char value)

{

unsigned char temp;

int i;

WRITE REG(REG CHANNEL INDIRECT DATA BUFFER, value);

WRITE REG(REG CHANNEL INDIRECT ADDRESS, (offset&0x7F));

for (i = 0; i < MAX BUSY READ; i++)

temp = READ REG(REG MICRO ACCESS STATUS);

```

```

if ((temp & BIT_BUSY) == 0) return SUCCESS;

}

return FAILURE;

}

```

#### **Table 2: Indirect Access Registers**

| Davidou Dafina                   | Register Number |       |       |

|----------------------------------|-----------------|-------|-------|

| Register Define                  | TPSC            | RPSC  | SIGX  |

| REG_MICRO_ACCESS_STATUS          | 0xQ6D           | 0xQ71 | 0xQ51 |

| REG_CHANNEL_INDIRECT_DATA_BUFFER | 0xQ6F           | 0xQ73 | 0xQ53 |

| REG_CHANNEL_INDIRECT_ADDRESS     | 0xQ6E           | 0xQ72 | 0xQ52 |

## 4 Programming the COMET-QUAD Using register accesses

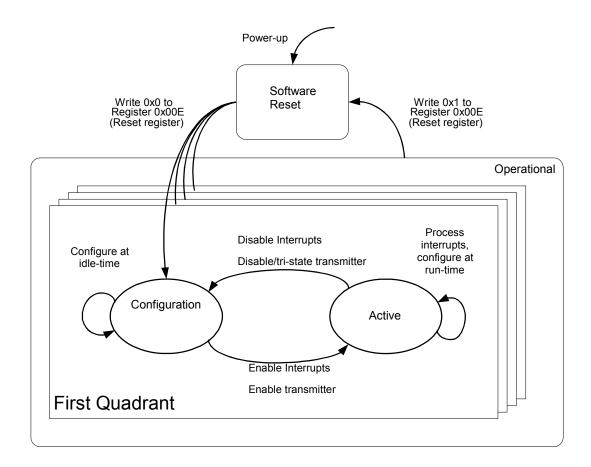

Typically, the software controlling the COMET-QUAD will have a few main software states:

- 1) Software Reset (Global)

- 2) Operational (Global)

- a) Configuration (Per port)

- b) Active (Per port)

Immediately after the COMET-QUAD completes a power-up sequence, the software begins by issuing a software reset. The software reset applies to all four ports, and resets the registers to the default values specified in the datasheet. Note that many of the register bits don't have default values – namely the read-only and unused bits.

As soon as the device is taken out of software reset, it is in an "Operational" state. This means that the device is running, and ready to be programmed to perform a useful function.

Within this "Operational" state are usually two software sub-states:

"Configuration state": Before each port can be do anything useful, the software needs to configure it (through a series of register accesses). Typically when the software is in this state, it will leave the analog transmitter the default high-impedance state to prevent garbage from being transmitted during configuration. In addition, the software will usually leave all interrupts disabled by leaving all the interrupt enable ('E' bits) as their default '0'. This is to ensure that the microprocessor doesn't receive garbage interrupts.

After configuration of each port, the software will typically put the port into use. The software transitions into "Active" state. It first takes the port transmitter out of its high-impedance state to enable transmission and enables the INTB output interrupt pin. Then the software typically begins processing the interrupts and monitoring status.

If during operation, the device needs to be reconfigured, the software can handle this a few ways. The simplest is to make the change "on-the-fly", staying in Active state. This can be done with most small changes. For larger changes, it is generally recommended for the software to transition into Configuration state. This is to take the device "offline", so that it won't generate any garbage or meaningless outputs during the re-configuration. For example, re-programming a different transmit pulse waveform would normally be done in Configuration state.

For significant reconfigurations, such as switching between T1 and E1 modes, the software will usually go through a Software Reset cycle, and re-configure the entire device from scratch. In particular, a software reset cycle is required any time the backplane rates are changed (ie. Changing the value of the RATE[1:0] bits).

A typical software state transition diagram is shown below in Figure 1.

Figure 1 Software State Diagram of the COMET-QUAD

#### 4.1 Resetting the COMET-QUAD

To put the COMET-QUAD in *Reset* state, set the 'RESET' bit in register 0x00E:

WRITE REG(0x00E, 0x01);

The device will remain in a software reset state until the 'RESET' bit is explicitly cleared:

WRITE REG(0x00E, 0x00);

**Note:** A Software Reset should be done only after a valid power-up sequence: When powering up the COMET-QUAD, all the 3.3 V power pins (analog power) should ramp-up before the 2.5 V pins (digital power). During the ramp-up, it is critical that the instantaneous voltage on the 2.5 V pins never exceeds the instantaneous voltage on the 3.3 V pins.

The power ramp-up is considered complete when both the 2.5 V power and 3.3 V power have risen above the minimum input level thresholds specified in section 15 (DC Characteristics) of the COMET-QUAD Datasheet (PMC-1990315). These minimum thresholds are 3.135 V for the 3.3 V power and 2.3 V for the 2.5 V power.

After the ramp-up, there are three things that must be done before the device is operational:

- 1) The RSTB (chip reset) pin must be driven active-low for a minimum of 100 ns

- 2) The CSB (Chip Select) pin must be driven high concurrently with RSTB being driven low at least once in order to clear any internal test modes. (The most common way to accomplish this is to drive CSB high during the chip reset in step 1). Although there is no specified minimum time that CSB & /RSTB need to be driven for, 100 ns provides a safe margin.

- 3) The TRSTB (JTAG reset) must also be driven active-low for a minimum of 100 ns in order to reset the JTAG state machine so that the I/O pins are in their correct operational configuration. This JTAG reset can be performed independently of the above two steps 1) and 2).

#### 4.2 Configuring the COMET-QUAD

To configure the COMET-QUAD for operation, the configuration routine has to implement the following procedure for all quadrants:

- 1. Select T1 or E1 Operation (Common for all four ports)

- 2. Select the Crystal Clock (Common for all four ports)

- 3. Select the Line Encoding

- 4. Select the Framing Format

- 5. Configure the Transmit Timing

- 6. Configure the Receive Timing

- 7. Configure the Backplane interfaces

- 8. Configure the Elastic Stores

- 9. Configure the Jitter Attenuators

- 10. Set the RLPS Voltage Reference value

- 11. Program the RLPS Equalizer RAM table

- 12. Enable the RLPS Equalizer

- 13. Program the Transmit Pulse Waveform

- 14. Run the XLPG Initialization Procedure

- 15. Run the RLPS Optimization routine (Common for all four ports)

- 16. Release the tri-states to begin transmission

The remainder of this section describes how to implement each of the items listed above.

#### 4.2.1 Select T1 or E1 Operation (Common for all four ports)

Select E1 or T1 operation via the 'E1/T1B' in register 0x000 (Global Configuration). This selects E1 or T1 for all four ports.

#### 4.2.2 Select the Crystal Clock (Common for all four ports)

Select the frequency being supplied for crystal clock (XCLK). This is done in the CSU Configuration register (0x0D6). If E1 was chosen in the previous step, then a 2.048MHz crystal must be selected here. If T1, then either a 2.048MHz or 1.544MHz crystal may be chosen.

To select the frequency for XCLK, choose the appropriate value for the MODE[2:0] bits from the table below:

| <b>Table</b> | 3: | <b>XCL</b> | K F | requ | iencies |

|--------------|----|------------|-----|------|---------|

|--------------|----|------------|-----|------|---------|

| MODE[2:0] | XCLK frequency | T1 or E1 |  |

|-----------|----------------|----------|--|

| 000       | 2.048 MHz E1   |          |  |

| 001       | 1.544 MHz      | T1       |  |

| 01X       | Reserved       | Reserved |  |

| 10X       | Reserved       | Reserved |  |

| 110       | Reserved       | Reserved |  |

| 111       | 2.048 MHz      | T1       |  |

Note that the setting here applies to all four ports.

#### 4.2.3 Select the Line Encoding

If T1 mode has been selected above, the line encoding can be either AMI or B8ZS. For the receive path, the line-encoding is selected with the 'AMI' bit in register 0xQ10 (CDRC Configuration). For the transmit path, it is selected with the 'B8ZS' bit in register 0xQ54 (T1-XBAS Configuration).

If in E1 mode, the line encoding can be AMI or HDB3. For the receive path, the line-encoding is selected with the 'AMI' bit in register 0xQ10 (CDRC Configuration), just as in T1 mode. For the transmit path, the line-encoding is selected with the 'AMI' bit in register 0xQ80 (E1-TRAN Configuration).

#### 4.2.4 Select the Framing Format

In T1 mode, the T1-XBAS inserts framing bits into the transmit direction (outgoing stream), while the T1-FRMR locates framing bits in the receive direction (incoming stream). Because the T1-FRMR block is not capable of detecting alarms, there is an additional block in the receive path, T1-ALMI, that is used to perform all T1 alarm detection.

The T1-XBAS, T1-FRMR, and T1-ALMI are configurable for all T1 framing formats: SF, ESF, T1DM and SLC96. The relevant registers are:

- 0xQ54 (T1-XBAS Configuration)

- 0xQ48 (T1-FRMR Configuration)

- 0xQ60 (T1-ALMI Configuration)

Each of these registers contain the bits ESF and FMS[1:0] which specify the framing format according to the following table:

**Table 4: T1 Framing Modes**

| ESF | FMS1 | FMS0 | Mode             |  |

|-----|------|------|------------------|--|

| 0   | 0    | 0    | SF               |  |

| 0   | 0    | 1    | T1DM             |  |

| 0   | 1    | 0    | SLC96            |  |

| 0   | 1    | 1    | "alternate" T1DM |  |

| 1   | 0    | 0    | ESF              |  |

| 1   | 0    | 1    | Reserved         |  |

| 1   | 1    | 0    | Reserved         |  |

| 1   | 1    | 1    | Reserved         |  |

There is one additional register in T1 mode where the framing format needs to be specified. The SIGX block, which extracts the CAS signaling bits in the receive direction, has an 'ESF' bit in register 0xQ50. This bit must be set to '1' for ESF framing format, and set to '0' for all other T1 framing formats (SF, SLC-96, T1DM).

In E1 mode, the E1-TRAN inserts framing bytes (timeslot 0) into the outgoing stream, while the E1-FRMR locates framing bytes in the incoming stream. The E1-FRMR also detects E1 alarms.

At minimum, the E1 structure contains Basic Framing, which E1-TRAN and E1-FRMR automatically support. The Basic Framing pattern is carried in every odd framing byte (called the FAS, or "Frame Alignment Signal" bytes). In addition to Basic Framing, the E1 format optionally provides CRC Multiframing and Signaling multiframing.

To enable the optional CRC Multiframing, set GENCRC='1' in register 0xQ80 (E1-TRAN Configuration) and CRCEN='1' in register 0xQ90 (E1-FRMR Configuration). The GENCRC bit enables the E1-TRAN to insert the CRC Multiframe pattern in the transmit stream, while the CRCEN bit enables the E1-FRMR to detect the CRC Multiframe pattern in the receive stream. The CRC Multiframe pattern comprises of a MFAS (Multiframe Alignment Signal) pattern, '001011', carried in the first bit of all even framing bytes, as well as CRC-4 computational bytes carried in the first bit of all odd framing bytes.

To enable the optional Signaling Multiframing, set SIGEN=DLEN='1' in register 0xQ80, and write CASDIS='0' in register 0xQ90. The SIGEN and DLEN bits will enable insertion of CAS (Channel Associated Signaling) – and hence Signaling Multiframing — into timeslot 16 in the outgoing stream. The CASDIS bit controls whether Signaling Multiframe is to be detected in the receive stream.

The table below summarizes the possible settings for E1 operation:

**Table 5: E1 Framing Modes**

|                                                         | Transmit<br>(E1-TRAN Configuration,<br>0xQ80) |            | Receive (E1-FRMR Configuration 0xQ90) |        |

|---------------------------------------------------------|-----------------------------------------------|------------|---------------------------------------|--------|

|                                                         | GENCRC                                        | DLEN=SIGEN | CRCEN                                 | CASDIS |

| Basic<br>Framing                                        | 0                                             | 0          | 0                                     | 1      |

| Basic<br>Framing +<br>CRC<br>Multiframe                 | 1                                             | 0          | 1                                     | 1      |

| Basic<br>Framing +<br>Signaling<br>Multiframe           | 0                                             | 1          | 0                                     | 0      |

| Basic Framing + CRC Multiframe and Signaling Multiframe | 1                                             | 1          | 1                                     | 0      |

#### 4.2.5 Configure the Transmit Timing

Configuring the timing of the transmit path involves specifying three things:

- a) Source of the transmit timing. In general, there are three possible sources: (a) the backplane, either BTCLK or CMV8MCLK in H-MVIP mode (b) the Backplane datarate), (b) the external CTCLK pin (c) receive recovered clock (also called "looptiming").

- b) Whether TJAT (Transmit Jitter Attenuator) is used.

c) Whether the transmit backplane (BTIF) is operating as Clock Master or Clock Slave.

The table below summarizes all the possible configurations. (It is based on the "Transmit Timing Options" table in the datasheet under the register description for 0xQ06):

**Table 6: Transmit Timing configurations**

|                                                                                                    | PLLREF[1:0]<br>(Reg 0xQ06) | OCLKSEL[1:0]<br>(Reg 0xQ06) | TXELSTB<br>YP<br>(Reg<br>0xQ06) | LINELB<br>(Reg<br>0xQ06) | CMODE<br>(0x40 BTIF<br>Config) |

|----------------------------------------------------------------------------------------------------|----------------------------|-----------------------------|---------------------------------|--------------------------|--------------------------------|

| Transmit timing configuration: Source of Transmit Timing TJAT or No TJAT Backplane Master or Slave |                            |                             |                                 |                          |                                |

| Backplane With TJAT Backplane Slave                                                                | ,0X,                       | ,00,                        | 1                               | 0                        | 1                              |

| Recovered clock With TJAT Backplane Master                                                         | '10'                       | ,00,                        | 1                               | 0                        | 0                              |

| Recovered clock With TJAT Backplane Slave                                                          | '10'                       | ,00,                        | 0                               | 0                        | 1                              |

| CTCLK With TJAT Backplane Master                                                                   | '11'                       | ,00,                        | 1                               | 0                        | 0                              |

| CTCLK With TJAT Backplane Slave                                                                    | '11'                       | ,00,                        | 0                               | 0                        | 1                              |

| Backplane No TJAT Backplane Slave                                                                  | ,00,                       | '1X'                        | 1                               | 0                        | 1                              |

| CTCLK No TJAT Backplane Master                                                                     | '11'                       | '01'                        | 1                               | 0                        | 0                              |

| CTCLK  No TJAT  Backplane Slave                                                                    | '11'                       | '01'                        | 0                               | 0                        | 1                              |

| Lineloopback                                                                                       | 'X0'                       | '00'                        | X                               | 1                        |                                |

#### 4.2.6 Configure the Receive Timing

Configuring the timing of the receive path involves specifying two things:

- (a) Whether the receive backplane (BRIF) is a clock master or slave. This is controlled by the 'CMODE' bit in register 0xQ30. In addition, the receive elastic store (RX-ELST) needs to be enabled or disabled via the 'RXELSTBYP' bit in register 0xQ02. It must be enabled anytime the backplane clock or frame pulse is a slave. In otherwords, the RX-ELST is required anytime the backplane timing differs from the line-side timing in terms of rate (clock) and/or alignment (frame pulse).

- (b) Whether RJAT (Receive Jitter Attenuator) is used. This is controlled by the 'RJATBYP' bit in register 0xQ02.

#### 4.2.7 Configure the Backplane interfaces

Configure the interface timing of the backplanes. This is controlled in the BRIF registers (0xQ30 and 0xQ31) and the BTIF Configuration register (0xQ40 and 0xQ41). In the previous two steps, the clock master or clock slave has already been specified. However, further details need to be specified, including: backplane data rate, frame pulse master or slave, frame pulse type, clock edges, and so on. Both the BRIF and BTIF contain the following bits:

RATE[1:0]: Selects the data rate of the backplane. The table below shows the setting for all available data rates. If the clock master mode was selected in the previous steps, then here you must select a backplane data rate equal the line-rate (ie. 1.544Mbit/s for T1 and 2.048Mbit/s for E1). The higher backplane rates (where the data is gapped) are supported only in clock slave mode.

Table 7: Backplane rates

| RATE[1:0]   | Backplane Rate                 |

|-------------|--------------------------------|

| ,00,        | 1.544 Mbit/s (T1 only)         |

| '01'        | 2.048 Mbit/s (T1 or E1)        |

| '10'        | Reserved                       |

| <b>'11'</b> | 8.192 Mbit/s H-MVIP (T1 or E1) |

NX64KBIT/S[1:0]: Selects the bandwidth of data that is transferred through the backplane interfaces. A setting of '00', for "Full Frame" mode, means that the entire T1 or E1 structure will pass through the backplane.

DE: Specifies which clock edge the data (PCM and signaling) are updated or sampled on.

FE: Specifies which clock edge the frame pulse is updated or sampled on.

CMS: In clock slave mode, setting this bit allows the clock to run twice as fast as the data. The BRIF or BTIF will divide the clock by 2, ensuring the internal clock and data rate are the same.

FPMODE: Specifies whether the frame pulse is master (output) or slave (input).

In addition, you may need to specify the period of the frame pulse. The relevant bits to specify this differ between BRIF and BTIF, and also depend on whether you are in T1 or E1 mode, as well as on whether you are in frame pulse master or slave mode. The table below shows the relevant bits for each mode:

Table 8: Relevant Bits for Specifying Period of Frame Pulse

| Backplane | Frame-pulse Master or Slave | Relevant Bits                                                                                                                                                                    |

|-----------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BRIF      | Frame-pulse Master          | In E1: ROHM, BRXSMFP/BRXCMFP                                                                                                                                                     |

|           |                             | In T1: BRXSMFP                                                                                                                                                                   |

|           | Frame-pulse Slave           | N/A.                                                                                                                                                                             |

|           |                             | When the receive backplane is configured as frame pulse slave, it accepts only a basic-frame pulse, not any multi-frame pulse. Therefore, there is no need to select the period. |

| BTIF      | Frame-pulse Master          | In E1: FPTYP                                                                                                                                                                     |

|           |                             | In T1: FPTYP, ESF_EN                                                                                                                                                             |

|           | Frame-pulse Slave           | In E1: FPTYP                                                                                                                                                                     |

|           |                             | In T1: FPTYP, ESF_EN                                                                                                                                                             |

#### 4.2.8 Configure the Elastic Stores

Both Elastic Stores need to be configured to T1 mode or E1 mode. This is done via the 'IR' and 'OR' bits (in registers 0xQ20 for TX-ELST, and 0xQ1C for RX-ELST). For T1, set IR=OR=0. For E1, set IR=OR=1.

#### 4.2.9 Configure the Jitter Attenuators

Both jitter-attenuators (RJAT and TJAT) need to be configured. Each have an N1/N2 divisor value that needs to be programmed for its internal PLL to function correctly. For RJAT, set N1=N2= 0x2F for T1, or N1=N2= 0xFF for E1. For TJAT, please refer to the table in the datasheet (under the register description for 0xQ1A). For your convenience, a simplified version of the table is copied below:

Table 9: Jitter Attenuator N1 and N2 values

| Transmit clock reference                             | T1 or E1 mode | N1   | N2   |

|------------------------------------------------------|---------------|------|------|

| 1.544MHz (from<br>Backplane, Recovered,<br>or CTCLK) | T1            | 0x2F | 0x2F |

| 2.048MHz (from<br>Backplane, Recovered,              | E1            | 0xFF | 0xFF |

| or CTCLK)                                      |    |      |      |

|------------------------------------------------|----|------|------|

| 2.048MHz (from CTCLK)                          | T1 | 0xFF | 0xC0 |

| 1.544MHz (from CTCLK)                          | E1 | 0xC0 | 0xFF |

| Nominal 1.544MHz<br>(Backplane H-MVIP<br>mode) | T1 | 0xC0 | 0xC0 |

| 8kHz (CTCLK)                                   | T1 | 0x00 | 0xC0 |

| 16kHz (CTCLK)                                  | T1 | 0x01 | 0xC0 |

| 8kHz (CTCLK)                                   | E1 | 0x00 | 0xFF |

| 16kHz (CTCLK)                                  | E1 | 0x01 | 0xFF |

Note: Even if the TJATs are not used, they still must be fully configured, because they are used to generate high-speed clocks used internally by the XLPG analog transmitters.

#### 4.2.10 Set the RLPS Voltage Reference value

The RLPS (the analog receiver) requires an equalizer voltage reference value to be programmed into the 'EQ\_VREF[5:0]' bits in registers 0xQDC. For T1, use the value 0x2C. For E1, use the value 0x3D.

#### 4.2.11 Program the RLPS Equalizer RAM table

Program the Receive Equalizer RAM table into the RLPS Indirect Registers. This table must be programmed in order to recover analog pulses. This table consists of 256 rows, with each row consisting of 4 bytes. A total of 256 indirect writes are necessary to program the entire table.

A single indirect write is done as follows:

- (1) Wait at least 3 line-rate cycle to ensure that previous indirect accesses are complete.

- (2) Write the four data bytes into the four "data" registers: 0xQD8, 0xQD9, 0xQDA, and 0xQDB.

- (3) Set the 'RWB' bit (Read Write select) in register 0xQFD to 0 to select a write operation.

- (4) Write the Indirect Address into register 0xQFC (the "address" register). This initiates the indirect write, which will take one line-rate cycle to complete. The values for the Indirect Address will range from 0x00 to 0xFF, representing the 256 rows of the Equalizer RAM table.

#### 4.2.12 Enable the RLPS Equalizer

Enable the Receive Equalizer by setting the 'EQEN' bit in registers 0xQFF to '1'. This will enable the equalizer by activating the feedback loop. The equalizer will begin to move up and down the Equalizer RAM table according to changes in the incoming signal level.

#### 4.2.13 Program the Transmit Pulse Waveform

Program the Transmit Pulse Waveform. Each pulse waveform provided in the datasheet includes a Transmit Waveform table, which is programmed into Indirect Registers and controls the *shape* of the pulse, as well as a SCALE[4:0] value (register 0xQF0) which controls the *amplitude* of the pulse. When writing a SCALE[4:0] value into the register 0xQF0, it is usually recommended to leave the HIGHZ bit as '1' (in the same register), so that the transmitter remains in high-impedance during the remainder of the configuration. This avoids garbage from being transmitted during configuration.

Programming the Transmit Waveform table consists of 24 rows and 5 columns. Therefore, there are a total of 24x5 = 120 indirect writes are necessary to program the entire table. Each Indirect write is done as follows:

- (1) Wait one line-rate cycle to ensure that previous indirect accesses are complete.

- (2) Write the data byte into the "data" register (0xQF3)

- (3) Write the Indirect Address into the "address" register (0xQF2). This will initiate the Indirect write. The Indirect Address is comprised of the SAMPLE[4:0] bits, which index the 24 rows of the table, and the UI[2:0] bits, which index the 5 columns of the table. Therefore, valid values for the SAMPLE index range from '00000' to '10111', and valid values for the UI index range from '000' to '100'

#### 4.2.14 Run the XLPG Initialization Procedure

Run the XLPG Initialization procedure outlined in the Datasheet (PMC-1990315). This procedure must be run for each quadrant after device reset. Its purpose is to compensate for variations in fabrication of the XLPG analog drivers. If it isn't done, the transmit pulse waveform may vary in amplitude over time. The XLPG Initialization procedure is as follows:

- (1) Write 06H to register 0xQF6 (XLPG Initialization register)

- (2) Write 00H to register 0xQF4 (XLPG Configuration #1 register)

- (3) Write 00H to register 0xQF5 (XLPG Configuration #2 register)

- (4) Write 00H to register 0xQF6

After the sequence has been completed, the XLPG Initialization register bits must remain at logic 0 until the next time the COMET-QUAD is reset.

#### 4.2.15 Run the RLPS Optimization routine (Common for all four ports)

Run the RLPS Optimization routine. This is a sequence of 29 writes, which is provided in the datasheet in the Operation section, under "Using the Line Receiver". For convenience, the sequence is copied in the table below. This routine needs to be run only once, after configuring all four ports.

**Table 10: Write Sequence for RLPS Optimization Routine**

| Step | Address    | Data |  |  |  |

|------|------------|------|--|--|--|

| 1    | 0x4D7      | 0x00 |  |  |  |

| 2    | 0x4F1      | 0x00 |  |  |  |

| 3    | 0x5F1      | 0x00 |  |  |  |

| 4    | 0x6F1      | 0x00 |  |  |  |

| 5    | 0x7F1      | 0x00 |  |  |  |

| 6    | 0x4F9      | 0x00 |  |  |  |

| 7    | 0x5F9      | 0x00 |  |  |  |

| 8    | 0x6F9      | 0x00 |  |  |  |

| 9    | 0x7F9      | 0x00 |  |  |  |

| 10   | 0x4F9      | 0x04 |  |  |  |

| 11   | 0x4FB      | 0x09 |  |  |  |

| 12   | 0x00B      | 0x20 |  |  |  |

| 13   | Wait 1 ms  |      |  |  |  |

| 14   | 0x4F9      | 0x00 |  |  |  |

| 15   | 0x00B      | 0x00 |  |  |  |

| 16   | 0x5F9      | 0x04 |  |  |  |

| 17   | 0x5FB      | 0x09 |  |  |  |

| 18   | 0x00B      | 0x20 |  |  |  |

| 19   | Wait 1 ms  |      |  |  |  |

| 20   | 0x5F9      | 0x00 |  |  |  |

| 21   | 0x00B      | 0x00 |  |  |  |

| 22   | 0x6F9      | 0x04 |  |  |  |

| 23   | 0x6FB      | 0x09 |  |  |  |

| 24   | 0x00B      | 0x20 |  |  |  |

| 25   | Wait 1 ms  |      |  |  |  |

| 26   | 0x6F9      | 0x00 |  |  |  |

| 27   | 0x00B      | 0x00 |  |  |  |

| 28   | 0x7F9      | 0x04 |  |  |  |

| 29   | 0x7FB      | 0x09 |  |  |  |

| 30   | 0x00B      | 0x20 |  |  |  |

| 31   | Wait 1 ms  |      |  |  |  |

| 32   | 0x7F9 0x00 |      |  |  |  |

| 33   | 0x00B      | 0x00 |  |  |  |

#### 4.2.16 Release the tri-states to begin transmission

After the device is fully configured, one can begin transmission of T1 or E1 signals. This is done by clearing the HIGHZ bits in register 0xQF0 (XLPG Line Driver Configuration register).

#### 4.3 Using the Per-Channel Serial Controllers

The Per-Channel Serial Controllers (TPSC and RPSC) control the per-channel functions for the transmit and receive PCM data.

The software should configure the TPSC and RPSC while in *Idle* state. The following steps should be followed in order:

- 1) Disable the PCCE bit and Enable the IND bit in the register 0xQ6C (TPSC Configuration) or register 0xQ70 (RPSC Configuration).

- 2) Program the required TPSC (or RPSC) configuration.

- 3) Enable the PCCE bit in the registers 0xQ6C (TPSC) or 0xQ70 (RPSC).

The following sections discuss step 2.

#### 4.3.1 Using RPSC

On power up, the per-channel control is normally disabled by default. Once the RPSC is configured, the PCCE bit in register 0xQ70 must be set to activate per channel control.

The RPSC Indirect Registers (PCM Data Control byte (0x20-0x3F), Data Trunk Conditioning Code byte (0x40-0x5F), and Signaling Trunk Conditioning byte (0x61-0x7F)) are accessible on a per-channel basis. Table 11 provides a summary of some of the control bits (in the RPSC Indirect Registers 20H-3FH: PCM Data Control byte) that must be programmed to configure the channels.

Table 11: Control Bits for the PCM Data Control byte

| Bit                                                                                                 |                                                                                           | Resulting Action                                                                                            |

|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| TEST                                                                                                | 0                                                                                         | No test features applied.                                                                                   |

| 1                                                                                                   |                                                                                           | Depending on the value of the RXPATGEN bit of the PRBS Positioning/Control (0xQ0F), performs the tests:     |

|                                                                                                     |                                                                                           | 0: Channel data is checked against the PRBS test pattern.                                                   |

|                                                                                                     |                                                                                           | 1: Channel data is overwritten with the PRBS test pattern.                                                  |

| DTRKC                                                                                               | 0                                                                                         | No data trunk conditioning applied                                                                          |

|                                                                                                     | 1                                                                                         | BRPCM output data is replaced with content of Data Trunk Conditioning Code Byte (0x40-0x5F) for the channel |

| STRKC 0                                                                                             |                                                                                           | No signaling trunk conditioning applied                                                                     |

|                                                                                                     | 1 BRSIG output data is replaced with content of Signaling Tru (0x61-0x7F) for the channel |                                                                                                             |

| DMW                                                                                                 | 0                                                                                         | No digital milliwatt pattern replaces BRPCM output data                                                     |

| 1 BRPCM output data is replaced with a digital milliwatt pattern (base DMWALAW bit) for the channel |                                                                                           | BRPCM output data is replaced with a digital milliwatt pattern (based on the DMWALAW bit) for the channel   |

| DMWALAW 0                                                                                           |                                                                                           | Only applicable if DMW = 1. Digital milliwatt pattern used is the digital A-law pattern                     |

|                                                                                                     |                                                                                           | Only applicable if DMW = 1. Digital milliwatt pattern used is the µ-law pattern                             |

| Bit     |   | Resulting Action                                                              |

|---------|---|-------------------------------------------------------------------------------|

| SIGNINV | 0 | No action                                                                     |

|         | 1 | Most Significant Bit of data output on BRPCM pin is inverted for the channel. |

#### Notes:

- 1. RPSC indirect registers have no default values after the COMET-QUAD is reset; therefore, values must be programmed in for the desired configuration.

- 2. If a channels DTRKC and/or STRKC bit(s) is/are set, then values must be set in the corresponding Conditioning Code Byte. If none are set, default values will be sent.

#### **RPSC Indirect Register Access**

The RPSC indirect registers are for the per-channel control of the receive serial data stream. On power-up, the per-channel control is normally disabled by default. The PCCE bit in register 0xQ70 must be set to enable per channel control.

The "IND" bit must be set before the software can access RPSC indirect registers. On power-up or software reset, this bit is clear by default. Once the "IND" bit is set, the following pseudo code shows how to read a RPSC indirect register and how to write to a RPSC indirect register.

```

#define REG RPSC INDIRECT ADDRESS

0xQ72

#define REG RPSC MICRO ACCESS STATUS

0xQ71

#define REG RPSC INDIRECT DATA

0xQ73

#define MAX BUSY READ

0x5

#define BIT BUSY

0x80

/** to read a RPSC register: **/

int ReadRpsc(int offset, unsigned char &value)

int i;

WRITE REG(REG RPSC INDIRECT ADDRESS, (offset | 0x80));

for (i = 0; i < MAX BUSY READ; i++)

value = READ REG(REG RPSC MICRO ACCESS STATUS);

if ((value & BIT BUSY) == 0)

value = READ REG(REG RPSC INDIRECT DATA);

return SUCCESS;

}

return FAILURE;

}

/** to write a RPSC register: **/

int WriteRpsc(int offset, unsigned char value)

```

```

{

unsigned char temp;

int i;

WRITE_REG(REG_RPSC_INDIRECT_DATA, value);

WRITE_REG(REG_RPSC_INDIRECT_ADDRESS, (offset & 0x7F));

for (i = 0; i < MAX_BUSY_READ; i++)

{

temp = READ_REG(REG_RPSC_MICRO_ACCESS_STATUS);

if ((temp & BIT_BUSY) == 0) return SUCCESS;

}

return FAILURE;

}</pre>

```

#### 4.3.2 Using TPSC

The TPSC indirect registers provide per-channel serial control over the transmit data stream. The per-channel control is normally disabled by default, on power-up. The PCCE bit in register 0xQ6C must be set to activate per channel control once the RPSC is configured.

On power up, the per-channel control is normally disabled by default. Once the TPSC is configured, the PCCE bit must be set to activate per channel control. See section 0 for accessing the TPSC indirect registers.

The TPSC Indirect Registers (PCM Data Control byte (0x20-0x3F), IDLE Code byte (0x40-0x5F) and Signaling/E1 Control byte (0x60-0x7F)) are accessible on a per-channel basis.

The PCM Data Control byte provides control over how to condition the data received on the BTPCM pin, as shown in Table 12.

| Table 12: Control Bits for the | <b>PCM Data Control byte</b> |

|--------------------------------|------------------------------|

|--------------------------------|------------------------------|

| Bit       |    | Resulting Action                                                                                        |  |  |

|-----------|----|---------------------------------------------------------------------------------------------------------|--|--|

| INVERT    | 0  | PCM data of this channel is not inverted.                                                               |  |  |

|           | 1  | PCM data for this channel is inverted.                                                                  |  |  |

| IDLE_CHAN | 0  | PCM data of this channel is not overwritten with idle code                                              |  |  |

|           | 1  | Idle code overwrites PCM data for this channel                                                          |  |  |

| DMW       | 0  | PCM channel data is not replaced with digital mW pattern.                                               |  |  |

|           | 1  | Digital mW pattern replaces channel PCM data.                                                           |  |  |

| TEST      | 0  | No test features applied.                                                                               |  |  |

|           | 1  | Depending on the value of the RXPATGEN bit of the PRBS Positioning/Control (0xQ0F), performs the tests: |  |  |

|           |    | 0: Channel data is checked against the PRBS test pattern.                                               |  |  |

|           |    | 1: Channel data is overwritten with the PRBS test pattern.                                              |  |  |

| LOOP      | 0  | Channel PCM data is not looped back.                                                                    |  |  |

|           | 1  | PCM data for this channel is looped back to receive path.                                               |  |  |

| ZCS[1:0]  | 00 | No zero-code suppression.                                                                               |  |  |

|           | 01 | GTE zero-code suppression.                                                                              |  |  |

|           | 10 | Jammed bit 8.                                                                                           |  |  |

| 11        |    | Bell zero-code suppression.                                                                             |  |  |

The IDLE Code byte stores a constant value that the programmer can transmit for any channel. The Signaling/E1 Control byte provides data manipulation in E1 mode and signaling insertion in T1 mode

#### **TPSC Indirect Register Access**

The TPSC indirect registers are for the per-channel control of the transmit serial data stream. On power-up, the per-channel control is normally disabled by default; therefore, the PCCE bit in register 0xQ6C must be set to enable per channel control once the TPSC is configured.

The IND bit must be set before the software can access TPSC indirect registers. On power-up or software reset, this bit is clear by default. Once the IND bit is set, the following pseudo code shows how to read a TPSC indirect register and write to a TPSC indirect register.

```

WRITE REG(REG TPSC INDIRECT ADDRESS, (offset | 0x80));

for (i = 0; i < MAX BUSY READ; i++)

value = READ REG(REG TPSC MICRO ACCESS STATUS);

if ((value & BIT BUSY) == 0)

{

value = READ REG(REG TPSC INDIRECT DATA);

return SUCCESS;

return FAILURE;

}

/** to write a TPSC register: **/

int WriteTpsc(int offset, unsigned char value)

unsigned char temp;

int i;

WRITE REG(REG TPSC INDIRECT DATA, value);

WRITE REG(REG TPSC INDIRECT ADDRESS, (offset & 0x7F));

for (i = 0; i < MAX BUSY READ; i++)

temp = READ_REG(REG_TPSC_MICRO_ACCESS_STATUS);

if ((temp & BIT BUSY) == 0) return SUCCESS;

return FAILURE;

}

```

#### 4.4 Using the Signaling Extractor

The Signaling Extraction (SIGX) block provides channel associated signaling (CAS) extraction from an E1 signaling multiframe or from SF, SLC®96, and ESF T1 Formats. The SIGX block extracts the signaling bits from the received data stream and serializes the results on the BRSIG output pin.

Control of CAS is normally disabled by default, on power-up or reset. The PCCE bit in register 0xQ50 (SIGX Configuration Register) must be set to activate per channel control. The SIGX configuration should be setup when the COMET-QUAD is in *Configuration* state. The following steps should be followed in order:

1) Disable the PCCE and enable the IND and COSS bit (if indirect registers need to be accessed) in register 0xQ50.

- 2) Program the required SIGX Configuration.

- 3) Disable and COSS bits and enable the PCCE bit in register 0xQ50.

Register 0xQ50 (SIGX Configuration) can represent two different registers depending on the value of its COSS bit. This is discussed below.

**COSS** = 0: The SIGX indirect registers are disabled on reset and have no default value when enabled. Setting the IND bit to logic 1 and the COSS bit to logic 0 in register 0xQ50 (SIGX Configuration Register) enables access to the SIGX configuration indirect registers.

The SIGX configuration indirect registers (Timeslot/Channel Signaling Data (0x20-0x3F) and Per-Timeslot Configuration (0x40-0x5F)) are accessible on a per-channel basis.

Timeslot/Channel Signaling Data registers store signaling data sent to the BRSIG pin. These registers contain the A,B,C,D bits for the ESF, SF, SLC®96 and signaling multiframe format (where bits C and D are replaced with A and B for SF and SLC®96). The Per-Timeslot Configuration registers provide data conditioning in conjunction with the RPSC Data Control bytes.

**COSS** = 1: The registers 0xQ50-0xQ53 (SIGX Change of Signaling State) are used to indicate a change of signaling state on a channel/timeslot. In T1 mode, COSS bits 1 to 24 represent each of the 24 channels. In E1 mode, COSS bits 1 to 30 represent each of the 30 timeslots. These registers may be polled to determine the channel that had a signaling state change. The COSS bits are cleared when the register is read.

#### 4.4.1 SIGX Indirect Register Access

The SIGX indirect registers store the channel associated signaling from framing formats. On power-up, the per-channel control is disabled by default. The PCCE bit in register 0xQ50 (with COSS = 0) must be set to enable per channel control.

The IND bit must be set to logic 1 and the COSS bit must be set to logic 0 before the software can access SIGX indirect registers. By default, on power-up or software reset, these bits are cleared. Once the IND bit is set, the following pseudo code shows how to read a SIGX indirect register and write to a SIGX indirect register.

```

WRITE REG(REG SIGX INDIRECT ADDRESS, (offset | 0x80));

for (i = 0; i < MAX BUSY READ; i++)

value = READ REG(REG SIGX MICRO ACCESS STATUS);

if ((value&BIT BUSY) == 0)

value = READ_REG(REG_SIGX_INDIRECT_DATA);

return SUCCESS;

return FAILURE;

}

/** to write a SIGX register: **/

int WriteSigx(int offset, unsigned char value)

unsigned char temp;

int i;

WRITE REG(REG SIGX INDIRECT DATA, value);

WRITE REG(REG SIGX INDIRECT ADDRESS, (offset & 0x7F));

for (i = 0; i < MAX BUSY READ; i++)

temp = READ REG(REG SIGX MICRO ACCESS STATUS);

if ((temp & BIT BUSY) == 0) return SUCCESS;

return FAILURE;

}

```

#### 5 Interrupts using register access

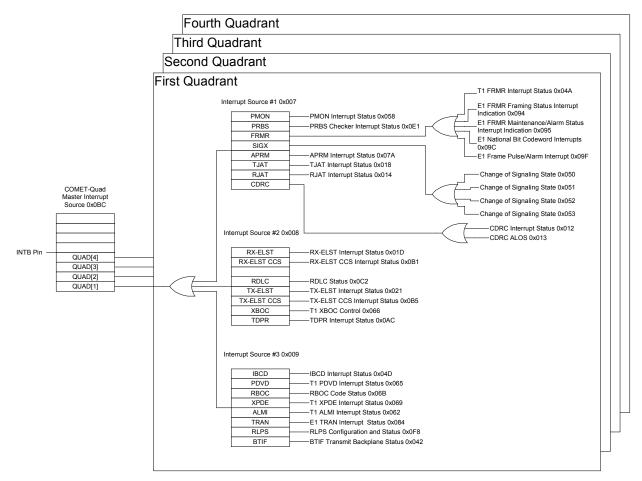

COMET-QUAD has a single interrupt pin (INTB) flagging the interrupt request status for all functional blocks and quadrants. The interrupt status of each quadrant and functional block is indicated by a number of interrupt status registers, as shown in Figure 2.

Figure 2 COMET-QUAD Interrupt Status Register Hierarchy

## 5.1 Interrupt Status and Interrupt Enable Bits

The COMET-QUAD\_Master\_Interrupt\_Register(0x0BC) indicates which COMET-QUAD quadrant has an interrupt status flagged. Each quadrant has three interrupt source registers, Interrupt\_Source\_#1-3(0xQ07-0xQ09), indicating which functional block has an active interrupt request.

Each functional block has at least one status register indicating what type of interrupt occurred in the block. Blocks having more than 8 types of interrupts (such as FRMR and SIGX) may have more than one interrupt status register. The status registers contain interrupt status bits (also called 'I' bits) indicating what kind of interrupt occurred within the block.

Each 'I' bit has an associated interrupt enable bit (also called the 'E' bit). If this bit is enabled, the value of the 'I' bit is propagated to the associated interrupt source register, and accordingly, to the COMET-QUAD\_Master\_Interrupt\_Source(0x0BC) register. If the 'E' bit is disabled, the 'I' bit will still be asserted in case of an interrupt condition, but its value will not be propagated to that block's interrupt source register (and onward to the master interrupt source register). Hence, if the 'E' bit is disabled, that interrupt condition will be masked and will not generate an interrupt on the INTB pin, thus indicating that it does not need any attention from the processor. All 'E' bits are disabled upon COMET-QUAD reset, which means that the chip will not generate any interrupts after a reset. The user has to explicitly set the 'E' bits for the COMET-QUAD to generate desired interrupts.

The INTB pin on the COMET-QUAD will remain asserted until the last requested interrupt is confirmed by reading the block's status register, which means that COMET-QUAD will remain in 'interrupt' state until all the requested interrupts have been serviced.

#### 5.2 Interrupt Reference

Table 13 below references all interrupt bits in the register they appear and the location and name of the corresponding enable/disable and status bit. The table is shown in the order displayed by Figure 2.

**Table 13: Interrupt Reference**

| Interrupt              |                               | Enable/Disable |         | Status   |         |                                 |  |

|------------------------|-------------------------------|----------------|---------|----------|---------|---------------------------------|--|

| Register               | "I" Bit or<br>source<br>group | Register       | "E" Bit | Register | "V" Bit | Comments                        |  |

|                        | PMON                          |                |         |          |         | This is a top-level             |  |

|                        | PRBS                          |                |         |          |         | interrupt source register so no |  |

| Interrupt<br>Source #1 | FRMR                          |                |         |          |         | enable/disable or               |  |

|                        | SIGX                          |                |         |          |         | status bits exist.              |  |

| 0xQ07                  | APRM                          |                |         |          |         | - Individual "I" bits           |  |

|                        | TJAT                          |                |         |          |         | belonging to a group            |  |

|                        | RJAT                          |                |         |          |         | are shown later in              |  |

|                        | CDRC                          |                |         |          |         | this table.                     |  |

| Interrupt              | RX-ELST                       |                |         |          |         | This is a top-level             |  |

| Interrupt                   |                               | Enable/Dis                  | Enable/Disable |                     |         |                                                                |

|-----------------------------|-------------------------------|-----------------------------|----------------|---------------------|---------|----------------------------------------------------------------|

| Register                    | "I" Bit or<br>source<br>group | Register                    | "E" Bit        | Register            | "V" Bit | Comments                                                       |

| Source #2<br>0xQ08          | RX-ELST<br>CCS                |                             |                |                     |         | interrupt source register so no                                |

|                             | Unused                        |                             |                |                     |         | enable/disable bits exist.                                     |

|                             | RDLC                          |                             |                |                     |         | Individual "I" bits                                            |

|                             | TX-ELST                       |                             |                |                     |         | belonging to a group                                           |

|                             | TX-ELST<br>CCS                |                             |                |                     |         | are shown later in this table.                                 |

|                             | XBOC                          |                             |                |                     |         |                                                                |