# Serial Input PLL with 2.5-GHz Prescaler

#### Features

- Operating voltage 2.7V to 5.5V

- Operating frequency: up to 2.5 GHz with prescaler ratios of 32/33 and 64/65

- Lock detect feature

- Power-down mode

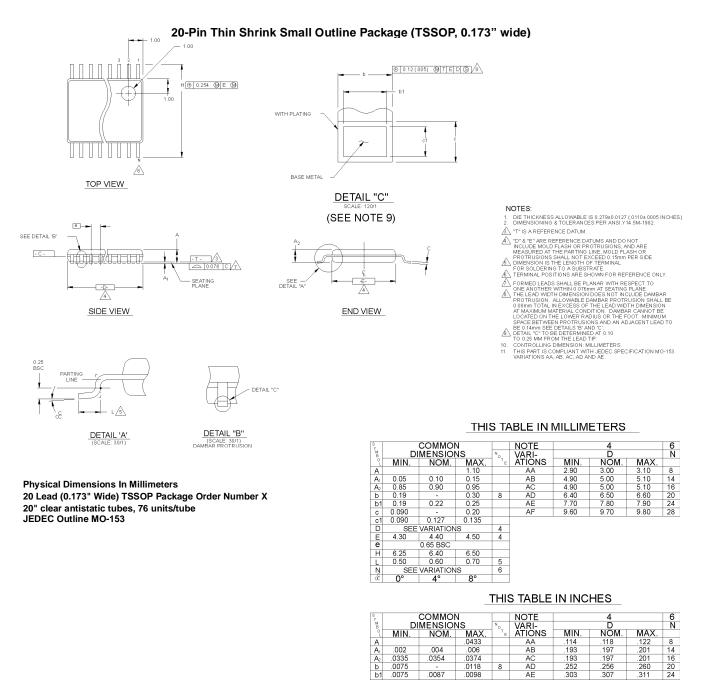

- 20-pin TSSOP (Thin Shrink Small Outline Package)

## Applications

- Wireless LAN

- · Wireless communication handsets

- Base Stations

- Microcells

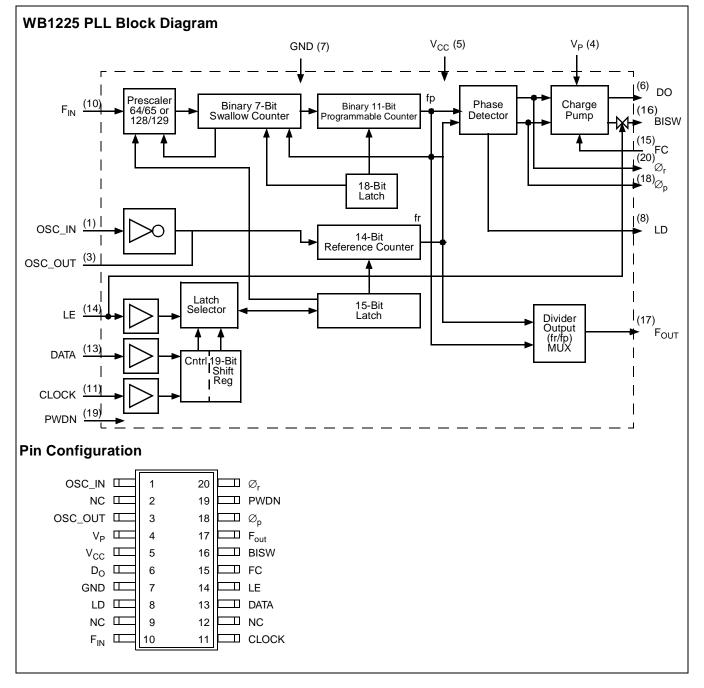

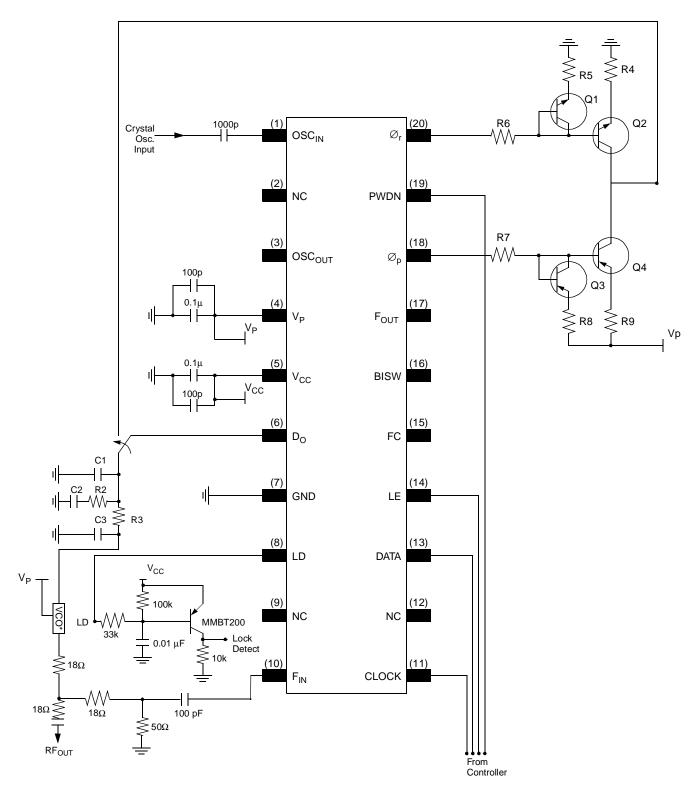

Figure 1. Application Diagram Example - WB1225 2.5-GHz PLL

# **Pin Definitions**

| Pin Name         | Pin<br>No. | Pin<br>Type | Pin Description                                                                                                                                                                                                              |  |  |  |  |  |

|------------------|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| OSC_IN           | 1          | I           | <b>Oscillator Input:</b> This input has a $V_{CC}/2$ threshold and CMOS logic level sensitivity.                                                                                                                             |  |  |  |  |  |

| NC               | 2          |             | No Connect                                                                                                                                                                                                                   |  |  |  |  |  |

| OSC_OUT          | 3          | 0           | Oscillator Output                                                                                                                                                                                                            |  |  |  |  |  |

| V <sub>P</sub>   | 4          | Р           | Charge Pump Rail Voltage: This supply for charge pump. Must be > V <sub>CC</sub> .                                                                                                                                           |  |  |  |  |  |

| V <sub>CC</sub>  | 5          | Р           | <b>Power Supply Connection for PLL:</b> When power is removed from $V_{CC}$ all latched data is lost.                                                                                                                        |  |  |  |  |  |

| D <sub>O</sub>   | 6          | 0           | <i>harge Pump Output:</i> The phase detector gain is $I_P/2\pi$ . Sense polarity can be re-<br>ersed by setting FC LOW (pin 15).                                                                                             |  |  |  |  |  |

| GND              | 7          | G           | Analog and Digital Ground Connection: This pin must be grounded.                                                                                                                                                             |  |  |  |  |  |

| LD               | 8          | 0           | Lock Detect Pin: This output is HIGH with narrow LOW pulses when the loop is locked.                                                                                                                                         |  |  |  |  |  |

| NC               | 9          |             | No Connect                                                                                                                                                                                                                   |  |  |  |  |  |

| F <sub>IN</sub>  | 10         | I           | Input to Prescaler: Maximum frequency 2.5 GHz.                                                                                                                                                                               |  |  |  |  |  |

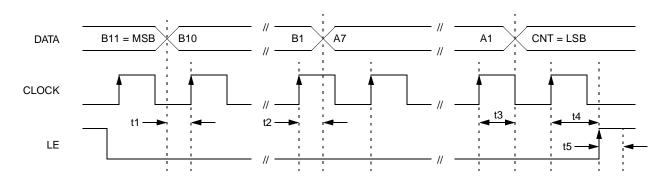

| CLOCK            | 11         | I           | <b>Data Clock Input:</b> One bit of data is loaded into the Shift Register on the rising edge of this signal.                                                                                                                |  |  |  |  |  |

| NC               | 12         |             | No Connect                                                                                                                                                                                                                   |  |  |  |  |  |

| DATA             | 13         | I           | Serial Data Input                                                                                                                                                                                                            |  |  |  |  |  |

| LE               | 14         | I           | <b>Load Enable:</b> On the rising edge of this signal, the data stored in the Shift Register is latched into the counters and configuration controls.                                                                        |  |  |  |  |  |

| F <sub>C</sub>   | 15         | I           | <b>Phase Sense Control for Phase Detector with Internal Pull-up:</b> When pulled LOW, the polarity of the Phase Detector is reversed.                                                                                        |  |  |  |  |  |

| BISW             | 16         | 0           | Analog Switch Output: Connects to output of charge pump when LE is HIGH.                                                                                                                                                     |  |  |  |  |  |

| F <sub>OUT</sub> | 17         | 0           | Monitor Point for Phase Detector Input                                                                                                                                                                                       |  |  |  |  |  |

| Ø <sub>P</sub>   | 18         | 0           | External Charge Pump Output: Open drain N-Channel FET, pull-up resistor required.                                                                                                                                            |  |  |  |  |  |

| PWDN             | 19         | I           | <b>Power Down Pin with Internal Pull-up:</b> When pin is HIGH, device is in normal state. When pin is LOW, device is in power-down mode. When device enters power-down mode the charge pump is in the three-state condition. |  |  |  |  |  |

| Ø <sub>R</sub>   | 20         | 0           | External Change Pump: (CMOS logic output).                                                                                                                                                                                   |  |  |  |  |  |

# **Absolute Maximum Ratings**

Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability.

| Parameter                         | Description          | Rating                       | Unit |  |  |

|-----------------------------------|----------------------|------------------------------|------|--|--|

| V <sub>CC</sub> or V <sub>P</sub> | Power Supply Voltage | -0.5 to +6.5                 | V    |  |  |

| V <sub>OUT</sub>                  | Output Voltage       | –0.5 to V <sub>CC</sub> +0.5 | V    |  |  |

| I <sub>OUT</sub>                  | Output Current       | ±15                          | mA   |  |  |

| TL                                | Lead Temperature     | +260                         | °C   |  |  |

| T <sub>STG</sub>                  | Storage Temperature  | –55 to +150                  | °C   |  |  |

#### **Handling Precautions**

Devices should be transported and stored in antistatic containers.

These devices are static sensitive. Ensure that equipment and personnel contacting the devices are properly grounded.

Cover workbenches with grounded conductive mats.

Always turn off power before adding or removing devices from system.

Protect leads with a conductive sheet when handling or transporting PC boards with devices.

If devices are removed from the moisture protective bags for more than 36 hours, they should be baked at 85°C in a moisture free environment for 24 hours prior to assembly in less than 24 hours.

#### **Recommended Operating Conditions**

| Parameter       | Description           | Test Condition            | Rating                  | Unit |

|-----------------|-----------------------|---------------------------|-------------------------|------|

| V <sub>CC</sub> | Power Supply Voltage  |                           | 2.7 to 5.5              | V    |

| V <sub>P</sub>  | Charge Pump Voltage   |                           | V <sub>CC</sub> to +5.5 | V    |

| T <sub>A</sub>  | Operating Temperature | Ambient air at 0 CFM flow | -40 to +85              | °C   |

| Parameter                         | Description                                             | Test Condition                                                                                                                       | Pin                | Min.                  | Тур. | Max.                  | Unit      |

|-----------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|------|-----------------------|-----------|

| I <sub>CC</sub>                   | Power Supply Current                                    |                                                                                                                                      | V <sub>CC</sub>    |                       | 8    |                       | mA        |

| I <sub>PD</sub>                   | Power-down Current                                      | Power-down, $V_{CC} = 3.0V$                                                                                                          | V <sub>CC</sub>    |                       | 6    | 100                   | μA        |

| F <sub>IN</sub>                   | Maximum Operating<br>Frequency                          |                                                                                                                                      | F <sub>IN</sub>    | 2.5                   |      |                       | GHz       |

| F <sub>OSC</sub>                  | Oscillator Input Frequency                              | No load on OSC_OUT                                                                                                                   | OSC_IN             | 2                     |      | 60                    | MHz       |

|                                   |                                                         | With OSC_OUT loaded                                                                                                                  |                    | 2                     |      | 25                    | MHz       |

| Fφ                                | Maximum Phase Detector<br>Frequency                     |                                                                                                                                      |                    | 10                    |      |                       | MHz       |

| PF <sub>IN</sub>                  | Input Sensitivity                                       | $V_{CC} = 2.7V$                                                                                                                      | F <sub>IN</sub>    | -15                   |      | 4                     | dBm       |

|                                   |                                                         | $V_{CC} = 5.5V$                                                                                                                      |                    | -10                   |      | 4                     | dBm       |

| V <sub>OSC</sub>                  | Oscillator Input Sensitivity                            |                                                                                                                                      | OSC_IN             | 0.5                   |      |                       | $V_{P-P}$ |

| I <sub>IH</sub> , I <sub>IL</sub> | Oscillator Input Current                                |                                                                                                                                      |                    | -100                  |      | 100                   | μA        |

| V <sub>IH</sub>                   | High Level Input Voltage                                | $V_{CC} = 5.0V$                                                                                                                      | DATA,              | V <sub>CC</sub> * 0.8 |      |                       | V         |

| V <sub>IL</sub>                   | Low Level Input Voltage                                 |                                                                                                                                      | CLOCK,<br>LE       |                       |      | V <sub>CC</sub> * 0.3 | V         |

| I <sub>IH</sub>                   | High Level Input Current                                |                                                                                                                                      |                    | -10                   | 1    | 10                    | μA        |

| IIL                               | Low Level Input Current                                 |                                                                                                                                      |                    | -10                   | 1    | 10                    | μA        |

| V <sub>OH</sub>                   | High Level Output Voltage                               |                                                                                                                                      | F <sub>O</sub> /LD | 2.2                   |      |                       | V         |

| V <sub>OL</sub>                   | Low Level Output Voltage                                |                                                                                                                                      |                    |                       |      | 0.4                   | V         |

| ID <sub>O(SO)</sub>               | ID <sub>O</sub> , Source Current                        | $V_{P} = 3.0V, VD_{O} = V_{P}/2$                                                                                                     | D <sub>O</sub>     |                       | -3.2 |                       | mA        |

|                                   |                                                         | $V_{P} = 5.0V, VD_{O} = V_{P}/2$                                                                                                     |                    |                       | -3.8 |                       | mA        |

| ID <sub>OH(SI)</sub>              | ID <sub>O</sub> High, Sink Current                      | $V_{P} = 3.0V, VD_{O} = V_{P}/2$                                                                                                     | D <sub>O</sub>     |                       | 3.2  |                       | mA        |

|                                   |                                                         | $V_{P} = 5.0V, VD_{O} = V_{P}/2$                                                                                                     |                    |                       | 3.8  |                       | mA        |

| $\Delta ID_O$                     | ID <sub>O</sub> Charge Pump Sink<br>and Source Mismatch | $\begin{array}{l} VD_O = V_P / 2 \\ [IID_{O(SI)}I - IID_{O(SO)}I] / \\ [1/2^* \{IID_{O(SI)}]I + IID_{O(SO)}I\}]^* 100\% \end{array}$ |                    |                       | 5    |                       | %         |

| ID <sub>O</sub> vs T              | Charge Pump Current<br>Variation vs. Temperature        | $-40^{\circ}\text{C} < \text{T} < 85^{\circ}\text{C}, \text{ V}_{\text{DO}} = \text{V}_{\text{P}}/2^{[1]}$                           |                    |                       | 5    |                       | %         |

| ID <sub>O-tri</sub>               | Charge Pump High-<br>Impedance Leakage<br>Current       |                                                                                                                                      |                    |                       | ±2   |                       | nA        |

# **Electrical Characteristics:** $V_{CC}$ = 3.0V, $V_{P}$ = 3.0V, $T_{A}$ = -40 °C to +85 °C, Unless otherwise specified

Note:

ID<sub>O</sub>VS T; Charge pump current variation vs. temperature. [IID<sub>O(SI)@T</sub>I − IID<sub>O(SI)@25° C</sub>I]/IID<sub>O(SI)@25°C</sub>I \* 100% and [IID<sub>O(SO)@T</sub>I − IID<sub>O(SO)@25°C</sub>I]/IID<sub>O(SO)@25°C</sub>I \* 100%.

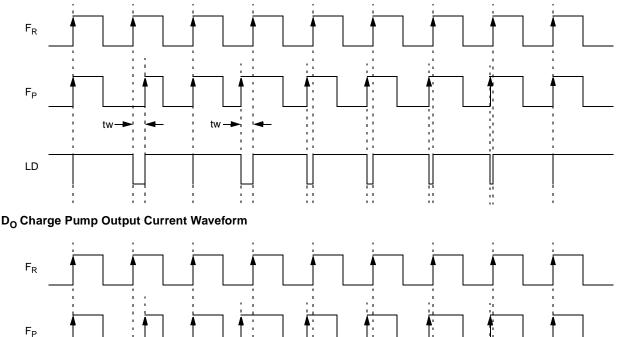

# **Timing Waveforms**

#### Phase Characteristics

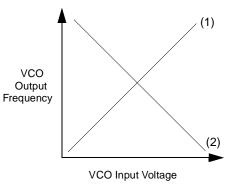

For normal operation, the FC pin is used to select the output polarity of the phase detector. Both the internal and any external charge pump are affected.

Depending upon VCO characteristics, FC pin should be set accordingly:

When VCO characteristics are like (1), FC should be set HIGH or OPEN CIRCUIT:

When VCO characteristics are like (2), FC should be set LOW.

When FC is set HIGH or OPEN CIRCUIT,  $F_{out}$  pin is set to the reference divider output,  $F_r$  When FC is set LOW,  $F_{out}$  pin is set to the programmable divider output  $F_p$ .

Phase Comparator Sense

••••• ۰,

Three-state

#### **Phase Detector Output Waveform**

tw

tw

$D_0$

IDo

11

# Timing Waveforms (continued) Serial Data Input Timing Waveform<sup>[2, 3, 4, 5]</sup>

# **Serial Data Input**

Data is input serially using the DATA, CLOCK, and LE pins. Two control bits direct data into the locations given in Table 1.

#### Table 1. Control Configuration

| CNT | Function                                                                         |

|-----|----------------------------------------------------------------------------------|

| 1   | Reference Counter: R = 3 to 16383, set prescaler ratio PRE =0:64/65, PRE=1:32/33 |

| 0   | <b>Program Counter:</b> A = 0 to 63, B = 3 to 2047                               |

# Table 2. Shift Register Configuration<sup>[6]</sup>

|        |                                          | •  |       | 0                                                                |         |          |         |                |          |          |                    |        |         |        |     |    |     |     |

|--------|------------------------------------------|----|-------|------------------------------------------------------------------|---------|----------|---------|----------------|----------|----------|--------------------|--------|---------|--------|-----|----|-----|-----|

| 1      | 2                                        | 3  | 4     | 5                                                                | 6       | 7        | 8       | 9              | 10       | 11       | 12                 | 13     | 14      | 15     | 16  | 17 | 18  | 19  |

| Refer  | Reference Counter and Configuration Bits |    |       |                                                                  |         |          |         |                |          |          |                    |        |         |        |     |    |     |     |

| CNT    | R1                                       | R2 | R3    | R4                                                               | R5      | R6       | R7      | R8             | R9       | R10      | R11                | R12    | R13     | R14    | PRE |    |     |     |

|        |                                          |    |       |                                                                  |         |          |         |                |          |          |                    |        |         |        |     |    |     |     |

| Progr  | Programmable Counter Bits                |    |       |                                                                  |         |          |         |                |          |          |                    |        |         |        |     |    |     |     |

| CNT    | A1                                       | A2 | A3    | A4                                                               | A5      | A6       | A7      | B1             | B2       | B3       | B4                 | B5     | B6      | B7     | B8  | B9 | B10 | B11 |

|        |                                          |    |       |                                                                  |         |          |         |                |          |          |                    |        |         |        |     |    |     |     |

| Bit(s) | Name                                     | )  | Func  | tion                                                             |         |          |         |                |          |          |                    |        |         |        |     |    |     |     |

| CNT    |                                          |    | Cont  | rol Bit:                                                         | Direct  | s progi  | rammir  | ng data        | to refe  | erence   | or prog            | gramma | able co | unters |     |    |     |     |

| R1–R   | 14                                       |    | Refer | rence (                                                          | Counte  | er Setti | ing Bit | <b>s:</b> 14 b | its, R = | = 3 to 1 | 6383. <sup>[</sup> | 7]     |         |        |     |    |     |     |

| PRE    |                                          |    | Preso | caler D                                                          | ivide E | Bit: LO  | W = 64  | l/65 an        | d HIGI   | H = 32/  | 33.                |        |         |        |     |    |     |     |

| A1–A   | 7                                        |    | Swall | Swallow Counter Divide Ratio: A = 0 to 63.                       |         |          |         |                |          |          |                    |        |         |        |     |    |     |     |

| B1–B   | 11                                       |    | Prog  | Programmable Counter Divide Ratio: B = 3 to 2047. <sup>[7]</sup> |         |          |         |                |          |          |                    |        |         |        |     |    |     |     |

Notes:

The SE low count ratios and violate frequency limits of the second seco 2. 3. 4. 5. 6. 7.

## Table 3. 7-Bit Swallow Counter (A) Truth Table<sup>[8]</sup>

| Divide Ratio A | A7 | A6  | A5  | A4  | A3  | A2  | A1  |

|----------------|----|-----|-----|-----|-----|-----|-----|

| 0              | Х  | 0   | 0   | 0   | 0   | 0   | 0   |

| 1              | Х  | 0   | 0   | 0   | 0   | 0   | 1   |

| :::            | Х  | ::: | ::: | ::: | ::: | ::: | ::: |

| 62             | Х  | 1   | 1   | 1   | 1   | 1   | 0   |

| 63             | Х  | 1   | 1   | 1   | 1   | 1   | 1   |

## Table 4. 11-Bit Programmable Counter (B) Truth Table<sup>[9]</sup>

| Divide Ratio B | B11 | B10 | B9  | B8  | B7  | B6  | B5  | B4  | B3 | B2 | B1  |

|----------------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|-----|

| 3              | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 1  | 1   |

| 4              | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1  | 0  | 0   |

| :::            | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: |    |    | ::: |

| 2046           | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 0   |

| 2047           | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1   |

#### Table 5. 14-Bit Programmable Reference Counter Truth Table<sup>[9]</sup>

| Divide Ratio R | R14 | R13 | R12 | R11 | R10 | R9  | R8  | R7  | R6  | R5  | R4  | R3  | R2  | R1  |

|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 3              | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   |

| 4              | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   |

| :::            | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: | ::: |

| 16382          | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   |

| 16383          | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

# **Ordering Information**<sup>[10]</sup>

| Ordering Code | Package<br>Name | Package Type               | TR                   |

|---------------|-----------------|----------------------------|----------------------|

| WB1225        | Х               | 20-pin TSSOP (0.173" wide) | Tape and Reel Option |

Notes: 8. 9.

B is greater than or equal to A. Divide ratio less than 3 is prohibited. The divide ratio can be calculated using the following equation:

fvco = {(P \* B) + A} \* fosc / R where (A  $\leq$  B)

fvco: Output frequency of the external VCO. fosc: The crystal reference oscillator frequency.

A: Preset divide ratio of the 7-bit swallow counter.

B: Preset ratio of the 11-bit programmable counter (3 to 2047).

P: Preset divide ratio of the dual modulus prescaler.

R: Preset ratio of the 15-bit programmable reference counter (3 to 16383).

The divide ratio N = (P \* B) + A.

10. Operating temperature range: -40°C to +85°C.

Document #: 38-00866-A

# Package Diagram

0035

.169

246

.020

0°

c C .0035

E e

Н

Ņ

0079

0053

177

256

.028

8

4

4

5 6

.0050

173

0256 BSC

.252 .024

SEE VARIATIONS

4 \*VARIATION AF IS DESIGNED BUT NOT TOOLED\*

SEE VARIATIONS

AF

.378

382

386 28