# CDC 3207G-C3

### Contents

| Page | Section | Title                                        |

|------|---------|----------------------------------------------|

| 3    | 1.      | Introduction                                 |

| 3    | 1.1.    | Features                                     |

| 6    | 1.2.    | Abbreviations                                |

| 7    | 1.3.    | Block Diagram                                |

| 9    | 2.      | Packages and Pins                            |

| 9    | 2.1.    | Package Outline Dimensions                   |

| 10   | 2.2.    | Pin Assignment                               |

| 10   | 2.3.    | Pin Function Description                     |

| 11   | 2.4.    | External Components                          |

| 13   | 3.      | Electrical Data                              |

| 13   | 3.1.    | Absolute Maximum Ratings                     |

| 14   | 3.2.    | Recommended Operating Conditions             |

| 15   | 3.3.    | Characteristics                              |

| 17   | 3.4.    | Recommended Quartz Crystal Characteristics   |

| 19   | 4.      | CPU and Clock System                         |

| 21   | 5.      | Memory and Special Function ROM (SFR) System |

| 23   | 6.      | Core Logic                                   |

| 23   | 6.1.    | Control Word (CW)                            |

| 25   | 7.      | Hardware Options                             |

| 25   | 7.1.    | Functional Description                       |

| 27   | 8.      | Differences                                  |

| 28   | 9.      | Data Sheet History                           |

# 1. Introduction

# Release Note: Revision bars indicate significant changes to the previous edition.

The device is a microcontroller for use in automotive applications. The on-chip CPU is an ARM<sup>®</sup> processor ARM7TDMI<sup>™</sup> with 32-bit data and address bus, which supports Thumb<sup>™</sup> format instructions.

The chip contains timer/counters, an interrupt controller, a multichannel A/D converter, a stepper motor and LCD driver,

CAN interfaces, PWM outputs and a crystal clock multiplying PLL.

This document provides MCM Flash hardware-specific information. General information on operating the IC can be found in the document "CDC32xxG-C Automotive Controller - Family User Manual, CDC3205G-C Automotive Controller" (6251-579-1DS)".

### 1.1. Features

Table 1-1: CDC32xxG-C Family Feature List

| Item                                                | CDC3205G-<br>C<br>EMU                                             | CDC3207G-<br>C<br>MCM Flash                             | CDC3217G-<br>C<br>MCM Flash                              | CDC3257G-<br>C2<br>MCM Flash                            | CDC3272G-<br>C<br>Mask ROM              | CDC3231G<br>C<br>Mask ROM              |  |  |

|-----------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------|-----------------------------------------|----------------------------------------|--|--|

| Core                                                |                                                                   |                                                         |                                                          |                                                         |                                         |                                        |  |  |

| CPU                                                 | 32-bit ARM71                                                      |                                                         |                                                          |                                                         |                                         |                                        |  |  |

| CPU-active operation modes                          | DEEP SLOW                                                         | , SLOW, FAST a                                          | and PLL                                                  |                                                         |                                         |                                        |  |  |

| Power-saving operation modes (CPU inactive)         | IDLE, WAKE                                                        | and STANDBY                                             |                                                          |                                                         |                                         |                                        |  |  |

| CPU clock multiplication                            | PLL delivering                                                    | g up to 50 MHz                                          |                                                          |                                                         |                                         |                                        |  |  |

| EMI reduction mode                                  | selectable in                                                     | selectable in PLL mode                                  |                                                          |                                                         |                                         |                                        |  |  |

| Oscillators                                         | 4 to 5 MHz quartz and 32 kHz internal RC                          |                                                         |                                                          |                                                         |                                         |                                        |  |  |

| RAM, zero wait state, 32 bit wide                   | ro wait state, 32 bit wide 32 Kbyte 16 Kbyte 16 Kbyte             |                                                         |                                                          |                                                         |                                         |                                        |  |  |

| ROM                                                 | ROMIess,<br>ext. up to<br>4 M × 32/<br>8 M × 16                   | 512-Kbyte<br>Flash<br>(256 K × 16)<br>top-boot<br>conf. | 1024-Kbyte<br>Flash<br>(512 K × 16)<br>top-boot<br>conf. | 256-Kbyte<br>Flash<br>(128 K × 16)<br>top-boot<br>conf. | 384 Kbyte<br>(96 K × 32/<br>192 K × 16) | 128 Kbyte<br>(32 K × 32/<br>64 K × 16) |  |  |

| Boot ROM                                            | 8 Kbyte (spec                                                     | cial function RO                                        | M)                                                       |                                                         |                                         |                                        |  |  |

| Digital watchdog                                    | <b>v</b>                                                          |                                                         |                                                          |                                                         |                                         |                                        |  |  |

| Central clock divider                               | <b>v</b>                                                          |                                                         |                                                          |                                                         |                                         |                                        |  |  |

| Interrupt controller expanding IRQ                  | g 40 inputs, 16 priority levels 26 input<br>16 priorievels levels |                                                         |                                                          |                                                         |                                         |                                        |  |  |

| Port interrupts including slope selection           | 6 inputs                                                          |                                                         |                                                          |                                                         |                                         | 5 inputs                               |  |  |

| Port wake-up inputs including slope/level selection | 10 inputs                                                         |                                                         |                                                          |                                                         |                                         |                                        |  |  |

#### This Device:

#### Table 1-1: CDC32xxG-C Family Feature List

|                                                                                                |                                                                                                                                          | This<br>Device:                                                                |                             |                              |                            |                                               |  |

|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------|------------------------------|----------------------------|-----------------------------------------------|--|

| Item                                                                                           | CDC3205G-<br>C<br>EMU                                                                                                                    | CDC3207G-<br>C<br>MCM Flash                                                    | CDC3217G-<br>C<br>MCM Flash | CDC3257G-<br>C2<br>MCM Flash | CDC3272G-<br>C<br>Mask ROM | CDC3231G-<br>C<br>Mask ROM                    |  |

| Patch module                                                                                   | 10 ROM loca                                                                                                                              | tions                                                                          |                             |                              |                            |                                               |  |

| Boot system                                                                                    | allows in-syst<br>memory via J                                                                                                           | em downloading<br>TAG                                                          | g of external co            | de to Flash                  | -                          |                                               |  |

| Device lock module                                                                             | inhibits acces<br>tomer                                                                                                                  | s to internal firn                                                             | nware, lock can             | be set by cus-               | -                          |                                               |  |

| Analog                                                                                         |                                                                                                                                          |                                                                                |                             |                              |                            |                                               |  |

| Reset/Alarm                                                                                    | combined inp                                                                                                                             | ut for regulator                                                               | input supervisio            | n                            |                            |                                               |  |

| Clock and supply supervision                                                                   | ~                                                                                                                                        |                                                                                |                             |                              |                            |                                               |  |

| 10-bit ADC, charge balance type                                                                | 16 channels (                                                                                                                            | each selectable                                                                | e as digital input          | :)                           |                            |                                               |  |

| ADC reference                                                                                  | VREF pin, P1                                                                                                                             | .0 pin, P1.1 pin                                                               | or VREFINT in               | ternal bandgap               | selectable                 |                                               |  |

| Comparators                                                                                    | P06COMP with 1/2 AVDD reference,<br>WAITCOMP with internal bandgap reference                                                             |                                                                                |                             |                              |                            |                                               |  |

| LCD                                                                                            | internal processing of all analog voltages for the LCD driver                                                                            |                                                                                |                             |                              |                            |                                               |  |

| Communication                                                                                  |                                                                                                                                          |                                                                                |                             |                              |                            |                                               |  |

| DMA                                                                                            | 3 DMA chanr<br>and SPI1                                                                                                                  | 3 DMA channels, one each for serving the graphics bus interface, SPI0 and SPI1 |                             |                              |                            |                                               |  |

| UART                                                                                           | 2: UART0 and                                                                                                                             | d UART1                                                                        |                             |                              |                            | UART0                                         |  |

| Synchronous serial peripheral interfaces                                                       | 2: SPI0 and S                                                                                                                            | SPI1, DMA supp                                                                 | orted                       |                              |                            |                                               |  |

| Full CAN modules V2.0B<br>each with a 32-object RAM<br>(LCAN000E)                              | 4: CAN0, CA                                                                                                                              | N1, CAN2 and C                                                                 | CAN3                        | 2: CAN0 and                  | CAN1                       | 1: CAN0                                       |  |

| DIGITbus                                                                                       | 1 master mod                                                                                                                             | lule                                                                           |                             |                              |                            | -                                             |  |

| l <sup>2</sup> C                                                                               | 2 master mod                                                                                                                             | lules: I2C0 and                                                                | I2C1                        |                              |                            | I2C0                                          |  |

| Graphics bus interface                                                                         | 8-bit data bus<br>LCD controlle                                                                                                          | ON SED 1560                                                                    | -                           |                              |                            |                                               |  |

| Input & Output                                                                                 |                                                                                                                                          |                                                                                |                             |                              |                            |                                               |  |

| Universal ports selectable as<br>4:1-mux LCD segment/back-<br>plane lines or digital I/O ports | up to 52 I/O or 48 LCD segment lines (= 192 segments),       up or or loc         individually configurable as I/O or LCD       segments |                                                                                |                             |                              |                            |                                               |  |

| Universal port slew rate                                                                       | SW-selectabl                                                                                                                             | e                                                                              |                             |                              |                            |                                               |  |

| Stepper motor control modules with high-current ports                                          | 7 modules,<br>32 dl/dt-contr                                                                                                             | olled ports                                                                    |                             |                              |                            | 4 modules<br>23 dl/dt-<br>controlled<br>ports |  |

Feb. 10, 2005; 6251-589-1DS

Table 1-1: CDC32xxG-C Family Feature List

|                                                                            |                                     | Device:                       |                             |                              |                            |                                                                  |

|----------------------------------------------------------------------------|-------------------------------------|-------------------------------|-----------------------------|------------------------------|----------------------------|------------------------------------------------------------------|

| Item                                                                       | CDC3205G-<br>C<br>EMU               | CDC3207G-<br>C<br>MCM Flash   | CDC3217G-<br>C<br>MCM Flash | CDC3257G-<br>C2<br>MCM Flash | CDC3272G-<br>C<br>Mask ROM | CDC3231G-<br>C<br>Mask ROM                                       |

| PWM modules, each config-<br>urable as two 8-bit PWMs or one<br>16-bit PWM | 6 modules: P<br>11                  | WM0/1, PWM2                   | /3, PWM4/5, PV              | vm6/7, PWM8/9                | and PWM10/                 | 5 modules:<br>PWM0/1,<br>PWM2/3,<br>PWM4/5,<br>PWM6/7,<br>PWM8/9 |

| Pulse/frequency modulator                                                  | 2: PFM0 and                         | PFM1                          |                             |                              |                            | -                                                                |

| Audio module with auto-decay                                               | ~                                   |                               |                             |                              |                            |                                                                  |

| SW-selectable clock outputs                                                | 2                                   |                               |                             |                              |                            |                                                                  |

| Polling/flash timer output                                                 | 1 high-curren                       | t port output op              | erable in power             | -saving operation            | on modes                   |                                                                  |

| Timers & Counters                                                          |                                     |                               |                             |                              |                            |                                                                  |

| 16-bit free-running counters with capture/compare modules                  | CCC0 with 4<br>CCC1 with 2          |                               |                             |                              |                            | CCC0 with<br>4 CAPCOM                                            |

| 16-bit timers                                                              | 1: T0                               |                               |                             |                              |                            |                                                                  |

| 8-bit timers                                                               | 4: T1, T2, T3                       | and T4                        |                             |                              |                            |                                                                  |

| Real-time clock, delivering hours, minutes and seconds                     | <b>v</b>                            |                               |                             |                              |                            |                                                                  |

| Miscellaneous                                                              |                                     |                               |                             |                              |                            |                                                                  |

| Scalable layout in CAN, RAM and ROM                                        | -                                   | •                             |                             |                              |                            |                                                                  |

| Various HW options selectable at random                                    | set by copy fr                      | om user progra                | m storage durir             | ng system start-             | ир                         |                                                                  |

| JTAG interface                                                             | allows Flash                        | programming                   |                             |                              | ~                          | ~                                                                |

| On-chip debug aids                                                         | Embedded<br>trace mod-<br>ule, JTAG | JTAG                          |                             |                              |                            |                                                                  |

| Core bond-out                                                              | ~                                   | -                             |                             |                              |                            |                                                                  |

| Supply voltage                                                             | 3.5 to 5.5 V (                      | imited I/O perfo              | ormance below 4             | 4.5 V)                       |                            |                                                                  |

| Case temperature range                                                     | 0 °C to<br>+70 °C                   | -40 °C to +10                 | 05 °C                       |                              |                            |                                                                  |

| Package                                                                    |                                     |                               |                             |                              |                            |                                                                  |

| Туре                                                                       | ceramic<br>257PGA                   | plastic 128Ql<br>0.5 mm pitch |                             |                              |                            |                                                                  |

| Bonded pins                                                                | 256                                 | 128                           | 128                         | 128                          | 126                        | 111                                                              |

This Device:

$ARM^{\textcircled{R}}$  and Thumb R are the registered trademarks of ARM Limited. ARM7TDMI^{TM} is the trademark of ARM Limited.

## 1.2. Abbreviations

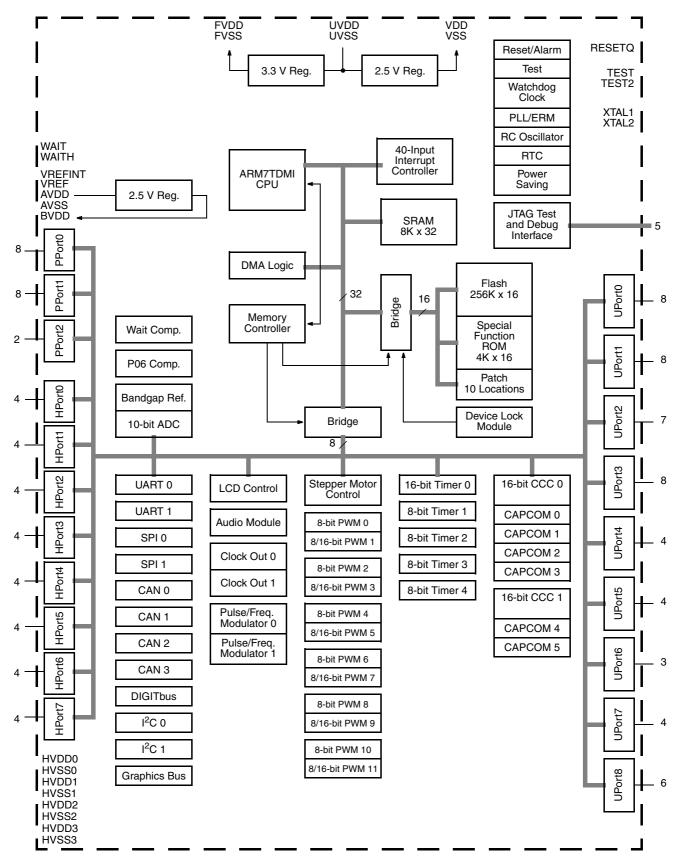

## 1.3. Block Diagram

Fig. 1–1: CDC3207G-C block diagram

# 2. Packages and Pins

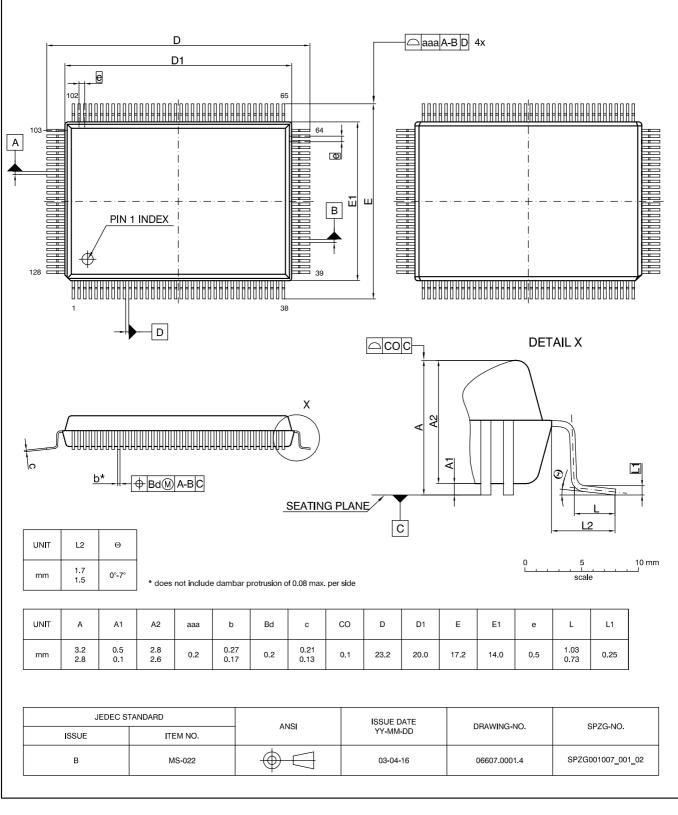

## 2.1. Package Outline Dimensions

#### Fig. 2–1: PMQFP128-2: Plastic Metric Quad Flat Package, 128 leads, $14 \times 20 \times 2.7 \text{ mm}^3$ Ordering code: MF Weight approximately 1.8 g

## 2.2. Pin Assignment

|        |                  | Functions       |              | Not      |     |                 |                  |     | Pin  |              | _        | Pin Func       |                |       |

|--------|------------------|-----------------|--------------|----------|-----|-----------------|------------------|-----|------|--------------|----------|----------------|----------------|-------|

|        | Port             | Port            | Basic        | е        | No. |                 |                  |     | No.  | е            | Basic    | Port           | Port           | LCD   |

| lode   | Special Out      | Special In      | Function     |          |     |                 |                  |     |      |              | Function | Special In     | Special Out    | Mode  |

| SEG3.1 | CC1-OUT          | CC1-IN / TMS    | U3.1         |          | 116 | ٦               |                  |     | 115  |              | U3.2     | CC0-IN / TCK   | CC0-OUT        | SEG3. |

| SEG3.0 | CC2-OUT          | CC2-IN / TDI    | U3.0         |          | 117 | \               |                  | /   | 114  | 1            | U3.3     |                | CO0/TDO        | SEG3. |

| 0200.0 | 002 001          | 002 111/101     |              |          | 118 | 1               |                  | /   | 113  |              | U3.4     | SPI0-CLK-IN    | SPI0-CLK-OUT   |       |

|        |                  |                 | TEST2        |          |     | 1               |                  |     |      |              |          |                |                | SEG3. |

|        |                  |                 | UVDD         |          | 119 | \               |                  | /   | 112  |              | U3.5     | SPI0-D-IN      | тоз            | SEG3  |

|        |                  |                 | UVSS         |          | 120 | 1               |                  | 1   | 111  |              | U3.6     |                | SPI0-D-OUT     | SEG3  |

| SEG2.6 | DIGIT-OUT        | DIGIT-IN        | U2.6         |          | 121 | \               |                  | /   | 110  | -            | U3.7     | SPI1-CLK-IN    | SPI1-CLK-OUT   | SEG3  |

|        |                  |                 |              |          |     | \               | ,                | /   | -    |              |          |                |                |       |

| SEG2.5 | CC1-OUT          | UART0-RX        | U2.5         |          | 122 | 1               | /                |     | 109  |              | U4.0     | SPI1-D-IN      | CC0-OUT        | BP0   |

| SEG2.4 | UART0-TX         | DIGIT-IN/CC1-IN | U2.4         |          | 123 |                 | /                |     | 108  |              | U4.1     | CC0-IN         | SPI1-D-OUT     | BP1   |

| SEG2.3 | CC2-OUT          | UART1-RX        | U2.3         |          | 124 | 1               | /                |     | 107  |              | U4.2     |                | CAN0-TX        | BP2   |

|        | UART1-TX         |                 | U2.2         |          | 125 |                 | /                |     | 106  |              |          | CAN0-RX/WP5    | TO2            | BP3   |

| SEG2.2 |                  | CC2-IN          |              |          |     |                 | /                |     |      |              | U4.3     | CANU-RA/WP5    |                |       |

| SEG7.7 | CO0              |                 | U7.7/GD7     | 1,2      | 126 |                 | · /              |     | 105  | 1,2          | U8.0     |                | CC4-OUT        | SEG8  |

| SEG7.6 | CO1              |                 | U7.6/GD6     | 1,2      | 127 |                 | \ /              |     | 104  | 1,2          | U8.1     |                | CC3-OUT        | SEG8  |

| SEG7.5 | LCK/PFM1         |                 | U7.5/GD5     |          |     |                 | \ /              |     | 103  | 1,2          | U8.2     | LCD-CLK-IN     | CAN3-TX        | SEG8  |

|        |                  |                 |              |          | 120 |                 | \ /              |     |      |              |          |                |                |       |

| SEG7.4 | CC5-OUT          | CC5-IN          | U7.4/GD4     | 1,2      | 1   |                 | \ /              | 1   | 102  | 1,2          | U8.3     | CAN3-RX/WP9    | LCD-CLK-OUT    | SEG8  |

|        |                  |                 | FVDD         | 1,2      | 2   |                 | \ /              |     | 101  | 1,2          | U8.4     | LCD-SYNC-IN    | CAN2-TX        | SEG8  |

|        |                  |                 | FVSS         | 1,2      |     |                 | \ /              |     | 100  | 1,2          | U8.5     | CAN2-RX/PINT3/ | LCD-SYNC-OUT   | SEG8  |

| 000000 |                  | 007.00          |              |          |     | ١               | $\setminus$ /    | 1   | 1.00 | -,2          | 00.0     | WP8            | 200 0110-001   | 0200  |

| SEG5.3 | CC4-OUT          | CC4-IN          | U5.3/GD3     |          | 4   | 1               | $\setminus$ /    | 1   | L    | <u> </u>     | L        | VVFO           |                | 1     |

| SEG5.2 | SDA1             | SDA1            | U5.2/GD2     | 1        | 5   | 1               | \ /              | 1   | 99   | 1            | U6.0     |                | CAN1-TX        | SEG6  |

| SEG5.1 | SCL1             | SCL1            | U5.1/GD1     |          | 6   | 1               | $\setminus$ /    | 1   | 98   | 1            | U6.1     | CAN1-RX/WP7    | GOEQ           | SEG6  |

|        | PFM0             | 55E1            | U5.0/GD0     |          |     | 1               | \ /              | 1   | 97   | 1            | U6.2     |                | GWEQ           | SEG6  |

| SEG5.0 |                  |                 |              |          |     | 1               | $\setminus$ /    | 1   |      | Ľ            |          |                | anila          | 0200  |

| SEG2.1 | SDA0             | WP6/SDA0/CAN0-  | U2.1         | 1        | 8   | 1               | $\setminus$ /    | 1   | 96   | 1            | P2.0     |                |                |       |

|        |                  | RX              | 1            | 1        |     | 1               | \/               | 1   | 95   |              | P2.1     |                |                |       |

| SEG2.0 | SCL0/CAN0-TX     | SCL0            | U2.0         | 1        | 9   | 1               | V                | 1   | 94   | 1            | P0.0     | CC4-IN         |                | 1     |

|        |                  |                 |              |          |     | 1               |                  | 1   |      | <u> </u>     |          | 507 III        | +              | 4     |

| SEG1.7 | PFM0             | WP0/PINT0       | -            |          | 10  |                 |                  | 1   | 93   | L            | P0.1     |                |                |       |

| SEG1.6 | INTRES/CO0       | PINT1           | U1.6         |          | 11  | 1 10            | 110 115 100      | 1   | 92   |              | P0.2     |                |                |       |

| SEG1.5 | CO1/CO0Q         | PINT2           | U1.5         |          | 12  | 12              | 116 115 103      | 4   | 91   |              | P0.3     |                |                |       |

| JEG1.0 | 001/0000         | 111112          |              |          |     | 1 0             | 0                | 102 |      |              |          |                | _              | _     |

|        |                  |                 | TEST         |          | 13  | '               |                  | 102 | 90   |              | P0.4     |                |                |       |

|        |                  | RE              | SETQ/ALARMQ  |          | 14  |                 |                  |     | 89   |              | P0.5     |                |                |       |

|        |                  |                 | XTAL2        |          | 15  |                 |                  |     | 88   |              | P0.6     | P0.6 Comp.     |                |       |

|        |                  |                 |              |          |     |                 |                  |     |      |              |          | 1 010 00mp.    |                | -     |

|        |                  |                 | XTAL1        |          | 16  |                 |                  |     | 87   |              | P0.7     |                |                |       |

|        |                  |                 | VSS          |          | 17  |                 |                  |     | 86   |              | WAITH    |                |                |       |

|        |                  |                 | VDD          |          | 18  |                 |                  |     | 85   |              | WAIT     |                |                |       |

| SEG1.4 | ITSTOUT/AM-OUT   |                 | U1.4         |          |     |                 |                  |     | 84   |              | BVDD     |                |                |       |

|        |                  |                 |              |          | 19  |                 |                  |     |      |              |          |                |                |       |

| SEG1.3 | MTO/AM-PWM       | WP3             | U1.3         |          | 20  |                 |                  |     | 83   |              | AVSS     |                |                |       |

| SEG1.2 | INTRES/T0-OUT    | MTI/ITSTIN      | U1.2         |          | 21  |                 |                  |     | 82   |              | AVDD     |                |                |       |

| SEG1.1 | T1-OUT           |                 | U1.1         | 1        | 22  |                 |                  |     | 81   | -            | VREFINT  |                |                |       |

|        |                  |                 |              |          |     |                 |                  |     |      |              |          |                |                |       |

| SEG1.0 | T2-OUT           |                 | U1.0         |          | 23  |                 |                  |     | 80   |              | VREF     |                |                |       |

| SEG0.7 | T3-OUT           | WP4             | U0.7         |          | 24  | 00              |                  | 05  | 79   |              | P1.0     | VREF0/WP1      |                |       |

| SEG0.6 | CC3-OUT/T4-OUT   | CC3-IN          | U0.6         |          | 25  | <sup>38</sup> o |                  | 65  | 78   |              | P1.1     | VREF1/WP2      |                |       |

|        |                  |                 |              |          |     | 39              | 51 52 64         | I   |      | <del> </del> |          |                | -              | +     |

| SEG0.5 | CC3-OUT          | PINT4           | U0.5         |          | 26  | 1 33            | 51 52 04         | 1   | 77   |              | P1.2     | PINT0          |                |       |

| SEG0.4 | CO1              | PINT5           | U0.4         |          | 27  | 1               |                  | 1   | 76   |              | P1.3     | PINT1          |                |       |

| SEG0.3 | PWM0             |                 | U0.3         | 1        | 28  | 1               | ٨                | 1   | 75   | 1            | P1.4     | PINT2          | 1              | 1     |

|        |                  |                 |              |          |     | 1               | /\               | 1   |      | <u> </u>     |          |                | -              | -     |

| SEG0.2 | PWM1             |                 | U0.2         |          | 29  | 1               | / \              | 1   | 74   |              | P1.5     | PINT3          |                | 1     |

| SEG0.1 | PWM2             |                 | U0.1         | 1        | 30  | 1               | / \              | 1   | 73   | 1 -          | P1.6     | PINT4          |                | 1     |

| SEG0.0 | PWM3             |                 | U0.0         |          | 31  | 1               | / \              | 1   | 72   | 1            | P1.7     | PINT5          | 1              | 1     |

|        | SME1+/PWM4       | SME-COMP3       |              |          | 32  | 1               | / \              | 1   |      | 1            | H0.0     |                | SMG2-/PWM7     | +     |

|        |                  |                 | H7.3         |          |     | 1               | / \              | 1   | 71   | Ľ            |          | SMG-COMP0      |                | 1     |

|        | SME1-/PWM6       | SME-COMP2       | H7.2         | 1        | 33  | 1               | / \              | 1   | 70   | 1            | H0.1     | SMG-COMP1      | SMG2+/PWM5     |       |

|        | SME2+/PWM8       | SME-COMP1       | H7.1         | 1        | 34  | 1               | / \              | 1   | 69   | 1            | H0.2     | SMG-COMP2      | SMG1-/PWM3/POL | 1     |

|        | SME2-/PWM9       | SME-COMP0       | H7.0         |          | 35  | 1               | / \              | 1   | 68   | 1            | H0.3     | SMG-COMP3      | SMG1+/PWM1     | +     |

|        | SIVIE2-/F VVIVI9 | SIVIE-COIVIPU   |              |          |     |                 | / \              | 1   |      | Ľ.           |          | SIVIG-COIVIP3  |                | 1     |

|        |                  |                 | HVDD2        | 1,2      |     |                 | / \              | 1   | 67   | 1,2          | HVSS3    |                |                |       |

|        |                  |                 | HVSS2        | 1,2      | 37  |                 | / \              | 1   | 66   | 1,2          | HVDD3    |                |                |       |

|        | PWM8             |                 | H6.3         | 1,2      | 38  |                 | /                |     | 65   |              | H1.0     | SMF-COMP0      | SMF2-          | 1     |

|        |                  |                 |              |          |     |                 | /                |     |      |              |          |                |                | 1     |

|        | PWM9             |                 | H6.2         | 1,2      | 39  |                 | / \              |     | 64   | 1,2          | H1.1     | SMF-COMP1      | SMF2+          |       |

|        | PWM10            |                 | H6.1         | 1,2      | 40  |                 | ۲ I              |     | 63   | 1,2          | H1.2     | SMF-COMP2      | SMF1-          | 1     |

|        | PWM11            |                 | H6.0         | 1.2      | 41  |                 | /                |     | 62   | 1,2          | H1.3     | SMF-COMP3      | SMF1+          | +     |

|        |                  | 0110 00110-     |              | <i>'</i> |     | /               | 1                |     |      | 1,4          |          |                |                | 1     |

|        | SMD1+            | SMD-COMP3       | H5.3         | L        | 42  |                 | /                |     | 61   | L            | H2.0     | SMC-COMP0      | SMC2-          |       |

|        | SMD1-            | SMD-COMP2       | H5.2         |          | 43  |                 | /                |     | 60   |              | H2.1     | SMC-COMP1      | SMC2+          |       |

|        |                  |                 | HVDD0        |          | 44  | 1               | /                |     | 59   | <u> </u>     | HVSS1    | 1              |                |       |

|        |                  |                 |              |          |     | /               | 1                | ١   |      | <u> </u>     |          |                |                |       |

|        |                  |                 | HVSSO        |          | 45  | 1               |                  | 1   | 58   | 1            | HVDD1    |                |                |       |

|        | SMD2+            | SMD-COMP1       | H5.1         |          | 46  | 1               |                  | 1   | 57   | 1            | H2.2     | SMC-COMP2      | SMC1-          | 1     |

|        |                  | SMD-COMP0       |              |          | 47  | 1               |                  | 1   | 56   | <u> </u>     | H2.3     | SMC-COMP3      | SMC1+          | +     |

|        | CMDO             |                 |              |          |     | 1               |                  | \   |      |              |          |                |                |       |

|        | SMD2-            |                 |              |          | 48  |                 |                  | 1   | 55   | 1 7          | H3.0     | SMB-COMP0      | SMB2-          | 1 -   |

|        | SMA1+            | SMA-COMP3       |              |          | 40  | / NC            | = not connected. |     |      |              | 110.0    |                |                |       |

|        | SMA1+            |                 |              |          |     |                 | = not connected, |     |      |              |          |                |                |       |

|        | SMA1+<br>SMA1-   | SMA-COMP2       | H4.2         |          | 49  | / lea           | e vacant         |     | 54   |              | H3.1     | SMB-COMP1      | SMB2+          |       |

|        | SMA1+            |                 | H4.2<br>H4.1 | 2        |     | / lea           |                  |     |      |              |          |                |                |       |

**Fig. 2–2:** Pin assignment for PQFP128 package Note 1 denotes pins that will not be available in future 88-pin versions. Note 2 denotes pins that will not be available in future 104-pin versions.

## 2.3. Pin Function Description

(differing from document "CDC32xxG-C Automotive Controller - Family User Manual, CDC3205G-C Automotive Controller" (6251-579-1DS))

#### TEST2

For normal operation with internal code connect TEST2 to System Ground (no internal pull-down).

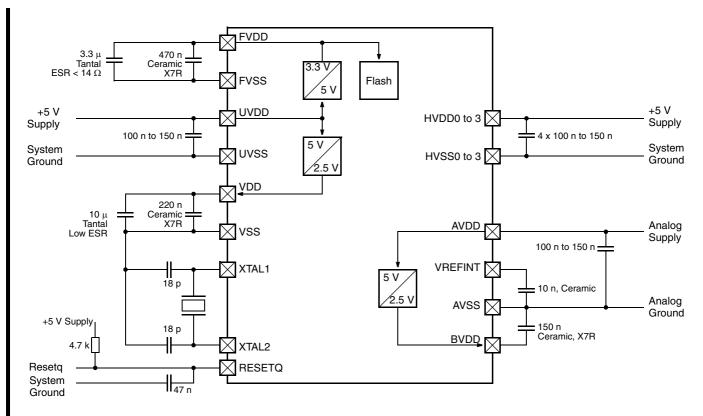

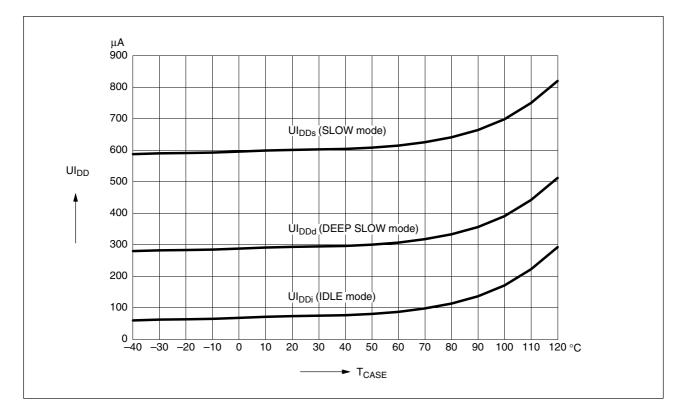

## 2.4. External Components

To provide effective decoupling and to improve EMC behavior, the small decoupling capacitors must be located as close to the supply pins as possible. The self-inductance of these capacitors and the parasitic inductance and capacitance of the interconnecting traces determine the self-resonant frequency of the decoupling network. Too low a frequency will reduce decoupling effectiveness, will increase RF emissions and may adversely affect device operation.

XTAL1 and XTAL2 quartz connections are especially sensitive to capacitive coupling from other PC board signals. It is strongly recommended to place quartz and oscillation capacitors as close to the pins as possible and to shield the XTAL1 and XTAL2 traces from other signals by embedding them in a VSS trace.

The RESETQ pin adjacent to XTAL2 should be supplied with a 47 nF capacitor, to prevent fast RESETQ transients from being coupled into XTAL2, to prevent XTAL2 from coupling into RESETQ, and to guarantee a time constant of  $\geq$ 200 µs sufficient for proper wake reset functionality.

# 3. Electrical Data

## 3.1. Absolute Maximum Ratings

Stresses beyond those listed in the "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these conditions is not implied. Exposure to absolute maximum ratings conditions for extended periods will affect device reliability.

This device contains circuitry to protect the inputs and outputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than absolute maximum-rated voltages to this high-impedance circuit.

**Table 3–1:** All voltages listed are referenced to ground ( $UV_{SS} = HV_{SSn} = AV_{SS} = 0$  V), except where noted. All ground pins except VSS must be connected to a low-resistive ground plane close to the IC.

| Symbol             | Parameter                                                                     | Pin Name                                | Min.                          | Max.                   | Unit |

|--------------------|-------------------------------------------------------------------------------|-----------------------------------------|-------------------------------|------------------------|------|

| V <sub>SUP</sub>   | Main supply voltage<br>Analog supply voltage<br>SM supply voltage             | UVDD<br>AVDD<br>HVDD0 HVDD3             | -0.3                          | 6.0                    | V    |

| V <sub>REG</sub>   | Flash supply voltage                                                          | FVDD                                    | -0.3                          | 4.0                    | V    |

|                    | Core supply voltage<br>PLL supply voltage                                     | VDD<br>BVDD                             | -0.3                          | 3.0                    | V    |

| I <sub>SUP</sub>   | Core supply current<br>Main supply current                                    | VDD, VSS,<br>UVDD, UVSS                 | -100                          | 100                    | mA   |

|                    | Analog supply current                                                         | AVDD, AVSS                              | -20                           | 20                     | mA   |

|                    | SM supply current<br>@ $T_{CASE}$ = 105 °C, duty factor = 0.71 <sup>1</sup> ) | HVDD0 HVDD3<br>HVSS0 HVSS3              | -250                          | 250                    | mA   |

|                    | Flash supply current                                                          | FVDD, FVSS                              | -50                           | 50                     | mA   |

|                    | PLL supply current                                                            | BVDD                                    | -20                           | 20                     | mA   |

| V <sub>in</sub>    | Input voltage                                                                 | U ports,<br>XTAL,RESETQ,<br>TEST, TEST2 | UV <sub>SS</sub> – 0.5        | UV <sub>DD</sub> + 0.7 | V    |

|                    |                                                                               | P ports<br>VREF                         | $\mathrm{UV}_\mathrm{SS}-0.5$ | AV <sub>DD</sub> + 0.7 | V    |

|                    |                                                                               | H ports                                 | HV <sub>SS</sub> – 0.5        | HV <sub>DD</sub> + 0.7 | V    |

| l <sub>in</sub>    | Input current                                                                 | all inputs                              | 0                             | 2                      | mA   |

| I <sub>o</sub>     | Output current                                                                | U ports,<br>RESETQ, WAITH               | -5                            | 5                      | mA   |

|                    |                                                                               | H ports                                 | -60                           | 60                     | mA   |

| t <sub>oshsl</sub> | Duration of short circuit to UVSS or UVDD, Port SLOW mode enabled             | U ports, except in DP mode              |                               | indefinite             | S    |

| Tj                 | Junction temperature under bias                                               |                                         | -45                           | 115                    | °C   |

|                    |                                                                               |                                         | -45                           | 125                    | °C   |

| Τ <sub>s</sub>     | Storage temperature                                                           |                                         |                               |                        |      |

## 3.2. Recommended Operating Conditions

#### Do not insert the device into a live socket. Instead, apply power by switching on the external power supply.

#### Keep $UV_{DD}=AV_{DD}$ during all power-up and power-down sequences.

Failure to comply with the above recommendations will result in unpredictable behavior of the device and may result in device destruction.

Functional operation of the device beyond those indicated in the "Recommended Operating Conditions" of this specification is not implied, may result in unpredictable behavior of the device and may reduce reliability and lifetime.

**Table 3–2:** All voltages listed are referenced to ground ( $UV_{SS} = HV_{SSn} = AV_{SS} = 0$  V), except where noted. All ground pins except VSS must be connected to a low-resistive ground plane close to the IC.

| Symbol                        | Parameter                                                           | Pin Name                                      | Min.                  | Тур.            | Max.                 | Unit    |

|-------------------------------|---------------------------------------------------------------------|-----------------------------------------------|-----------------------|-----------------|----------------------|---------|

| V <sub>SUP</sub>              | Main supply voltage<br>Analog supply voltage                        | UVDD = AVDD                                   | 3.5                   | 5               | 5.5                  | V       |

| HV <sub>SUP</sub>             | SM supply voltage                                                   | HVDDn                                         | 4.75                  | 5               | 5.25                 | V       |

| dV <sub>DD</sub>              | Ripple, peak-to-peak                                                | UVDD<br>AVDD<br>BVDD<br>FVDD<br>VDD           |                       |                 | 200                  | mV      |

| dV <sub>DD</sub> /dt          | Supply voltage up/down ramping rate                                 | UVDD<br>AVDD                                  |                       |                 | 20                   | V/μs    |

| f <sub>XTAL</sub>             | XTAL clock frequency                                                | XTAL1                                         | 4                     | 4               | 5                    | MHz     |

| f <sub>SYS</sub>              | CPU clock frequency, PLL on                                         |                                               | For a list o          | of available se | ettings see Tab      | le 4–1. |

| f <sub>BUS</sub>              | Program storage clock frequency,<br>PLL on                          |                                               |                       |                 |                      |         |

| V <sub>il</sub> <sup>1)</sup> | Automotive low input voltage                                        | U ports<br>H ports<br>P ports                 |                       |                 | $0.5 \times xV_{DD}$ | V       |

|                               | CMOS low input voltage                                              | U ports, TEST,<br>TEST2<br>H ports<br>P ports |                       |                 | $0.3 \times xV_{DD}$ | V       |

| V <sub>ih</sub> <sup>1)</sup> | Automotive high input voltage                                       | U ports<br>H ports<br>P ports                 | $0.86 \times xV_{DD}$ |                 |                      | V       |

|                               | CMOS high input voltage                                             | U ports,TEST,<br>TEST2<br>H ports<br>P ports  | $0.7 \times xV_{DD}$  |                 |                      | V       |

| RV <sub>il</sub>              | Reset active input voltage                                          | RESETQ                                        |                       |                 | 0.75                 | V       |

| WRV <sub>il</sub>             | Reset active input voltage during power-saving modes and wake reset | RESETQ                                        |                       |                 | 0.4                  | V       |

| RV <sub>im</sub>              | Reset inactive and alarm active input voltage                       | RESETQ                                        | 1.5                   |                 | 2.3                  | V       |

| <b>Table 3–2:</b> All voltages listed are referenced to ground ( $UV_{SS} = HV_{SSn} = AV_{SS} = 0$ V), except where noted. All ground pins |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| except VSS must be connected to a low-resistive ground plane close to the IC.                                                               |

| Symbol            | Parameter                                                                   | Pin Name | Min.                        | Тур. | Max.                | Unit |

|-------------------|-----------------------------------------------------------------------------|----------|-----------------------------|------|---------------------|------|

| RV <sub>ih</sub>  | Reset inactive and alarm inactive input voltage                             | RESETQ   | 3.2                         |      |                     | V    |

| WRV <sub>ih</sub> | Reset inactive input voltage during<br>power-saving modes and wake<br>reset | RESETQ   | UV <sub>DD</sub><br>- 0.4 V |      |                     | V    |

| V <sub>REFi</sub> | Ext. ADC reference input voltage                                            | VREF     | 2.56                        |      | AV <sub>DD</sub>    | V    |

| PVi               | ADC port input voltage referenced to ext. VREF reference                    | P ports  | 0                           |      | V <sub>REFi</sub>   | V    |

|                   | ADC port input voltage referenced to int. VREFINT reference                 |          | 0                           |      | V <sub>REFINT</sub> |      |

### 3.3. Characteristics

Listed are only those characteristics that differ from Chapter 3.3 of Document "CDC32xxG-C Automotive Controller - Family User Manual, CDC3205G-C Automotive Controller" (6251-579-1DS). All not differing characteristics, that are not listed here, apply, but in a T<sub>CASE</sub> temperature range extended to -40 °C to +105 °C.

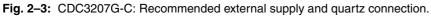

**Table 3–3:**  $UV_{SS} = FV_{SS} = HV_{SSn} = AV_{SS} = 0 V$ , 3.5 V <  $AV_{DD} = UV_{DD} < 5.5 V$ , 4.75 V <  $HV_{DDn} < 5.25 V$ ,  $T_{CASE} = -40 °C$  to+105 °C,  $f_{XTAL} = 5 MHz$ , external components according to Fig. 2–3 (unless otherwise noted).

| Symbol               | Parameter                                                           | Pin Na.                      | Min.              | Тур. <sup>1)</sup>    | Max.                 | Unit         | Test Conditions                                                                                                                                        |

|----------------------|---------------------------------------------------------------------|------------------------------|-------------------|-----------------------|----------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Package              |                                                                     | <u> </u>                     | <u>.</u>          | <u> </u>              |                      | +            |                                                                                                                                                        |

| R <sub>thjc</sub>    | Thermal resistance from junction to case                            |                              |                   | 9                     |                      | K/W          | measured on Micronas<br>typical 2-layer board,                                                                                                         |

| R <sub>thja</sub>    | Thermal resistance from junction to ambient                         |                              |                   | 31                    |                      | K/W          | <ul> <li>1s1p, described in document "Integrated Circuits</li> <li>Thermal Characterization of Packages" (6200 266-1E) (modified JESD-51.3)</li> </ul> |

| Supply Cu            | rrents (CMOS levels on all input                                    | its, i.e., V <sub>il</sub> = | $xV_{SS} \pm 0.3$ | V and V <sub>ih</sub> | = xV <sub>DD</sub> ± | 0.3 V, no lo | bads on outputs)                                                                                                                                       |

| UI <sub>DDp</sub>    | UVDD PLL mode supply<br>current                                     | UVDD                         |                   |                       | 65<br>120            | mA           | f <sub>SYS</sub> = 24 MHz<br>f <sub>SYS</sub> = 50 MHz                                                                                                 |

| UI <sub>DDprog</sub> | UVDD Flash program sup-<br>ply current                              | UVDD                         |                   |                       | 45                   | mA           | Flash Write/Erase, all modules off, <sup>2)</sup>                                                                                                      |

| UI <sub>DDf</sub>    | UVDD FAST mode supply<br>current                                    | UVDD                         |                   |                       | 18                   | mA           | all modules off, <sup>2)</sup>                                                                                                                         |

| UI <sub>DDs</sub>    | UVDD SLOW mode supply current                                       | UVDD                         |                   | see<br>Fig. 3–1       | 1.4                  | mA           | all modules off, <sup>2) 3)</sup>                                                                                                                      |

|                      | values describe typical behavi<br>nded Operating Conditions ap      |                              |                   |                       |                      | herwise n    | oted), with typical                                                                                                                                    |

|                      | ay be exceeded with unusual ha<br>d with external clock. Add typica | -                            | -                 | n on quartz           | with SR0             | ).XTAL=0 (   | Oscillator RUN mode).                                                                                                                                  |

| Symbol             | Parameter                             | Pin Na.                | Min. | Typ. <sup>1)</sup> | Max. | Unit | Test Conditions                          |

|--------------------|---------------------------------------|------------------------|------|--------------------|------|------|------------------------------------------|

| UI <sub>DDd</sub>  | UVDD DEEP SLOW mode<br>supply current | UVDD                   |      | see<br>Fig. 3–1    | 0.9  | mA   | all modules off, 3)                      |

| UI <sub>DDw</sub>  | UVDD WAKE mode supply current         | UVDD                   | 0    | 20                 | 50   | μA   | RC and XTAL oscillator off               |

| UI <sub>DDst</sub> | UVDD STANDBY mode<br>supply current   | UVDD                   |      | 35                 | 75   | μΑ   | RC oscillator on, XTAL off               |

|                    |                                       | UVDD                   |      | 60                 | 100  | μA   | XTAL oscillator on, RC off 3)            |

| UI <sub>DDi</sub>  | UVDD IDLE mode supply current         | UVDD                   |      | 50                 | 475  | μA   | RC oscillator on, XTAL off               |

|                    |                                       |                        |      | see<br>Fig. 3–1    | 500  | μA   | XTAL oscillator on, RC off <sup>3)</sup> |

| Al <sub>DDa</sub>  | AVDD active supply current            | AVDD                   |      | 0.35               | 0.6  | mA   | ADC on, PLL off                          |

|                    |                                       |                        |      |                    | 2    | mA   | ADC, buffer and PLL or                   |

| Al <sub>DDq</sub>  | Quiescent supply current              | AVDD                   | 0    | 1                  | 10   | μA   | ADC and PLL off                          |

| HI <sub>DDq</sub>  |                                       | Sum of<br>all<br>HVDDn | 0    | 1                  | 40   | μΑ   | no output activity,<br>SM module off     |

| Inputs             |                                       |                        |      | •                  |      |      |                                          |

| li                 | Input leakage current                 | TEST2                  | -1   |                    | 1    | μA   | $0 < V_i < UV_{DD}$                      |

**Table 3–3:**  $UV_{SS} = FV_{SS} = HV_{SSn} = AV_{SS} = 0 V$ , 3.5 V <  $AV_{DD} = UV_{DD} < 5.5 V$ , 4.75 V <  $HV_{DDn} < 5.25 V$ ,  $T_{CASE} = -40 °C$  to+105 °C,  $f_{XTAL} = 5 MHz$ , external components according to Fig. 2–3 (unless otherwise noted).

<sup>3)</sup> Measured with external clock. Add typically 120  $\mu$ A for operation on quartz with SR0.XTAL=0 (Oscillator RUN mode).

Fig. 3–1: Typical UI<sub>DD</sub> characteristics over temperature @ f<sub>XTAL</sub> = 4 MHz, 5 V

## 3.4. Recommended Quartz Crystal Characteristics

See Chapter 3.4 of document "CDC32xxG-C Automotive Controller - Family User Manual, CDC3205G-C Automotive Controller" (6251-579-1DS).

# 4. CPU and Clock System

#### 4.1. Recommended Register Settings

Settings for PMF, IOP and WSR differing from those given in Table 4–1 must not be used and may result in undefined behavior. It is required not to operate I/O faster than Flash. Suppression Strength (SUP) and Clock Tolerance (TOL) may be varied between zero and the values for strong settings according to the rules in Section 4.4.2 of the document "CDC32xxG-C Automotive Controller - Family User Manual, CDC3205G-C Automotive Controller" (6251-579-1DS). The given limits must not be exceeded.

| f <sub>XTAL</sub> | CPU              |              | Flash            |      | I/O                                 |             | ER                            | MC.E | OM = | 1    |     |     | ER  | MC.E | OM =           | 2 or 3      | 3              |              |

|-------------------|------------------|--------------|------------------|------|-------------------------------------|-------------|-------------------------------|------|------|------|-----|-----|-----|------|----------------|-------------|----------------|--------------|

|                   |                  |              |                  |      |                                     |             | We                            | ak   | No   | rmal | Str | ong | We  | ak   | No             | rmal        | Stre           | ong          |

|                   | f <sub>SYS</sub> | PLLC.<br>PMF | f <sub>BUS</sub> | WSR  | f <sub>IO</sub> =<br>f <sub>0</sub> | IOC.<br>IOP | SUP                           | TOL  | SUP  | TOL  | SUP | TOL | SUP | TOL  | SUP            | TOL         | SUP            | TOL          |

| 4                 | 16               | 3            | 8                | 0x11 | 8                                   | 1           | 0                             | 8    | 0    | 14   | 0   | 15  | 8   | 4    | 14             | 7           | 22             | 11           |

|                   | 24               | 5            | 8                | 0x22 | 8                                   | 2           | 0                             | 12   | 0    | 15   | 0   | 15  | 12  | 6    | 21             | 11          | 31             | 12           |

|                   |                  |              | 12               | 0x11 |                                     |             | 0                             | 10   | 0    | 10   | 0   | 10  | 12  | 2    | 21             | 2           | 33             | 2            |

|                   | 32               | 7            | 8                | 0x33 | 8                                   | 3           | 0                             | 12   | 0    | 12   | 0   | 12  | 16  | 8    | 28             | 12          | 31             | 12           |

|                   |                  |              | 10.67            | 0x22 |                                     |             | 0                             | 12   | 0    | 12   | 0   | 12  | 16  | 8    | 19<br>23<br>28 | 9<br>7<br>6 | 19<br>23<br>37 | 9<br>7<br>6  |

|                   | 40               | 9            | 10               | 0x33 | 8                                   | 4           | 0                             | 6    | 0    | 6    | 0   | 6   | 21  | 6    | 35             | 6           | 37             | 6            |

|                   | 48               | 11           | 12               | 0x33 | 8                                   | 5           | 0                             | 1    | 0    | 1    | 0   | 1   | 25  | 1    | 42             | 1           | 42             | 1            |

| 5                 | 10               | 1            | 10               | 0x00 | 10                                  | 0           | 0                             | 5    | 0    | 8    | 0   | 14  | 5   | 3    | 8              | 4           | 14             | 7            |

|                   | 20               | 3            | 10               | 0x11 | 10                                  | 1           | 0                             | 10   | 0    | 15   | 0   | 15  | 10  | 5    | 17             | 8           | 28             | 8            |

|                   | 30               | 5            | 10               | 0x22 | 10                                  | 2           | 0                             | 14   | 0    | 14   | 0   | 14  | 15  | 8    | 24<br>26       | 12<br>11    | 28<br>30<br>35 | 10<br>9<br>8 |

|                   | 40               | 7            | 10               | 0x33 | 10                                  | 3           | 0                             | 6    | 0    | 6    | 0   | 6   | 21  | 6    | 35             | 6           | 37             | 6            |

|                   | 50               | 9            | 12.5             | 0x33 | 10                                  | 4           | set ERMC.EOM=0 set ERMC.EOM=0 |      |      |      |     |     |     |      |                |             |                |              |

Table 4–1: PLL and ERM modes: Recommended settings and resulting operating frequencies (MHz)

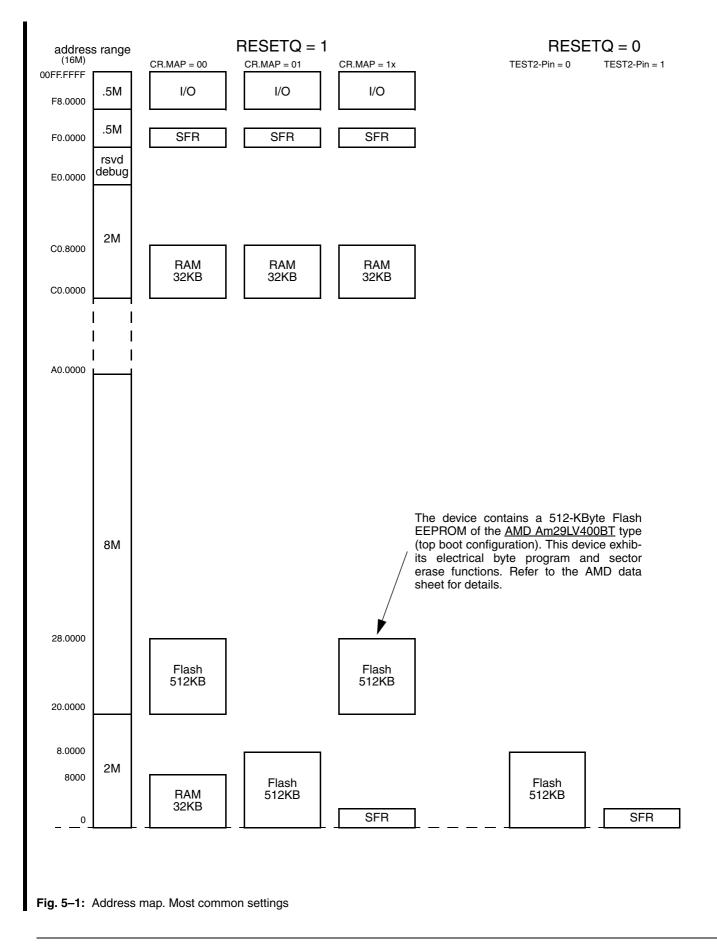

# 5. Memory and Special Function ROM (SFR) System

# CDC 3207G-C3

#### Warning:

Since only a 24-bit address space is supported, do not use addresses outside this range when debugging this device.

# 6. Core Logic

## 6.1. Control Word (CW)

A number of important system configuration properties are selectable during device start-up by means of a unique control word (CW).

#### 6.1.1. Reset Active

At the end of the reset period, the device fetches this CW from address locations 0x20 to 0x23 of a source that is determined by the state of pins TEST and TEST2 and flag MFPLR.MFPL, see Table 6–1 for MCM parts, Table 6–2 for ROM parts.

Table 6–1: CW fetch in MCM parts (QFP128)

| "Control Word Fetch"<br>desired from                                                                          | Necessary Reset Con-<br>figuration |      |                 |  |  |  |

|---------------------------------------------------------------------------------------------------------------|------------------------------------|------|-----------------|--|--|--|

|                                                                                                               | TEST2                              | TEST | MFPL            |  |  |  |

| Int. Flash                                                                                                    | 0                                  | 0    | x               |  |  |  |

| Int. Flash                                                                                                    | 0                                  | 1    | 1               |  |  |  |

| Ext. via multifunction port                                                                                   |                                    |      | 0 <sup>1)</sup> |  |  |  |

| Int. special-function ROM                                                                                     | 1                                  | х    | х               |  |  |  |

| <ul> <li><sup>1)</sup> Only available after a non-power-on RESET with MFPL</li> <li>= 0 set before</li> </ul> |                                    |      |                 |  |  |  |

As Table 6–1 shows, the device disables external access (through the multifunction port) to internal code, as long as MFPLR.MFPL is 1 (= state after UVDD power-up). Setting it to 0 requires internal SW. By this means, an effective device lock mechanism is implemented, which prevents unauthorized access to internal SW.

In ROM parts, flag MFPLR.MFPL is available, but does not lock the multifunction port. Thus Table 6–1 reduces to Table 6–2.

| "Control Word Fetch" desired<br>from | Necessary Reset config. of pins |      |  |  |  |

|--------------------------------------|---------------------------------|------|--|--|--|

|                                      | TEST2                           | TEST |  |  |  |

| Internal ROM                         | 0                               | 0    |  |  |  |

| External via multifunction port      | 0                               | 1    |  |  |  |

| Int. special-function ROM            | 1                               | x    |  |  |  |

#### Table 6–2: CW fetch in ROM parts (QFP128)

#### 6.1.2. Reset Inactive

When exiting Reset, the CW is read and stored in the control register (CR) and the system will start up according to the configuration defined therein.

Normally the CW is fetched from the same memory that the system will start executing code from. Table 6–3 gives fixed CWs for a list of the most commonly used configurations.

Table 6–3:

Some common system configurations and the corresponding CW setting

| Part | "Program Start" desired from | Additional desired properties | Necessary CW |        |  |

|------|------------------------------|-------------------------------|--------------|--------|--|

| Туре |                              |                               | 31:16        | 15:0   |  |

| MCM  | int. 16-bit Flash            | -                             | Don't care   | 0x7F5F |  |

| ROM  | int. 16-bit ROM              | -                             | Don't care   | 0x7F5F |  |

# 7. Hardware Options

## 7.1. Functional Description

Hardware options are available in several areas to adapt the IC function to the host system requirements. For details see the document "CDC32xxG-C Automotive Controller - Family User Manual, CDC3205G-C Automotive Controller" (6251-579-1DS).

Setting hardware options is carried out in two steps:

1. selection is effected by programming dedicated address locations in the HW options field with the desired options' code.

2. activation is effected by copying the HW options field to the corresponding HW options' registers at least once after each reset.

In EMU and MCM devices, all hardware options are soft-ware-progammable.

In mask ROM derivatives, the clock options and the watchdog, clock and supply monitors are hard-wired, according to the HW options field of the ROM code hex file. Those options can only be altered by changing a production mask.

To ensure compatible option settings in this IC and mask ROM derivatives when run with the same ROM code, it is mandatory to always write the HW options field to the HW option registers directly after reset.

## 8. Differences

This chapter describes differences between this document and predecessor document: "CDC3207G-C Automotive Controller Specification" (6251-589-1PD).

| Section                                      | Description                                                                                                                                               |  |  |  |  |  |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|