### **Description**

The MK2308-2 is a low jitter, low skew, high performance Phase-Lock Loop (PLL) based zero delay buffer for high speed applications. Based on ICS' proprietary low jitter PLL techniques, the device provides eight low skew outputs at speeds up to 160 MHz at 3.3 V. The MK2308-2 includes a bank of four outputs running at 1/2X. In the zero delay mode, the rising edge of the input clock is aligned with the rising edges of all eight outputs. Compared to competitive CMOS devices, the MK2308-2 has the lowest jitter.

#### **Features**

- Packaged in 16-pin SOIC

- Zero input-output delay

- Four 1X outputs plus four 1/2X outputs

- Output to output skew is less than 250 ps

- Output clocks up to 160 MHz at 3.3 V

- · Ability to generate 2X the input

- Full CMOS outputs with 18 mA output drive capability at TTL levels at 3.3 V

- Spread Smart<sup>TM</sup> technology works with spread spectrum clock generators

- Advanced, low power, sub micron CMOS process

- Operating voltage of 3.3 V or 5 V

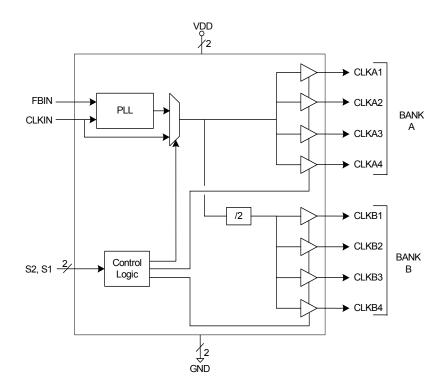

### **Block Diagram**

# **Pin Assignment**

|         |                    |     | 1     |

|---------|--------------------|-----|-------|

| CLKIN   | 1                  | 16  | FBIN  |

| CLKA1   | 2                  | 15  | CLKA4 |

| CLKA2   | 3                  | 14  | CLKA3 |

| VDD _   | 4                  | 13  | □ VDD |

| GND _   | 5                  | 12  | GND   |

| CLKB1 _ | 6                  | 11  | CLKB4 |

| CLKB2   | 7                  | 10  | CLKB3 |

| S2 _    | 8                  | 9   | S1    |

|         |                    |     |       |

|         | 16-pin (150 mil) S | OIC |       |

|         | (                  | 0.0 |       |

# **Feedback Configuration Table**

| Feedback From | CLKA1:A4 | CLKB1:B4 |

|---------------|----------|----------|

| Bank A        | CLKIN    | CLKIN/2  |

| Bank B        | 2XCLKIN  | CLKIN    |

# **Output Clock Mode Select Table**

| S2 | S1 | Clocks A1:A4               | Clocks B1:B4 Internet Generation |                             | PLL Status |

|----|----|----------------------------|----------------------------------|-----------------------------|------------|

| 0  | 0  | Tri-state (high impedance) | Tri-state (high impedance)       | None                        | On         |

| 0  | 1  | Running                    | Tri-state (high impedance)       | PLL                         | On         |

| 1  | 0  | Running                    | Running                          | Buffer only (no zero delay) | Off        |

| 1  | 1  | Running                    | Running                          | PLL                         | On         |

# **Pin Descriptions**

| Pin<br>Number | Pin<br>Name | Pin<br>Type | Pin Description                                                            |

|---------------|-------------|-------------|----------------------------------------------------------------------------|

| 1             | CLKIN       | Input       | Clock input. Connect to input clock source.                                |

| 2 - 3         | CLKA1:A4    | Output      | Clock A bank of four outputs.                                              |

| 4             | VDD         | Power       | Power supply. Connect pin to same voltage as pin 13 (either 3.3 V or 5 V). |

| 5             | GND         | Power       | Connect to ground.                                                         |

| 6 - 7         | CLKB1:B4    | Output      | Clock B bank of four outputs. These are low skew divide by two of bank A.  |

| 8             | S2          | Input       | Select input 2. Selects mode for outputs per table above.                  |

| 9             | S1          | Input       | Select input 1. Selects mode for outputs per table above.                  |

| 10 - 11       | CLKB1:B4    | Output      | Clock B bank of four outputs. These are low skew divide by two of bank A.  |

| 12            | GND         | Power       | Connect to ground.                                                         |

| 13            | VDD         | Power       | Power supply. Connect pin to same voltage as pin 4 (either 3.3 V or 5 V).  |

| 14 - 15       | CLKA1:A4    | Output      | Clock A bank of four outputs.                                              |

| 16            | FBIN        | Input       | Feedback input. Determines outputs per table above.                        |

#### **External Components**

The MK2308-2 requires a minimum number of external components for proper operation. Decoupling capacitors of  $0.1\mu F$  should be connected between VDD and GND, as close to the part as possible. A  $33\Omega$  series terminating resistor should be used on each clock output to reduce reflections.

### **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the MK2308-2. These ratings, which are standard values for ICS commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Item                          | Rating              |

|-------------------------------|---------------------|

| Supply Voltage, VDD           | 7 V                 |

| All Inputs and Outputs        | -0.5 V to VDD+0.5 V |

| Ambient Operating Temperature | 0 to +70 °C         |

| Storage Temperature           | -65 to +150 °C      |

| Junction Temperature          | 175 °C              |

| Soldering Temperature         | 260 °C              |

#### **Recommended Operation Conditions**

| Parameter                                         | Min. | Тур. | Max. | Units |

|---------------------------------------------------|------|------|------|-------|

| Ambient Operating Temperature                     | 0    |      | +70  | °C    |

| Power Supply Voltage (measured in respect to GND) | +3.0 |      | +5.5 | V     |

#### **DC Electrical Characteristics**

**VDD=3.3 V \pm 10\%**, Temp 0 to  $+70^{\circ}$  /-40 to  $+85^{\circ}$  C

| Parameter           | Symbol          | Conditions               | Min.      | Тур.  | Max.      | Units |

|---------------------|-----------------|--------------------------|-----------|-------|-----------|-------|

| Operating Voltage   | VDD             |                          | 3.0       |       | 5.5       | V     |

| Input High Voltage  | V <sub>IH</sub> | CLKIN pin only           | (VDD/2)+1 | VDD/2 |           | V     |

| Input Low Voltage   | V <sub>IL</sub> | CLKIN pin only           |           | VDD/2 | (VDD/2)-1 | V     |

| Input High Voltage  | V <sub>IH</sub> |                          | 2         |       |           | V     |

| Input Low Voltage   | V <sub>IL</sub> |                          |           |       | 0.8       | V     |

| Output High Voltage | V <sub>OH</sub> | I <sub>OH</sub> = -18 mA | 2.4       |       |           | V     |

| Output Low Voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 18 mA  |           |       | 0.4       | V     |

| Output High Voltage | V <sub>OH</sub> | $I_{OH} = -5 \text{ mA}$ | VDD-0.4   |       |           | V     |

| Parameter                                  | Symbol          | Conditions         | Min. | Тур. | Max. | Units |

|--------------------------------------------|-----------------|--------------------|------|------|------|-------|

| Operating Supply Current<br>100 MHz, CLKIN | IDD             | No Load<br>S1=S2=1 |      | 44   |      | mA    |

| Short Circuit Current                      | Ios             | Each output        |      | ± 65 |      | mA    |

| Input Capacitance                          | C <sub>IN</sub> | S1, S1, FBIN       |      | 7    |      | pF    |

### **AC Electrical Characteristics**

**VDD = 3.3V ±10%**, Temp 0 to  $+70^{\circ}/-40$  to  $+85^{\circ}$  C

| Parameter                                   | Symbol            | Conditions                                       | Min. | Тур. | Max. | Units |

|---------------------------------------------|-------------------|--------------------------------------------------|------|------|------|-------|

| Input Frequency                             |                   | FBIN to CLKA1<br>S1=S2=1                         | 20   |      | 160  | MHz   |

| Output Frequency                            |                   | FBIN to CLKA1<br>S1=S2=1                         | 20   |      | 160  | MHz   |

| Output Rise Time                            | t <sub>OR</sub>   | 0.8 to 2.0 V, C <sub>L</sub> =30 pF              |      |      | 1.5  | ns    |

| Output Fall Time                            | t <sub>OF</sub>   | 0.8 to 2.0 V, C <sub>L</sub> =30 pF              |      |      | 1.5  | ns    |

| Output Clock Duty Cycle                     |                   | at 1.4V                                          | 40   | 50   | 60   | %     |

| Device to Device skew, equally loaded       |                   | rising edges at VDD/2                            |      |      | 700  | ps    |

| Output to Output skew, equally loaded       |                   | rising edges at VDD/2                            |      |      | 200  | ps    |

| Maximum Absolute Jitter                     |                   |                                                  |      | 300  |      | ps    |

| Cycle to Cycle Jitter                       |                   | 30 pF loads<br>66.67 MHz outputs                 |      |      | 400  | ps    |

|                                             |                   | 15 pF loads<br>66.67 MHz outputs                 |      |      | 400  | ps    |

| Skew from Output Bank A to<br>Output Bank B |                   | All outputs equally loaded                       |      |      | 400  | ps    |

| Delay CLKIN Rising Edge to FBIN Rising Edge |                   | measured at VDD/2                                |      |      | ±250 | ps    |

| PLL Lock Time                               | t <sub>LOCK</sub> | Stable power supply, valid clocks on CLKIN, FBIN |      |      | 1    | ms    |

### **Thermal Characteristics**

| Parameter                           | Symbol            | Conditions     | Min. | Тур. | Max. | Units |

|-------------------------------------|-------------------|----------------|------|------|------|-------|

| Thermal Resistance Junction to      | $\theta_{JA}$     | Still air      |      | 120  |      | °C/W  |

| Ambient                             | $\theta_{JA}$     | 1 m/s air flow |      | 115  |      | °C/W  |

|                                     | $\theta_{\sf JA}$ | 3 m/s air flow |      | 105  |      | °C/W  |

| Thermal Resistance Junction to Case | $\theta_{\sf JC}$ |                |      | 58   |      | °C/W  |

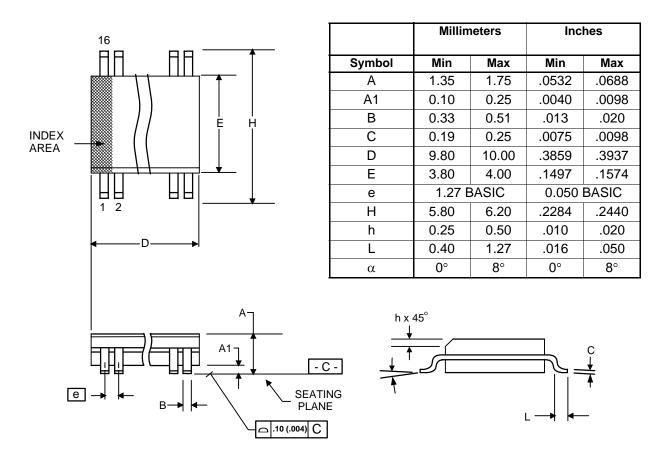

#### Package Outline and Package Dimensions (16-pin SOIC, 150 Mil. Narrow Body)

Package dimensions are kept current with JEDEC Publication No. 95

## **Ordering Information**

| Part / Order Number | Marking     | Shipping packaging | Package     | Temperature   |

|---------------------|-------------|--------------------|-------------|---------------|

| MK2308S-2           | MK2308S-2   | Tubes              | 16-pin SOIC | 0 to 70° C    |

| MK2308S-2T          | MK2308S-2T  | Tape and Reel      | 16-pin SOIC | 0 to 70° C    |

| MK2308S-2I          | MK2308S-2I  | Tubes              | 16-pin SOIC | -40 to +85° C |

| MK2308S-2IT         | MK2308S-2IT | Tape and Reel      | 16-pin SOIC | -40 to +85° C |

While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems (ICS) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not recommended without additional processing by ICS. ICS reserves the right to change any circuitry or specifications without notice. ICS does not authorize or warrant any ICS product for use in life support devices or critical medical instruments.