# AN1149NFHK

# 6-ch DC-DC Converter

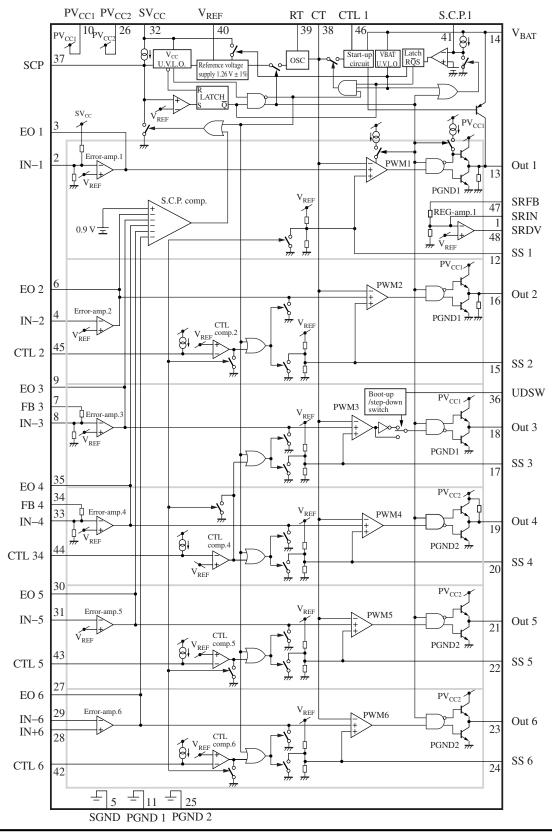

### Overview

4 channels of step-up, 1 channel of step-down and 1 channel of step-up/down voltage, 6 channels in total have been integrated onto a single chip. Each channel can be remote-controlled and work with two dry cells. A high precision output voltage can be obtained thanks to the accurate reference of  $V_{REF} \pm 1\%$ .

#### Features

- Low voltage operation (1.5 V min.)

- High precision reference voltage (±1%)

- Remote control for each channel

#### Applications

• Digital still cameras

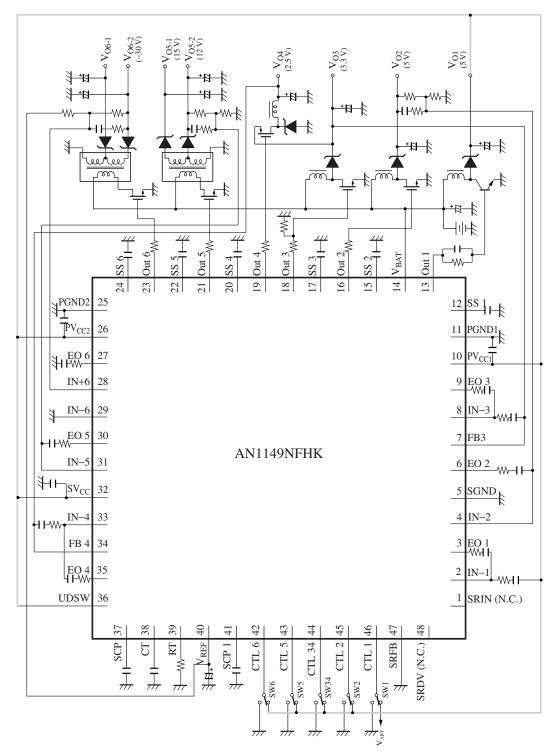

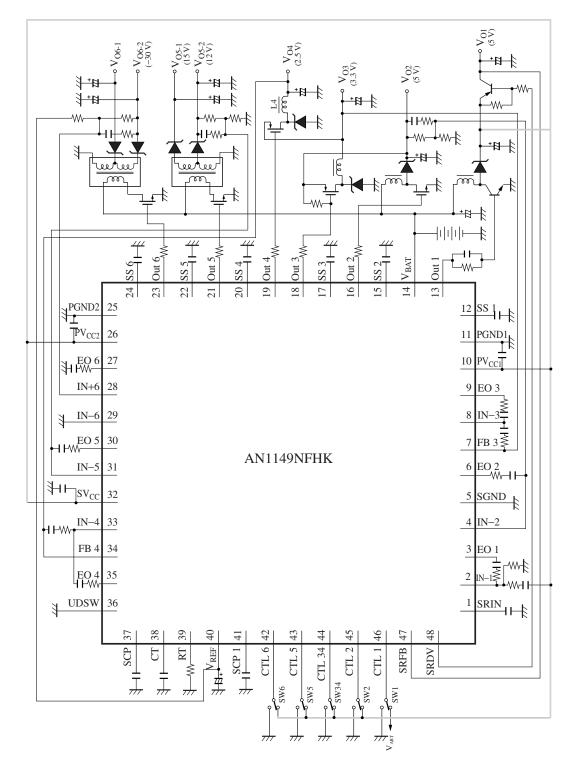

#### Block Diagram

#### Pin Descriptions

| Pin No. | Symbol            | Description                                | Pin No. | Symbol           | Description                                       |

|---------|-------------------|--------------------------------------------|---------|------------------|---------------------------------------------------|

| 1       | SRIN              | Regulator amplifier input pin              | 27      | EO 6             | Output pin for part-6 error amplifier             |

| 2       | IN-1              | Inverse input for part-1 error amplifier   | 28      | IN+6             | Non-inverted input pin for part-6 error amplifier |

| 3       | EO 1              | Output for part-1 error amplifier          | 29      | IN-6             | Inverted input pin for part-6 error amplifier     |

| 4       | IN-2              | Inverse input for part-2 error amplifier   | 30      | EO 5             | Output pin for part-5 error amplifier             |

| 5       | SGND              | Signal GND pin                             | 31      | IN-5             | Inverted input pin for part-5 error amplifier     |

| 6       | EO 2              | Output for part-2 error amplifier          | 32      | SV <sub>CC</sub> | Supply voltage application pin for signal block   |

| 7       | FB 3              | CH 3 output voltage detection pin          | 33      | IN-4             | Inverted input pin for part-4 error amplifier     |

| 8       | IN-3              | Inverse input for part-3 error amplifier   | 34      | FB 4             | CH 4 output voltage detection pin                 |

| 9       | EO 3              | Output for part block-3 error amplifier    | 35      | EO 4             | Output pin for part-4 error amplifier             |

| 10      | PV <sub>CC1</sub> | Voltage application pin 1 for output block | 36      | UDSW             | Step-down output setup pin for CH 3               |

| 11      | PGND1             | Output GND pin 1                           | 37      | SCP              | Short-circuit protection time constant            |

| 12      | SS-1              | CH 1 soft start setting pin                |         |                  | setup capacitance connection pin for CH 2-6       |

| 13      | Out-1             | Push-pull output pin for out-1 block       | 38      | СТ               | Oscillator frequency setup capacitor              |

| 14      | V <sub>BAT</sub>  | Battery voltage application pin            |         |                  | connection pin                                    |

| 15      | SS-2              | CH 2 soft start setting pin                | 39      | RT               | Oscillator frequency setup resistor               |

| 16      | Out-2             | Totem pole output pin for out-2 block      |         |                  | connection pin                                    |

| 17      | SS-3              | CH 3 soft start setting pin                | 40      | V <sub>REF</sub> | Reference voltage output pin                      |

| 18      | Out-3             | Totem pole output pin for out-3 block      | 41      | SCP 1            | Output short-circuit protection time constant     |

| 19      | Out-4             | Totem pole output pin for out-4 block      |         |                  | setup capacitor connection pin for CH 1           |

| 20      | SS-4              | CH 4 soft start setting pin                | 42      | CTL 6            | CH 6. on-off control pin                          |

| 21      | Out-5             | Totem pole output pin for out-5 block      | 43      | CTL 5            | CH 5. on-off control pin                          |

| 22      | SS-5              | CH 5 soft start setting pin                | 44      | CTL 34           | CH 3, CH 4. on-off control pin                    |

| 23      | Out-6             | Totem pole output pin for out-6 block      | 45      | CTL 2            | CH 2. on-off control pin                          |

| 24      | SS-6              | CH 6 soft start setting pin                | 46      | CTL 1            | CH 1. on-off control pin                          |

| 25      | PGND2             | Output GND pin 2                           | 47      | SRFB             | Regulator amplifier output voltage detection pin  |

| 26      | PV <sub>CC2</sub> | Voltage application pin 2 for output block | 48      | SRDV             | Regulator amplifier drive pin                     |

#### Absolute Maximum Ratings

| Parameter                                                                     | Symbol            | Rating           | Unit |

|-------------------------------------------------------------------------------|-------------------|------------------|------|

| Supply voltage                                                                | SV <sub>CC</sub>  | 9.2              | V    |

| Power $V_{CC1}$ allowable application voltage                                 | PV <sub>CC1</sub> | 9.2              | V    |

| Power $V_{CC2}$ allowable application voltage                                 | PV <sub>CC2</sub> | 9.2              | V    |

| Battery input allowable application voltage                                   | V <sub>BAT</sub>  | 9.2              | V    |

| Allowable application voltage to regulator output voltage detection input pin | V <sub>SRFB</sub> | SV <sub>CC</sub> | V    |

Note) 1. Do not apply external currents or voltages to any pins not specifically mentioned.

For the circuit currents, '+' denotes current flowing into the IC, and '-' denotes current flowing out of the IC.

2. Except for the power dissipation, operating ambient temperature and storage temperature, all ratings are for  $T_a = 25^{\circ}C$ .

#### Absolute Maximum Ratings (continued)

| Parameter                                                         | Symbol             | Rating                   | Unit |

|-------------------------------------------------------------------|--------------------|--------------------------|------|

| Step up / down switch input<br>allowable application voltage *2   | V <sub>UDSW</sub>  | SV <sub>CC</sub>         | V    |

| Allowable application voltage to output voltage detection input 3 | V <sub>FB3</sub>   | SV <sub>CC</sub>         | V    |

| Allowable application voltage to output voltage detection input 4 | V <sub>FB4</sub>   | SV <sub>CC</sub>         | V    |

| Allowable application voltage to control input 1                  | V <sub>CTL1</sub>  | $V_{BAT}$                | V    |

| Allowable application voltage to control input 2                  | V <sub>CTL2</sub>  | SV <sub>CC</sub>         | V    |

| Allowable application voltage to control input 3, 4               | V <sub>CTL34</sub> | SV <sub>CC</sub>         | V    |

| Allowable application voltage to control input 5                  | V <sub>CTL5</sub>  | SV <sub>CC</sub>         | V    |

| Allowable application voltage to control input 6                  | V <sub>CTL6</sub>  | SV <sub>CC</sub>         | V    |

| Error amplifier allowable application voltage to input pin        | V <sub>IN</sub>    | -0.2 to SV <sub>CC</sub> | V    |

| Supply current                                                    | I <sub>CC</sub>    | _                        | mA   |

| Output 2 allowable peak current                                   | I <sub>OP2</sub>   | ±400                     | mA   |

| Output 3 allowable peak current                                   | I <sub>OP3</sub>   | ±400                     | mA   |

| Output 4 allowable peak current                                   | I <sub>OP4</sub>   | ±400                     | mA   |

| Output 5 allowable peak current                                   | I <sub>OP5</sub>   | ±400                     | mA   |

| Output 6 allowable peak current                                   | I <sub>OP6</sub>   | ±400                     | mA   |

| Output 1 allowable sequence current                               | I <sub>O1</sub>    | -50                      | mA   |

| Output 2 allowable sequence current                               | I <sub>O2</sub>    | ±100                     | mA   |

| Output 3 allowable sequence current                               | I <sub>O3</sub>    | ±100                     | mA   |

| Output 4 allowable sequence current                               | I <sub>O4</sub>    | ±100                     | mA   |

| Output 5 allowable sequence current                               | I <sub>O5</sub>    | ±100                     | mA   |

| Output 6 allowable sequence current                               | I <sub>O6</sub>    | ±100                     | mA   |

| Reference voltage allowable application current                   | I <sub>REF</sub>   | -5                       | mA   |

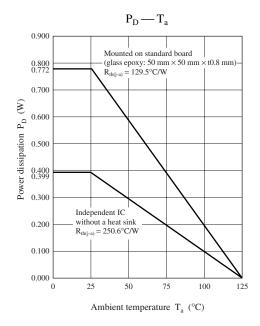

| Power dissipation *1                                              | P <sub>D</sub>     | 160                      | mW   |

| Operating ambient temperature                                     | T <sub>opr</sub>   | -20 to +85               | °C   |

| Storage temperature                                               | T <sub>stg</sub>   | -55 to +125              | °C   |

Note) 1. Do not apply external currents or voltages to any pins not specifically mentioned.

For the circuit currents, '+' denotes current flowing into the IC, and '-' denotes current flowing out of the IC.

2. Except for the power dissipation, operating ambient temperature and storage temperature, all ratings are for  $T_a = 25^{\circ}C$ .

3. \*1:  $T_a = 85^{\circ}C$ . For the independent IC without a heat sink. Note that applications must observe the derating curve for the relationship between the IC power consumption and the ambient temperature.

\*2: Allowable application voltage shall be 8.2 V or less when  $SV_{CC} \ge 8.2$  V.

# Recommended Operating Range

| Parameter      | Symbol           | Range    | Unit |

|----------------|------------------|----------|------|

| Supply voltage | V <sub>BAT</sub> | 1.5 to 9 | V    |

|                | SV <sub>CC</sub> | 4.5 to 9 | V    |

## Recommended Operating Conditions

| Parameter                                                  | Symbol                 | Range        | Unit |

|------------------------------------------------------------|------------------------|--------------|------|

| Out-1 source current                                       | I <sub>OUT1</sub>      | 30 (max.)    | mA   |

| Out-2 to Out-6 peak current                                | I <sub>OUT2 to 6</sub> | -400 to 400  | mA   |

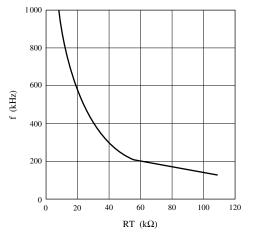

| Timing resistance                                          | R <sub>T</sub>         | 8 to 100     | kΩ   |

| Timing capacitance                                         | CT                     | 560 (fixed)  | pF   |

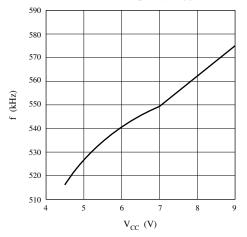

| Oscillation frequency                                      | f <sub>OUT</sub>       | 100 to 1000  | kHz  |

| Short-circuit protection time constant setting capacitance | C <sub>SCP1,2</sub>    | 1 000 (min.) | pF   |

# Electrical Characteristics at $V_{BAT} = 3 V$ , $SV_{CC} = PV_{CC1} = PV_{CC2} = 5 V$ , $C_{REF} = 0.1 \mu F$ , $T_a = 25^{\circ}C$

| Parameter                                 | Symbol                 | Condition                                  | ns                         | Min          | Тур  | Max   | Unit |

|-------------------------------------------|------------------------|--------------------------------------------|----------------------------|--------------|------|-------|------|

| Reference voltage                         |                        |                                            |                            |              |      |       |      |

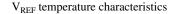

| Reference voltage                         | V <sub>REF</sub>       | $I_{REF} = -0.1 \text{ mA}$                |                            | 1.247        | 1.26 | 1.273 | V    |

| Line regulation                           | Line                   | $V_{CC} = 4.5 \text{ V}$ to 9 V            |                            | —            | 3    | 20    | mV   |

| Load regulation                           | Load                   | $I_{\text{REF}} = -0.1 \text{ mA to} -$    | -1 mA                      | -20          | -5   | —     | mV   |

| SV <sub>CC</sub> low voltage protection   |                        |                                            |                            |              |      |       |      |

| Circuit operation start voltage           | SV <sub>CCON</sub>     |                                            |                            | 3.9          | 4.1  | 4.3   | V    |

| Circuit operation stop voltage            | SV <sub>CCOFF</sub>    |                                            |                            | 3.7          | 3.9  | 4.1   | V    |

| V <sub>BAT</sub> low voltage protection   |                        |                                            |                            |              |      |       |      |

| Circuit operation start voltage           | V <sub>BATON</sub>     |                                            |                            | 1.36         | 1.43 | 1.5   | V    |

| Circuit operation stop voltage            | V <sub>BATOFF</sub>    |                                            |                            | 1.33         | 1.39 | 1.45  | V    |

| Oscillator                                |                        |                                            |                            |              |      |       |      |

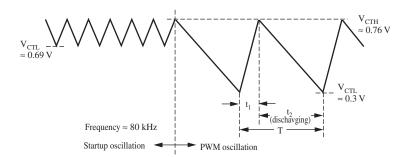

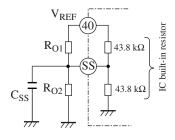

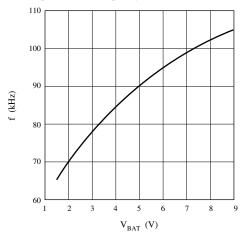

| CH 1 oscillation frequency at startup     | f <sub>ST</sub>        | CT = 560 pF                                |                            | 55           | 80   | 105   | kHz  |

|                                           |                        | $SV_{CC} = PV_{CC1} = PV$                  | $_{\rm CC2} = 1 \text{ V}$ |              |      |       |      |

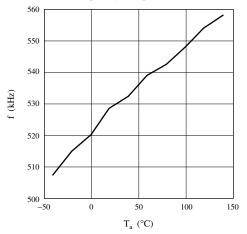

| CH 1 to CH 6 oscillation frequency        | f <sub>OUT1 to 6</sub> | $RT = 20 k\Omega$                          |                            | 490          | 540  | 590   | kHz  |

|                                           |                        | CT = 560 pF                                |                            |              |      |       |      |

| Output block                              | 1                      |                                            |                            |              |      |       |      |

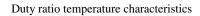

| CH 1 to CH 6 output maximum               | D <sub>U1 to 6</sub>   | $RT = 20 k\Omega$                          | CH 4                       | 78           | 84   | 90    | %    |

| duty ratio                                |                        | CT = 560 pF                                | except CH 4                | 82           | 88   | 94    | %    |

| CH 1 output duty ratio at startup         | D <sub>UST</sub>       | CT = 560 pF                                |                            | 60           | 68   | 76    | %    |

|                                           |                        | $SV_{CC} = PV_{CC1} = PV$                  | $_{\rm CC2} = 1 \text{ V}$ |              |      |       |      |

| Output high voltage 1 (CH 1)              | V <sub>OH1</sub>       | $I_{OUT1} = 20 \text{ mA}$                 |                            | $V_{CC}-2$   |      | —     | V    |

| Output source current                     | I <sub>OL1</sub>       | $V_{OUT1} = 0.7 V$                         |                            | 20           |      |       | mA   |

| Output high voltage 2 to 6 (CH 2 to CH 6) | V <sub>OH2 to 6</sub>  | $I_{OUT2 \text{ to } 6} = -0.1 \text{ mA}$ | ۱                          | $V_{CC} - 1$ |      | —     | V    |

| Output low voltage 2 to 6 (CH 2 to CH 6)  | V <sub>OL2 to 6</sub>  | $I_{OUT2 \text{ to } 6} = 0.1 \text{ mA}$  |                            |              |      | 1     | V    |

| Output block (continued)         Image: Continued of the standard sta                                                                                                                                                                                                                                               | Electrical Characteristics at $V_{BAT}$    | r = 3 V, SV            | $V_{\rm CC} = PV_{\rm CC1} = PV_{\rm CC2} = 5 \text{ V}, C_{\rm R}$ | $_{\rm EF} = 0.1  \mu F,$ | $T_a = 25$ | °C (con | tinued) |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------|---------------------------------------------------------------------|---------------------------|------------|---------|---------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Parameter                                  | Symbol                 | Conditions                                                          | Min                       | Тур        | Max     | Unit    |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Output block (continued)                   |                        |                                                                     |                           |            |         |         |

| (CH 2, CH 3, CH 5, CH 6)         International constraints         Internation constraints         Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                            | V <sub>OHS3,4</sub>    | $I_{OUT3, 4} = -0.1 \text{ mA}$                                     | V <sub>CC</sub> -1        |            |         | V       |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                            | V <sub>OLS2 to 6</sub> | $I_{OUT2, 3, 5, 6} = 0.1 \text{ mA}$                                | -                         |            | 1.0     | V       |

| Error amplifier (CH 1 to CH 6)         VTH1 to 6         1.241         1.26         1.279         V           Input threshold voltage 1 to 6         VTH1 to 6         -0.22         -0.12         -0.1         -         V           High-level output voltage 1 to 6         VEBU to 6         -0.22         -0.12         -         V           Low-level output voltage 1 to 6         VEBU to 6         -         -         -         0.2         V           Output source current 1 to 6         Isot to 6         -         -         -         -         m           CH 6 offset voltage         VOFF6         -         -         -         m         m           CH 1 short-circuit protection circuit block         -         -         -         m         m           CH 1 short-circuit protection circuit block         -         -         -         0.1         N           Latch threshold voltage         VLTH         0.27         0.3         0.33         N           Pin voltage at standby         VSTB1         -         -         0.1         N           Charge current         I_CHG1         VSCP1 = 0 V         -3.1         -2.4         -1.7         p.0           Pin voltage at standby <td< td=""><td>CH 3 output setup block</td><td>1</td><td></td><td>I</td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CH 3 output setup block                    | 1                      |                                                                     | I                         |            |         |         |

| Error amplifier (CH 1 to CH 6)           Input threshold voltage 1 to 6 $V_{TH1 to 6}$ 1.241         1.26         1.279         N           Input bias current 2, 5, 6         IB2, 5, 6         -0.22         -0.12          N           Low-level output voltage 1 to 6         VEH1 to 6         1.0          N           Low-level output voltage 1 to 6         VEL1 to 6           0.2         N           Output source current 1 to 6         Isti to 6         -45         -38         -32         µ           Output sink current 1 to 6         Isti to 6         0.5           m           CH 1 offset voltage         VOFF6        6         -6         6         m           CH 1, CH 3, CH 4 output detection         Ro1, 3, 4        1          1.0         9           CH 1 short-circuit protection circuit block         Pin voltage at standby         V <sub>STB1</sub> -0         0.1         N           Latch threshold voltage         V <sub>LTH</sub> 0.27         0.3         0.33         N           Pin voltage at standby         V <sub>STB1</sub> -         0.1         N           Charge curre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Threshold voltage                          | V <sub>CTH</sub>       |                                                                     | 1.56                      | 1.96       | 2.36    | V       |

| Input bias current 2, 5, 6       IB2, 5, 6 $-0.22$ $-0.12$ $ \mu$ High-level output voltage 1 to 6       VEH1 to 6 $  0.2$ V         Low-level output voltage 1 to 6       VEL1 to 6 $  0.2$ V         Output source current 1 to 6       Ison to 6 $-45$ $-38$ $-32$ $\mu$ Output sink current 1 to 6       Ison to 6 $0.5$ $ -$ m         CH 6 offset voltage       VorF6 $-6$ $-6$ $-$ 6       m         CH 1, CH 3, CH 4 output detection resistance division ratio       Roi, 3, 4 $-1$ $  0.1$ $N$ CH 1 short-circuit protection circuit block       Pin voltage at standby $V_{STB1}$ $  0.1$ $N$ Latch threshold voltage $V_{LTH1}$ $0.27$ $0.3$ $0.33$ $N$ Pin voltage at standby $V_{SCP1} = 0$ $-3.1$ $-2.4$ $-1.7$ $\mu$ Charge current       I <sub>CHG1</sub> $V_{SCP1} = 0$ $-3.1$ $-2.4$ $-1.7$ $\mu$ Din voltage 2 to 6 at latch operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Error amplifier (CH 1 to CH 6)             | 1                      |                                                                     |                           |            |         |         |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Input threshold voltage 1 to 6             | V <sub>TH1 to 6</sub>  |                                                                     | 1.241                     | 1.26       | 1.279   | V       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Input bias current 2, 5, 6                 | I <sub>B2, 5, 6</sub>  |                                                                     | - 0.22                    | - 0.12     | _       | μA      |

| Output source current 1 to 6         Isola 6         -45         -38         -32 $\mu_{L}$ Output sink current 1 to 6         Isil to 6         0.5         -         -         m           CH 6 offset voltage         VoFF6         -6         -         6         m'           CH 1, CH 3, CH 4 output detection ratio         Rol, 3.4         -1         -1         -1         9           resistance division ratio         Pin voltage at standby         VSTB1         -         -         0.1         N           Latch threshold voltage         VLTH1         0.27         0.3         0.33         N           Pin voltage at standby         VSTB1         -         -         0.1         N           Charge current         Ic(LG)         VSCP1 = 0 V         -3.1         -2.4         -1.7 $\mu_{L}$ CH 2 to CH 6 short-circuit protection circuit block         -         -         0.1         N           Pin voltage at standby         VSTB1         -         -         0.1         N           Latch threshold voltage 2 to 6         VLTH2 to 6         0.8         0.9         1.0         N           Charge current         ICHG1         VSCP = 0 V         -1.53         -1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | High-level output voltage 1 to 6           | V <sub>EH1 to 6</sub>  |                                                                     | 1.0                       |            |         | V       |

| Output sink current 1 to 6         ISIL to 6         0.5           m           CH 6 offset voltage $V_{OFF6}$ 6        6         -6         mi           CH 1, CH 3, CH 4 output detection<br>resistance division ratio $R_{01, 3, 4}$ 1        1          1 $q_{2}$ CH 1 short-circuit protection circuit block           0.1         N           Ch 4 short-circuit protection circuit block           0.1         N           Latch threshold voltage $V_{LTH1}$ 0.27         0.3         0.33         N           Pin voltage at latch operation $V_{SLT1}$ 0.1         N           CH 2 to CH 6 short-circuit protection circuit block           0.1         N           Pin voltage at standby $V_{STB1}$ 0.1         N           Latch threshold voltage 2 to 6 $V_{LTH2 to 6}$ 0.8         0.9         1.0         N           Pin voltage at standby $V_{SLT2 to 6}$ 0.1         N           Charge current         I <sub>CHG1</sub> $V_{SCP} = 0$ V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Low-level output voltage 1 to 6            | V <sub>EL1 to 6</sub>  |                                                                     | _                         |            | 0.2     | V       |

| $ \begin{array}{ c c c c c c c } \hline CH 6 offset voltage & V_{OFF6} & -6 & -6 & -6 & m \\ \hline CH 1, CH 3, CH 4 output detection R_{O1,3,4} & -1 & -1 & -8 & 1 & 9 \\ \hline CH 1 short-circuit protection circuit block & & & & & \\ \hline CH 1 short-circuit protection circuit block & & & & & & & \\ \hline Pin voltage at standby & V_{STB1} & & - & 0.1 & V \\ \hline Latch threshold voltage & V_{LTH1} & 0.27 & 0.3 & 0.33 & V \\ \hline Pin voltage at latch operation & V_{SLT1} & & - & 0.1 & V \\ \hline Charge current & I_{CHG1} & V_{SCP1} = 0 V & -3.1 & -2.4 & -1.7 & \mu \\ \hline CH 2 to CH 6 short-circuit protection circuit block & & & & \\ \hline Pin voltage at standby & V_{STB1} & & - & 0.1 & V \\ \hline Latch threshold voltage 2 to 6 & V_{LTH2 to 6} & 0.8 & 0.9 & 1.0 & V \\ \hline Pin voltage 2 to 6 at latch operation & V_{SLT2 to 6} & & - & 0.1 & V \\ \hline Charge current & I_{CHG1} & V_{SCP} = 0 V & -1.53 & -1.2 & -0.87 & \mu \\ \hline Control & & & & & \\ \hline Pin current & I_{CHG1} & V_{SCP} = 0 V & -1.53 & -1.2 & -0.87 & \mu \\ \hline Charge current & I_{CHG1} & V_{SCP} = 0 V & -1.53 & -1.2 & -0.87 & \mu \\ \hline Charge current & I_{CHG1} & V_{SCP} = 0 V & -1.53 & -1.2 & -0.87 & \mu \\ \hline Charge current & I_{CHG1} & V_{SCP} = 0 V & -1.53 & -1.2 & -0.87 & \mu \\ \hline Charge current & I_{CHG1} & V_{SCP} = 0 V & -1.53 & -1.2 & -0.87 & \mu \\ \hline Charge current & I_{CHG1} & V_{SCP} = 0 V & -1.53 & -1.2 & -0.87 & \mu \\ \hline Charge current & I_{CHG1} & V_{SCP} = 0 V & -1.53 & -1.2 & -0.87 & \mu \\ \hline Charge current & I_{CHG1} & V_{CTL2 to 6} & -1.53 & -1.2 & -0.87 & \mu \\ \hline Charge current & V_{CH2 to 6} & -1.53 & -1.2 & -0.87 & \mu \\ \hline Charge current & V_{CH2 to 6} & -1.53 & -1.2 & -0.87 & \mu \\ \hline Charge current & V_{CH2 to 6} & -1.53 & -1.2 & -0.87 & \mu \\ \hline Charge current & V_{CH2 to 6} & -1.53 & -1.2 & -0.87 & \mu \\ \hline Charge current & V_{CH2 to 6} & -1.53 & -1.2 & -0.87 & \mu \\ \hline Charge current & V_{CH2 to 6} & -1.53 & -1.2 & -0.87 & \mu \\ \hline Charge current & V_{CH2 to 6} & -1.55 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 & -1.5 $ | Output source current 1 to 6               | I <sub>SO1 to 6</sub>  |                                                                     | -45                       | -38        | -32     | μA      |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Output sink current 1 to 6                 | I <sub>SI1 to 6</sub>  |                                                                     | 0.5                       | _          | _       | mA      |

| resistance division ratio       Image and the second                                                                                                                                                                                                                                                       | CH 6 offset voltage                        | V <sub>OFF6</sub>      |                                                                     | -6                        |            | 6       | mV      |

| Pin voltage at standby $V_{STB1}$ —       —       —       0.1       N         Latch threshold voltage $V_{LTH1}$ 0.27       0.3       0.33       N         Pin voltage at latch operation $V_{SLT1}$ —       —       —       0.1       N         Charge current $I_{CHG1}$ $V_{SCP1} = 0$ V       —3.1       —2.4       —1.7 $\mu$ CH 2 to CH 6 short-circuit protection circuit block       —       —       0.1       N         Pin voltage at standby $V_{STB1}$ —       —       0.1       N         Latch threshold voltage 2 to 6 $V_{LTH2 to 6}$ 0.8       0.9       1.0       N         Latch threshold voltage 2 to 6 at latch operation $V_{SLT2 to 6}$ —       —       —       0.1       N         Charge current $I_{CHG1}$ $V_{SCP} = 0$ V       —1.53       —1.2       —0.87 $\mu$ Control       I $V_{CTL2 to 6}$ I       —       —       1.0       1.5       N         CH 1 threshold voltage $V_{CTL1}$ I       I       I       I       N       I       N         CH 2, CH 34, CH 5, CH 6 $V_{CTL2 to 6}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                          | R <sub>01, 3, 4</sub>  |                                                                     | -1                        |            | 1       | %       |

| Latch threshold voltage $V_{LTH1}$ 0.27       0.3       0.33       V         Pin voltage at latch operation $V_{SLT1}$ —       —       0.1       V         Charge current $I_{CHG1}$ $V_{SCP1} = 0 V$ —        0.1       V         CH 2 to CH 6 short-circuit protection circuit block       —       —       0.1       V         Pin voltage at standby $V_{STB1}$ —       —       0.1       V         Latch threshold voltage 2 to 6 $V_{LTH2 to 6}$ 0.8       0.9       1.0       V         Pin voltage 2 to 6 at latch operation $V_{SLT2 to 6}$ —       —       —       0.1       V         Charge current $I_{CHG1}$ $V_{SCP} = 0 V$ —       —       0.1       V         Charge current $I_{CHG1}$ $V_{SCP} = 0 V$ —       —       0.1       V         Control       —       —       0.1       V       V       —       —       0.87 $\mu \mu$ Charge current $I_{CHG1}$ $V_{SCP} = 0 V$ —       —       —       0.1       N         Charge current $I_{CHG1}$ $V_{SCP} = 0 V$ —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CH 1 short-circuit protection circuit      | t block                |                                                                     | I                         |            |         |         |

| Pin voltage at latch operation $V_{SLT1}$ —       —       —       —       —       0.1       N         Charge current       I <sub>CHG1</sub> $V_{SCP1} = 0$ V       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       …       —       —       …       —       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pin voltage at standby                     | V <sub>STB1</sub>      |                                                                     |                           |            | 0.1     | V       |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Latch threshold voltage                    | V <sub>LTH1</sub>      |                                                                     | 0.27                      | 0.3        | 0.33    | V       |

| CH 2 to CH 6 short-circuit protection circuit block         Pin voltage at standby $V_{STB1}$ —       —       0.1       N         Latch threshold voltage 2 to 6 $V_{LTH2 to 6}$ 0.8       0.9       1.0       N         Pin voltage 2 to 6 at latch operation $V_{SLT2 to 6}$ —       —       —       0.1       N         Charge current $I_{CHG1}$ $V_{SCP} = 0$ V       —       —       0.1       N         Control       I $V_{SCP} = 0$ V       —       —       0.8       0.9       1.0       N         Pin current       ICHG1 $V_{SCP} = 0$ V       —       —       0.1       N         Control       I       C       N       —       —       0.87 $\mu \mu$ CH 2, CH 34, CH 5, CH 6)       I       I       I       I       N       N       I       N       N       N         CH 2, CH 34, CH 5, CH 6       V       V       N       I       I       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N       N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin voltage at latch operation             | V <sub>SLT1</sub>      |                                                                     | _                         | _          | 0.1     | V       |

| Pin voltage at standby $V_{STB1}$ 0.1       N         Latch threshold voltage 2 to 6 $V_{LTH2 to 6}$ 0.8       0.9       1.0       N         Pin voltage 2 to 6 at latch operation $V_{SLT2 to 6}$ 0.1       N         Charge current $I_{CHG1}$ $V_{SCP} = 0$ V       -1.53       -1.2       -0.87 $\mu_{LT2}$ Control        -1.53       -1.2       -0.87 $\mu_{LT2}$ -0.10       N         Pin current $I_{CHG1}$ $V_{SCP} = 0$ V       -1.53       -1.2       -0.87 $\mu_{LT2}$ Control        -1.0       1.5        -0.87 $\mu_{LT2}$ CH 1 threshold voltage $V_{CTL1}$ 1.00       1.5       N         CH 2, CH 34, CH 5, CH 6 $V_{CTL2 to 6}$ 1.07       1.26       1.45       N         Regulator amplifier       Output high voltage $V_{HRA}$ $V_{CC} = 5$ N         1       N         Pin voltage when external PNP<br>transistor is connected       N       SV <sub>CC</sub> = 5.5 V to 7.5 V       4.9       5.0       5.1       N <td>Charge current</td> <td>I<sub>CHG1</sub></td> <td><math>V_{SCP1} = 0 V</math></td> <td>-3.1</td> <td>-2.4</td> <td>-1.7</td> <td>μA</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Charge current                             | I <sub>CHG1</sub>      | $V_{SCP1} = 0 V$                                                    | -3.1                      | -2.4       | -1.7    | μA      |

| Latch threshold voltage 2 to 6 $V_{LTH2 to 6}$ 0.8       0.9       1.0       N         Pin voltage 2 to 6 at latch operation $V_{SLT2 to 6}$ 0.1       N         Charge current $I_{CHG1}$ $V_{SCP} = 0 V$ -1.53       -1.2       -0.87 $\mu_{A}$ Control       -       -       1.0       1.5       -       -       0.8       0.9       1.0       N         Pin current $I_{CHG1}$ $V_{SCP} = 0 V$ -1.53       -1.2       -0.87 $\mu_{A}$ Control       -       -       1.0       1.5       N       -       -       0.8       0.9       1.0       N         Pin current $I_{CTL2 to 6}$ -       -       1.0       1.5       N       N         CH 1 threshold voltage $V_{CTL1}$ -       -       1.00       1.5       N         CH 2, CH 34, CH 5, CH 6 $V_{CTL2 to 6}$ 1.07       1.26       1.45       N         Regulator amplifier       Output high voltage $V_{HRA}$ $V_{CC} = 5 V_{ISRDV} = 10 mA$ -       -       1       N         Pin voltage when external PNP $V_{RA}$ $SV_{CC} =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CH 2 to CH 6 short-circuit protecti        | on circuit             | block                                                               |                           |            |         |         |

| Pin voltage 2 to 6 at latch operation $V_{SLT2 to 6}$ —       —       —       0.1       N         Charge current $I_{CHG1}$ $V_{SCP} = 0$ V       —       —       0.1       N         Control       —       —       0.1       N       N         Pin current $I_{CHG1}$ $V_{SCP} = 0$ V       —       —       0.1       N         Control       —       —       0.1       N       N       N       N         Pin current $I_{CTL2 to 6}$ I       —       —       1.0       1.5       N         CH 1 threshold voltage       V <sub>CTL1</sub> —       —       1.00       1.5       N         CH 2, CH 34, CH 5, CH 6 $V_{CTL2 to 6}$ N       1.07       1.26       1.45       N         Chreshold voltage       V <sub>CTL2 to 6</sub> N       —       —       —       1       N       N         Regulator amplifier       Output high voltage $V_{HRA}$ $V_{CC} = 5$ V       —       —       —       1       N         Pin voltage when external PNP $V_{RA}$ $SV_{CC} = 5.5$ V to 7.5 V       4.9       5.0       5.1       N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Pin voltage at standby                     | V <sub>STB1</sub>      |                                                                     | _                         | _          | 0.1     | V       |

| Charge current       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I <thi< th=""></thi<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Latch threshold voltage 2 to 6             | V <sub>LTH2 to 6</sub> |                                                                     | 0.8                       | 0.9        | 1.0     | V       |

| Control         Pin current<br>(CH 2, CH 34, CH 5, CH 6) $I_{CTL2 \text{ to } 6}$ $-1.53$ $-1.2$ $-0.87$ $\mu_A$ CH 1 threshold voltage $V_{CTL1}$ —       1.0       1.5       N         CH 2, CH 34, CH 5, CH 6 $V_{CTL2 \text{ to } 6}$ $V_{CTL2 \text{ to } 6}$ 1.07       1.26       1.45       N         CH 2, CH 34, CH 5, CH 6 $V_{CTL2 \text{ to } 6}$ $V_{CTL2 \text{ to } 6}$ 1.07       1.26       1.45       N         Regulator amplifier $V_{HRA}$ $V_{CC} = 5 \text{ V}$ —       —       1       N         Output high voltage $V_{HRA}$ $V_{CC} = 5 \text{ V}$ $$ —       1       N         Pin voltage when external PNP $V_{RA}$ $SV_{CC} = 5.5 \text{ V}$ to 7.5 V       4.9       5.0       5.1       N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pin voltage 2 to 6 at latch operation      |                        |                                                                     |                           | _          | 0.1     | V       |

| Pin current<br>(CH 2, CH 34, CH 5, CH 6) $I_{CTL2 to 6}$ $-1.53$ $-1.2$ $-0.87$ $\mu_{L}$ CH 1 threshold voltage $V_{CTL1}$ $$ $1.0$ $1.5$ $V_{CTL2}$ CH 2, CH 34, CH 5, CH 6<br>threshold voltage $V_{CTL2 to 6}$ $1.07$ $1.26$ $1.45$ $V_{CTL2 to 6}$ Regulator amplifier $V_{CTL2 to 6}$ $V_{CC} = 5 V_{ISRDV} = 10 \text{ mA}$ $$ $$ $1$ $V_{CC}$ Pin voltage when external PNP<br>transistor is connected $V_{RA}$ $SV_{CC} = 5.5 V to 7.5 V_{ISR}$ $4.9$ $5.0$ $5.1$ $V_{CC}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Charge current                             | I <sub>CHG1</sub>      | $V_{SCP} = 0 V$                                                     | -1.53                     | -1.2       | - 0.87  | μA      |

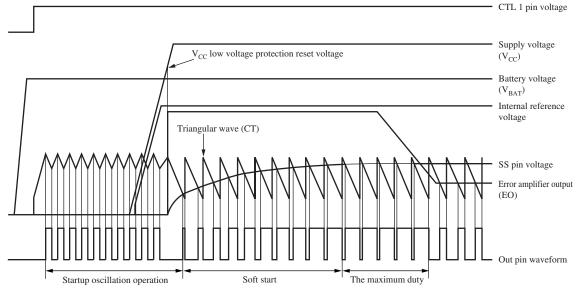

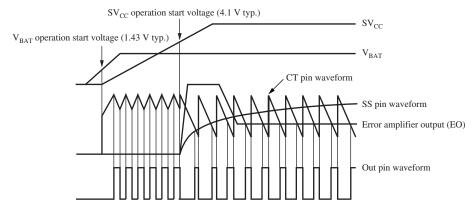

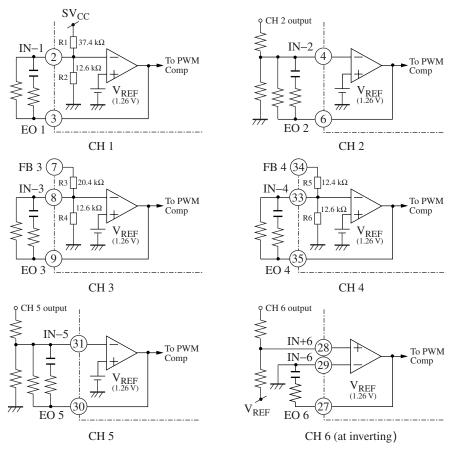

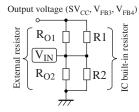

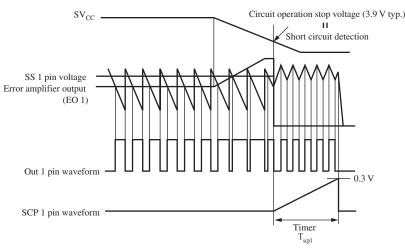

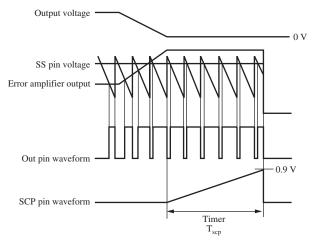

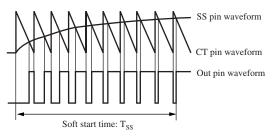

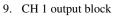

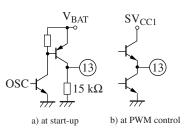

| (CH 2, CH 34, CH 5, CH 6)       CH 2 to 6       Image: CH 2 to 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Control                                    |                        |                                                                     |                           | 1          |         |         |