# M65818AFP

## Digital Amplifier Processor of S-Master\* Technology

REJ03F0019-0100Z Rev.1.00 Sep.04.2003

## **Description**

The M65818AFP is a S-Master technique processor for digital amplifier enable to convert from multi liner-PCM digital input signal to high precise switching-pulse digital output without analog processing.

The M65818AFP has built-in 24bit sampling rate converter and digital-gain-controller.

The M65818AFP enables to realize high precise (X`tal oscillation precision) fully digital amplifier systems combining with power driver IC.

#### **Features**

• Built-in 24bit Sampling Rate Converter.

Input Signal Sampling Rate

from 32KHz to 192KHz(24bit Maximum).

- 4 kinds of Digital Input Format.

- Built-in L/R Independent Digital Gain Control.

- Built-in Soft Mute Function with Exponential Approximate-Curve.

- Correspondence for SACD signal (64Fs 1bit,Fs=44.1KHz).

- Direct Output from Sampling Rate Converter.

- 3.3V and 5.0V Power Supply Operation at Output Clock, Input Data, and Control Signal Port

## **Main Applications**

Master Clock

Primary Clock: 256Fsi/512Fsi Secondary Clock: 1024Fso/512Fso

• Input Signal Format:

MSB First Right Justified(16/20/24bit), MSB First Left Justified(24bit)

LSB First Right Justified(24bit),I2S(24bit)

- Input Signal Sampling Rate from 32kHz to 192kHz.

- 8Fs Input Mode: Correspondence for External Digital Filter, Sampling Rate Converter Outputs.

- Gain Control Function:

- +30dB~ -∞dB(0.1dB Step until -96dB, -138dB Minimum)

- Third Order  $\Delta\Sigma$  (16Fso:6bit/5bit,32Fso: 5bit)

- Sampling Rate Converter Output :MSB First Left justified /Lch,Rch Independent/32BCK

### **Recommended Operating Conditions**

Logic Block: 3.3V±10%, PWM Buffer Block: 5.0V±10%

(\*\* "S-Master" is the digital amplifier technology developed by Sony Corporation.

"S-Master" is a trademark of Sony Corporation.

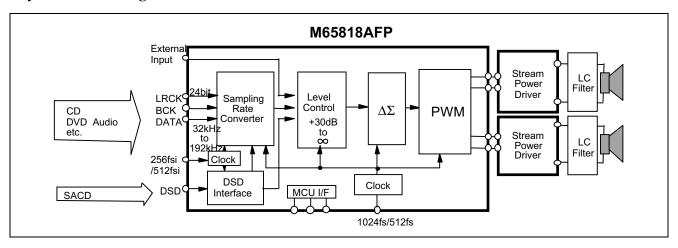

## **System Block Diagram**

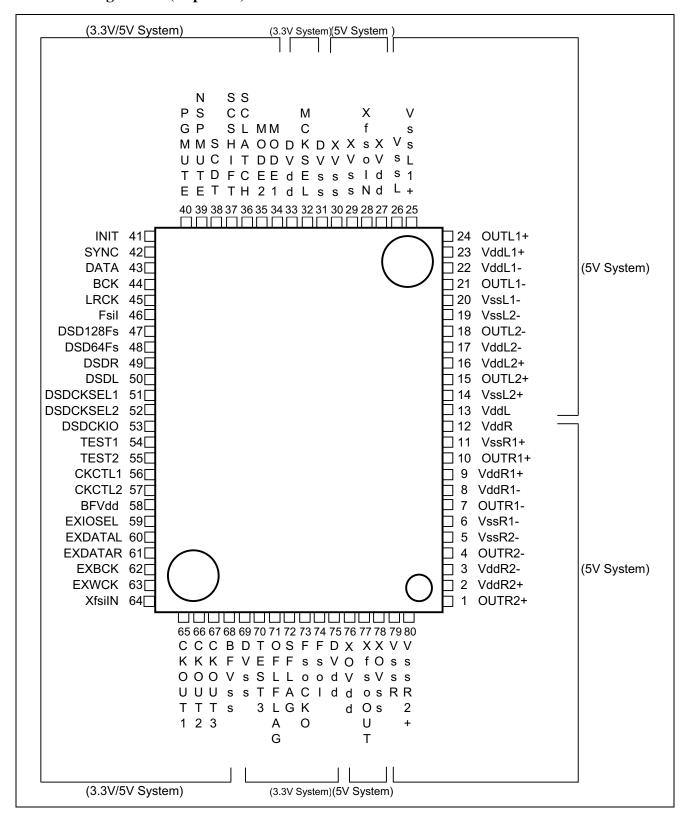

## 1. Pin Configuration (Top View)

## A-1 Difference between M65818AFP and M65817AFP

M65818AFP has added the following functions to M65817AFP.

|                                                                            | M65817AFP                                                                       | M65818AFP                                                                                                                                                        |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWM Output Form                                                            | General Pulse Width Modulation                                                  | Selectable 4 kind of Output Form (Refer to M65818AFP Data Sheet: P28/38 System1Mode bit22,23)                                                                    |

| Reverse Output Pins Function of PWM Output "OUTL1-/R1-"                    | Reverse Phase between OUTL1+/R1+ and OUTL1-/R1-                                 | Selectable phase between OUTL1+/R1+<br>and OUTL1-/R1- to Same/Reverse (Refer to<br>M65818AFP Data Sheet: P28/38<br>System1Mode bit24)                            |

| $\Delta\Sigma$ Operation Ratio                                             | 16fso Fixed                                                                     | Selectable operation ratio to 16fso/32fso (Refer to M65818AFP Data Sheet: P31/38 System2 Mode bit16)                                                             |

| Selection of Muting operation at<br>Primary Side Asynchronous<br>Detection | PWM Output Duty 50% Mute at primary side asynchronous detection                 | Selectable PWM Output Duty 50% Mute<br>On/Off at primary side asynchronous<br>detection (Refer to M65818AFP Data Sheet:<br>P28/38 System1Mode bit20)             |

| Selection of External 8Fs<br>Data Input Mode                               | Only synchronize to secondary side clock (Input the data to Gain Control Block) | Added the function of synchronization to primary side clock: Input the data to Sampling Rate Converter (Refer to M65818AFP Data Sheet: P28/38 System1Mode bit21) |

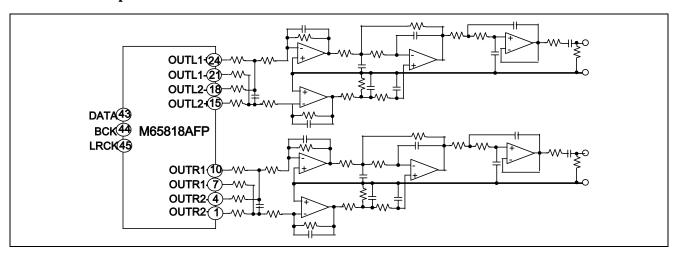

## **A-2** The Example of Evaluation Circuit

| Reference Characteristics |              | Condition                                                               |  |  |

|---------------------------|--------------|-------------------------------------------------------------------------|--|--|

| S/N 104dB(typ)            |              | Input Signal: 1kHz 0dB Full scale sine wave                             |  |  |

| THD+N 0.                  | 0.0014%(typ) | Fs: Primary Clock 44.1kHz, Secondary Clock 48kHz                        |  |  |

|                           |              | PWM Output Format1                                                      |  |  |

|                           |              | AC dithering E                                                          |  |  |

|                           |              | DC dithering 0.1%                                                       |  |  |

|                           |              | <ul> <li>Gain Data Setting:(Index)10000b/(Mantissa)10000000b</li> </ul> |  |  |

|                           |              | THD+N: Filter 20kHz LPF S/N: Filter 20kHz LPF + JIS-A                   |  |  |

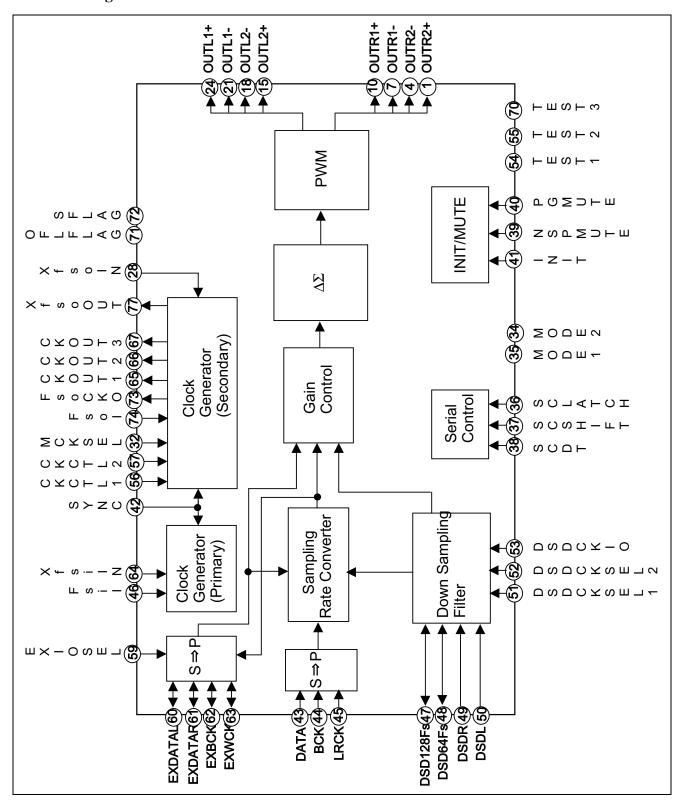

## 2. Block Diagram

## 3. Pin Descriptions

| Pin |         |     |                                                          | Output<br>Current |              |

|-----|---------|-----|----------------------------------------------------------|-------------------|--------------|

| No. | Name    | I/O | Description                                              | 5V/3.3V           | Signal Level |

| 1   | OUTR2+  | 0   | Rch PWM2(+) Output                                       |                   | 5V           |

| 2   | VddR2+  |     | Power Supply for Rch PWM2(+) (5V)                        | _                 | _            |

| 3   | VddR2-  |     | Power Supply for Rch PWM2(-) (5V)                        | _                 | _            |

| 4   | OUTR2-  | 0   | Rch PWM2 (-) Output                                      |                   | 5V           |

| 5   | VssR2-  |     | GND for Rch PWM2(-)                                      | _                 | _            |

| 6   | VssR1-  |     | GND for Rch PWM1(-)                                      | _                 | _            |

| 7   | OUTR1-  | 0   | Rch PWM1 (-) Output                                      |                   | 5V           |

| 8   | VddR1-  |     | Power Supply for Rch PWM1(-) (5V)                        | _                 | _            |

| 9   | VddR1+  |     | Power Supply for Rch PWM1(+) (5V)                        | _                 | _            |

| 10  | OUTR1+  | 0   | Rch PWM1 (+) Output                                      |                   | 5V           |

| 11  | VssR1+  |     | GND for Rch PWM1(+)                                      | _                 | _            |

| 12  | VddR    |     | Power Supply for Rch PWM (5V)                            | _                 | _            |

| 13  | VddL    |     | Power Supply for Lch PWM (5V)                            | _                 | _            |

| 14  | VssL2+  |     | GND for Lch PWM2(+)                                      | _                 | _            |

| 15  | OUTL2+  | 0   | Lch PWM2 (+) Output                                      |                   | 5V           |

| 16  | VddL2+  |     | Power Supply for Lch PWM2(+) (5V)                        | _                 | _            |

| 17  | VddL2-  |     | Power Supply for Lch PWM2(-) (5V)                        | _                 | _            |

| 18  | OUTL2-  | 0   | Lch PWM2 (-) Output                                      |                   | 5V           |

| 19  | VssL2-  |     | GND for Lch PWM2(-)                                      | _                 | _            |

| 20  | VssL1-  |     | GND for Lch PWM1(-)                                      | _                 | _            |

| 21  | OUTL1-  | 0   | Lch PWM1 (-) Output                                      |                   | 5V           |

| 22  | VddL1-  |     | Power Supply for Lch PWM1(-) (5V)                        | _                 | _            |

| 23  | VddL1+  |     | Power Supply for Lch PWM1(+) (5V)                        | _                 | _            |

| 24  | OUTL1+  | 0   | Lch PWM1 (+) Output                                      |                   | 5V           |

| 25  | VssL1+  |     | GND for Lch PWM1(+)                                      | _                 | _            |

| 26  | VssL    |     | GND for Lch PWM                                          | _                 | _            |

| 27  | XVdd    |     | Power Supply for Master Clock Buffer                     | _                 | _            |

| 28  | XfsoIN  | I   | Secondary Master Clock                                   | _                 | 5V           |

|     |         |     | Input:1024Fso/512Fso                                     |                   |              |

| 29  | XVss    |     | GND for Master Clock Buffer                              | _                 | _            |

| 30  | XVss    |     | GND for Master Clock Buffer                              | _                 | _            |

| 31  | DVss    |     | GND for Digital Block                                    | _                 | _            |

| 32  | MCKSEL  | I   | Secondary Master Clock Selection;<br>L:1024Fso, H:512Fso | _                 | 3.3V         |

| 33  | DVdd    |     | Power Supply for Digital Block (3.3V)                    | _                 | _            |

| 34  | MODE1   | I   | Input Mode Selection 1                                   |                   | 5V/3.3V      |

| 35  | MODE2   | I   | Input Mode Selection 2                                   |                   | 5V/3.3V      |

| 36  | SCLATCH | I   | Serial Control•Latch Signal Input                        | _                 | 5V/3.3V      |

| 37  | SCSHIFT | I   | Serial Control•Shift Clock Input                         |                   | 5V/3.3V      |

| 38  | SCDT    | I   | Serial Control•Data Input                                |                   | 5V/3.3V      |

| 39  | NSPMUTE | I   | PWM Duty 50% Mute (L :Active)                            | _                 | 5V/3.3V      |

| 40  | PGMUTE  | ı   | PWM G-MUTE (L :Active)                                   | _                 | 5V/3.3V      |

|     |         |     | · · · · · · · · · · · · · · · · · · ·                    |                   |              |

| Pin |           |     |                                                               | Output<br>Current |              |

|-----|-----------|-----|---------------------------------------------------------------|-------------------|--------------|

| No. | Name      | I/O | Description                                                   | 5V/3.3V           | Signal Level |

| 41  | INIT      | I   | Initialize Input(Power Supply Reset): ;<br>L:Reset, H:Release | _                 | 5V/3.3V      |

| 42  | SYNC      | I   | Synchronous Set of System Clock (at Rising Edge)              | _                 | 5V/3.3V      |

| 43  | DATA      | I   | DATA Input (CD/MD / DVD audio mode) PCM Signal                | _                 | 5V/3.3V      |

| 44  | BCK       | I   | BCK Input (CD/MD / DVD audio mode) PCM Signal                 | _                 | 5V/3.3V      |

| 45  | LRCK      | I   | LRCK Input (CD/MD / DVD audio mode) PCM Signal                | _                 | 5V/3.3V      |

| 46  | Fsil      | I   | Primary Fsi Clock Input (SACD mode)                           | _                 | 5V/3.3V      |

| 47  | DSD128Fs  | I/O | SACD Interface Clock(128Fs)                                   | 2mA/1.5mA         | 5V/3.3V      |

| 48  | DSD64Fs   | I/O | SACD Interface Clock(64Fs)                                    | 2mA/1.5mA         | 5V/3.3V      |

| 49  | DSDR      | I   | SACD Rch Data Input                                           |                   | 5V/3.3V      |

| 50  | DSDL      | I   | SACD Lch Data Input                                           |                   | 5V/3.3V      |

| 51  | DSDCKSEL1 | I   | SACD Interface Selection 1                                    | _                 | 5V/3.3V      |

| 52  | DSDCKSEL2 | I   | SACD Interface Selection 2                                    | _                 | 5V/3.3V      |

| 53  | DSDCKIO   | I   | I/O Selection for SACD(64Fs,128Fs)Clock<br>L:input,H:output   | _                 | 5V/3.3V      |

| 54  | TEST1     | I   | TEST1 must be connected to GND.                               | _                 | 5V/3.3V      |

| 55  | TEST2     | ı   | TEST2 must be connected to GND.                               |                   | 5V/3.3V      |

| 56  | CKCTL1    | I   | fso System Clock(CKOUT1,2,3) Output<br>Selection 1            | _                 | 5V/3.3V      |

| 57  | CKCTL2    | I   | fso System Clock(CKOUT1,2,3) Output<br>Selection 2            | _                 | 5V/3.3V      |

| 58  | BFVdd     |     | Power Supply for Input/Output (3.3V/5V)Buffer                 | _                 | _            |

| 59  | EXIOSEL   | I   | 8Fs Data Input/Output Selection L:Input<br>H:Output           | _                 | 5V/3.3V      |

| 60  | EXDATAL   | I/O | 8Fs Data Lch                                                  | 2mA/1.5mA         | 5V/3.3V      |

| 61  | EXDATAR   | I/O | 8Fs Data Rch                                                  | 2mA/1.5mA         | 5V/3.3V      |

| 62  | EXBCK     | I/O | BCK for 8fs Data (32BCK=1WCK)                                 | 2mA/1.5mA         | 5V/3.3V      |

| 63  | EXWCK     | I/O | Word Clock for 8fs Data (1WCK=32BCK)                          | 2mA/1.5mA         | 5V/3.3V      |

| 64  | XfsilN    | I   | Primary Master Clock Input (256fsi/512fsi)                    |                   | 5V/3.3V      |

| 65  | CKOUT1    | 0   | fso System Clock Output 1                                     | 4mA/3mA           | 5V/3.3V      |

| 66  | CKOUT2    | 0   | fso System Clock Output 2                                     | 4mA/3mA           | 5V/3.3V      |

| 67  | CKOUT3    | 0   | fso System Clock Output 3                                     | 4mA/3mA           | 5V/3.3V      |

| 68  | BFVss     |     | GND for Digital Block Input/Output Buffer                     | _                 |              |

| 69  | DVss      |     | GND for Digital Block                                         |                   |              |

| 70  | TEST3     | I   | TEST3 must be connected to GND.                               |                   | 3.3V         |

| 71  | OFLFLAG   | 0   | Overflow Detector Flag of Digital Operation (H :Active)       | 2mA               | 3.3V         |

| 72  | SFLAG     | 0   | Asynchronous Flag (H :Active)                                 | 2mA               | 3.3V         |

| 73  | FsoCKO    | 0   | Secondary Fso Clock Output                                    | 4mA               | 3.3V         |

| 74  | Fsol      | I   | Secondary Fso Clock Input                                     | _                 | 3.3V         |

| 75  | DVdd      |     | Power Supply for Digital Block(3.3V)                          | _                 |              |

| 76  | XOVdd     |     | Power Supply for Secondary Master Clock<br>Buffer(5V)         | _                 | _            |

## M65818AFP

| Pin<br>No. | Name    | I/O | Description                                             | Output<br>Current<br>5V/3.3V | Signal Level |

|------------|---------|-----|---------------------------------------------------------|------------------------------|--------------|

| 77         | XfsoOUT | 0   | Buffered Output of Secondary Master Clock (1024/512fso) | 2mA                          | 5V           |

| 78         | XOVss   |     | GND for Secondary Master Clock Buffer                   | _                            | _            |

| 79         | VssR    |     | GND for Rch PWM                                         | _                            | _            |

| 80         | VssR2+  |     | GND for Rch PWM2(+)                                     | _                            | _            |

## 4. Electrical Characteristics

## **Absolute Maximum Ratings**

| Parameter           | Symbol    | Min. | Тур. | Max      | Unit | Conditions                     |

|---------------------|-----------|------|------|----------|------|--------------------------------|

| Supply Voltage      | PWMVdd    | -0.3 | _    | 6.0      | V    | 5V XVdd, XOVdd, and Vdd (PWM). |

|                     | BFVdd     | -0.3 | _    | 6.0      | V    | 5.0V System                    |

|                     | DVdd      | -0.3 | _    | 4.2      | V    | 3.3V System                    |

| Input Voltage Range | Vi (5.0V) | -0.3 | _    | Vdd+0.3V | V    |                                |

|                     | Vi (3.3V) | -0.3 | _    | Vdd+0.3V | V    |                                |

| Power Dissipation   | Pd        |      | 600  |          | mW   | Ta=60 °C                       |

| Storage Temperature | Tstg      | -40  | _    | 125      | °C   |                                |

## **Recommended Operating Conditions**

| Parameter             | Symbol | Min. | Тур. | Max | Unit | Conditions                     |

|-----------------------|--------|------|------|-----|------|--------------------------------|

| Supply Voltage        | PWMVdd | 4.5  | 5.0  | 5.5 | V    | 5V XVdd, XOVdd, and Vdd (PWM). |

|                       | BFVdd  | 4.5  | 5.0  | 5.5 | V    | 5.0V function                  |

|                       |        | 3.0  | 3.3  | 3.6 | V    | 3.3V function                  |

|                       | DVdd   | 3.0  | 3.3  | 3.6 | V    |                                |

| Operating Temperature | Та     | -20  | _    | 75  | °C   |                                |

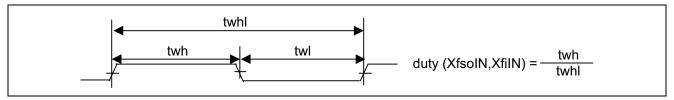

| Operating Frequency   | XFsoIN | 16   | _    | 50  | MHz  |                                |

|                       | XFsiIN | 8    | _    | 25  | MHz  |                                |

## **DC** Characteristics

(Ta=25°C, PWMVdd=5V, DVdd=3.3V: Unless otherwise specified.)

| Parameter            |                                                 | Symbol | Min.      | Тур. | Max     | Unit | Conditions                             |

|----------------------|-------------------------------------------------|--------|-----------|------|---------|------|----------------------------------------|

| H Level Input Voltag | ge                                              | VIH5   | 0.75Vdd   | _    | _       | ٧    | BFVdd=4.5 to 5.5V                      |

|                      |                                                 |        | 0.75Vdd   | _    | _       | V    | BFVdd=3.0 to 3.6V                      |

| L Level Input Voltag | L Level Input Voltage                           |        | _         | _    | 0.25Vdd | V    | BFVdd=4.5 to 5.5V                      |

|                      |                                                 | VIL3   | _         | _    | 0.25Vdd | V    | BFVdd=3.0 to 3.6V                      |

| Input Leak Current   |                                                 | lleak  | _         | _    | 10      | μΑ   |                                        |

| "H"Level Output      | DSD128Fs                                        | VOH5   | Vdd-0.5   | _    | _       | V    | BFVdd=4.5 to 5.5V IOH5=-2.0mA          |

| Voltage              | DSD64Fs<br>EXDATAL<br>EXDATAR<br>EXBCK<br>EXWCK | VOH3   | Vdd – 0.5 | _    | _       | V    | BFVdd=3.0 to 3.6V IOH3=-1.5mA          |

|                      | CKOUT1                                          | VOH5   | Vdd – 0.5 | _    | _       | V    | BFVdd=4.5 to 5.5V IOH5=-4.0mA          |

|                      | CKOUT2<br>CKOUT3                                | VOH3   | Vdd – 0.5 | _    | _       | V    | BFVdd=3.0 to 3.6V IOH3=-3.0mA          |

|                      | XfsoOUT                                         | VOH5   | Vdd - 0.5 | _    | _       | V    | BFVdd=4.5 to 5.5V IOH5=-2.0mA          |

|                      | OFLFAG<br>SFLAG<br>FsoCKO                       | VOH3   | Vdd – 0.5 | _    | _       | V    | BFVdd=3.0 to 3.6V IOH3=-2.0mA          |

|                      | OUTLXX<br>OUTRXX                                | VOH5   | Vdd – 0.5 | _    | _       | V    | VddLXX/RXX=4.5V to 5.5V<br>IOH5=–4.0mA |

| "L" Level Output     | DSD128Fs                                        | VOL5   | _         | _    | 0.5     | V    | BFVdd=4.5 to 5.5V IOH5=2.0mA           |

| Voltage              | DSD64Fs<br>EXDATAL<br>EXDATAR<br>EXBCK<br>EXWCK | VOL3   | _         | _    | 0.5     | V    | BFVdd=3.0 to 3.6V IOH3=1.5mA           |

|                      | CKOUT1                                          | VOL5   | _         | _    | 0.5     | V    | BFVdd=4.5 to 5.5V IOH5=4.0mA           |

|                      | CKOUT2<br>CKOUT3                                | VOL3   | _         | _    | 0.5     | V    | BFVdd=3.0 to 3.6V IOH3=3.0mA           |

|                      | XfsoOUT                                         | VOL5   | _         | _    | 0.5     | V    | BFVdd=4.5 to 5.5V IOH5=2.0mA           |

|                      | OFLFAG<br>SFLAG<br>FsoCKO                       | VOL3   | _         |      | 0.5     | V    | BFVdd=3.0 to 3.6V IOH3=2.0mA           |

|                      | OUTLXX<br>OUTRXX                                | VOL5   | _         | _    | 0.5     | V    | VddLXX/RXX=4.5V to 5.5V<br>IOH5=4.0mA  |

| Power Supply Curre   | ent                                             | ldd    |           | 33   |         | mΑ   | BFVdd=5V                               |

## 5. Explanation of Operation

## 5.1. MODE1, MODE2 34 35

The states of MODE1 and MODE2 pins select input signal mode.

MODE1 and MODE2 are control pins for input signal mode (Normal / SACD / External 8fs Input).

These are selectable as follows.

| Pin | Name / MODE | Normal | External 8fs Data | SACD-fsi | SACD-fso |

|-----|-------------|--------|-------------------|----------|----------|

| 34  | MODE1       | L      | L                 | Н        | Н        |

| 35  | MODE2       | L      | Н                 | L        | Н        |

#### M65818AFP

#### • Normal mode

The Normal is data input mode from CD,MD,DVD etc.

Input pins are DATA, BCK, and LRCK.

#### External 8fs Data mode

In this mode, the 8fs rate data inputted from external device.

Input pins are EXDATAL, EXDATAR, EXBCK and EXWCK.

The data synchronized with the clock of EXBCK, EXWCK pins are inputted into EXDATAL, EXDATAR pins.

Selectable "Input for primary side synchronization" and "Input for secondary side synchronization"

by the serial control System1 mode bit21 (EXMODE)

In the case of primary side synchronization, the data inputted to the Sampling Rate Converter block.

In the case of secondary side synchronization, the data inputted to Gain Control block.

#### SACD-fsi mode

In this mode, SACD format data inputted.

Input pins are DSDL,DSDR,DSD128Fs and DSD64Fs.

The clock of a Down Sampling Filter is given from a \*primary side, and down sampled data are inputted into the Sampling Rate Converter block.

The data synchronized with the clock of DSD128Fs,DSD64Fs pins are inputted into DSDL,DSDR pins.

#### • SACD-fso mode

In this mode, SACD format data inputted.

Input pins are DSDL, DSDR, DSD128Fs and DSD64Fs.

The clock of a Down Sampling Filter is given from a \*secondary side, and down sampled data are inputted into the Gain Control block.

The data synchronized with the clock of DSD128Fs,DSD64Fs pins are inputted into DSDL,DSDR pins.

\* primary clock: This clock means input side clock System of the sampling rate converter. secondary clock: This clock means output side clock System of the sampling rate converter. The block after Sampling Rate Converter (Gain Control Block, ΔΣ Block, and PWM Block) operate with secondary clock

"fsi", "fso", and "fs" are defined as follows in this data sheet.

fsi: The primary side Sampling Frequency

fso: The secondary side Sampling Frequency

fs: The sampling frequency which can be set as both by the side of primary and secondary.

(External 8fs Data, SACD Data etc.)

RENESAS

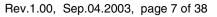

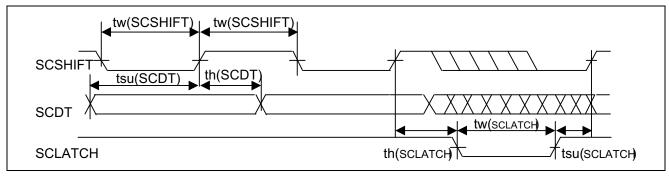

## 5.2. SCDT, SCSHIFT, SCLATCH 38 37 36

**SCDT,SCSHIFT,**and **SCLATCH** are input pins for setting M65818AFP's operation.

Input format of SCDT, SCSHIFT and SCLATCH is shown below.

• Input format of SCDT, SCSHIFT, and SCLATCH.

### • Mode Setting

The operating Mode are classified in four and assigned by bit1 and bit2. These four functions are shown below.

(bit1 and bit2) = ("L" and "L") Gain control mode: Gain control.

(bit1 and bit2) = ("L"and "H") System1 Mode: Primary block initialization, etc.

(bit1 and bit2) = ("H" and "L") System2 Mode: Secondary block initialization, etc.

(bit1 and bit2) = ("H" and "H") Test mode (setting prohibition)

Refer to Chapter 6 about these four setting in detail.

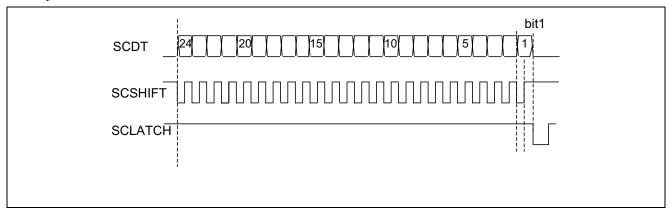

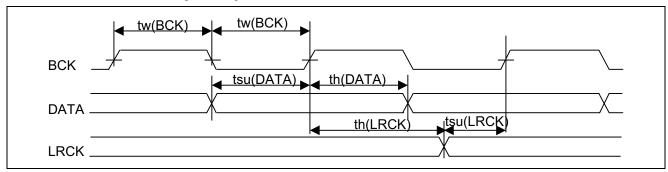

## 5.3. DATA, BCK, LRCK 43 44 45

**DATA, BCK** and **LRCK** are input pins under condition of `Normal` mode.

Input formats are supported by following 4 ways, and are set by Serial Control, "System1 Mode, bit3 and bit4".

Input data length are selectable in the case of "MSB First Right Justified"

(Serial Control "System1 Mode, bit5, 6").

and Input Signal Sampling Rate(1/2/4fsi) are set by Serial Control, "System1 Mode, bit7,8"

Input formats are shown in following figures.

### • Input Formats of DATA, BCK, and LRCK

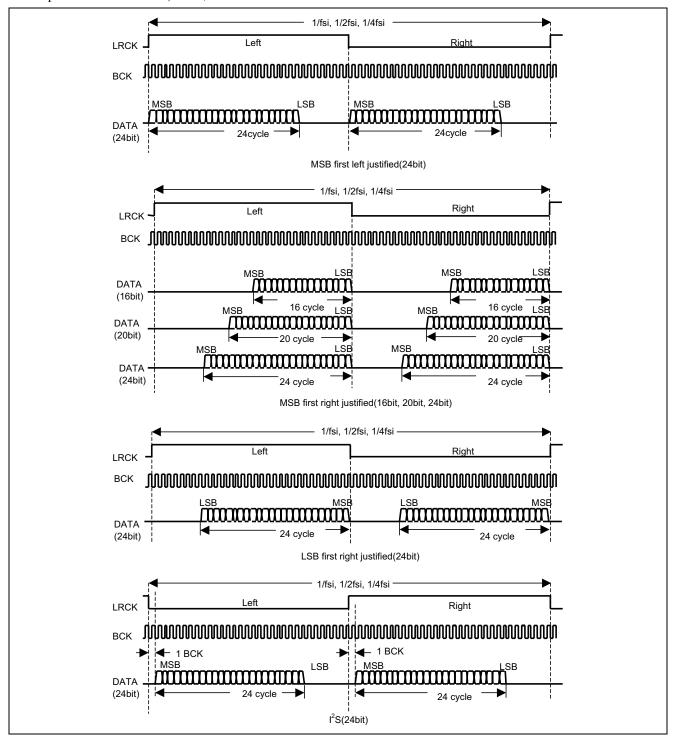

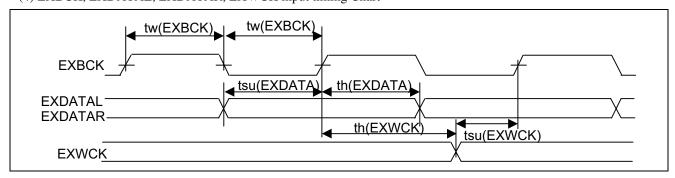

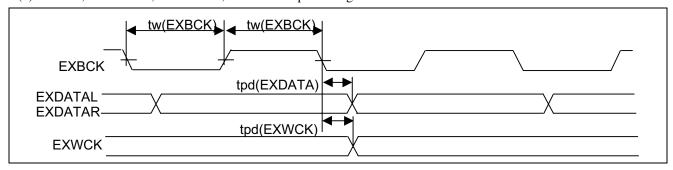

## 5.4. EXBCK, EXWCK, EXDATAL, EXDATAR, EXIOSEL 62 63 60 61 59

When "input signal mode" is "external 8fs data mode", regardless of a setup of **EXIOSEL** pin, the data of 8fs rate are inputted from **EXDATAL**, **EXDATAR** pins.

By setup of serial control "System1 mode:bit21", Primary Side Synchronous Input or Secondary Side Synchronous Input can be selected.

In case an external 8fs data input is secondary side synchronous, the data is inputted to Gain Control Block.

In case an external 8fs data input is primary side synchronous, the data is inputted to Sampling Rate Converter Block.

When "input signal mode" is except a "external 8fs data mode", the output data of sampling rate converter are outputted from **EXDATAL,EXDATAR** pins setting up EXIOSEL pin into "H".

When "input signal mode" is except a "external 8fs data mode", **EXBCK**, **EXWCK**, **EXDATAL**, **EXDATAR** pins serve as input terminals by setting up **EXIOSEL** pin into "L".

Therefore, when not using "external 8fs data mode", **EXIOSEL** can be set to "L" and other four pins (**EXBCK**, **EXWCK**, **EXDATAL**, **EXDATAR**) can be fixed to "L" or "H".

EXDATAL, EXDATAR, EXBCK, and EXWCK pin's input/output format is following figure.

| Input Signal Mode                    | EXIOSEL<br>pin | EXMODE<br>Flag | EXWCK,EXBCK,EXDATAL,EXDATAR Input / Output                      |

|--------------------------------------|----------------|----------------|-----------------------------------------------------------------|

| "External 8fs Mode"<br>(MODE1,2=L,H) | Χ              | L              | Secondary Side Synchronous 8fs Data Input (24 bit effective)    |

|                                      |                | Н              | Primary Side Synchronous 8fs Data Input (Upper 20bit effective) |

| Except "External 8fs                 | L              | X              | Input ("L" or "H" fixed)                                        |

| Mode"<br>(Except MODE1,2=L,H)        | Н              | _              | Internal Sampling Rate Converter Output                         |

### • EXDATAL, EXDATAR, EXBCK, and EXWCK input/output format

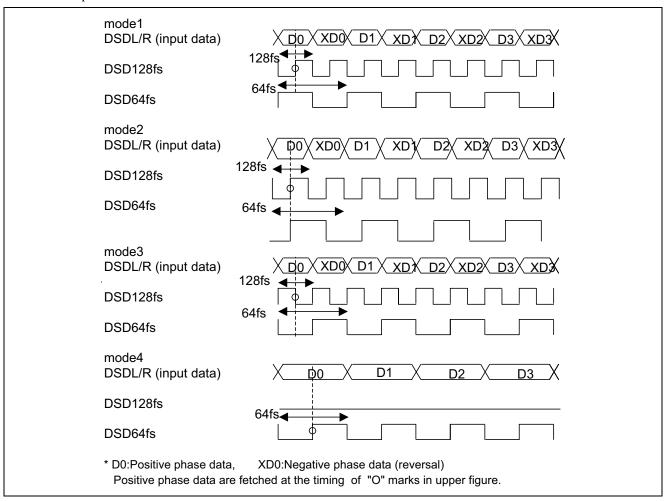

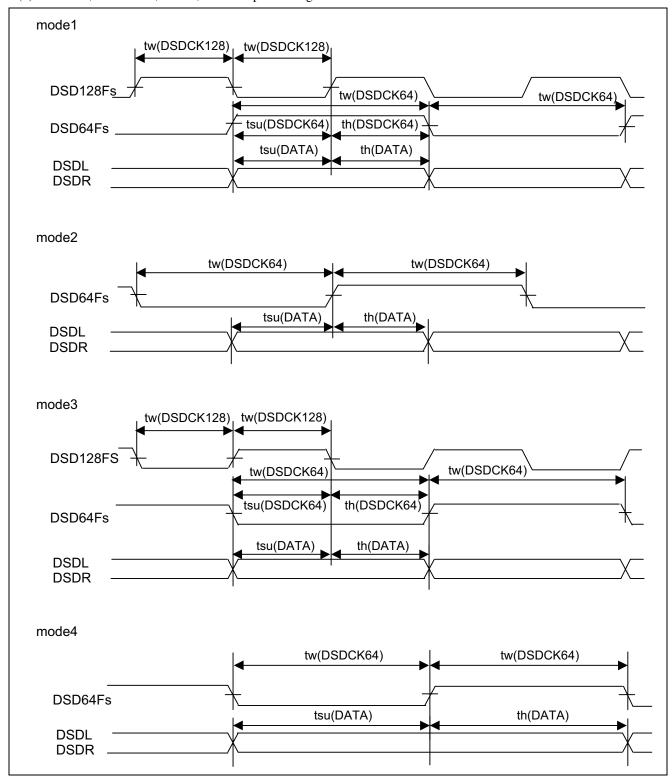

### 5.5. DSDL, DSDR, DSD128Fs, DSD64Fs, DSDCKSEL1, DSDCKSEL2, DSDCKIO 50 49 47 48 51 52 53

When "input signal mode" is "SACD-fsi Mode" or "SACD-fso Mode", the data is inputted to DSDL,DSDR pins.

Under `SACD-fsi ` mode, the clock of a Down Sampling Filter is given from a primary side, and down sampled data are inputted into the Sampling Rate Converter block.

Under `SACD-fso` mode, the clock of a Down Sampling Filter is given from a \*secondary side, and down sampled data a inputted into the Gain Control block.

The states of **DSDCKSEL1,DSDCKDEL2** pins select 4 "SACD timing mode".

DSDCKIO pin select input or output pin-type of DSD128Fs/DSD64Fs clock for data fetch.

The relations of **DSDCKSEL1** and **DSDCKSEL2** pins and SACD input format mode setting are following figures.

| DSDCKSEL1 | DSDCKSEL2 | SACD timing mode |

|-----------|-----------|------------------|

| L         | L         | mode1            |

| L         | Н         | mode2            |

| Н         | L         | mode3            |

| Н         | Н         | mode4            |

Setting of **DSDCKIO** is following table.

| DSDCKIO | Selection of DSD64fs and DSD128fs I/O |  |

|---------|---------------------------------------|--|

| L       | Input mode                            |  |

| Н       | Output mode                           |  |

## SACD Input Format

## 5.6. MCKCEL, XfsoIN, XfsoOUT

**XfsoIN** pin is secondary master clock input.

The state of MCKSEL pin selects secondary master clock.

| MCKSEL | XfsoIN  |  |

|--------|---------|--|

| L      | 1024fso |  |

| Н      | 512fso  |  |

XfsoOUT pin is buffered-output from XfsoIN pin's input clock.

#### 5.7. XfsiIN

**XfsiIN** pin is primary master clock input.

Frequency of primary master clock must be selected by the serial control "System2 mode:bit3".

| bit3(IMCKSEL) | XfsilN |

|---------------|--------|

| Н             | 512fsi |

| L             | 256fsi |

• The relations between input signal sampling rate and master clock frequency.

| Input sampling rate                      | Primary clock 512fsi/256fsi[Hz] | Secondary clock 1024fso/512fso[Hz] |

|------------------------------------------|---------------------------------|------------------------------------|

| 1fsi: 32k / 2fsi: 64k / 4fsi: 128k       | 16.384M/8.192M                  | 32.768M/16.384M                    |

| 1fsi: 44.1k / 2fsi: 88.2k / 4fsi: 176.4k | 22.579M/11.290M                 |                                    |

| 1fsi: 48k / 2fsi: 96k / 4fsi: 192k       | 24.576M/12.288M                 | 49.152M/24.576M                    |

Input signal and primary clock are related to synchronization. The primary clock frequency are 512 or 256 times as much as the input signal fsi (32k, 44.1k and 48k.)

The primary and secondary clock are related to independence. ( asynchronization )

At 1024fso setting, secondary clock= frequency range from 32.768MHz to 49.152MHz.

At 512fso setting, secondary clock = frequency range from 16.384MHz to 24.576MHz.

### 5.8. CKCTL1, CKCTL2, CKOUT1, CKOUT2, CKOUT3

**CKOUT1**, **CKOUT2**, and **CKOUT3** pins are divided-clock output from secondary clock.

At power on, these frequency is free-running.

The states of CKCTL1 and CKCTL2 pins selects clock frequency of CKOUT1, CKOUT2, and CKOUT3 pins.

The setting table of **CKCTL1** and **CKCTL2** pins is shown below.

| CKCTL1 | CKCTL2 | CKOUT1 | CKOUT2 | CKOUT3 |  |

|--------|--------|--------|--------|--------|--|

| L      | L      | L      | L      | L      |  |

| L      | Н      | 256Fso | 16Fso  | 8Fso   |  |

| Н      | L      | 512Fso | 256Fso | 16Fso  |  |

| Н      | Н      | 512Fso | 256Fso | 8Fso   |  |

#### 5.9. FsoCKO

**FsoCKO** is clock output pin of 1fso frequency. The output is divided-clock of **XfsoIN**, and frequency is free-running at power on. **FsoCKO** pin's clock is utilized for a synchronization in case that have used plural M65818AFP, take a synchronization between M65818AFP and other external devices.

Detail explanation is shown in next paragraph, "SYNC".

## 5.10. SYNC, FsoI, FsiI, SFLAG

42 74 46 72

M65818AFP synchronizes in clock input from the external source devices. So it makes synchronized operation between source devices or another M65818AFP (in case of Multi channel Operation)

The clock which can be set as the object of an synchronization is a clock of **FsoI** (1fso), **FsiI** (1fsi), **LRCK** (1/2/4 fsi), and **EXWCK** (8fs). The object clock changes by input signal mode setting.

These relations are shown in following table.

#### M65818AFP

M65818AFP detects rise edge of these synchronized clock in normal operation, and the M65818AFP does operation of resynchronization in case that the cycle has changed.

In addition, the M65818AFP re-synchronizes for a synchronized clock, in case that M65818AFP detects SYNC pin's rises edge, too.

This SYNC function exists also in serial control "System2 mode:bit6" under the same name.

While re-synchronizing, SFLAG pin outputs "H" and data is muted inside.

|                   |                                | `Synchronization detection` clock |                |  |

|-------------------|--------------------------------|-----------------------------------|----------------|--|

| Input Signal Mode |                                | Primary Side                      | Secondary Side |  |

| Normal            |                                | LRCK                              | Fsol           |  |

| External 8fs Data | Primary Side Synchronization   | EXWCK *                           | Fsol           |  |

|                   | Secondary Side Synchronization |                                   | Fsol           |  |

| SACD-fsi          |                                | Fsil                              | Fsol           |  |

| SACD-fso          |                                |                                   | Fsol           |  |

<sup>\*</sup> Internal 8 dividing clock

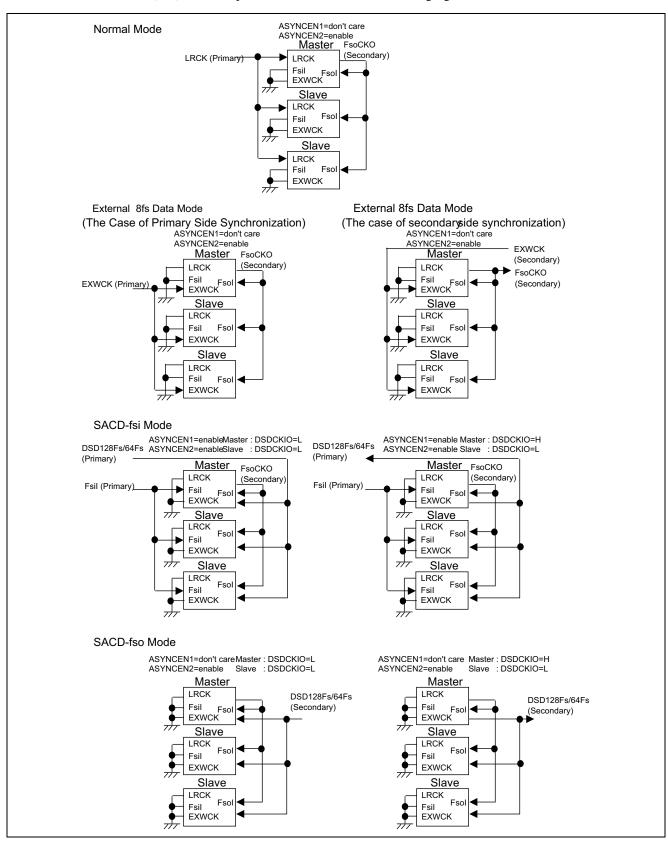

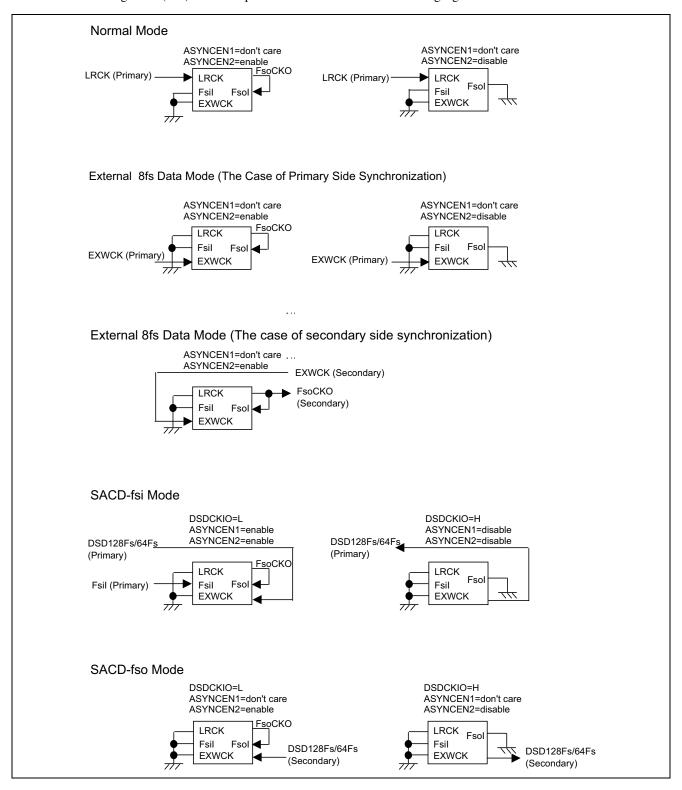

In the case of using Multiplex(for multi channel application) and Single (for 2ch application), detail explanation is shown according to each "signal input mode" below.

#### Normal Mode

<Multiplex use>

The primary side: It synchronizes with **LRCK**. All ICs synchronize with an input device by connecting common **LRCK**.

The Secondary side: It synchronizes with FsoCKO of Master IC. One of M65818AFP becomes a master IC, and the synchronization between ICs is carried out by FsoCKO of Master IC.

FsoCKO pin outputted from this master IC is entered each FsoI pins of master and slave ICs.

#### <Single use>

The primary side: It synchronizes with LRCK. Therefore M65818AFP synchronizes with source devices. The secondary side: there is no need for external devices and other ICs to synchronize, therefore FsoCKO is connected to FsoI, In other way, By setting secondary side asynchronous detection to "disable" with "ASYNCEN2" flag(Serial Control,System2 mode,bit8), FsoI can also be considered as fixation.

In this mode, M65818AFP always perform synchronous detection between **LRCK** pin's clock in primary side. Therefore with regardless to a setup by the serial control "System1 mode:bit16(ASYNCEN1)", the synchronous detection perform as `forced-enable`.

• External 8fs Data Mode (The case of primary side synchronization)

<Multiplex use>

The primary side: M65818AFP synchronizes with **EXWCK** (internal 8 dividing clock). All ICs synchronize with an input device by connecting common **EXWCK**.

The secondary side: M65818AFP synchronizes with FsoCKO of Master IC. One of M65818AFP becomes a master IC, and the synchronization between ICs is carried out by FsoCKO of Master IC.

FsoCKO pin outputted from this master IC is entered each FsoI pins of master and slave ICs.

#### <Single use>

The primary side: M65818AFP synchronizes with **EXWCK** (internal 8 dividing clock).

Thereby it synchronize with an input device.

The secondary side: there is no need for external devices and other ICs to synchronize, therefore FsoCKO is connected to FsoI, In other way,

By setting secondary side asynchronous detection to "disable" with "ASYNCEN2" flag(Serial Control, System2 mode, bit8), FsoI can also be considered as fixation.

In this mode, M65818AFP always perform synchronous detection between **EXWCK** pin's clock in primary side. Therefore with regardless to a setup by the serial control "System1 mode:bit16(ASYNCEN1)", the synchronous detection perform as `forced-enable`.

#### • External 8fs Data Mode (The case of secondary side synchronization)

<Multiplex use and Single use> (common)

The primary side: Synchronous operation does not carry out since internal sampling rate converter is not used. In this mode, asynchronous detection by the primary side is set to disable by force.

Therefore with regardless to a setup by the serial control "System1 mode:bit16(ASYNCEN1)", the synchronous detection perform as `forced-disable`.

The Secondary Side: M65818AFP synchronizes with **FsoCKO** of Master IC (in single use, it is own IC). One of the M65818AFP becomes a master, and the synchronization between ICs is carried out by FsoCKO of Master IC.FsoCKO pin outputted from this master IC is entered each FsoI pins of master and slave ICs.

Moreover, the rise edge of **FsoCKO** sent from M65818AFP and the rise edge of **EXWCK** (8fs) which comes from the external device need to be with a synchronous phase.

#### • SACD-fsi Mode

#### <Multiplex use>

The primary side: M65818AFP synchronizes with **FsiI** inputted in common to each IC. And primary side synchronous **DSD128Fs/DSD64Fs** are used as a clock in common to all ICs.

Thus, **DSD128 Fs/DSD64Fs** in common to all ICs is inputted (all IC DSDCKIO=L) or the **DSD128 Fs/DSD64Fs** output (**DSDCKIO=**"H") generated by dividing of the primary side master clock within Master IC is inputted Into the **DSD128 Fs/DSD64Fs** (**DSDCKIO=**"L") of other slaves IC. The synchronous operation of the SACD input in the case of multi is possible by doing in this way.

The secondary side: M65818AFP synchronizes with FsoCKO of Master IC. One of M65818AFP becomes a master IC, and the synchronization between ICs is carried out by FsoCKO of Master IC.

FsoCKO pin outputted from this master IC is entered each FsoI pins of master and slave ICs.

### <Single use>

The primary side: Input to **FsiI** pin or set **FsiI** as fixed by setting primary side asynchronous detection to disable by serial control "System1 mode:bit16 (ASYNCEN1)".

The secondary side: there is no need for external devices and other ICs to synchronize, therefore FsoCKO is connected to FsoI, In other way, By setting secondary side asynchronous detection to "disable" with "ASYNCEN2" flag(Serial Control,System2 mode,bit8), FsoI can also be considered as fixation.

#### M65818AFP

#### • SACD-fso Mode

#### <Multiplex use>

The primary side: Synchronous operation does not carry out since internal sampling rate converter is not used. In this mode, asynchronous detection by the primary side is set to disable by force.

Therefore with regardless to a setup by the serial control "System1 mode:bit16(ASYNCEN1)", the synchronous detection perform as `forced-disable`.

The secondary side: M65818AFP synchronizes with FsoCKO of Master IC. One of M65818AFP becomes a master IC, and the synchronization between ICs is carried out by FsoCKO of Master IC.

FsoCKO pin outputted from this master IC is entered each FsoI pins of master and slave ICs.

And **DSD128Fs/DSD64Fs** for secondary synchronization are connected as a clock in common to all ICs. Thus, **DSD128 Fs/DSD64Fs** in common to all ICs is inputted (all IC **DSDCKIO=**"L") or the **DSD128 Fs/DSD64Fs** output (**DSDCKIO=**"H") generated by dividing of the primary side master clock within Master IC is inputted into the **DSD128 Fs/DSD64Fs** (**DSDCKIO=**"L") of other slaves IC.

The synchronous operation of the SACD input in the case of multi is possible by doing in this way.

#### <Single use>

The primary side: Synchronous operation does not carry out since internal sampling rate converter is not used. In this mode, asynchronous detection by the primary side is set to disable by force.

Therefore with regardless to a setup by the serial control "System1 mode:bit16(ASYNCEN1)", the synchronous detection perform as `forced-disable`.

The secondary side: there is no need for external devices and other ICs to synchronize, therefore FsoCKO is connected to FsoI, In other way, By setting secondary side asynchronous detection to "disable" with "ASYNCEN2" flag(Serial Control,System2 mode,bit8), FsoI can also be considered as fixation.

RENESAS

### The examples of a connection diagram

The case of the multi use (6ch) in each input mode are shown in the following figure.

### The examples of a connection diagram

The case of the single use (2ch) in each input mode are shown in the following figure.

#### 5.11. OFLFLAG

**OFLFLAG** pin is output the 'over flow flag' in the operation. **OFLFLAG** pin outputs "H" level by detection of over flow from Gain Control Block and others.

The "H" level width is over 0.6msec, so detection result is held.

### 5.12. OUTL1+, OUTL1-, OUTL2+, OUTL2-, OUTR1+, OUTR1-, OUTR2+, OUTR2-

OUTL1+, OUTL2+, OUTL2+, OUTR1+, OUTR1-, OUTR2+, and OUTR2- pins are pulse output modulated  $\Delta\Sigma$  output signal to PWM signal.

These pins are connected to external Power Driver ICs.

PWM Output Form 1, 2, 3 and 4 can be selected by serial control data(System1 mode:bit22,23).

PWM Output Form1 : General Modulation PWM Output Form2 : Symmetrical Modulation

PWM Output Form3: Modulation returned with time domain. (The rise and fall edge of Lch and Rch in a term are reverse.)

PWM Output Form4: Modulation returned with time domain.

(The rise and fall edge of Lch and Rch in a term are same timing.)

In each 4 forms, the operating rate and bit length of PWM Output can be changed following the setting of  $\Delta\Sigma$  And the output mute function and the output pins reverse function, can be controlled by the pin setting or serial control.

The PWM output control is shown in the following table.

| Item                                  | Operation                                                                                                                                                | Setting Operation                                                                                                                                                                   |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Form                           | Output Form Selection 1,2,3,4                                                                                                                            | Set up by the serial control system 1 mode<br>bit 22,23 (PWM MODE 0 and 1).<br>(Refer to Chapter 6.2. system 1 mode for details)                                                    |

| Operating Rate and Data<br>Bit Length | Select to 16fso/6bit ,16fso/5bit ,32fso/5bit from operating rate and data bit length of $\Delta\Sigma$ . PWM operation are synchronized by this setting. | Set up by the serial control system 2 mode bit16 and bit17. (Refer to Chapter 6.3. system 2 mode for details.)                                                                      |

| Output Muting                         | Duty 50% Mute                                                                                                                                            | Set <b>NSPMUTE</b> pin "L" or set up by serial control System 2 mode bit14 ( <b>NSPMUTE</b> ) "H". (Refer to Chapter 5.13.NSPMUTE pin description and 6.3.system2 mode for details) |

|                                       | Absolute Zero Mute                                                                                                                                       | Set <b>PGMUTE</b> pin "L" or set up by serial control system2 mode bit15(PGMUTE) "H".  (Refer to Chapter 5.14. <b>PGMUTE</b> pin description and 6.3 system2 mode for details)      |

| Reverse Output Pins Function          | Reverse on Lch and Rch of output pins.                                                                                                                   | Set up by serial control system2 mode bit9 (CHSEL).                                                                                                                                 |

|                                       | Reverse for OUTL1- and OUTR1- of output pins.( Output OUTL1+ /R1+ data to OUTL1- /OUTR1-data.)                                                           | Set up by serial control system1 mode bit124(PWMHP). (Refer to Chapter 6.2. system1 mode for details.)                                                                              |

#### **5.13. NSPMUTE**

NSPMUTE pin is input to make for PWM output to 50% duty mute.

"L": PWM output 50% duty Mute. ""H": Mute release.

#### **5-14. PGMUTE**

**PGMUTE** pin is input to make PWM output to absolute zero mute.

"L": PWM output mute.

The case of System1 mode:bit24,PWMHP = "L"

**OUTL1** (+), **OUTL2** (+), **OUTR1** (+), **OUTR2** (+): "L" fixed

**OUTL1** (-), **OUTL2** (-), **OUTR1** (-), **OUTR2** (-): "H" fixed

The case of System1 mode:bit24,PWMHP = "H"

OUTL1 (+), OUTL2 (+), OUTR1 (+), OUTR2 (+) ,OUTL1(-),OUTR1(-) : "L" fixed

**OUTL2** (-), **OUTR2** (-): "H" fixed

"H": MUTE release.

**5.15 INIT**

INIT is the pin for reset to all functions of M65818AFP.

"L" level: (1). Clear of data memory. (2). Initialization of Serial Control.

(3). PWM output Duty 50 %.

"L" period needs more than 5 msec.

"H" level: usual operation.

"L">"H" rise edge: Resynchronization treatment, which is same at SYNC function.

## **5.16. TEST1, TEST2, TEST3**

**TEST1,TEST2**, and **TEST3** pins are test input for factory shipping test of M65818AFP.

**TEST1,TEST2,** and **TEST3** pins must be tied to "L" level on usual operation.

### 5.17. Power Supply and GND

Power supply and GND routes have 5 isolated lines.

(1) VddL1+, VssL1+, VddL1-, VssL1-, VddL2+, VssL2+, VddL2-, VssL2-, VddR1+, VssR1+, VddR1-, VssR1-, VddR2+, VssR2+, VddR2-, VssR2-, VssL, VddL, VssR, VddR

These pins are Power supply and GND for PWM output buffer block.

It has a pair of independent Power Supply, and GND to each 8 output pin. Power Supply voltage must be fixed at 5.0V.

(2)**XVdd, XVss**These pins are Power supply and GND for **XfsoIN** clock input block.

Power Supply voltage must be fixed at 5.0V.

(3)XOVdd, XOVss

**76 78**

These pins are Power supply and GND for XfsoOUT clock output block.

Power Supply voltage must be fixed at 5.0V.

(4)DVdd, DVss

**75 69**

These pins are Power supply and GND for digital block and fixed input/output buffer only for 3.3V (32,70-74 pins). Power Supply voltage must be fixed at 3.3V

### (5)BFVdd, BFVss

These pins are Power supply and GND for input/output buffer (3.3V/5V). In a case that **BFVdd** pin is applied at 5.0V, input/output voltage level of 34-67pins becomes 5.0V signal level. In another case that **BFVdd** pin is supplied at 3.3V, input/output pins (34-67 pins) becomes 3.3V signal level.

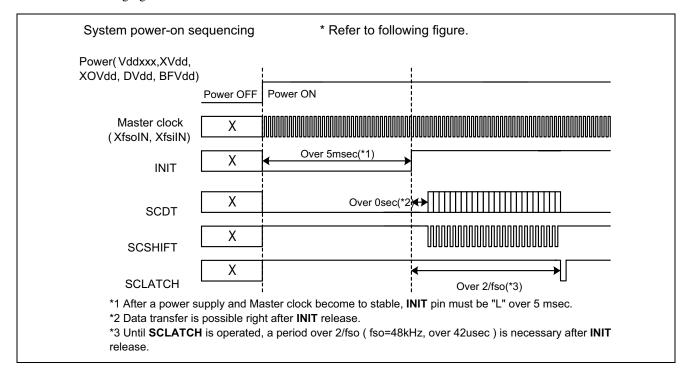

#### **5.18. Power sequences**

System power-on sequencing

\* Refer to following figure.

### 6. Serial Control

#### 6.1. Gain Control Mode

No setting bits means "Don't care".

| bit | Flag Name | <b>Functional Explanation</b>                 | Н                     | L          | INIT |

|-----|-----------|-----------------------------------------------|-----------------------|------------|------|

| 1   | MODE1     | Mode Setting 1                                |                       | "L" fixed  | _    |

| 2   | MODE2     | Mode Setting 2                                |                       | "L" fixed  | _    |

| 3   | TEST1     | Test Mode 1                                   |                       | "L" fixed  | L    |

| 4   | TEST2     | Test Mode 2                                   |                       | "L" fixed  | L    |

| 5   | NSLMT1    | Output Limit 1                                | Refer to Table 6-1-2. |            | L    |

| 6   | NSLMT2    | Output Limit 1                                | _                     |            | L    |

| 7   | GCONT1    | Channel selection for Gain Control Block 1    | L / R independence    | L/R common | L    |

| 8   | GCONT2    | Channel selection for Gain<br>Control Block 2 | Lch                   | Rch        | L    |

| 9   |           |                                               |                       |            | _    |

| 10  |           |                                               |                       |            | _    |

| 11  |           |                                               |                       |            |      |

| 12  | GAIN0     | Gain Data Index (MSB)                         |                       |            | H    |

| 13  | GAIN1     | Gain Data Index                               |                       |            | L    |

| 14  | GAIN2     | Gain Data Index                               |                       |            | L    |

| 15  | GAIN3     | Gain Data Index                               |                       |            | L    |

| 16  | GAIN4     | Gain Data Index (LSB)                         |                       |            | L    |

| 17  | GAIN5     | Gain Data Mantissa (MSB)                      |                       |            | H    |

| 18  | GAIN6     | Gain Data Mantissa                            |                       |            | L    |

| 19  | GAIN7     | Gain Data Mantissa                            |                       |            | L    |

| 20  | GAIN8     | Gain Data Mantissa                            |                       |            | L    |

| 21  | GAIN9     | Gain Data Mantissa                            |                       |            | L    |

| 22  | GAIN10    | Gain Data Mantissa                            |                       |            | L    |

| 23  | GAIN11    | Gain Data Mantissa                            |                       |            | L    |

| 24  | GAIN12    | Gain Data Mantissa (LSB)                      |                       |            | L    |

## • Output Limit (bit5,bit6:NSLMT1 ,NSLMT2 )

The M65818AFP has Over Flow Limit function which detects by input signal level and limit gain control.

Limit value is set by Gain Control Mode:bit5,bit6 "NSLMT1, NSLMT2" and System2 Mode:bit17"NSOBIT".

The limit value setting of Gain control block and PWM output.

Table (6-1-1a). Limit Value [In the case of 6bit mode, System2 mode:bit17(NSOBIT)="L"]

| DSLMT1 | DSLMT2 | Gain Block | PWM Output (Limit Value from DS Block ) |

|--------|--------|------------|-----------------------------------------|

| L      | L      | ±0.9375    | 63 values (±31)                         |

| Н      | L      | ±0.90625   | 61 values (±30)                         |

| L      | Н      | ±0.875     | 59 values (±29)                         |

| Н      | Н      | ±0.84375   | 57 values (±28)                         |

RENESAS

Table (6-1-1b). Limit Value [In the case of 5bit mode System2 mode:bit17(NSOBIT)="H"]

| DSLMT1 | DSLMT2 | Limit Value of Gain | PWM Output Value (Limit Value from $\Delta\Sigma$ Block) |

|--------|--------|---------------------|----------------------------------------------------------|

| L      | L      | ±0.90625            | 31 values (±15)                                          |

| Н      | L      | ±0.875              | 31 values (±15)                                          |

| L      | Н      | ±0.84375            | 29 values (±14)                                          |

| Н      | Н      | ±0.8125             | 29 values (±14)                                          |

• Channel Selection for Gain Control Block (bit7,bit8:GCONT1,GCONT2)

These bit selection enable to control gain data "L/R common" or "L/R independence".

GCONT1: "L"...L/Rch common, "H"...L/Rch independence.

$GCONT2: "L"...Rch\ only,\ "H"...Lch\ only.$

Bit8 is available only the case of `bit7 = "H"`.

• The index and Mantissa part of Gain Data. (bit12 -bit24,: GAIN0 -GAIN12 )

The Gain value is set from bit12 to bit24.

Index part: bit12 (MSB) to bit16(LSB) Mantissa part: bit17 (MSB) to bit24 (LSB)

The Gain Data is assigned 13bits, composed of Index part 5bits and of Mantissa part 8bits,

The range of Index parts is following statements.

Index part: 10100b(16.0) to 10000b(1.0) to  $00000b(2^{-16})$

The range of mantissa part is following as statement.

Index part; 10100b to 00001b: Mantissa part; 111111111b to 10000000b (128 step/1 Index).

Index part; 00000b: Mantissa part; 11111111b to00000000b (256 step).

Initial value: Index part: 10000b Mantissa part:10000000b infinity zero: Index part: 00000b Mantissa part:00000000b

#### # Notice of GAIN value Setting continuously

In the case of GAIN value Setting continuously, for example of Setting L/Rch independently, please take the interval time (pulse interval time of SCLATCH signal) more than 1/fso. For example, in the case of fso=48kHz, please take the interval time more than 21µsec.

• The Gain Data and Audio Output Level.

Gain data consists of 13bits (Index part; 5bit, Mantissa part; 8bit).

e.g. 10000b(1.0)/10000000b(0.5) means 0.5(0dB).

Table (6-1-2). The Gain Data and Output Level

| Gain Data          | Polarity      | <b>Absolute Output Value</b> | Output Level |

|--------------------|---------------|------------------------------|--------------|

| 10100/11111111 (b) | +             | 15.9375                      | +30.069dB    |

| to                 |               | to                           | to           |

| 10001/10000000 (b) |               | 1.0                          | +6.021dB     |

| to                 |               | to                           | to           |

| 10000/10000000 (b) |               | 0.5                          | 0dB          |

| 01111/11111111 (b) | <del></del> · | 0.498046875                  | -0.0340dB    |

| to                 |               | to                           | to           |

| 00000/10000000 (b) |               | 0.5* <sup>-16</sup>          | -96.330dB    |

| to                 |               | to                           | to           |

| 00000/00000001 (b) |               | 0.00390625*2-16              | -138.474dB   |

| 00000/00000000 (b) |               | infinity zero                | -∞           |

### • Calculation method of Gain value.

The way to calculation of Gain value from Gain Data is following equation.

Gain value =

$$20\log \left[ 2^{<\text{Index data (decimal value)-16>}} \times \frac{\text{Mantissa data (decimal value)}}{128} \right] dB$$

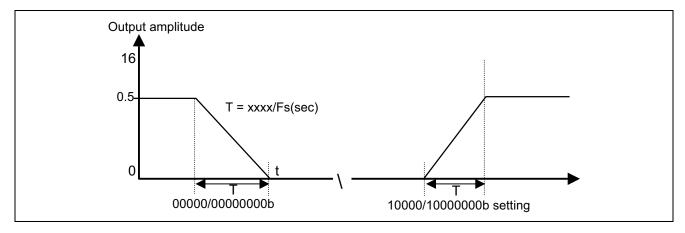

#### • Soft Mute.

The Soft Mute function is executed by setting of Gain Data as 00000/00000000b

( "/" :means dividing point between index part and mantissa part).

The release from Soft Mute function must be executed by setting the gain data before soft mute.

The Soft Mute function and release from there don't have linear curve but

have characteristics of approximate exponential curve.

#### • Operating time of Soft Mute

Total steps from Maximum value(10100b/111111111b) to Minimum value(00000b/00000000b)

$(128\text{steps/1 index}) \times (20\text{index} (10100\text{b}-10000\text{b})) + 256\text{steps} = 2816\text{steps}.$

The transition term of up and down depend on 2fso clock.

Therefore, in case of fso=48kHz, T=1/2fso=10.416µsec/step, transition term are following.

From Maximum value (10100b/1111111111b) to Minimum value (00000b/00000000b): 2816T=29.333msec. From 0dB value (10000b/10000000b) to Minimum value (00000b/0000000b): 2304T=24msec 6dB transition term (when over 00000b/10000000b (=-96dB) value ): 128T=1.333msec.

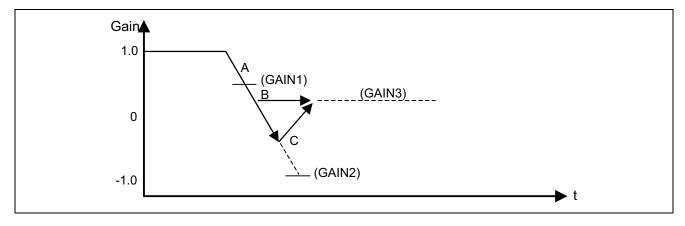

### • Soft Attenuate.

Transition from older Gain Attenuation to newer Gain Attenuation always operates with Soft Mute function.

For example, in case of Gain1 > Gain3 > Gain2, transition process is shown below.

At first, GAIN1 is operated, then second, GAIN2 is operated.

In case that GAIN2 is operated faster than GAIN1 of transition completion (refer to "A" situation in figure)

GAIN1 is ignored and data approaches at GAIN2.

Further, GAIN3 is operated faster than GAIN2 of transition completion( Refer to "B" or "C" situation in figure), GAIN2 is ignored and data approaches at GAIN3.

## 6.2. System1 Mode

| MODE1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit | Flag Name  | Functional Explanation        | Н                     | L            | INIT |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-------------------------------|-----------------------|--------------|------|

| Selection   Refer to Table 6-2-1.   L   L   L   L   L   L   L   L   L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1   | MODE1      | Mode Setting 1                |                       | "L" fixed    | _    |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2   | MODE2      | Mode Setting 2                | "H" fixed             |              | _    |

| 5         IBITO         Setting for Input Word Length         Refer to Table 6-2-2.         L           6         IBIT1         L         L           7         ISFO         Input Sampling Rate Selection         Refer to Table 6-2-3.         L           8         ISF1         EMPFS1         Fs selection for De-emphasis Filter         Refer to Table 6-2-4.         L           10         EMPFS2         L         L           11         DF1IMUTE         Zero Mute of DATA input Active Non-active         Non-active         L           12         DF2IMUTE         Zero Mute at sampling rate converter input         Active Non-active         —           13         don't care         —           14         don't care         —           15         don't care         —           16         ASYNCEN1         synchronous Detection Flag for Primary Side         enable         disable         L           17         don't care         —           18         don't care         —           19         don't care         —           20         ASYNC1MODE         Select process under asynchronization in primary side         Zero Mute         PWM:duty 50%         L           21         EXM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3   | IFMT0      | Input Format Selection        | Refer to Table 6-2-1. |              | L    |

| 6         IBIT1         L           7         ISF0         Input Sampling Rate Selection         Refer to Table 6-2-3.         L           8         ISF1         L         L           9         EMPFS1         Fs selection for De-emphasis Filter         Refer to Table 6-2-4.         L           10         EMPFS2         L         L           11         DF1IMUTE         Zero Mute of DATA input Active Non-active Active Non-active Converter input         L           12         DF2IMUTE         Zero Mute at sampling rate Converter input         Active Non-active Non-active Active Non-active Converter input         —           13         don't care Converter input         don't care Converter input Co                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4   | IFMT1      |                               |                       |              | L    |

| Texas   Isfo   Input Sampling Rate Selection   Refer to Table 6-2-3.   L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5   | IBIT0      | Setting for Input Word Length | Refer to Table 6-2-2. |              | L    |

| B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6   | IBIT1      |                               |                       |              | L    |

| Semantial Sema  | 7   | ISF0       | Input Sampling Rate Selection | Refer to Table 6-2-3. |              | L    |

| Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8   | ISF1       | -                             |                       |              | L    |

| 11 DF1IMUTE Zero Mute of DATA input Active Non-active L  12 DF2IMUTE Zero Mute at sampling rate converter input  13 don't care  14 don't care  15 don't care  16 ASYNCEN1 synchronous Detection Flag for Primary Side  17 don't care  18 don't care  19 don't care  20 ASYNC1MODE Select process under asynchronization in primary side  21 EXMODE Mode select of external 8fs data input side  22 PWMMODE0 Selection of Output PWM Form Refer to Table 6-2-5  L DATE Non-active Non-active Non-active Lactive Non-active Non-active Lactive Non-active Non-active Lactive Non-active Non-active Lactive Non-active Non-active Lactive Non-active Non-active Non-active Non-active | 9   | EMPFS1     | ·                             | Refer to Table 6-2-4. |              | L    |