SONY

# **CXB1549Q**

# Laser Diode Driver

#### Description

The CXB1549Q is a high-speed monolithic Laser Diode Driver/Current Switch with ECL/PECL input level. Open collector outputs are provided at the output pins (Q, QBX) and have the capacity of driving modulation current of 50mAp-p at a max. data rate of 1.25Gbps (Min.). Along with the modulation current generator there is the laser diode bias generator which has capacity of sourcing up to 60mA (Bias). The laser diode current can be controlled by either a voltage or current into the bias adjust pin (BiasAdj) and the bias set pin (SBias), depending on how these pins are configured. Control of the diode bias current is achieved through the APC (Automatic Power Control) circuitry. In order to avoid having a large current go through the laser diode, this IC also provides an Activity detector and Power on Reset functions for Laser Safety. The Activity detector circuit detects data edge transitions and if no data transition occur after a certain time period, then both the modulation and bias current are shutdown.

The Power on Reset circuit holds the modulation and bias current off for a set period of time while the system power is applied. Additionally, this IC has an internal Duty Cycle correction circuit that can control the falling edge of the input pulse up to a maximum of 0.2ns (Min.).

#### Features

- Maximum data rate (NRZ): 1.25Gbps

- Power on Reset function

- Alarm and Shutdown function

- Signal Duty cycle correction

- Automatic Power Control (APC) for bias current

- · Activity detector function for laser safety

- Power indicate function

- Differential PECL inputs or AC coupled inputs

#### Application

- Gbit-ethernet: 1.25Gb/s

- SONET/SDH: 622Mb/s

- Fibre channel: 532Mb/s,1.062Gb/s

#### **Absolute Maximum Ratings**

|                                    | -                                             |              |    |  |  |  |

|------------------------------------|-----------------------------------------------|--------------|----|--|--|--|

| <ul> <li>Supply voltage</li> </ul> | Vcc – Vee                                     | -0.3 to +6.0 | V  |  |  |  |

| <ul> <li>Input voltage</li> </ul>  | Vin                                           | VEE to Vcc   | V  |  |  |  |

| • Differential input               | voltage                                       |              |    |  |  |  |

|                                    | Vd – Vdb                                      | 0 to 2.5     | V  |  |  |  |

| Bias output curre                  | ent                                           | 0 to 80      | mA |  |  |  |

| Modulation output                  | <ul> <li>Modulation output current</li> </ul> |              | mΑ |  |  |  |

| SBias input/output                 | 0 to 5                                        | mΑ           |    |  |  |  |

| Input bias contro                  | l current                                     |              |    |  |  |  |

|                                    | lset (Ibiasadj)                               | 0 to 5       | mΑ |  |  |  |

| Input bias contro                  |                                               |              |    |  |  |  |

| Vset (Vbiasadj)                    |                                               | 0 to 3       | V  |  |  |  |

| Storage temperature                |                                               |              |    |  |  |  |

|                                    | Tstg                                          | -65 to +150  | °C |  |  |  |

|                                    |                                               |              |    |  |  |  |

#### **Recommended Operating Conditions**

DC power supply voltage Vcc - VEE 3.14 to 3.46 V

Operating ambient temperature Ta -40 to +85 °C

#### Structure

Bipolar silicon monolithic IC

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

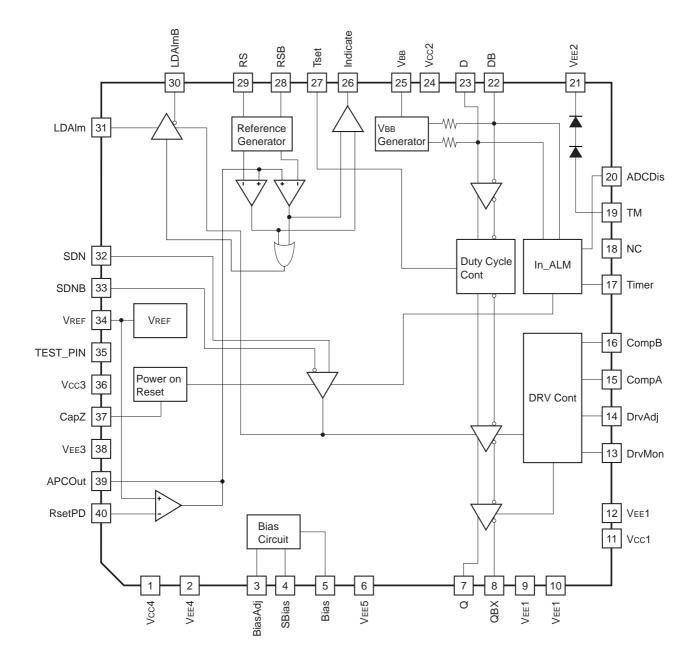

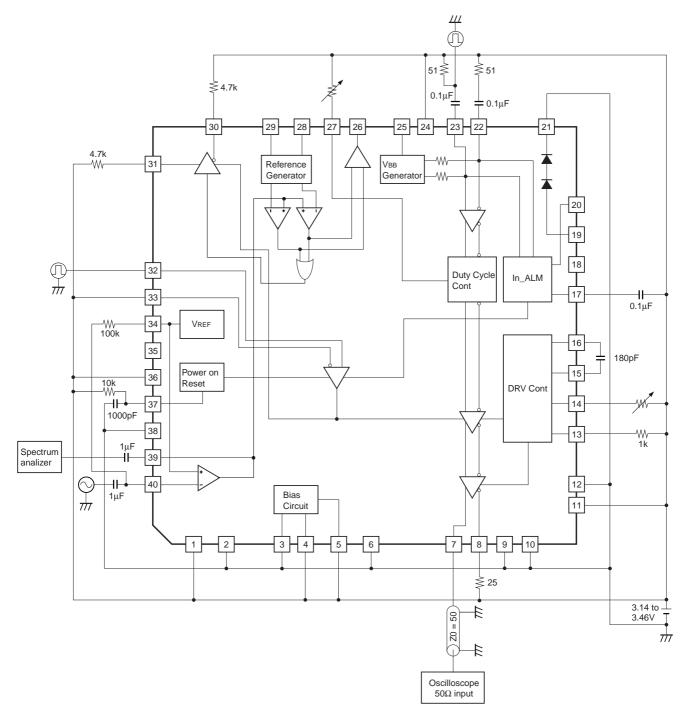

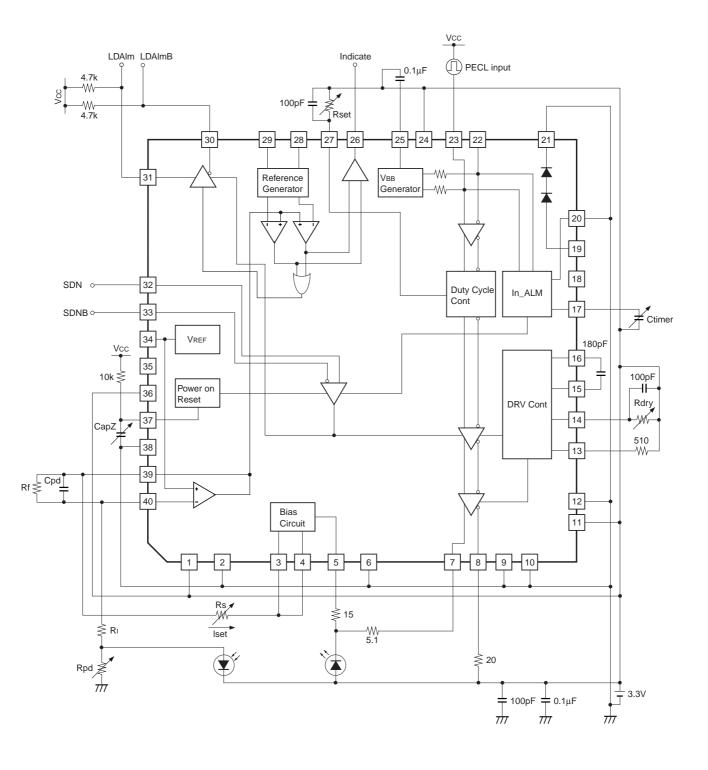

# **Block Diagram and Pin Assignment**

# **Pin Description**

| Pad   | Symbol  | Typical v          | oltage [V]                                                   | Equivalent circuit                              | Description                                                                                                                             |

|-------|---------|--------------------|--------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| No.   | Cynisor | DC                 | AC                                                           |                                                 |                                                                                                                                         |

| 1     | Vcc4    | 3.3                |                                                              |                                                 | Positive power supply<br>pin for APC circuit.                                                                                           |

| 2     | Vee4    | 0                  |                                                              |                                                 | Negative power supply pin for APC circuit.                                                                                              |

| 3     | BiasAdj | 1.5 to 0           |                                                              |                                                 | Sets Laser bias current pin.                                                                                                            |

| 4     | SBias   | 0mA<br>to<br>2.5mA |                                                              | 3<br>10pF<br>3                                  | Sets Laser bias current or monitor pin.                                                                                                 |

| 5     | Bias    | 0mA<br>to<br>60mA  |                                                              |                                                 | Laser bias current<br>output.<br>Open collector output.                                                                                 |

| 6     | Vee5    | 0                  |                                                              |                                                 | Negative power supply<br>pin for Bias circuit.                                                                                          |

| 7     | Q       | 1.3 to 3.3         | 6mA to<br>30mA <sup>*1</sup><br>6mA to<br>50mA <sup>*2</sup> | 78                                              | Laser modulation<br>current output.<br>Open collector output.                                                                           |

| 8     | QBX     | 1.3 to 3.3         | 6mA to<br>30mA*1<br>6mA to<br>50mA*2                         | VEE VEE                                         | Complementary current<br>output.<br>Q and QBX are<br>not symmetrical output.<br>Please uses Q output<br>for Laser modulation.           |

| 9, 10 | Vee1    | 0                  |                                                              |                                                 | Negative power supply<br>pin for Driver circuit.                                                                                        |

| 11    | Vcc1    | 3.3                |                                                              |                                                 | Positive power supply<br>pin for Driver circuit.                                                                                        |

| 12    | Vee1    | 0                  |                                                              |                                                 | Negative power supply<br>pin for Driver circuit.                                                                                        |

| 13    | DrvMon  |                    | 0μA<br>to<br>600μA                                           | Vcc<br>Rdrv<br>Rdrv<br>Rmon<br>14<br>13<br>Rmon | Sets Laser modulation<br>current (IQ) monitor.<br>IQ is monitored by<br>connecting a resistor<br>(Rmon) to this pin.                    |

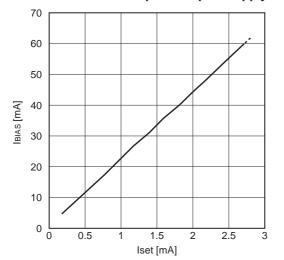

| 14    | DrvAdj  |                    | 0μA<br>to<br>600μA                                           | VEE                                             | Sets Laser modulation<br>current (IQ).<br>IQ is controlled by<br>connecting a resistor<br>(Rdrv) to this pin.<br>Please refer to Fig.2. |

\*1 Ta = -40 to 0°C

\*2 Ta = 0 to +85°C

| Pad | Symbol | Typical v                  | oltage [V] | Equivalent circuit                                                                   | Description                                                                                                                                                                                                                                   |

|-----|--------|----------------------------|------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Gymbol | DC                         | AC         |                                                                                      | Description                                                                                                                                                                                                                                   |

| 15  | CompA  |                            |            |                                                                                      | Modulation current<br>driver compensation.<br>Normally, connects<br>180pF Capacitor across<br>CompA and CompB<br>pins.                                                                                                                        |

| 16  | CompB  |                            |            | VEE                                                                                  |                                                                                                                                                                                                                                               |

| 17  | Timer  |                            |            | Vcc<br>Ctimer<br>25μA<br>VEE<br>Vcc<br>2.1k<br>2.1k<br>2.4k<br>2.4k<br>10pF<br>200μA | Capacitor port for<br>activity detector<br>(IN_ALM) operation.<br>This pin set the period<br>of inactive time for<br>activity detector.<br>Inactive time is<br>controlled by connecting<br>a capacitor to this pin.<br>Please refer to Fig.6. |

| 18  | NC     |                            |            |                                                                                      | No Connect pin.                                                                                                                                                                                                                               |

| 19  | ТМ     | 1.5                        |            | (19) H GND (21)                                                                      | Chip temperature monitor pin.                                                                                                                                                                                                                 |

| 20  | ADCDis | VEE<br>to<br>Vcc<br>(open) |            | Vcc<br>3.8k<br>35k<br>35k<br>35k<br>35k<br>35k<br>35k<br>35k<br>15μA                 | This pad control the<br>activity detector Circuit.<br>High (connected to Vcc<br>or open): an activity<br>detector is disable.<br>Low (connected to GND):<br>an activity detector is<br>enable.                                                |

| 21  | Vee2   | 0                          |            |                                                                                      | Negative power supply pin for Data input circuit.                                                                                                                                                                                             |

| Pad | Symbol   | Typical v | oltage [V] | Equivalent circuit                                                                                                                                                                                                                                                             | Description                                                                                                                                                                                                                                                                                        |

|-----|----------|-----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. |          | DC        | AC         |                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                    |

| 22  | DB       |           | 1.6 to 2.4 | 24<br>▲ 300 美 美 300 _ ▲                                                                                                                                                                                                                                                        | Differential PECL data<br>inputs pins.<br>These two inputs are                                                                                                                                                                                                                                     |

| 23  | D        |           | 1.6 to 2.4 | 22<br>200<br>400<br>200<br>400<br>200<br>10k<br>00<br>10k                                                                                                                                                                                                                      | internally biased by $10k\Omega$ to VBB.                                                                                                                                                                                                                                                           |

| 24  | Vcc2     | 3.3       |            |                                                                                                                                                                                                                                                                                | Positive power supply pin for Data input circuit.                                                                                                                                                                                                                                                  |

| 25  | Vвв      | 2         |            | (21) 600μA 600μA                                                                                                                                                                                                                                                               | Reference bias voltage.<br>(Option)                                                                                                                                                                                                                                                                |

| 26  | Indicate |           | 0.7 to 1.7 | Vcc<br>↓ 50µA ↓ 35µA ↓ 35µA<br>26 ↓ 100k ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓                                                                                                                                                                                                   | The analog voltage high impedance output which indicate of whether the optical power of Laser diode is operated normal or not. The power output range has following relationship.<br>High Light Indication; $Vo \ge 1.7V$<br>Nominal Operation; $Vo = 1.2V$<br>Low Light Indication; $Vo \le 0.7V$ |

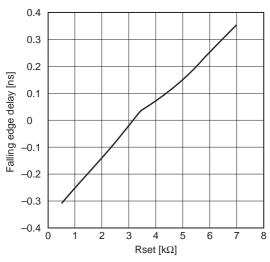

| 27  | Tset     |           |            | Vcc<br>2.4k 2.4k 20pF<br>70μA<br>VEE<br>220 5 5140<br>Rset 5<br>27<br>27<br>27<br>27<br>27<br>20<br>27<br>27<br>20<br>27<br>20<br>27<br>20<br>27<br>20<br>27<br>20<br>27<br>20<br>27<br>20<br>27<br>20<br>20<br>27<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20 | Selector for duty cycle<br>control.<br>This pin controls the<br>trailing edge of the input<br>high pulse. Variable<br>delay limit of that is from<br>0 to 0.2ns. Duty cycle is<br>controlled by connected<br>a resistor value between<br>Vcc and this pin.<br>Please refer to Fig.1.               |

| 28  | RSB      | 0.5       |            | Vcc<br>↓ 100µA<br>≥2.5k                                                                                                                                                                                                                                                        | Sets alarm (fail)<br>threshold assert voltage<br>by external resistors for<br>LD_ALARM.                                                                                                                                                                                                            |

| 29  | RS       | 2.5       |            | 28<br>↓ 5k<br>VEE                                                                                                                                                                                                                                                              | Default voltages are<br>RS equal to 2.5V and<br>RSB equal to 0.5V.<br>(Option)                                                                                                                                                                                                                     |

| Pad | Symbol       | Typical v | oltage [V] | Equivalent circuit                                                      | Description                                                                   |  |

|-----|--------------|-----------|------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|

| No. | Gymbol       | DC        | AC         |                                                                         | Description                                                                   |  |

| 30  | LDAImB       |           | 0.2 to 3   |                                                                         | Complementary open<br>collector TTL outputs.<br>Asserted when the fault       |  |

| 31  | LDAim        |           | 0.2 to 3   |                                                                         | Asserted when the fault<br>is detected in the Laser<br>monitor diode circuit. |  |

| 32  | SDN          |           | 0 to 3.3   | Vcc<br>300<br>32<br>√cc<br>5k ≶5k<br>5k ≶5k<br>300<br>300<br>300<br>300 | Complementary TTL inputs to disable output                                    |  |

| 33  | SDNB         |           | 0 to 3.3   | <u>33</u><br><u>Vee</u><br><u>Vee</u><br><u>60</u> µА<br><u>60</u> µА   | current.<br>When left open = "High"                                           |  |

| 34  | Vref         | 1.7       |            | Vcc<br>300 ≤ ≤ 300<br>34<br>2.4k ≤ 1.9mA<br>VEE 9.1k                    | Temperature<br>compensated reference<br>voltage for APC.<br>1.7V (Constant.)  |  |

| 35  | TEST_<br>PIN | OPEN      |            |                                                                         | Do not connect.                                                               |  |

| 36  | Vcc3         | 3.3       |            |                                                                         | Positive power supply<br>IC for Signal Detect<br>circuit.                     |  |

| Pad | Symbol | Typical ve | oltage [V] | Equivalent circuit                          | Description                                                                                                                                                                                                                                          |

|-----|--------|------------|------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Symbol | DC         | AC         | Equivalent circuit                          | Description                                                                                                                                                                                                                                          |

| 37  | CapZ   |            |            | Vcc<br>Rseries<br>3k<br>Cap_Z<br>VEE<br>VEE | Capacitor and resistor<br>port for slow start up.<br>This pin controls the<br>initial turn-on time of<br>this chip. (bias and<br>modulation current)<br>The time for this function<br>is set by an external RC<br>network.<br>Please refer to Fig.7. |

| 38  | Vee3   | 0          |            |                                             | Negative power supply<br>pin for Signal Detect<br>circuit.                                                                                                                                                                                           |

| 39  | APCOut |            |            |                                             | Output pad of APC OP-<br>Amp.<br>This signal control to<br>bias adjust pins.<br>(BiasAdj and SBias)                                                                                                                                                  |

| 40  | RsetPD |            |            | Vcc<br>300 ≥ 300<br>40<br>VEE               | Monitor PD connect<br>pad.                                                                                                                                                                                                                           |

# **Electrical Characteristics**

#### **DC Electrical Characteristics**

| Item                                | Symbol           | Condition                       | Min.       | Тур. | Max.       | Unit |

|-------------------------------------|------------------|---------------------------------|------------|------|------------|------|

| DC Power supply voltage             | Vdc              | Vcc – Vee                       | 3.14       | 3.3  | 3.46       | V    |

| Power supply current                | IEE              | $I_Q = 0mA$ , $I_{BIAS} = 0mA$  | -76        | -59  |            |      |

|                                     | lq1              | Ta = -40 to 0°C                 | 6          | _    | 30         | mA   |

| Modulation output current range     | lq2              | Ta = 0 to +85°C                 | 6          |      | 50         |      |

| Modulation output voltage range     | Vq               |                                 | Vcc – 2    |      | Vcc        | V    |

| Bias output current range           | Ів               |                                 | 0          |      | 60         | mA   |

| Bias output voltage range           | Vв               |                                 | Vcc – 2    |      | Vcc        | V    |

| Ratio of IB vs. Iset                | IBvslset         |                                 | 14         | 22   | 27         | _    |

| ECL input High voltage              | Veih             |                                 | Vcc – 1.17 |      | Vcc – 0.81 |      |

| ECL input Low voltage               | Veil             |                                 | Vcc – 1.84 |      | Vcc – 1.48 |      |

| SDN, SDNB, Reset input High voltage | Vтін             |                                 | 2          |      | Vcc        |      |

| SDN,SDNB, Reset input Low voltage   | V⊤iL             |                                 | 0          |      | 0.8        | V    |

| LDA, LDAB output High voltage       | Vтон             | Іон = –10µА, RL = 4.7k $\Omega$ | Vcc - 0.1  |      | Vcc + 0.2  |      |

| LDA, LDAB output Low voltage        | Vtol             | $IOL = 1mA, RL = 4.7k\Omega$    | 0          |      | 0.4        |      |

| Reference bias voltage for OP Amp   | Vref             |                                 | 1.5        | 1.7  | 1.9        |      |

| Operating current range of VREF     | Vref <b>dr</b> v |                                 | -500       |      | +500       | μA   |

#### (Vcc = 3.14 to 3.46V, VEE = 0V, Ta = -40 to +85°C)

#### **AC Electrical Characteristics**

(Vcc = 3.14 to 3.46V, VEE = 0V, Ta = -40 to +85°C)

| Item                                                 | Symbol   | Condition            | Min. | Тур. | Max. | Unit |

|------------------------------------------------------|----------|----------------------|------|------|------|------|

| Maximum Data Rate                                    | fdmax    |                      | 1.25 |      | —    | Gbps |

| Rise time (20 to 80%)                                | tr       | lq = 20mA, R∟ = 25Ω  | _    | 100  | —    | ps   |

| Fall time (20 to 80%)                                | tf       | lq = 20mA, R∟ = 25Ω  | _    | 200  | —    |      |

| Max. variable High pulse width by duty cycle control | tdelay   | Data rate = 1.25Gbps | 0.2  | _    | —    | ns   |

| Max. setting time range of IN_Alarm                  | ts_alm   |                      | 20   |      | _    |      |

| Max. setting time range of POR                       | ts_por   |                      | 150  |      |      | μs   |

| Shut down time                                       | tsut_off |                      | _    | _    | 10   |      |

| Shut down recovery time                              | tsut_on  |                      |      | _    | 100  |      |

# DC and AC Electrical Characteristics for OpAmp of APC Circuitry

| Item                       | Symbol | Condition | Min. | Тур. | Max. | Unit |

|----------------------------|--------|-----------|------|------|------|------|

| Input voltage range        | Vin    |           | 1.2  | —    | 2.8  | V    |

| Output voltage range       | Vo     |           | 0.6  |      | 2    | V    |

| Input bias current         | Ів     |           |      | 7    | _    | μA   |

| Input offset voltage       | Voff   |           |      | 2.5  | _    | mV   |

| Input offset Input current | IOFF   |           |      | 0.7  | _    | μA   |

| Input impedance            | Zin    |           |      | 12   | _    | kΩ   |

| Output drive current       | lo     |           | -5.0 |      | 1.0  | mA   |

| Through rate               | SR     |           |      | 1.9  | _    | V/µs |

| Open loop gain             | Av     |           |      | 55   | _    | dB   |

| Unity gain band-width      | funit  |           |      | 20   | _    | MHz  |

#### Description of each function block

#### 1. Data Buffer

Data Buffer is comprised of the data buffer and delay generator. ECL/PECL data is input to the data buffer at a maximum data rate of 1.25Gbps. This data is buffered and input to the delay circuitry. The delay circuitry adds a delay to the falling edge of the pulse up to a maximum of 0.2ns (Min.). The delay is set by a single external resistor between the delay set pin (Tset-Pin 27) and Vcc. A plot of the high pulse width vs. set resistance (Rset) is shown in Fig. 1.

#### 2. VBB Generator

This circuit provides a reference bias voltage to the data buffer for AC coupling inputs.

#### 3. Modulation Current Generator

This circuit can sink up to 50mA of current to modulate the laser diode. The modulation current is set by an external resistor to Vcc at modulation current set pin (DrvAdj-Pin 14). There is also a modulation current monitor pin (DrvMon-Pin 13) that allows the IC user to monitor the modulation current. By putting an external fixed resistor between Vcc and DrvMon pin, you can monitor the modulation current by measuring the voltage of DrvMon pin. A plot of the modulation current vs. setting resistance (Rdrv) is shown in Fig. 2.

#### 4. Laser Diode Bias Current Generator

This circuit is a very large current source capable of sourcing up to 60mA of current to bias the laser diode on. The circuit is a 22 to 1 current mirror that can be controlled externally two ways.

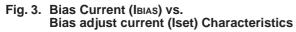

The first of these is to tie the BiasAdj (Pin 3) and SBias (Pin 4) terminals together and inject a current into the two terminals. The Bias (Pin 5) terminal is connected to the laser diode. Laser diode bias current vs. control current (lset) characteristics is shown in Fig. 3.

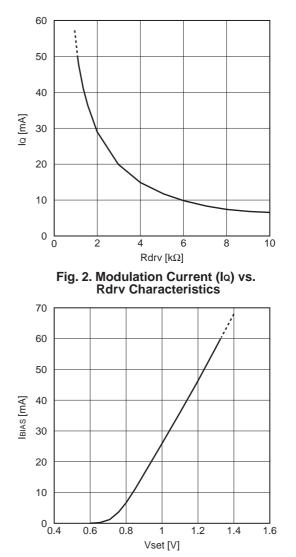

The second method of controlling the laser diode current is to ties the SBias (Pin 4) terminal to Vcc and tune the BiasAdj (Pin 3) terminal with a voltage source. Varying the voltage at the BiasAdj terminal will vary the current through the laser diode. Laser diode bias current vs. control voltage characteristics is shown in Fig. 4.

## 5. APC (Automatic Power Control) Circuitry

The APC Circuitry is comprised of the window comparator, APC OpAmp, laser diode alarm circuit and the diode power indicator.

The APC OpAmp is normally configured as an inverting integrator. The inverting input is connected to the photo diode that monitors the light intensity from the laser diode. The photo diode converts the received light from the laser diode to a current. The output of the OpAmp then drives the laser diode current bias adjust pin, and the laser diode bias set pin is held at Vcc. With the OpAmp configured as an inverting integrator, the OpAmp can tune the diode current inversely to the current in the photo diode. That is to say that if a low current is detected by the photo diode the integrator output goes up causing more bias current to go through the diode. If the photo diode current is high, then the output of the OpAmp will go low causing less bias current to flow through the laser diode.

The output of the APC OpAmp drives a window comparator. The function of the window comparator is to detect when the output of the APC OpAmp goes above or below a preset reference voltage for each comparator (RS, RSB). When this happens the comparators outputs cause the laser diode alarm circuit (LDAIm) to go high alerting the system that the laser diode current is either to high or to low.

The window comparator also drives the laser diode power indicator circuit (Indicate). This circuit is comprised of two switches and one fixed current sources. When the APC OpAmp output is such that the laser diode bias current is at its nominal set point, the output of the power indicator is at 1.2Vdc. If the APC OpAmp output goes low, the output of the power indicator increases to 1.7Vdc, indicating a high laser diode power condition. If the output of the APC OpAmp goes high, the output of the power indicator drops to 0.7Vdc.

Also connected to the output of the window comparator is laser alarm circuitry. This circuit alerts the user of the device when the laser diode power level has risen either twice the normal set power or half the normal set power. A high voltage at the laser diode alarm output indicates an alarm event. The laser diode alarm output is disabled whenever a shutdown event is encountered.

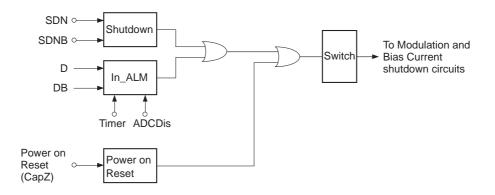

## 6. Shutdown and Input Alarm Circuitry

This portion of the circuit disables both the modulation current driver and the laser diode bias generator under various conditions. The function block diagram for all of the shutdown mechanisms for the circuit is shown in Fig. 5. Shown below is the signal priority primarily for the reset function.

1) Power on Reset

2) Shutdown, Input Alarm

The Shutdown circuit has complementary TTL input to disable output current. Shown below is the desired truth table for the shutdown function.

| SDN  | SDNB | output current |

|------|------|----------------|

| Low  | Low  | Off            |

| Low  | High | On             |

| High | Low  | Off            |

| High | High | Off            |

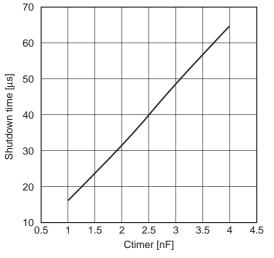

The Activity detector (In\_ALM) circuit is designed to detect an input pulse transition. If there is no input pulse transition over a period time determined by the user, then the output of the circuit will go high causing the modulation current and laser bias current to be shutdown. Inactive time is set by external capacitor value between Timer pin (Pin 17) and Vcc. Inactive time vs. Ctimer is shown in Fig.6.

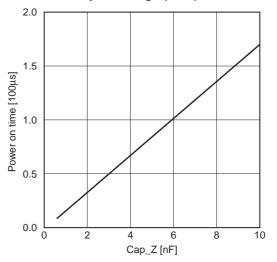

The Power on reset circuit is an inverting comparator that has an external RC network with CapZ pin (Pin 37) that is connected between Vcc and VEE. At power up, the RC begins to charge up towards the reference voltage of the comparator. Since this is an inverting comparator the output will stay high until the capacitor charges above the reference. As long as the comparator output is high, the laser diode is disabled. As soon as the capacitor charges up beyond the reference, the output of the circuit goes low and the laser diode is enabled and ready for normal operation. A plot of the power on reset time vs. capacitance for a  $10k\Omega$  resistor (Rseries) is shown in Fig. 7.

Fig.5. Shutdown and In\_ALM Functional Block Diagram

#### 7. Others

Pay attention to handling this IC because its electrostatic discharge strength is weak. The Tset terminal (27pin) has to be connected through a resistor to Vcc. Do not leave this pin open or connect to Vcc directly.

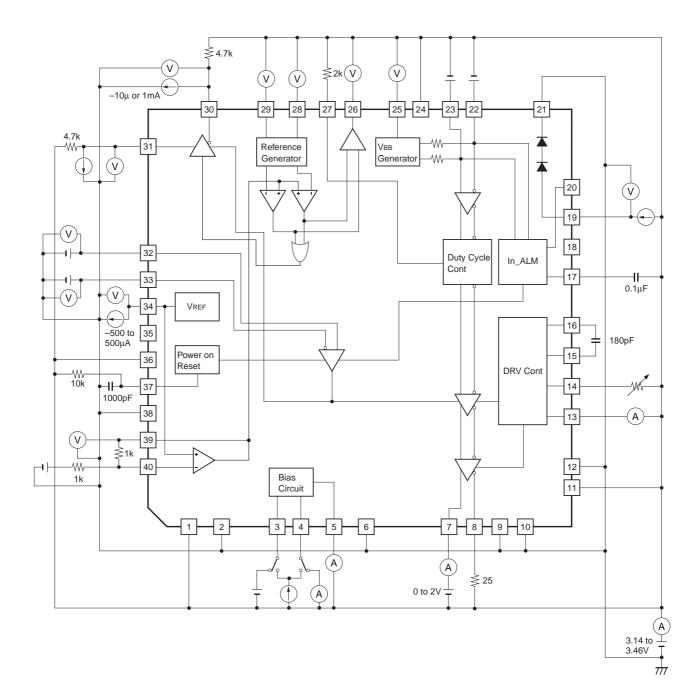

## **DC Electrical Characteristics Measurement Circuit**

### **AC Electrical Characteristics Measurement Circuit**

#### **Application Circuit** (at Vcc = 3.3V, VEE = 0V)

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

#### **Example of Representative Characteristics**

Fig. 6. Shutdown Time vs. Ctimer Characteristics

Fig. 4. Bias Current (IBIAS) vs. Bias adjust voltage (Vset) Characteristics

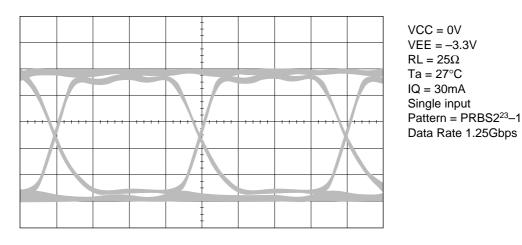

Ch.1 :150mV/div, Offset: -300mV Bandwidth: 20.0GHz Time Base : 200ps/div

#### Fig.8. Electrical output waveform

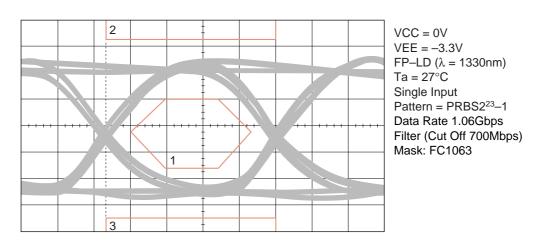

Ch.2 :5.0mV/div, Offset: 12.8mV Bandwidth: 12.4GHz Time Base:200ps/div

Fig.9. Optical output waveform

#### CXB1549Q

# CXB1549Q

| PIN# | PIN NAME | PIN# | PIN NAME |

|------|----------|------|----------|

| 1    | Vcc4     | 21   | Vee2     |

| 2    | VEE4     | 22   | DB       |

| 3    | BiasAdj  | 23   | D        |

| 4    | SBias    | 24   | Vcc2     |

| 5    | Bias     | 25   | Vвв      |

| 6    | Vee5     | 26   | Indicate |

| 7    | Q        | 27   | Tset     |

| 8    | QBX      | 28   | RSB      |

| 9    | VEE1     | 29   | RS       |

| 10   | VEE1     | 30   | LDAImB   |

| 11   | Vcc1     | 31   | LDAIm    |

| 12   | VEE1     | 32   | SDN      |

| 13   | DrvMon   | 33   | SDNB     |

| 14   | DrvAdj   | 34   | Vref     |

| 15   | CompA    | 35   | TEST_PIN |

| 16   | CompB    | 36   | Vcc3     |

| 17   | Timer    | 37   | CapZ     |

| 18   | NC       | 38   | Vee3     |

| 19   | ТМ       | 39   | APCOut   |

| 20   | ADCDis   | 40   | RsetPD   |

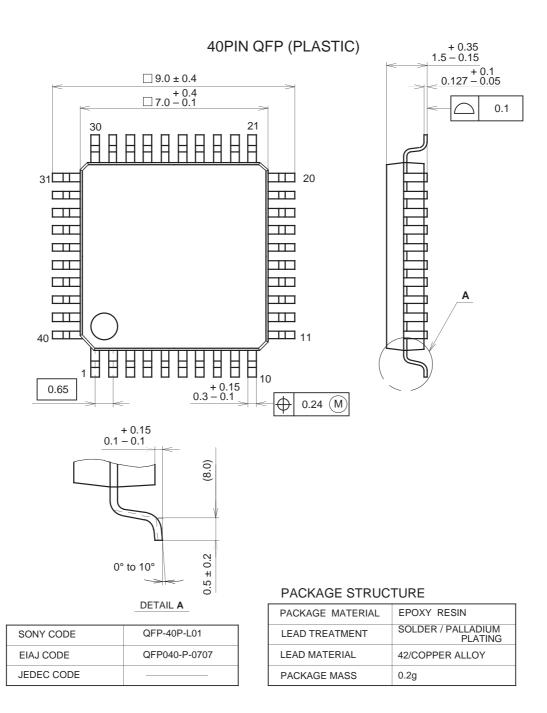

Package Outline Unit: mm

#### NOTE : PALLADIUM PLATING This product uses S-PdPPF (Sony Spec.-Palladium Pre-Plated Lead Frame).