## **Errata Sheet V1.0**

This Errata Sheet refers to:

The following datasheets:

AT91M63200 Summary, Rev. 1028DS-05/00

AT91M63200, Rev. 1028A-10/99

AT91M43300 Summary, Rev. 1322A-10/99

AT91M43300, AT91M63200 Electrical Characteristics, Rev. 1090B-05/00

176-lead TQFP and 144-ball BGA devices with the following markings:

## 6. Warning: Additional NWAIT Constraints

When the NWAIT signal is asserted during an external memory access, the following EBI behavior is correct:

- NWAIT is asserted before the first rising edge of the master clock and respects the NWAIT to MCKI rising setup timing as defined in the Electrical Characteristics datasheet.

- NWAIT is sampled inactive and at least one standard wait state remains to be executed, even if NWAIT does not meet the NWAIT to first MCKI rising setup timing (i.e., NWAIT is asserted only on the second rising edge of MCKI).

In these cases, the access is delayed as required by NWAIT and the access operations are correctly performed.

In other cases, the following erroneous behavior occurs:

- 32-bit read accesses are not managed correctly and the first 16-bit data sampling takes into account only the standard wait states. 16- and 8-bit accesses are not affected.

- During write accesses of any type, the NWE rises on the rising edge of the last cycle as defined by the programmed number of wait states. However, NWAIT assertion does affect the length of the total access. Only the NWE pulse length is inaccurate.

At maximum speed, asserting the NWAIT in the first access cycle is not possible, as the sum of the timings "MCKI Falling to Chip Select" and "NWAIT setup to MCKI rising" are generally higher than one half of a clock period. This leads to using at least one standard wait state. However, this is not sufficient except to perform byte or half-word read accesses. Word and write accesses require at least two standard wait states.

# AT91 ARM<sup>®</sup> Thumb<sup>®</sup> Microcontrollers

AT91M63200 AT91M43300 Errata Sheet V1.0

The following waveforms further explain the issue:

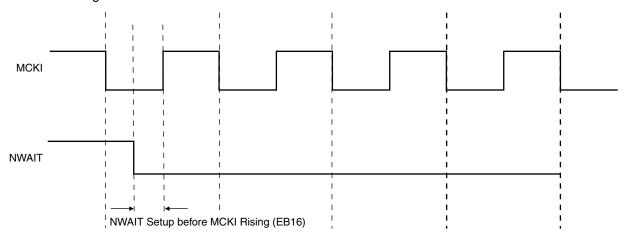

If the NWAIT setup time is satisfied on the first rising edge of MCKI, the behavior is accurate. The EBI operations are not affected when the NWAIT rises.

Figure 1. NWAIT Rising

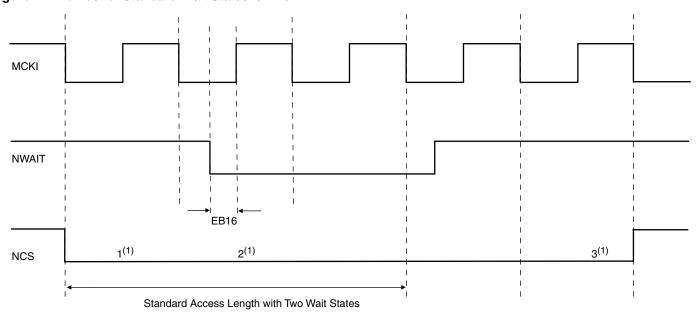

If the NWAIT setup time is satisfied on the following edges of MCKI and if at least one standard wait state remains to be executed, the behavior is accurate. In the following example, the number of standard wait states is two. The NWAIT setup time on the second rising edge of MCKI must be met.

Figure 2. Number of Standard Wait States is Two

Note: 1. These numbers refer to the standard access cycles.

2

## AT91M63200/AT91M43300 Errata Sheet

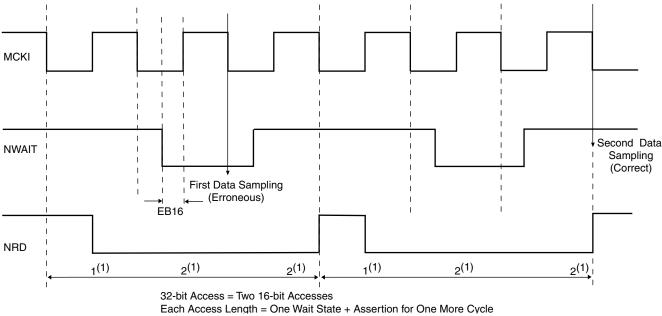

If the first two conditions are not met during a 32-bit read access, the first 16-bit data is read at the end of the standard 16-bit read access. In the following example, the number of standard waits is one. NWAIT assertions do affect both NRD pulse lengths, but first data sampling is not delayed. The second data sampling is correct.

Note: 1. These numbers refer to the standard access cycles.

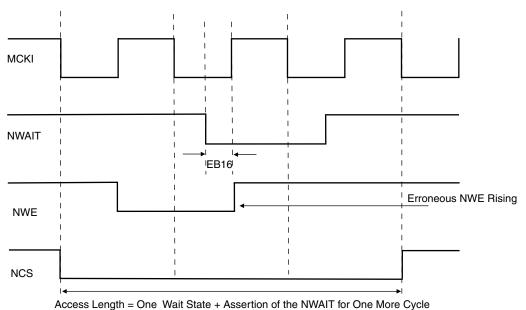

If the first two conditions are not met during write accesses, the NWE signal is not affected by the NWAIT assertion. The following example illustrates the number of standard wait states. NWAIT is not asserted during the first cycle, but is asserted at the second and last cycle of the standard access. The access is correctly delayed as the NCS line rises accordingly to the NWAIT assertion. However, the NWE signal waveform is unchanged, and rises too early.

Figure 4. Description of the Number of Standard Wait States

## 5. AT91M63200 Datasheet - Page 99

#### Problem Fix/Workaround

The reset value of the Status Register does not need to be defined at zero. The status of the SPI is updated at each cycle after the reset and the SPENDRX and SPENDTX bits are set, because the PDC counters are 0.

## 4. AT91M63200 Datasheet - Page 141

#### Problem Fix/Workaround

The correct description of the CPU bit is:

0 = CPU clock is disabled

1 = CPU clock is enabled

## 3. Initializing SPI in Master Mode May Cause a Mode Fault Detection:

### **Problem Fix/Workaround**

PA26/NPCS0/NSS pin must be pulled up to the V<sub>DDIO</sub> power supply.

PA26/NPCS0/NSS must be defined as a peripheral pin before programming the SPI peripheral.

#### 2. SPI in Slave Mode Does not Work

In transmission, the data to be transmitted (written in SP\_TDR) is transferred into the shift register and, consequently, the TDRE bit in SP\_SR is set to 1. Though the transfer has not begun, when the following data is written in SP\_TDR, it is also transferred into the shift register, crushing the preceding data and setting the bit TDRE to 1.

#### Problem Fix/Workaround

No workaround available.

## 1. Parity Error Bit (PARE) is Set Too Early

The Parity Error bit on the USART is set as soon as the parity bit is detected. However, the faulty character reception status (RXRDY) is set afterwards, only when the stop bit is detected. This is particularly unfortunate when working in Multi-drop mode, as the PARE bit identifies the Address Bytes. When it is detected, the corresponding character has not yet been transferred in the US\_RHR register and, therefore, is not yet available.

#### **Problem Fix/Workaround**

No problem fix/workaround to propose.

## **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

#### Europe

Atmel SarL Route des Arsenaux 41 Casa Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Atmel Asia, Ltd.

Room 1219

Chinachem Golden Plaza

77 Mody Road Tsimhatsui

East Kowloon

Hong Kong

TEL (852) 2721-9778

FAX (852) 2722-1369

#### Iapan

Atmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

## **Atmel Operations**

## Memory

Atmel Corporate 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 436-4270 FAX 1(408) 436-4314

#### Microcontrollers

Atmel Corporate 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 436-4270 FAX 1(408) 436-4314

Atmel Nantes La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

### ASIC/ASSP/Smart Cards

Atmel Rousset Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

Atmel Colorado Springs 1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Atmel Smart Card ICs Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743 RF/Automotive

Atmel Heilbronn

Theresienstrasse 2

Postfach 3535

74025 Heilbronn, Germany

TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

Atmel Colorado Springs 1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom Atmel Grenoble Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

*e-mail* literature@atmel.com

Web Site http://www.atmel.com

## © Atmel Corporation 2001.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical

ATMEL® is the registered trademark of Atmel.

ARM Powered®, ARM® and ARM® Thumb® are the registered trademarks of ARM Ltd. Other terms and product names may be the trademarks of others.