# **MOTOROLA SEMICONDUCTOR** TECHNICAL DATA

# Serial Input PLL Frequency Synthesizer with Analog Phase Detector

### Interfaces with Dual-Modulus Prescalers

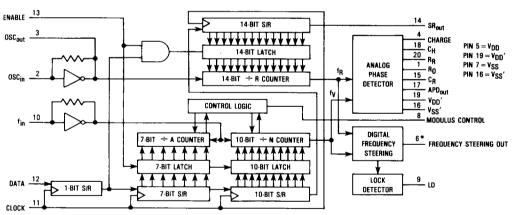

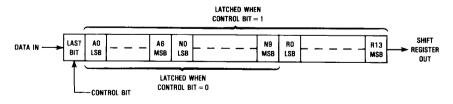

The MC145159-1 has a programmable 14-bit reference counter, as well as programmable divide-by-N/divide-by-A counters. The counters are programmed serially through a common data input and latched into the appropriate counter latch, according to the last data bit (control bit) entered.

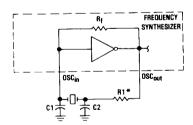

When combined with a loop filter and VCO, this device can provide all the remaining functions for a PLL frequency synthesizer operating up to the device's frequency limit. For higher VCO frequency operations, a down mixer or a dual modulus prescaler can be used between the VCO and the PLL.

General Purpose Applications:

CATV TV Tuning

AM/FM Radios

Scanning Receivers Two Way Radios Amateur Radio

- Low Power Consumption Through Use of CMOS Technology

- 3.0 to 9.0 V Supply Range

- On- or Off-Chip Reference Oscillator Operation

- · Compatible with the Serial Peripheral Interface (SPI) on CMOS MCUs

- ÷ R Range = 3 to 16383

- ÷ N Range = 16 to 1023, ÷ A Range = 0 to 127

- High-Gain Analog Phase Detector

- See Application Note AN969

# MC145159-1

### **BLOCK DIAGRAM**

\*NOTE: Pin 6 is not and cannot be used as a digital phase detector output.

MAXIMUM RATINGS\* (Voltages Referenced to VSS)

| Symbol           | Parameter                                             | Value                        | Unit |  |

|------------------|-------------------------------------------------------|------------------------------|------|--|

| V <sub>DD</sub>  | DC Supply Voltage                                     | - 0.5 to + 10.0              | V    |  |

| Vin, Vout        | Input or Output Voltage (DC or Transient)             | -0.5 to V <sub>DD</sub> +0.5 | V .  |  |

| lin, lout        | Input or Output Current (DC or Transient),<br>per Pin | ± 10                         | mA   |  |

| IDD, ISS         | Supply Current, VDD or VSS Pins                       | ± 30                         | mA   |  |

| PD               | Power Dissipation, per Package                        | 500                          | mW   |  |

| T <sub>stg</sub> | Storage Temperature                                   | -65 to +150                  |      |  |

| Τį               | Lead Temperature (8-Second Soldering)                 | 260                          | °C   |  |

<sup>\*</sup>Maximum Ratings are those values beyond which damage to the device may occur.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation it is recommended that V<sub>in</sub> and V<sub>out</sub> be constrained to the range V<sub>SS</sub> ≤(V<sub>in</sub> or V<sub>out</sub>) ≤ V<sub>DD</sub>.

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either VSS or VDD).

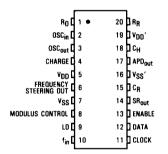

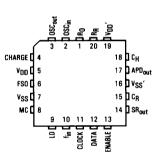

### PIN ASSIGNMENTS

PLASTIC DIP

PLCC

ELECTRICAL CHARACTERISTICS (Voltages Referenced to VSS except ICR and IAPD which are referenced to VSS')

| Characteristic                                                                                                                                                                                                                     |         | Symbol           | VDD         | 4                       | 0°C                       | 25                      | °C                        | 86                      | *C                         | Unit     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|-------------|-------------------------|---------------------------|-------------------------|---------------------------|-------------------------|----------------------------|----------|

|                                                                                                                                                                                                                                    |         | Syllibol         | VDD.        | Min                     | Max                       | Min                     | Max                       | Min                     | Max                        | Uni      |

| Power Supply Voltage Range                                                                                                                                                                                                         |         | V <sub>DD</sub>  | _           | 3                       | 9                         | 3                       | 9                         | 3                       | 9                          | V        |

| Output Voltage  V <sub>in</sub> = 0 V or V <sub>DD</sub> I <sub>out</sub> = 0 $\mu$ A                                                                                                                                              | 0 Level | VOL              | 3<br>5<br>9 | -<br>-                  | 0.05<br>0.05<br>0.05      | -                       | 0.05<br>0.05<br>0.05      |                         | 0.05<br>0.05<br>0.05       | V        |

| (Except OSC <sub>out</sub> and APD <sub>out</sub> )                                                                                                                                                                                | 1 Level | ∨он              | 3<br>5<br>9 | 2.95<br>4.95<br>8.95    | _<br>_<br>_               | 2.95<br>4.95<br>8.95    | _<br>_<br>_               | 2.95<br>4.95<br>8.95    | _<br>_<br>_                | ŀ        |

| Output Voltage<br>OSC <sub>out</sub><br>V <sub>in</sub> =0 V or V <sub>DD</sub>                                                                                                                                                    | 0 Level | VOL              | 3<br>5<br>9 | <br>-<br>-              | 0.9<br>1.5<br>2.7         | -<br>-<br>-             | 0.9<br>1.5<br>2.7         | -<br>-<br>-             | 0.9<br>1.5<br>2.7          | ٧        |

|                                                                                                                                                                                                                                    | 1 Level | ∨он              | 3<br>5<br>9 | 2.1<br>3.5<br>6.3       |                           | 2.1<br>3.5<br>6.3       | <u>-</u><br>-             | 2.1<br>3.5<br>6.3       | <del>-</del><br>-          |          |

| ΔVoltage, V <sub>CH</sub> – V <sub>APDout</sub><br>I <sub>APDout</sub> ≈ 0 μA                                                                                                                                                      | -       | ΔV               | -           |                         | -                         | -                       | 1.05                      | =                       | -                          | V        |

| Input Voltage  V <sub>Out</sub> = 0.5 V or V <sub>DD</sub> - 0.5 V  (All Outputs Except OSC <sub>Out</sub> )                                                                                                                       | 0 Level | VIL              | 3<br>5<br>9 | _<br>_<br>_             | 0.9<br>1.5<br>2.7         | -<br>-                  | 0.9<br>1.5<br>2.7         | <u>-</u><br>-           | 0.9<br>1.5<br>2.7          | ٧        |

|                                                                                                                                                                                                                                    | 1 Level | VIH              | 3<br>5<br>9 | 2.1<br>3.5<br>6.3       | _<br>_<br>_               | 2.1<br>3.5<br>6.3       | -<br>-<br>-               | 2.1<br>3.5<br>6.3       | _<br>_<br>_                |          |

| $ \begin{array}{l} \mbox{Input Voltage*-OSC}_{\mbox{in}} \\ \mbox{V}_{O} = 2.1 \ \mbox{V or } 0.9 \ \mbox{V} \\ \mbox{V}_{O} = 3.5 \ \mbox{V or } 1.5 \ \mbox{V} \\ \mbox{V}_{O} = 6.3 \ \mbox{V or } 2.7 \ \mbox{V} \end{array} $ | 0 Level | VIL              | 3<br>5<br>9 | _<br>_<br>_             | 0<br>0<br>0               |                         | 0<br>0<br>0               | -<br>-<br>-             | 0 0 0                      | ٧        |

| $V_O = 0.9 \text{ V or } 2.1 \text{ V}$<br>$V_O = 1.5 \text{ V or } 3.5 \text{ V}$<br>$V_O = 2.7 \text{ V or } 6.3 \text{ V}$                                                                                                      | 1 Level | VIH              | 3<br>5<br>9 | 3.0<br>5.0<br>9.0       | _<br>_<br>_               | 3.0<br>5.0<br>9.0       | -                         | 3.0<br>5.0<br>9.0       | -<br>-                     |          |

| Output Current—Modulus Control Vout = 2.7 V Vout = 4.6 V Vout = 8.5 V                                                                                                                                                              | Source  | ЮН               | 3<br>5<br>9 | -0.60<br>-0.90<br>-1.50 | _<br>                     | -0.50<br>-0.75<br>-1.25 | 1 1                       | -0.30<br>-0.50<br>-0.80 | - 1                        | mA       |

| $V_{out} = 0.3 \text{ V} V_{out} = 0.4 \text{ V} V_{out} = 0.5 \text{ V}$                                                                                                                                                          | Sink    | lOL              | 3<br>5<br>9 | 1.30<br>1.90<br>3.80    | _<br>_<br>_               | 1.10<br>1.70<br>3.30    |                           | 0.66<br>1.08<br>2.10    | -<br>-<br>-                |          |

| Output Current, C <sub>R</sub><br>V <sub>CR</sub> = 4.5 V, R <sub>R</sub> = 240 k                                                                                                                                                  |         | ICR              | 9           |                         | _                         | - 90                    | - 110                     | _                       | -                          | μΑ       |

| Output Current, APD <sub>Out</sub><br>R <sub>O</sub> = 240 k, V <sub>CH</sub> = 0 V<br>V <sub>APD<sub>Out</sub> = 4.5 V</sub>                                                                                                      |         | IAPD             | 9           | -                       | 1                         | 170                     | 350                       | _                       | _                          | μА       |

| Output Current—Other Outputs<br>V <sub>out</sub> = 2.7 V<br>V <sub>out</sub> = 4.6 V<br>V <sub>out</sub> = 8.5 V                                                                                                                   | Source  | ЮН               | 3<br>5<br>9 | -0.44<br>-0.64<br>-1.30 | -<br>-                    | -0.35<br>-0.51<br>-1.00 | -                         | -0.22<br>-0.36<br>-0.70 | -<br>-<br>-                | mA       |

| V <sub>out</sub> = 0.3 V<br>V <sub>out</sub> = 0.4 V<br>V <sub>out</sub> = 0.5 V                                                                                                                                                   | Sink    | lor              | 3<br>5<br>9 | 0.44<br>0.64<br>1.30    |                           | 0.35<br>0.51<br>1.00    | _<br>_<br>_               | 0.22<br>0.36<br>0.70    | _<br>_<br>_                |          |

| Input Current - Data, Clock, Enable                                                                                                                                                                                                |         | lin              | 9           |                         | ±0.3                      | _                       | ± 0.1                     |                         | ± 1.0                      | μΑ       |

| Input Current-f <sub>in</sub> , OSC <sub>in</sub>                                                                                                                                                                                  |         | lin              | 9           | ± 2                     | ± 50                      | ±2                      | ± 25                      | ±2                      | ± 22                       | μΑ       |

| Input Capacitance                                                                                                                                                                                                                  |         | C <sub>in</sub>  | -           |                         | 10                        |                         | 10                        | _                       | 10                         | pF       |

| 3-State Output Capacitance – Frequency Steer<br>Quiescent Current<br>V <sub>in</sub> = 0 V or V <sub>DD</sub><br>  <sub>out</sub> = 0 μA                                                                                           | ing Out | C <sub>out</sub> | 3<br>5<br>9 |                         | 10<br>800<br>1200<br>1600 | -                       | 10<br>800<br>1200<br>1600 | <u>-</u><br>-<br>-      | 10<br>1600<br>2400<br>3200 | pF<br>μA |

| 3-State Leakage Current<br>V <sub>out</sub> = 0 V or 9 V                                                                                                                                                                           |         | loz              | 9           |                         | ± 0.3                     | _                       | ± 0.1                     | -                       | ±3.0                       | μΑ       |

<sup>\*</sup>DC-coupled square wave.

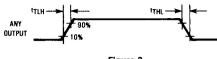

SWITCHING CHARACTERISTICS (TA = 25°C, C1 = 50 pF)

| Characteristic                                            | Symbol                          | V <sub>DD</sub> | Min      | Max       | Unit |

|-----------------------------------------------------------|---------------------------------|-----------------|----------|-----------|------|

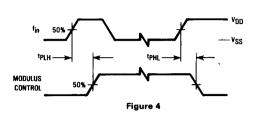

| Output Rise Time, Modulus Control (Figures 3 and 8)       | tтιн                            | 3<br>5          | _        | 115<br>60 | ns   |

|                                                           |                                 | 9               | _        | 40        |      |

| Output Fall Time, Modulus Control (Figures 3 and 8)       | tтнι                            | 3<br>5          | -        | 60<br>34  | ns   |

|                                                           |                                 | 9               | _        | 30        |      |

| Output Rise and Fall Time, LD and SRout (Figures 3 and 8) | ŢLH,                            | 3               | _        | 140       | ns   |

|                                                           | TTHL                            | 5<br>9          | _        | 80<br>60  |      |

| Propagation Delay Time                                    | tPLH,                           | 3               | _        | 125       | ns   |

| fin to Modulus Control (Figures 4 and 8)                  | tPHL                            | 5<br>9          | -        | 80<br>50  |      |

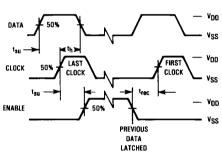

| Setup Times                                               | t <sub>su</sub>                 | 3               | 30       | _         | ns   |

| Data to Clock (Figure 5)                                  |                                 | 5<br>9          | 20<br>18 | _         |      |

| Clock to Enable (Figure 5)                                |                                 | 3               | 70       | -         |      |

| •••••                                                     |                                 | 5 9             | 32<br>25 | _         |      |

| Hold Time                                                 | th                              | 3               | 12       | _         | ns   |

| Clock to Data (Figure 5)                                  |                                 | 5<br>9          | 12<br>15 | _         |      |

| Recovery Time                                             | t <sub>rec</sub>                | 3               | 5        |           | ns   |

| Enable to Clock (Figure 5)                                |                                 | 5<br>9          | 10<br>20 | -         |      |

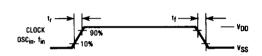

| Input Rise and Fall Times                                 | t <sub>r</sub> , t <sub>f</sub> | 3               | -        | 5         | μS   |

| Clock, OSC <sub>in</sub> , f <sub>in</sub> (Figure 6)     |                                 | 5<br>9          | _        | 2<br>0.5  |      |

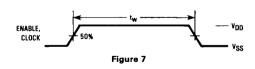

| Input Pulse Width, Enable, Clock (Figure 7)               | tw                              | 3               | 40       | -         | ns   |

|                                                           |                                 | 5<br>9          | 35<br>25 | ] _       |      |

#### PIN DESCRIPTIONS

#### INPUTS

### OSC<sub>in</sub>-Oscillator Input (Pin 2) OSC<sub>out</sub>-Oscillator Output (Pin 3)

These pins form an on-chip reference oscillator when connected to terminals of an external parallel resonant crystal. Frequency setting capacitors of appropriate value must be connected from OSC<sub>in</sub> to VSS and OSC<sub>out</sub> to VSS. OSC<sub>in</sub> may also serve as input for an externally generated reference signal. This signal will typically be ac coupled to OSC<sub>in</sub>, but for larger amplitude signals (standard CMOS logic levels), dc coupling may also be used. In the external reference mode, no connection is required to OSC<sub>out</sub>.

### fin-Frequency In (Pin 10)

Input to the positive edge triggered divide-by-N and divide-by-A counters.  $f_{in}$  is typically derived from a dual modulus prescaler and is ac coupled into pin 10. This input has an inverter biased in the linear region to allow use with ac-coupled signals as low as 500 mV peak-to-peak or direct-coupled signals swinging from Vpp to Vss.

### DATA - Serial Data Input (Pin 12)

Counter and control information is shifted into this input. The last data bit entered goes into the one-bit control shift register. A logic one allows the reference counter information to be loaded into it's 14-bit latch when Enable goes high. A logic zero entered as the control bit disables the reference counter latch. The divide-by-A/divide-by-N counter latch is loaded, regardless of the contents of the control register, when Enable goes high. The data entry format is shown below.

### ENABLE-Transparent Latch Enable (Pin 13)

A logic high on this input allows data to be entered into the divide-by-A/divide-by-N latch and, if the control bit is high, into the reference counter latch. Counter programming is unaffected when Enable is low.

### CLOCK-Shift Register Clock (Pin 11)

A low-to-high transition on this input shifts data from the serial data input into the shift registers.

### COMPONENT PINS

## CR-Ramp Capacitor (Pin 15)

The capacitor connected from this pin to  $V_{SS}'$  is charged linearly, at a rate determined by  $R_{I\!\!P}$ . The voltage on this

capacitor is proportional to the phase difference of the frequencies present at the internal phase detector inputs. A polystyrene or mylar capacitor is recommended.

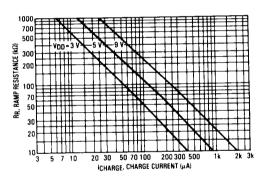

### RR-Ramp Current Bias Resistor (Pin 20)

A resistor connected from this pin to VSS' determines the rate at which the ramp capacitor is charged, thereby affecting the phase detector gain (see Figure 1).

### CH-Hold Capacitor (Pin 18)

The charge stored on the ramp capacitor is transferred to the capacitor connected from this pin to either  $V_{DD}'$  or  $V_{SS}'$ . The ratio of  $C_R$  to  $C_H$  should be large enough to have no affect on the phase detector gain ( $C_R > 10$   $C_H$ ). A low-leakage capacitor should be used.

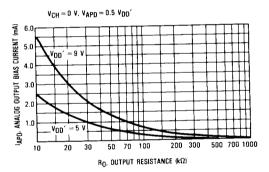

### Ro-Output Bias Current Resistor (Pin 1)

A resistor connected from this pin to VSS' biases the output N-channel transistor, thereby setting a current sink on the analog phase detector output (pin 17). This resistor adjusts the APDout bias current (see Figure 2).

### OUTPUTS

### APDout-Analog Phase Detector Output (Pin 17)

This output produces a voltage that controls an external VCO. The voltage range of this output ( $V_{DD} = +9$  V) is from below +0.5 V to +8 V or more. The source impedance of this output is the equivalent of a source follower with an externally variable source resistor. The source resistor depends upon the output bias current controlled by the output bias current resistor,  $R_{D}$ . The bias current is adjustable from 0.01 mA to 0.5 mA. The output voltage is not more than 1.05 V below the sampled point on the ramp. With a constant sample of the ramp voltage at 9 V and the hold capacitor of 50 pF, the instantaneous output ripple is about 5 mV peak-to-peak.

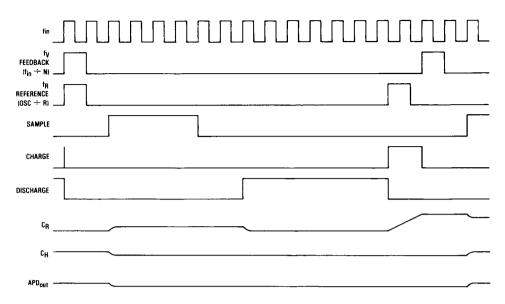

### Charge - Ramp Charge Indicator (Pin 4)

This output is high from the time  $f_R$  goes high to the time  $f_V$  goes high ( $f_R$  and  $f_V$  are the frequencies at the phase detector inputs). This high voltage indicates that the ramp capacitor,  $C_R$ , is being charged.

# Frequency Steering Out—Three-State Frequency Steering Output (Pin 6)

If the counted down input frequency on  $f_{in}$  is higher than the counted down reference frequency of  $OSC_{in}$ , this output

### **DATA ENTRY FORMAT**

MOTOROLA CMOS APPLICATION-SPECIFIC DIGITAL-ANALOG INTEGRATED CIRCUITS

goes low. If the counted down VCO frequency is lower than that of the counted down OSC<sub>in</sub>, this output goes high.

The repetition rate of the frequency steering output pulses is approximately equal to the difference of the frequencies of the two counted down inputs from the VCO and OSCin. See Application Note AN969 for further information.

## LD-Phase Lock Indicator (Pin 9)

This output is high during lock and goes low to indicate a non-lock condition. The frequency and duration of the non-lock pulses will be the same as either polarity of the frequency steering output.

# Modulus Control — Dual Modulus Prescaler Control (Pin 8)

The modulus control level is low at the beginning of a count cycle and remains low until the divide-by-A counter has counted down from its programmed value. At that time, the modulus control goes high and remains high until the divide-by-N counter has counted the rest of the way down from its programmed value (N – A additional counts, since both divide-by-N and divide-by-A are counting down during the first portion of the cycle). Modulus control is then set back low, the counters preset to their respective programmed values, and the above sequence is repeated. This provides a total programmable divide value of N<sub>T</sub> = N•P+A, where P and P+1

represent the dual modulus prescaler divide values, respectively, for high and low modulus control levels; N is the number programmed into the divide-by-N counter, and A is the number programmed into the divide-by-A counter.

# SRout-Shift Register Output (Pin 14)

This pin is the non-inverted output of the last stage of the 32-bit serial data shift register. It is not latched by the Enable line. If unused, SR<sub>out</sub> should be floated.

### **POWER PINS**

### VDD-Positive Power Supply (Pin 5)

Positive power supply input for all sections of the device except the analog phase detector. V<sub>DD</sub> and V<sub>DD</sub>' should be powered up at the same time to avoid damage to the MC145159-1.

# VSS-Negative Power Supply (Pin 7)

Circuit ground for all sections of the MC145159-1 except the analog phase detector.

## V<sub>SS</sub>' – Analog Phase Detector Circuit Ground (Pin 16) V<sub>DD</sub>' – Analog Power Supply (Pin 19)

Separate power supply and ground inputs are provided to help reduce the effects in the analog section of noise coming from the digital sections of this device and the surrounding circuitry.

Figure 1. Charge Current vs Ramp Resistance

Figure 2. APDout Bias Current versus Output Resistance

### **DESIGN EQUATION**

$$K_{\phi} = \frac{I_{CHARGE}}{2\pi f_{R}C_{R}}$$

where

$K_{\phi}$  = phase detector gain, ICHARGE is from Figure 1

fR = reference frequency

CR = ramp capacitor (in farads)

MOTOROLA CMOS APPLICATION-SPECIFIC DIGITAL-ANALOG INTEGRATED CIRCUITS

# 5

### **SWITCHING WAVEFORMS**

Figure 3

Figure 5

Figure 6

Figure 8. Test Circuit

MOTOROLA CMOS APPLICATION-SPECIFIC DIGITAL-ANALOG INTEGRATED CIRCUITS

5-81

### **DESIGN CONSIDERATIONS**

### CRYSTAL OSCILLATOR CONSIDERATIONS

The following options may be considered to provide a reference frequency to Motorola's CMOS frequency synthesizers.

### USE OF A HYBRID CRYSTAL OSCILLATOR

Commercially available temperature-compensated crystal oscillators (TCXOs) or crystal-controlled data clock oscillators provide very stable reference frequencies. An oscillator capable of sinking and sourcing 50  $\mu A$  at CMOS logic levels may be direct or dc coupled to OSCin. In general, the highest frequency capability is obtained utilizing a direct-coupled square wave having a rail-to-rail (VDD to VSS) voltage swing. If the oscillator does not have CMOS logic levels on the outputs, capacitive or ac coupling to OSCin may be used. OSCout, an unbuffered output, should be left floating.

For additional information about TCXOs and data clock oscillators, please consult the latest version of the *eem Electronic* Engineers Master Catalog, the Gold Book, or similar publications.

### **DESIGN AN OFF-CHIP REFERENCE**

The user may design an off-chip crystal oscillator using ICs specifically developed for crystal oscillator applications, such as the MC12061 MECL device. The reference signal from the MECL device is ac coupled to OSCin. For large amplitude signals (standard CMOS logic levels), dc coupling is used. OSCout, an unbuffered output, should be left floating. In general, the highest frequency capability is obtained with a direct-coupled square wave having rail-to-rail voltage swing.

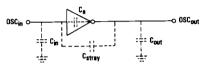

## USE OF THE ON-CHIP OSCILLATOR CIRCUITRY

The on-chip amplifier (a digital inverter) along with an appropriate crystal may be used to provide a reference source frequency. A fundamental mode crystal, parallel resonant at the desired operating frequency, should be connected as shown in Figure 9.

For VDD = 5 V, the crystal should be specified for a loading capacitance, CL, which does not exceed 32 pF for frequencies to approximately 8 MHz, 20 pF for frequencies in the area of

\*May be needed in certain cases. See text.

Figure 9. Pierce Crystal Oscillator Circuit

8 to 15 MHz, and 10 pF for higher frequencies. These are guidelines that provide a reasonable compromise between IC capacitance, drive capability, swamping variations in stray and IC input/output capacitance, and realistic  $C_L$  values. Assuming  $R1=0\,\Omega,$  the shunt load capacitance,  $C_L$ , presented across the crystal can be estimated to be:

$$C_L = \frac{C_{in}C_{out}}{C_{in} + C_{out}} + C_a + C_{stray} + \frac{C1 \cdot C2}{C1 + C2}$$

where

C<sub>in</sub>=5 pF (see Figure 10) C<sub>out</sub>=6 pF (see Figure 10)

C<sub>a</sub> = 1 pF (see Figure 10)

C1 and C2 = external capacitors (see Figure 9)

C<sub>stray</sub> = the total equivalent external circuit stray capacitance appearing across the crystal terminals

Figure 10. Parasitic Capacitances of the Amplifier and Catray

NOTE: Values are supplied by crystal manufacturer (parallel resonant crystal).

Figure 11. Equivalent Crystal Networks

The oscillator can be "trimmed" on-frequency by making a portion or all of C1 variable. The crystal and associated components must be located as close as possible to the OSCin and OSCout pins to minimize distortion, stray capacitance, stray inductance, and startup stabilization time. Circuit stray capacitance can also be handled by adding the appropriate stray value to the values for Cin and Cout. For this approach, the term Cstray becomes zero in the above expression for CL.

Power is dissipated in the effective series resistance of the crystal, R<sub>e</sub>, in Figure 11. The maximum drive level specified by the crystal manufacturer represents the maximum stress that the crystal can withstand without damage or excessive shift in operating frequency. R1 in Figure 9 limits the drive level. The use of R1 is not necessary in most cases.

5

To verify that the maximum dc supply voltage does not overdrive the crystal, monitor the output frequency as a function of voltage at OSC<sub>OUT</sub>. (Care should be taken to minimize loading.) The frequency should increase very slightly as the dc supply voltage is increased. An overdriven crystal will decrease in frequency or become unstable with an increase in supply voltage. The operating supply voltage must be reduced or R1 must be increased in value if the overdriven condition exists. The user should note that the oscillator start-up time is proportional to the value of R1.

Through the process of supplying crystals for use with CMOS inverters, many crystal manufacturers have developed expertise in CMOS oscillator design with crystals. Discussions with such manufacturers can prove very helpful. See Table 1.

### RECOMMENDED READING

Technical Note TN-24, Statek Corp. Technical Note TN-7, Statek Corp.

E. Hafner, "The Piezoelectric Crystal Unit – Definitions and Method of Measurement", *Proc. IEEE*, Vol. 57, No. 2, Feb.,

D. Kemper, L. Rosine, "Quartz Crystals for Frequency Control", *Electro-Technology*, June, 1969.

P. J. Ottowitz, "A Guide to Crystal Selection", *Electronic Design*, May, 1966.

D. Babin, "Designing Crystal Oscillators", Machine Design, March 7, 1985.

D. Babin, "Guidelines for Crystal Oscillator Design", Machine Design, April 25, 1985.

Table 1. Partial List of Crystal Manufacturers

| Name                        | Address                               | Phone          |  |  |  |  |  |

|-----------------------------|---------------------------------------|----------------|--|--|--|--|--|

| United States Crystal Corp. | 3605 McCart Ave., Ft. Worth, TX 76110 | (817) 921-3013 |  |  |  |  |  |

| Crystek Crystal             | 2371 Crystal Dr., Ft. Myers, FL 33907 | (813) 936-2109 |  |  |  |  |  |

| Statek Corp.                | 512 N. Main St., Orange, CA 92668     | (714) 639-7810 |  |  |  |  |  |

NOTE: Motorola cannot recommend one supplier over another and in no way suggests that this is a complete listing of crystal manufacturers.

Figure 12. Timing Diagram for Minimum Divide Value (N = 16)