### IC66LV10016AL

#### **Document Title**

16M-BIT (1M-WORD BY 16-BIT) Low Power Pseudo SRAM

### **Revision History**

Revision NoHistoryDraft DateRemark0AInitial DraftFebruary 05,2004Preliminary

The attached datasheets are provided by ICSI. Integrated Circuit Solution Inc reserve the right to change the specifications and products. ICSI will answer to your questions about device. If you have any questions, please contact the ICSI offices.

# 16M-BIT (1M-WORD BY 16-BIT) Low-Power Pseudo SRAM

#### **FEATURES**

Organization: 1M x 16

Power Supply Voltage: 2.7~3.3V

Three state output and TTL Compatible

Package Type: 48-FBGA-6.00x8.00 mm²

· Address Acess Time: 70ns

#### **DESCRIPTION**

The IC66LV10016AL is a family of low voltage, low power 16Mbit static RAM organized as 1M-words by 16-bit, designed with Pseudo SRAM technology, fabricated with CMOS process technology.

The IC66LV10016AL is designed specifically for low-power applications such as mobile cellular phones, personal digital assistants and other battery-operated products.

The operation modes are determined by a combination of the device control inputs  $\overline{CE}$ ,  $\overline{ZZ}$ ,  $\overline{LB}$ ,  $\overline{UB}$ ,  $\overline{WE}$  and  $\overline{OE}$ . Each mode is summarized in the function table.

A write operation is executed whenever the low level  $\overline{\text{WE}}$  overlaps with the low level  $\overline{\text{LB}}$  and/or  $\overline{\text{UB}}$  and the low level  $\overline{\text{CE}}$  and the high level  $\overline{\text{ZZ}}$ . The address (A0~A19) must be set up before the write cycle and must be stable during entire cycle.

A read operation is executed by setting  $\overline{WE}$  at a high level and  $\overline{OE}$  at a low level while  $\overline{LB}$  and/or  $\overline{UB}$  and  $\overline{CE}$  are in an active state,  $\overline{ZZ}$  is in a inactive state.

When setting  $\overline{LB}$  at the high level and other controls are in an active stage, upper-byte is selected for read and write operations, and lower-byte is not selected. When setting  $\overline{UB}$  at a high level and other pins are in an active stage, lower-byte is selected and upper-byte is not.

When setting  $\overline{LB}$  and  $\overline{UB}$  at a high level or  $\overline{CE}$  and  $\overline{ZZ}$  at a high level or  $\overline{ZZ}$  at a low level, the chip is in a non-select mode. In this mode, the output stage is in a high-impedance state, allowing OR-tie with other chips.

When  $\overline{\text{OE}}$  is at a high level, the output stage is in a high-impedance state.

#### PART NAME TABLE & KEY SPEC SUMMARY

| Deep powe             |             |                  |       |           |            |            |          |

|-----------------------|-------------|------------------|-------|-----------|------------|------------|----------|

| <b>Product Family</b> | Operating O | perating Voltage | Speed | down      | Standby    | Operating  | PKG Type |

|                       | Temperature | (VCC/VCCQ)       |       | (Izz,Max) | (IsB2,Max) | (Icc2,Max) |          |

| IC66LV10016AL-70      | OB Extended | 2.7-3.3V         | 70ns  | 25μΑ      | 70µA       | 20mA       | 48-TFBGA |

|                       | (-25-85°C)  |                  |       |           |            |            |          |

ICSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which may appear in this publication. © Copyright 2000, Integrated Circuit Solution Inc.

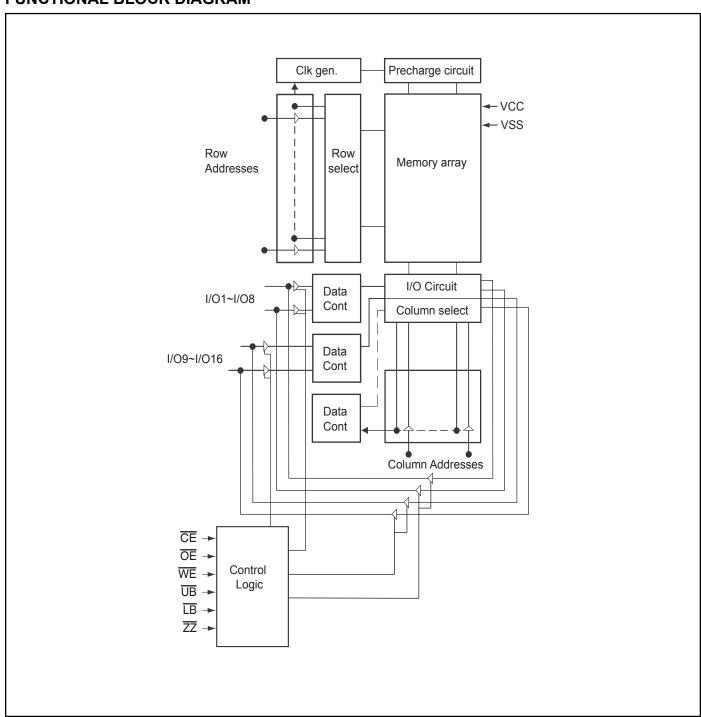

### **FUNCTIONAL BLOCK DIAGRAM**

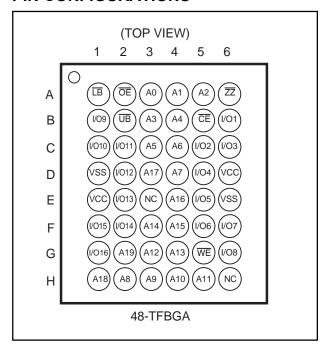

#### **PIN CONFIGURATIONS**

| Pin          | Function               |

|--------------|------------------------|

| A0~A19       | Address input          |

| I/O1 ~ I/O16 | Data input / output    |

| ZZ           | Low power modes        |

| CE           | Chip select input      |

| WE           | Write enable input     |

| ŌĒ           | Output enable input    |

| ŪB           | Upper Byte (I/O9 ~ 16) |

| LB           | Lower Byte (I/O1 ~ 8)  |

| VCC          | Power supply           |

| VSS          | Ground supply          |

| NC           | No connection          |

#### **FUNCTION TABLE**

| CE                   | 团 | ŌĒ               | WE               | LB               | ŪB               | I/O1-8 | I/O9-16 | Mode             | Power                |

|----------------------|---|------------------|------------------|------------------|------------------|--------|---------|------------------|----------------------|

| Н                    | Н | X <sup>(1)</sup> | X <sup>(1)</sup> | X <sup>(1)</sup> | X <sup>(1)</sup> | High-Z | High-Z  | Deselected       | Standby              |

| <br>X <sup>(1)</sup> | L | X <sup>(1)</sup> | X <sup>(1)</sup> | X <sup>(1)</sup> | X <sup>(1)</sup> | High-Z | High-Z  | Deselected       | Deep Power Down Mode |

| L                    | Н | Н                | Н                | X <sup>(1)</sup> | X <sup>(1)</sup> | High-Z | High-Z  | Output disabled  | Active               |

| L                    | Н | X <sup>(1)</sup> | Н                | Н                | Н                | High-Z | High-Z  | Output disabled  | Active               |

| L                    | Н | L                | Н                | L                | Н                | Dout   | High-Z  | Lower byte read  | Active               |

| L                    | Н | L                | Н                | Н                | L                | High-Z | Dout    | Upper byte read  | Active               |

| L                    | Н | L                | Н                | L                | L                | Dout   | Dout    | Word read        | Active               |

| L                    | Н | Н                | L                | L                | Н                | Din    | High-Z  | Lower byte write | Active               |

| L                    | Н | Н                | L                | Н                | L                | High-Z | Din     | Upper byte write | Active               |

| L                    | Н | Н                | L                | L                | L                | Din    | Din     | Word write       | Active               |

#### Notes:

1. X means don't-care.(Must be low or hight state)

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol   | Parameter                             | Ratings         | Unit |  |

|----------|---------------------------------------|-----------------|------|--|

| Vin,Vout | Voltage on any pin relative to Vss    | -0.2 to Vcc+0.3 | V    |  |

| Vcc      | Voltage on Vcc supply relative to Vss | -0.2 to 3.6     | V    |  |

| PD       | Power Dissipation                     | 1.0             | W    |  |

| Тѕтс     | Storage Temperature                   | -65 to 150      | °C   |  |

| Toper    | Operating Temperature                 | -25 to 85       | °C   |  |

Note:

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation should be restricted to recommended operating condition. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### DC ELECTRICAL CHARACTERISTICS (1)

| Symbol | Parameter              | Conditions      | Min                 | Max        | Units |

|--------|------------------------|-----------------|---------------------|------------|-------|

| Vcc    | Supply Voltage         |                 | 2.7                 | 3.3        | V     |

| Vih    | Input High Voltage     |                 | Vcc-0.3             | Vcc+0.3(2) | V     |

| VIL    | Input Low Voltage      |                 | -0.3 <sup>(3)</sup> | 0.3        | V     |

| lu     | Input Leakage current  | VIN=Vss to Vcc  | -1                  | 1          | μA    |

| llo    | Output Leakage current | Vour=Vss to Vcc | -1                  | 1          | μA    |

|        |                        | Output Disable  |                     |            |       |

| Vol    | Output low Voltage     | IoL=0.5mA       |                     | 0.3        | V     |

| Vон    | Output high Voltage    | Iон=-0.5mA      | Vcc-0.3             |            | V     |

Notes:

#### POWER CONSUMPTION CHARACTERISTICS

| Symbol            | Parameter             | Conditions                                         | Min | Max | Units |

|-------------------|-----------------------|----------------------------------------------------|-----|-----|-------|

| Icc1              | Vcc operating         | Cycle time=1µs,100% duty                           | _   | 3   | mA    |

|                   | supply current        | louт=0mA, <del>CE</del> ≤0.2V, <del>ZZ</del> =Vін, |     |     |       |

|                   |                       | Vin≤0.2V or Vin≥Vcc-0.2V                           |     |     |       |

| Icc2              | Vcc Dynamic operation | Cycle time=tRCmin,100% duty                        | _   | 20  | mA    |

|                   | supply current        | Iouт=0mA, <del>CE</del> =VıL, <del>ZZ=</del> Vıн,  |     |     |       |

|                   |                       | VIN=VIL or VIH                                     |     |     |       |

| Is <sub>B</sub> 1 | TTL Standby Current   | CE=Vih,ZZ=Vih,                                     | _   | 0.3 | mA    |

|                   | (TTL inputs)          | Other inputs=Vı∟ or Vıн                            |     |     |       |

| IsB2              | CMOS Standby Current  | CE≥Vcc-0.2V,ZZ≥Vcc-0.2V,                           | _   | 70  | μA    |

|                   | ( CMOS inputs )       | Vin≤0.2V or Vin≥Vcc-0.2V                           |     |     |       |

| Izz               | Deep power down mode  | <u>ZZ</u> ≤0.2V,                                   | _   | 25  | μA    |

|                   |                       | Vin≤0.2V or Vin≥Vcc-0.2V                           |     |     | •     |

#### **CAPACITANCE**

| Symbol | Parameter          | <b>Test Condition</b> | Min | Max | Notes |

|--------|--------------------|-----------------------|-----|-----|-------|

| Cin    | Input Capacitance  | V <sub>IN</sub> =0V   | -   | 8   | pF    |

| Сю     | Output Capacitance | V <sub>IO</sub> =0V   | -   | 10  | pF    |

Toper=-25 to 85°C, otherwise specified.

Overshoot : Vcc+1.0V in case of pulse width ≤ 20ns

<sup>3.</sup> Undershoot : -1.0V in case of pulse width ≤ 20ns

<sup>4.</sup> Overshoot and undershoot are sampled, not 100% tested.

### **AC OPERATING CONDITIONS**

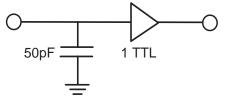

### **TEST CONDITIONS**(Test Load and Input/Output Reference)

| Parameter                          | Value           |

|------------------------------------|-----------------|

| Input pulse level                  | 0.3 to Vcc-0.3V |

| Input rise and fall time           | 5ns             |

| Input and output reference voltage | 0.5Vcc          |

| Output loads                       | CL=50pF+1TTL    |

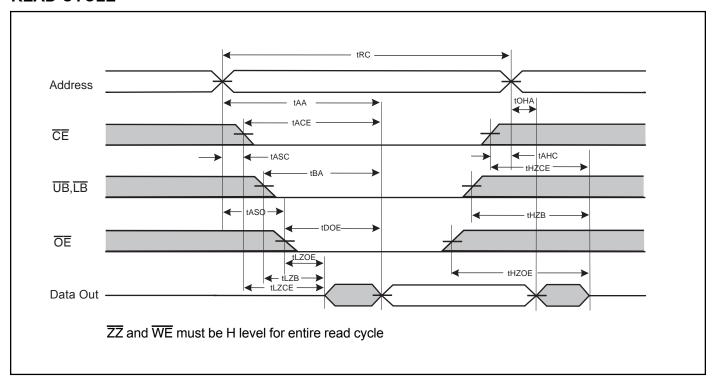

# ACCHARATERISTICS READCYCLE

| Symbol | Parameter                      | -7           | 70  |       |

|--------|--------------------------------|--------------|-----|-------|

| •      |                                | Min          | Max | Units |

| tRC    | Read Cycle Time                | 70           | 32K | ns    |

| tAA    | Address Access time            | _            | 70  | ns    |

| tOHA   | Output Hold Time               | 5            | _   | ns    |

| tACE   | CE Access Time                 | <del>_</del> | 70  | ns    |

| tDOE   | OE Access Time                 | _            | 40  | ns    |

| tBA    | UB, LB Access Time             | <del></del>  | 25  | ns    |

| tASO   | Address set up to OE Low       | -5           | _   | ns    |

| tASC   | Address set up to CE Low       | 0            | _   | ns    |

| tAHC   | Address hold time from OE High | 0            | _   | ns    |

| tLZCE  | CE to Low-Z Output             | 0            | _   | ns    |

| tLZB   | UB, LB to Low-Z Output         | 0            | _   | ns    |

| tLZOE  | OE to Low-Z Output             | 0            | _   | ns    |

| tHZCE  | CE to High- Z Output           | _            | 15  | ns    |

| tHZB   | UB, LB to High- Z Output       | _            | 15  | ns    |

| tHZOE  | OE to High-Z Output            | _            | 15  | ns    |

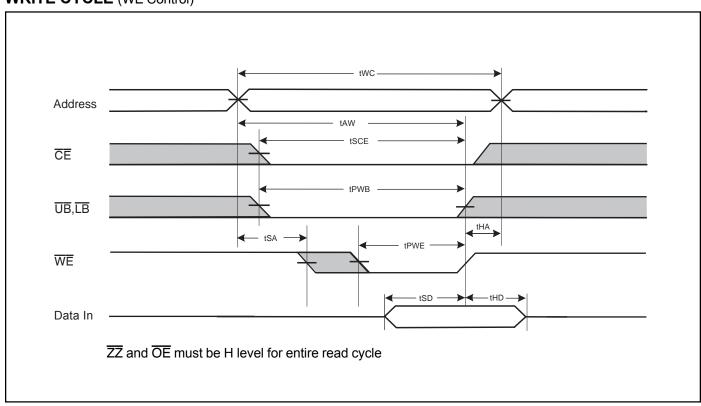

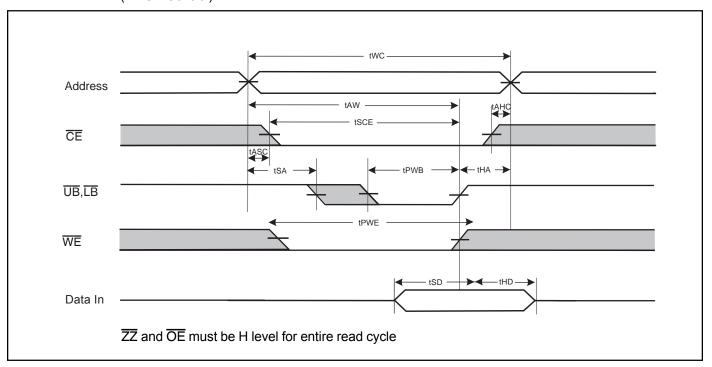

#### **WRITE CYCLE**

| Symbol | Parameter                       | -7  | -70 |       |  |  |

|--------|---------------------------------|-----|-----|-------|--|--|

| •      |                                 | Min | Max | Units |  |  |

| tWC    | Write Cycle Time                | 70  | 32K | ns    |  |  |

| tSCE   | CE to Write End                 | 60  | _   | ns    |  |  |

| tSA    | Address Setup Time              | 0   | _   | ns    |  |  |

| tAW    | Address Setup Time to Write End | 60  | _   | ns    |  |  |

| tASC   | Address set up to CE Low        | 0   | _   | ns    |  |  |

| tAHC   | Address hold time from OE High  | 0   | _   | ns    |  |  |

| tPWE   | WE Pulse Width                  | 40  | _   | ns    |  |  |

| tPWB   | LB, UB to End of Write          | 60  | _   | ns    |  |  |

| tHA    | Address Hold from Write End     | 0   | _   | ns    |  |  |

| tSD    | Data Setup to Write End         | 30  | _   | ns    |  |  |

| tHD    | Data Hold from Write End        | 0   | _   | ns    |  |  |

|        |                                 |     |     |       |  |  |

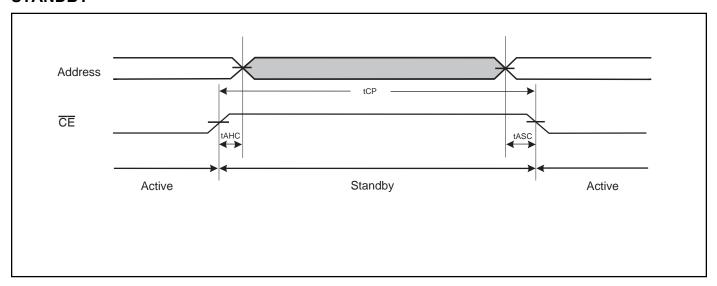

| tCP    | CE High Pulse width             | 30  |     | ns    |  |  |

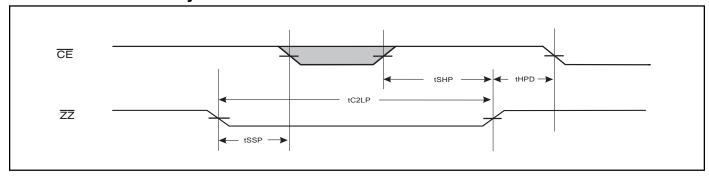

### Power Down Cycle( Ta = -25~85 °C)

| Symbol | Parameter                                | Min | Max | Units |

|--------|------------------------------------------|-----|-----|-------|

| tSSP   | CE High set up time for Power Down entry | 0   | _   | ns    |

| tSHP   | CE High hold time before Power Down exit | 0   | _   | ns    |

| TC2LP  | ZZ Low pulse width                       | 30  | _   | ns    |

| tHPD   | CE High hold time after Power Down exit  | 300 | _   | μs    |

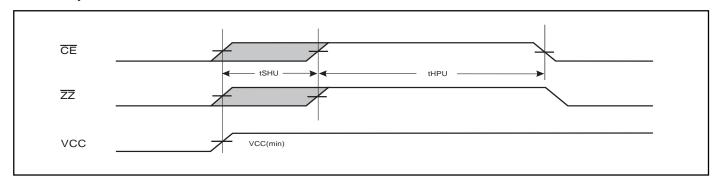

#### **Power Up Timing Requirement**( Ta = -25~85 °C)

| Symbol | Parameter                        | Min | Max | Units |  |

|--------|----------------------------------|-----|-----|-------|--|

| tSHU   | CE ZZ set up time after Power Up | 0   | _   | ns    |  |

| tHPU   | Standby hold time after Power Up | 300 | _   | μs    |  |

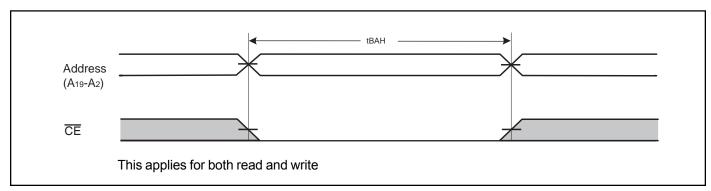

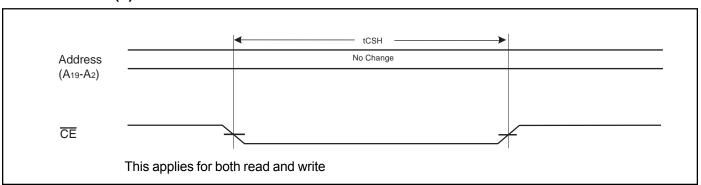

### **Data Retention Timing Requirement**( Ta = -25~85 °C)

| Symbol | Parameter                         | Min | Max | Units |

|--------|-----------------------------------|-----|-----|-------|

| tBAH   | A2 to A19 hold time during active | 0   | _   | ns    |

| tCSH   | CE hold time for A2 to A19 fix    | 300 | _   | μs    |

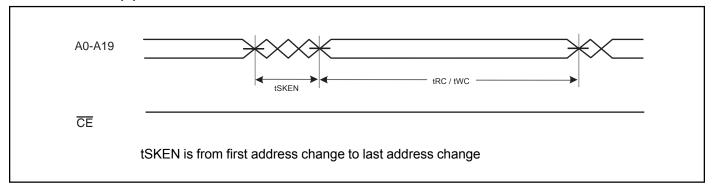

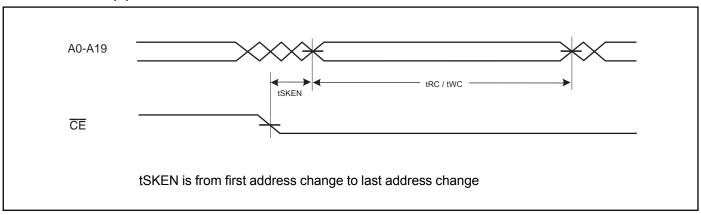

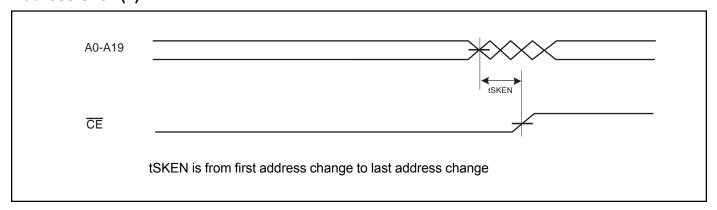

### Address Skew Timing Requirement( Ta = -25~85 °C)

| Symbol | Parameter            | Min | Max | Units |  |

|--------|----------------------|-----|-----|-------|--|

| tSKEW  | Maximum address skew | _   | 10  | ns    |  |

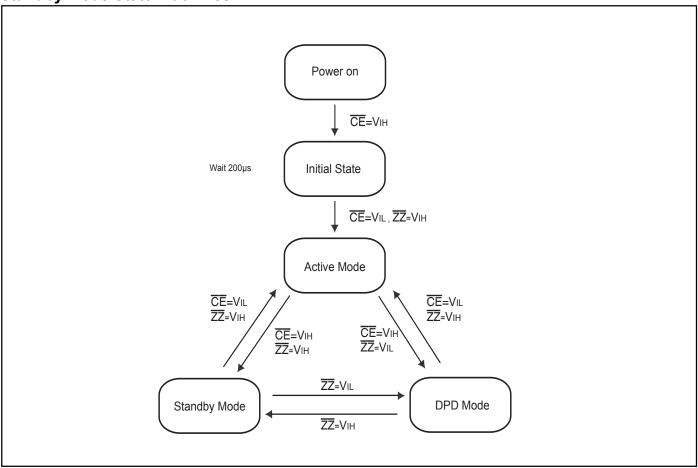

**Standby Mode State machines**

### **Standby Mode Characteristics**

| Mode     | Memory Cell Data | Standby Current(µA) | Wait Time(μS) |  |

|----------|------------------|---------------------|---------------|--|

| Standby  | Valid            | 70                  | 0             |  |

| DPD Mode | Invalid          | 25(Izz)             | 300           |  |

### **READ CYCLE**

### WRITE CYCLE (WE Control)

### WRITE CYCLE (LB UB Control)

### **STANDBY**

## **Power Down Mode Entry / Exit**

## **Power Up**

## Data Retention(1)

### Data Retention(2)

## Address Skew(1)

## Address Skew(2)

## Address Skew(2)

#### **ORDERING INFORMATION**

Temperature Range: -25°C to +85°C

| Order Part No.    | Speed (ns) | Package     |

|-------------------|------------|-------------|

| IC66LV10016AL-70B | 70         | 6*8mm TFBGA |

# Integrated Circuit Solution Inc.

**HEADQUARTER:**

NO.2, TECHNOLOGY RD. V, SCIENCE-BASED INDUSTRIAL PARK,

HSIN-CHU, TAIWAN, R.O.C.

TEL: 886-3-5780333 Fax: 886-3-5783000

**BRANCH OFFICE:**

7F, NO. 106, SEC. 1, HSIN-TAI 5<sup>TH</sup> ROAD,

HSICHIH TAIPEI COUNTY, TAIWAN, R.O.C.

TEL: 886-2-26962140 FAX: 886-2-26962252

http://www.icsi.com.tw