# ICs for Communications

ISDN High Voltage Power Controller IHPC

PEB 2026 Version 1.1

Data Sheet 09.99

DS<sub>2</sub>

| PEB 2026                                      | PEB 2026 |                                                                                                                                                   |  |  |  |  |  |

|-----------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Revision His                                  | story:   | Current Version: 09.99                                                                                                                            |  |  |  |  |  |

| Previous Ver                                  | sion:    | preliminary Data Sheet 02.96                                                                                                                      |  |  |  |  |  |

| Page Page S (in previous (in current Version) |          | Subjects (major changes since last revision)                                                                                                      |  |  |  |  |  |

| 3-2                                           |          | Information added about thermal protection and life time                                                                                          |  |  |  |  |  |

|                                               | 3-3      | Information added about parasitic diodes                                                                                                          |  |  |  |  |  |

|                                               | 3-3      | Extra paragraphfor subject "I <sub>BAT</sub> current peak"                                                                                        |  |  |  |  |  |

| 16                                            | 7-1      | Some values for absolute maximum ratings are extended/adapted.                                                                                    |  |  |  |  |  |

| 17                                            | 7-4      | The static thermal resistances are updated. The last two paragraphs on this page, explaning the reason for the different packages are additional. |  |  |  |  |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

ABM®, AOP®, ARCOFI®-BA, ARCOFI®-SP, DigiTape®, EPIC®-1, EPIC®-S, ELIC®, FALC®54, FALC®56, FALC®-E1, FALC®-LH, IDEC®, IOM®, IOM®-1, IOM®-2, IPAT®-2, ISAC®-P, ISAC®-S, ISAC®-S TE, ISAC®-P TE, ITAC®, IWE®, MUSAC®-A, OCTAT®-P, QUAT®-S, SICAT®, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4 $\mu$ C, SLICOFI® are registered trademarks of Infineon Technologies AG.

ACE™, ASM™, ASP™, POTSWIRE™, QuadFALC™, SCOUT™ are trademarks of Infineon Technologies AG.

#### Edition 09.99

Published by Infineon Technologies AG, TR, Balanstraße 73, 81541 München

© Infineon Technologies AG 1999.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Infineon Technologies AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Infineon Technologies AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| Table o         | of Contents                                                                     | Page |

|-----------------|---------------------------------------------------------------------------------|------|

| 1<br>1.1        | Overview                                                                        |      |

| 2<br>2.1<br>2.2 | Pin Description         Pin Configuration         Pin Definitions and Functions | 2-1  |

| 3               | Functional Description                                                          | 3-1  |

| 4               | Operating Modes                                                                 | 4-1  |

| 5               | Designing the External Components                                               | 5-1  |

| 6               | Application Note                                                                | 6-1  |

| 7               | Electrical Characteristics                                                      | 7-1  |

| 8               | Package Outlines                                                                | 8-1  |

| List of Figu | ıres                                                                          | Page |

|--------------|-------------------------------------------------------------------------------|------|

| Figure 2-1   | Pin Configuration P-DSO-20-6 (top view)                                       | 2-1  |

| Figure 2-2   | Pin Configuration P-DSO-20-10 (top view)                                      |      |

| Figure 3-1   | Block Diagram                                                                 |      |

| Figure 5-1   | Current limit I, imit.ON as a function of RREF (typical values)               |      |

| Figure 5-2   | Power Supply Current I <sub>BAT</sub> as a function of RREF (typical values). | 5-2  |

| Figure 5-3   | Power Supply Current IDD as a function of RREF (typical values) .             | 5-2  |

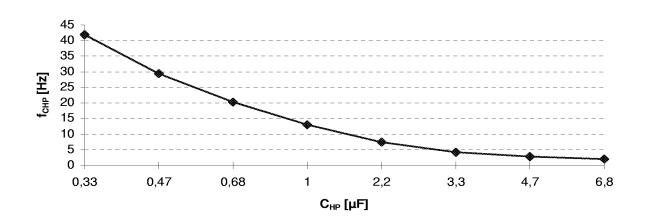

| Figure 5-4   | Corner frequency of high-pass filter as a function of C <sub>HP</sub>         |      |

|              | (typical values)                                                              | 5-3  |

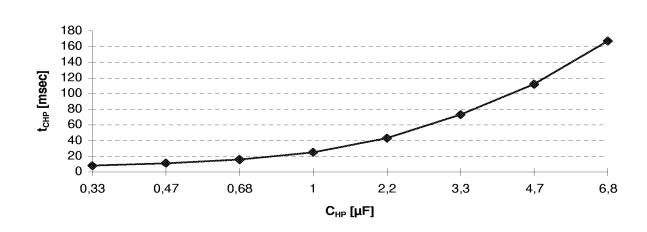

| Figure 5-5   | Time constant of high-pass filter as a function of $C_{\mbox{\tiny HP}}$      |      |

|              | (typical values)                                                              | 5-3  |

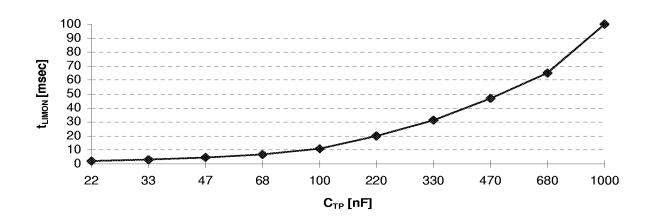

| Figure 5-6   | Delay time of the low-pass filter for the status output signal                |      |

|              | (typical values)                                                              | 5-4  |

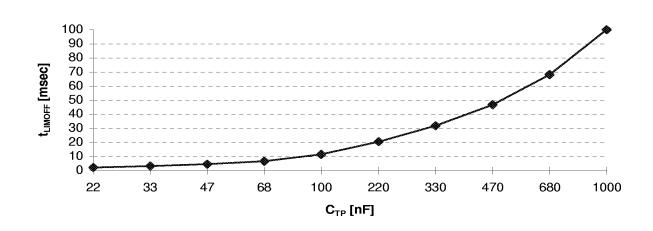

| Figure 5-7   | Delay time of the low-pass filter for the status output signal                |      |

|              | (typical values)                                                              | 5-4  |

| Figure 6-1   | Application Circuit                                                           | 6-1  |

| Figure 7-1   | Power Dissipation and Reference Voltage Output                                |      |

| Figure 7-2   | Maximal Line Currents                                                         |      |

| Figure 7-3   | Resistances                                                                   | 7-7  |

| Figure 7-4   | Line Status                                                                   |      |

| Figure 7-5   | Line Status under Superimposed Longitudinal Current                           |      |

| Figure 7-6   | Timing-Characteristics                                                        | 7-9  |

| Figure 7-7   | Lightning Voltage Influence                                                   | 7-10 |

| List of Table | es                                        | Page |

|---------------|-------------------------------------------|------|

| Table 2-1     | Pin Definitions and Functions P-DSO-20-6  | 2-2  |

| Table 2-2     | Pin Definitions and Functions P-DSO-20-10 | 2-2  |

| Table 7-1     | Absolute Maximum Ratings                  | 7-1  |

| Table 7-2     | Operating Range                           | 7-2  |

| Table 7-3     | Power-Supply                              | 7-3  |

| Table 7-4     | DC-Characteristics                        | 7-3  |

| Table 7-5     | Indication of Current Limit               | 7-4  |

| Table 7-6     | Timing-Characteristics                    | 7-6  |

Overview

#### 1 Overview

The IHPC is an integrated power controller especially designed for feeding two-wire ISDN-transmission lines. One line can be powered by one IHPC. An external resistor defines the value of the current-limit for the line. Powering can be switched on or off by the logic inputs "PFEN" and "PFENQ". With a logic low at the "APFI" output the IHPC signals that current-limiting is active; this signal is low-pass filtered. An external capacitor defines the corner frequency of this low-pass filter and the resulting delay time respectively. A second external capacitor is needed to make sure that longitudinal disturbances (AC) will not produce a current limiting effect. Line current-limiting and reducing this limiting level in case of overtemperature guards the IHPC against overloads.

# ISDN High Voltage Power Controller IHPC

**PEB 2026**

Version 1.1 CMOS

#### 1.1 Features

- Battery voltage up to 130 V

- Supplies power for one transmission line

- · Current limiting and chip temperature control

- Limiting current can be programmed by an external resistor

- Automatically reduced feeding current in case of overtemperature

- Reliable 170 V Smart Power Technology (SPT 170)

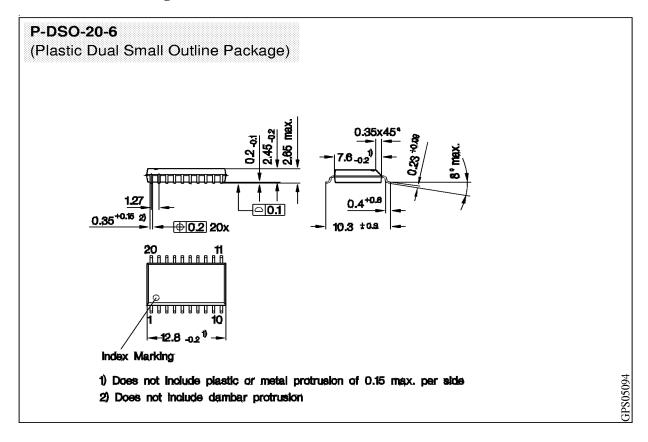

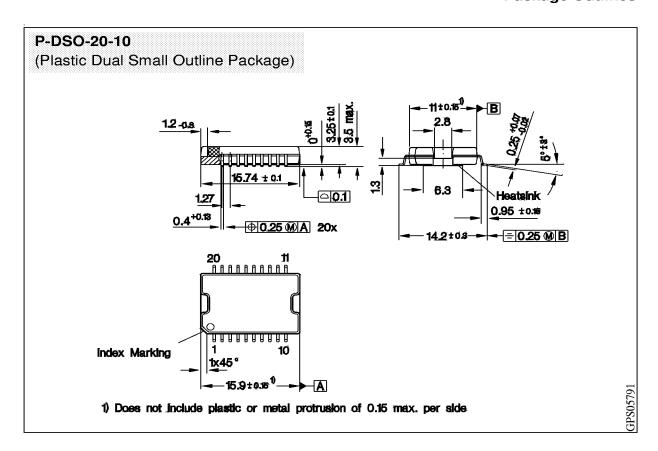

- Small P-DSO-20 package

| Туре     | Package     |

|----------|-------------|

| PEB 2026 | P-DSO-20-6  |

|          | P-DSO-20-10 |

Data Sheet 1-2 09.99

Pin Description

# 2 Pin Description

#### 2.1 Pin Configuration

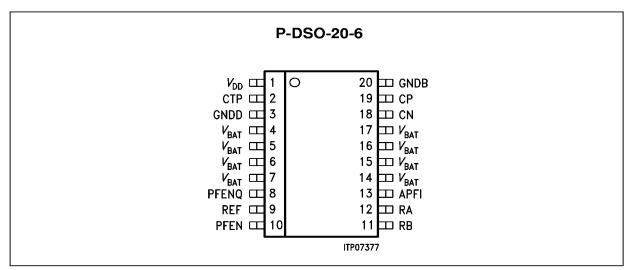

Figure 2-1 Pin Configuration P-DSO-20-6 (top view)

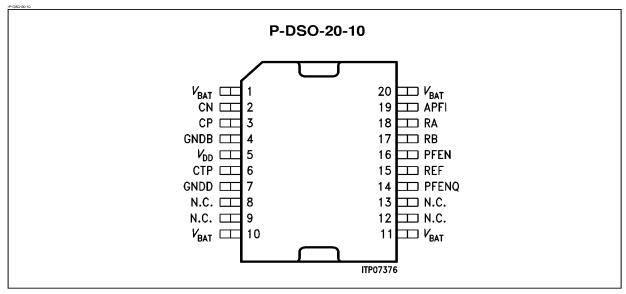

Figure 2-2 Pin Configuration P-DSO-20-10 (top view)

Data Sheet 2-1 09.99

**Pin Description**

#### 2.2 Pin Definitions and Functions

Table 2-1 Pin Definitions and Functions P-DSO-20-6

| Pin           | Symbol                       | Туре   | Description                                                                             |  |

|---------------|------------------------------|--------|-----------------------------------------------------------------------------------------|--|

| 4-7,<br>14-17 | $V_{\scriptscriptstyle BAT}$ | Supply | Negative battery supply voltage (- 100 V), referred to GNDB                             |  |

| 20            | GNDB                         | Supply | Battery ground: RB and RA refer to this pin                                             |  |

| 1             | $V_{\scriptscriptstyle DD}$  | Supply | Positive supply voltage (+ 5 V), referred to GNDD                                       |  |

| 3             | GNDD                         | Supply | Digital ground: $V_{\rm DD}$ , REF, CP, CN, CTP, PFEN, PFENQ and APFI refer to this pin |  |

| 9             | REF                          | 0      | Reference output, connected to GNDD via a resistor                                      |  |

| 19            | СР                           | 0      | Positive pole of the external capacitor $C_{\mbox{\tiny HP}}$                           |  |

| 18            | CN                           | I      | Negative pole of the external capacitor $C_{\mbox{\tiny HP}}$                           |  |

| 2             | СТР                          | 0      | Positive pole of the external capacitor $C_{\scriptscriptstyleTP}$                      |  |

| 11            | RB                           | 0      | Output for powering line b (tip), current sensing                                       |  |

| 12            | RA                           | 0      | High voltage output for powering line a (ring), current limiting/switching              |  |

| 10            | PFEN                         | I      | Logic high on this pin switches on the current feeding                                  |  |

| 8             | PFENQ                        | I      | Logic low on this pin switches on the current feeding                                   |  |

| 13            | APFI                         | 0      | Logic low on this pin signals active current-limiting                                   |  |

Table 2-2

Pin Definitions and Functions P-DSO-20-10

| Pin            | Symbol                       | Туре   | Description                                                                             |

|----------------|------------------------------|--------|-----------------------------------------------------------------------------------------|

| 1,10,<br>11,20 | $V_{\scriptscriptstyle BAT}$ | Supply | Negative battery supply voltage (- 100 V), referred to GNDB                             |

| 4              | GNDB                         | Supply | Battery ground: RB and RA refer to this pin                                             |

| 5              | $V_{	extsf{DD}}$             | Supply | Positive supply voltage (+ 5 V), referred to GNDD                                       |

| 7              | GNDD                         | Supply | Digital ground: $V_{\rm DD}$ , REF, CP, CN, CTP, PFEN, PFENQ and APFI refer to this pin |

| 15             | REF                          | 0      | Reference output, connected to GNDD via a resistor                                      |

| 3              | СР                           | 0      | Positive pole of the external capacitor $C_{\mbox{\tiny HP}}$                           |

| 2              | CN                           | I      | Negative pole of the external capacitor $C_{\mbox{\tiny HP}}$                           |

| 6              | CTP                          | 0      | Positive pole of the external capacitor $C_{	t TP}$                                     |

| 17             | RB                           | 0      | Output for powering line b (tip), current sensing                                       |

Data Sheet 2-2 09.99

# **Pin Description**

Table 2-2

Pin Definitions and Functions P-DSO-20-10 (cont'd)

| Pin | Symbol | Туре | Description                                                                |

|-----|--------|------|----------------------------------------------------------------------------|

| 18  | RA     | 0    | High voltage output for powering line a (ring), current limiting/switching |

| 16  | PFEN   | I    | Logic high on this pin switches on the current feeding                     |

| 14  | PFENQ  | I    | Logic low on this pin switches on the current feeding                      |

| 19  | APFI   | 0    | Logic low on this pin signals active current-limiting                      |

Data Sheet 2-3 09.99

#### **Functional Description**

# 3 Functional Description

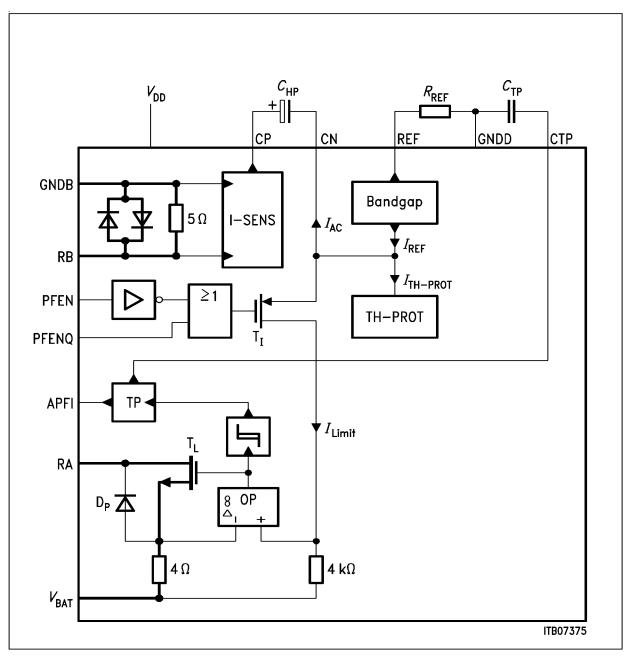

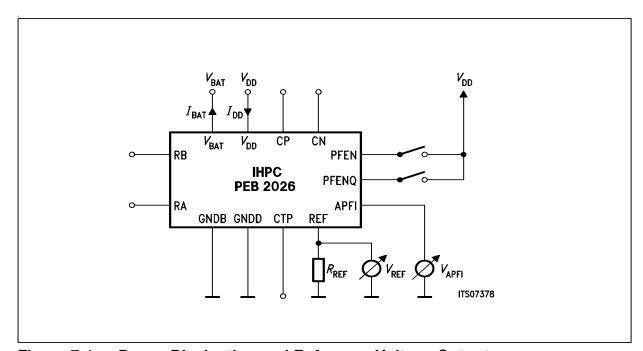

Figure 3-1 Block Diagram

The current flowing from GNDB to RB is measured. A down scaled image of this current is filtered by a high-pass filter with a corner frequency  $f_{\text{CHP}}$  of approximately 3 Hz (see

Data Sheet 3-1 09.99

#### **Functional Description**

Figure 5-4). This filter needs the external capacitor  $C_{\rm HP}$ . This "AC"-current is subtracted from the reference-current generated in the bandgap. The value of the reference-current is defined by the external resistor  $R_{\rm REF}$ .

In case of overtemperature the thermal protection TH-PROT sinks a current, so that the current  $I_{\text{Limit}}$  is reduced. So in case of high power dissipation on chip the junction temperature is limited to about 165 °C.

This function is a protection against instant damages due to overload at the outputs. Continuous high temperatures during operation, however, will reduce the life time of the IHPC. A maximum junction temperature of 150 °C shall not be exceeded (See section 7, "Electrical Characteristics")

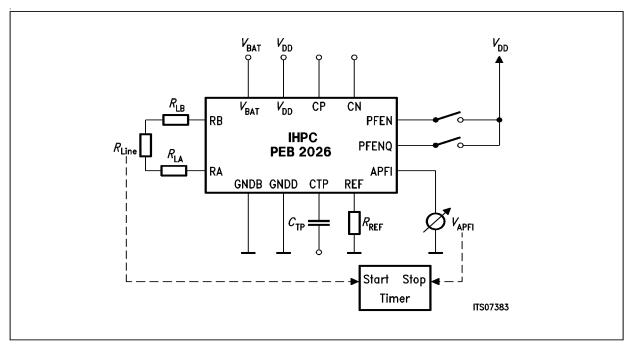

Measures have to be taken to switch off the IHPC in case of a short-circuit. E.g. if pin APFI indicates active current-limiting, the IHPC should be deactivated after 1.5 sec using pin PFEN or PFENQ. A consecutive power-up attempt shall give enough time to the IHPC to cool down again (e.g. 30 sec).

The current  $I_{\text{Limit}}$  is reflected to the output current  $I_{\text{Line}}$  flowing from RA to  $V_{\text{BAT}}$  using the operational-amplifier OP, the transistor  $T_{\text{L}}$  and two resistors (4  $\Omega$ , 4 k $\Omega$ ).

$$I_{\text{Line,max}}$$

(t) = 1000 ×  $I_{\text{Limit}}$  (t) = 1000 × ( $I_{\text{REF}} - I_{\text{TH-PROT}}$  (t) -  $I_{\text{AC}}$  (t))

In case of "no current-limiting" the output voltage of the operational-amplifier OP is equal to the positive OP-supply voltage. The transistor  $T_{\perp}$  is "switched on".

If the output current  $I_{\rm Line}$  rises to  $I_{\rm Line,max}$  the current-mirror becomes active and keeps the output current at this level.

The voltage level at the gate of transistor  $T_{\perp}$  shows the state of the current-limiter (current-limiting active or not). This state-signal is filtered by a low-pass filter and generates the logic output APFI. The external capacitor  $C_{\text{TP}}$  of this low-pass filter defines the corner frequency and the resulting delay times  $t_{\text{LIMON}}$  (Spec.-No.: 17) and  $t_{\text{LIMOFF}}$  (Spec.-No.: 18) respectively.

Summarized, the current sensor I-SENS and the high-pass filter prevent, that a longitudinal disturbance in the frequency range from about  $(5*f_{\text{CHP}})$  to about 100kHz result in a current limitation. This applies if the maximum amplitude of the longitudinal current is lower than about half of the current limit (Spec.-No.: 3) defined by the external resistor  $R_{\text{REF}}$ , see also Spec.-No.: 15 and 16.

There is also another effect from the current sensing and high-pass filtering, which can be seen when changing from status LIMOFF to LIMON. This can occur by switching power on to the line (loading the line capacitor) or in case of short-circuiting the line. The resulting current transient starts at half of  $I_{\rm Line,max}$  and increases (capacitor loading function) to  $I_{\rm Line,max}$  with a time constant  $t_{\rm CHP}$  also defined by the value of  $C_{\rm HP}$ .

#### **Functional Description**

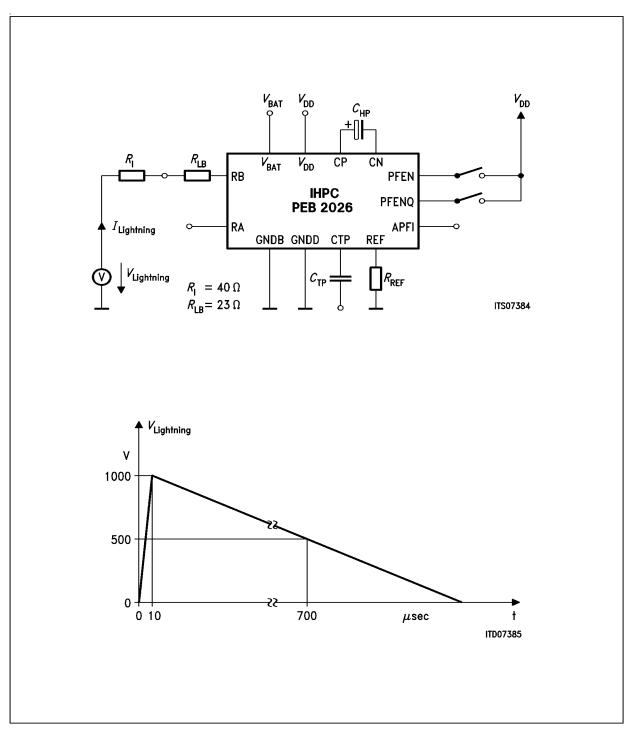

The diodes connected to GNDB and RB protect the IHPC against lightning and overvoltages (**see Absolute Maximum Ratings**). The diode  $D_p$  is the parasitic bulk-drain-diode of the DMOS-transistor  $T_L$ .

Because of technology reasons ("p"-substrate, junction isolation) there are also parasitic diodes from pin  $V_{\rm BAT}$  to all other pins.

#### $I_{\text{\tiny RAT}}$ current peak:

When line feeding is switched on (transistor  $T_{\rm L}$  is on) and a short circuit occurs between pins RA and GNDB (or GNDD) then it needs a certain time to unload the gate-source-capacitance of  $T_{\rm L}$  and to limit the current to the defined maximum value. In the meantime a current peak  $I_{\rm BAT}$  on the supply voltage  $V_{\rm BAT}$  can be seen.

An overvoltage protection circuit for pin RA, for example can produce such a short circuit between pins RA and GNDB.

In the IHPC a fast bipolar npn-transistor limits such current peaks. With  $V_{BAT}$  =100 V, the resulting  $I_{BAT}$  current transient has the profile of one triangular pulse with a peak value of about 1.5A and a time duration (50% to 50%) of about 130nsec.

Data Sheet 3-3 09.99

# **Operating Modes**

# 4 Operating Modes

| Operating Mode    | Status                       | PFEN                | PFENQ              | APFI                 |

|-------------------|------------------------------|---------------------|--------------------|----------------------|

| OFF, powering off |                              | " $V_{\sqcup}$ "    | Don't care         | " $V_{	extsf{oL}}$ " |

| OFF, powering off |                              | Don't care          | "V <sub>IH</sub> " | " $V_{	extsf{oL}}$ " |

| ON, powering on   | LIMON, limiter is active     | " $V_{IH}$ "        | "V <sub>"</sub> ." | " $V_{	extsf{oL}}$ " |

| ON, powering on   | LIMOFF, limiter isn't active | " $V_{	ext{	in}}$ " | " $V_{\Vdash}$ "   | " $V_{OH}$ "         |

The logic input pins PFEN and PFENQ are connected to GNDD by integrated current sources. If these pins are not connected externally the logic level is " $V_{\rm L}$ ".

Data Sheet 4-1 09.99

# 5 Designing the External Components

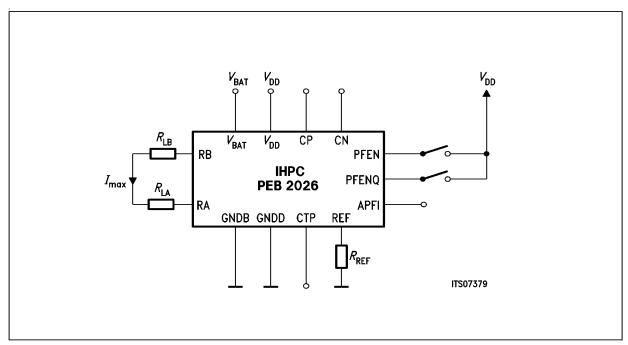

Resistor  $R_{REF}$ :

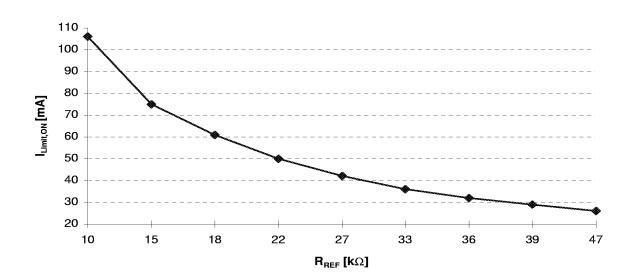

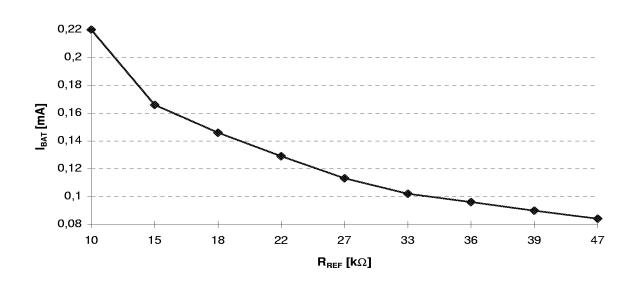

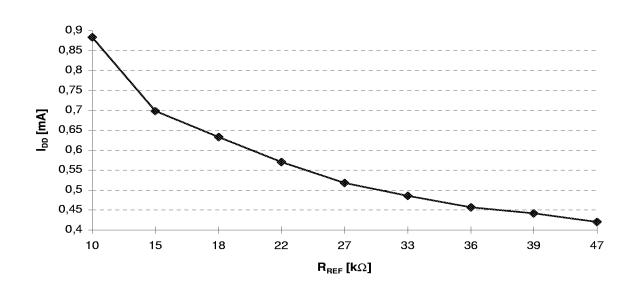

The value of this resistor defines the current limit  $I_{\text{Limit,ON}}$  (Spec.-No.: 3) and it will also effect power supply currents  $I_{\text{BAT}}$  (Spec.-No.: 2) and  $I_{\text{DD}}$  (Spec.-No.: 1). For typical values of  $I_{\text{Limit,ON}}$ ,  $I_{\text{BAT}}$  and  $I_{\text{DD}}$  as a function of  $R_{\text{REF}}$  see the following diagrams.

Figure 5-1 Current limit  $I_{Limit,ON}$  as a function of  $R_{REF}$  (typical values)

Figure 5-2 Power Supply Current  $I_{BAT}$  as a function of  $R_{REF}$  (typical values)

Figure 5-3 Power Supply Current  $I_{DD}$  as a function of  $R_{REF}$  (typical values)

Data Sheet 5-2 09.99

#### Capacitor $C_{HP}$ :

The value of this capacitor defines the corner frequency  $f_{CHP}$  of the high-pass filter and the time constant  $t_{CHP}$  of the current transient described at the last but one paragraph of chapter 2. The following diagrams show typical values of  $f_{CHP}$  and  $t_{CHP}$  as a function of  $C_{HP}$ .

Figure 5-4 Corner frequency of high-pass filter as a function of  $C_{\rm HP}$  (typical values)

Figure 5-5 Time constant of high-pass filter as a function of  $C_{HP}$  (typical values)

Data Sheet 5-3 09.99

#### Capacitor $C_{\text{\tiny TP}}$ :

The value of this capacitor defines the corner frequency and the resulting delay times  $t_{\text{LIMON}}$  (Spec.-No.: 17) and  $t_{\text{LIMOFF}}$  (Spec.-No.: 18), of the low-pass filter. For typical values of  $t_{\text{LIMON}}$  and  $t_{\text{LIMOFF}}$  as a function of  $C_{\text{TP}}$  see the following diagrams.

Figure 5-6 Delay time of the low-pass filter for the status output signal (typical values)

Figure 5-7 Delay time of the low-pass filter for the status output signal (typical values)

Data Sheet 5-4 09.99

# **Application Note**

# 6 Application Note

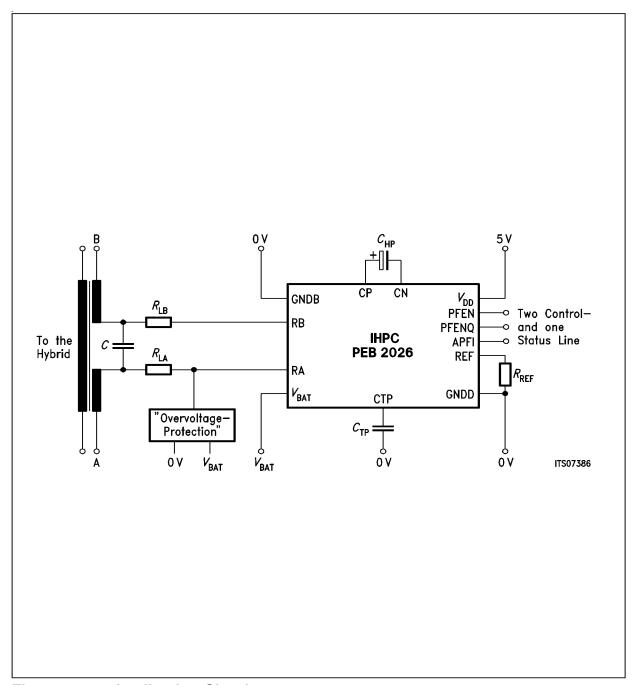

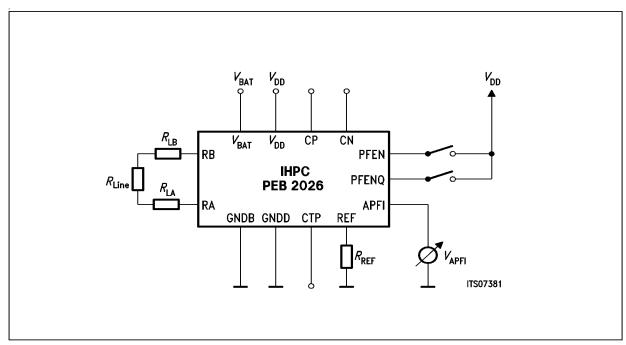

Figure 6-1 Application Circuit

Data Sheet 6-1 09.99

#### **Application Note**

$R_{\text{REF}}$  Defines the current-limit and the internal biasing currents. A

smaller/bigger value increases/decreases the current limit. It

will also effect power supply currents.

$C_{\text{\tiny TP}}$  Defines with an internal resistor the delay time (a typical value

is 20 msec) from the low pass filter, whose output signal is called 'APFI'. Short disturbances will therefore be filtered. A smaller/bigger value decreases/increases the delay time.

$C_{\rm HP}$  Defines with an internal resistor the corner frequency from a

high pass filter. It is used to make sure that longitudinal disturbances (AC) will not produce a current limiting effect. A smaller/bigger value decreases/increases the corner

frequency.

$R_{LA}$ ,  $R_{LB}$  These resistors limit the peak currents during lightning

transients. The maximum value for these resistors is defined

by the allowed voltage drop on the resistors.

C The AC-signal-current will be shunted by this capacitor.

A, B A- and B-line to the subscriber

$V_{\text{BAT}}$  The most negative supply voltage; also called battery voltage.

overvoltage protection This circuit makes sure that the voltage from  $R_A$  to  $V_{BAT}$  will not

exceed the defined limits in case of lightning (see Absolute

Maximum Ratings).

#### **Recommended Device Values:**

$R_{\rm BEF}$  22 k $\Omega$ , Current limiting is set to 50 mA

$C_{\text{TP}}$  220 nF, 'APFI' delay time is set to 20 msec

$C_{HP}$  4.7  $\mu$ F,AC longitudinal disturbances in a frequency range

higher than 16.666 Hz do not effect a current limiting.

$R_{LA}$ ,  $R_{LB}$  23  $\Omega$ , Minimum value, so that peek currents don't exceed 16 A

(using voltage peek = 1 kV from 40  $\Omega$  source resistance) in

case of lightning.

# 7 Electrical Characteristics

Table 7-1 Absolute Maximum Ratings

| Parameter                                                | Symbol                                                         | Symbol Limit Values |                                      | Unit | Test Condition                                       |  |

|----------------------------------------------------------|----------------------------------------------------------------|---------------------|--------------------------------------|------|------------------------------------------------------|--|

|                                                          |                                                                | min.                | max.                                 | 1    |                                                      |  |

| Battery voltage                                          | $V_{\scriptscriptstyle BAT}$                                   | - 150               | 0.5                                  | V    | Referred to GNDB                                     |  |

| $\overline{V_{\scriptscriptstyle  m DD}}$ supply voltage | $V_{	extsf{DD}}$                                               | - 0.5               | 6                                    | V    | Referred to GNDD                                     |  |

| Ground voltage difference                                | $V_{ m GNDB} - V_{ m GNDD}$                                    | - 0.5               | 0.5                                  | V    |                                                      |  |

| Ground pulse voltage difference                          | $V_{	ext{GNDB}} - V_{	ext{GNDD}}$                              | <b>– 1</b>          | 1                                    | V    | $t_{\text{max}} = 1 \text{ msec}$                    |  |

| Junction temperature                                     | $T_{\rm j}$                                                    |                     | 150                                  | °C   |                                                      |  |

| Voltages on logic inputs PFEN, PFENQ                     | $V_{\scriptscriptstyle{PFEN}},\ V_{\scriptscriptstyle{PFENQ}}$ | - 0.3               | $V_{\rm DD}$ + 0.3                   | V    | Referred to GNDD                                     |  |

| Voltages on REF                                          | $V_{\scriptscriptstyle{REF}}$                                  | - 0.3               | $V_{\scriptscriptstyle  m DD}$ + 0.3 | V    | Referred to GNDD                                     |  |

| Voltages on CP                                           | $V_{	extsf{CP}}$                                               | - 0.3               | $V_{\scriptscriptstyle  m DD}$ + 0.3 | V    | Referred to GNDD                                     |  |

| Voltages on CN                                           | $V_{\scriptscriptstyleCN}$                                     | - 0.3               | $V_{\scriptscriptstyle  m DD}$ + 0.3 | V    | Referred to GNDD                                     |  |

| Voltages on CTP                                          | $V_{	exttt{CTP}}$                                              | - 0.3               | $V_{\scriptscriptstyle  m DD}$ + 0.3 | V    | Referred to GNDD                                     |  |

| Voltages on logic output<br>APFI                         | $V_{\scriptscriptstyleAPFI}$                                   | - 0.3               | $V_{\text{DD}}$ + 0.3                | V    | Referred to GNDD                                     |  |

| RB voltage                                               | $V_{\scriptscriptstyle{RB}}$                                   | - 0.5               | + 0.5                                | V    | Referred to GNDB                                     |  |

| RB pulse current                                         | $I_{\rm RB}$ (into pin RB)                                     | - 8                 | 8                                    | Α    | $t_{\rm max} = 1 \; {\rm msec}$                      |  |

| RB peak current                                          | $I_{	ext{RB\_peak}}$                                           | <b>– 16</b>         | 16                                   | Α    | See figure 7-7                                       |  |

| RA voltages                                              | $V_{RA}$                                                       | - 0.3               | 150                                  | V    | Referred to $V_{\scriptscriptstyle BAT}$             |  |

| RA pulse current                                         | $I_{\rm RA}$ (into pin RA)                                     | <b>- 1</b>          | 1                                    | А    | $t_{\text{max}} = 1 \text{ msec}$                    |  |

| RA pulse voltage                                         | $V_{	extsf{RA\_pulse}}$                                        | <b>– 1</b>          | 170                                  | V    | $t_{\rm max}$ = 1 msec,<br>Referred to $V_{\rm BAT}$ |  |

| ESD-voltage, all pins                                    |                                                                |                     | 1                                    | kV   | Human body model                                     |  |

Note: Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

Table 7-2 Operating Range

| Parameter                                                     | Symbol                       | Limit Va | Limit Values |    | <b>Test Condition</b> |

|---------------------------------------------------------------|------------------------------|----------|--------------|----|-----------------------|

|                                                               |                              | min.     | max.         |    |                       |

| Battery voltage                                               | $V_{\scriptscriptstyle BAT}$ | - 130    | - 30         | V  | Referred to<br>GNDB   |

| $\overline{V_{\scriptscriptstyle 	extsf{DD}}}$ supply voltage | $V_{	extsf{DD}}$             | 4.75     | 5.25         | V  | Referred to GNDD      |

| Ground voltage difference                                     | $V_{ m GNDB} - V_{ m GNDD}$  | - 0.3    | 0.3          | V  |                       |

| Ambient temperature<br>PEB 2026<br>PEF 2026                   | $T_{A}$ $T_{A}$              | 0<br>-40 | +70<br>+85   | °C |                       |

#### **Static Thermal Resistance**

| Junction to ambient | $R_{th, jA}$    | 55 | K/W | P-DSO-20-10 |

|---------------------|-----------------|----|-----|-------------|

| Junction to case    | $R_{th, jC}$    | 4  | K/W | P-DSO-20-10 |

| Junction to ambient | $R_{th, jA}$    | 65 | K/W | P-DSO-20-6  |

| Junction to pins    | $R_{th, jPins}$ | 15 | K/W | P-DSO-20-6  |

Note: In the operating range the functions given in the circuit description are fulfilled.

The power package P-DSO-20-10 has an exposed copper-heatspreader with a high thermal capacitance. For power feeding to ISDN-lines which are in a fault condition (e.g. short circuit) the maximum power dissipation on chip will become  $V_{\rm BAT}$  supply voltage times limiting current (e.g.:  $100V \cdot 50 {\rm mA} = 5 {\rm W}$ ). It is necessary to try to feed the line for about 2 seconds under this condition (5W), then the feeding can be switched off but must be switched on again about 30 seconds later. In this application the thermal capacitance of the cooper-heatspreader helps to keep the maximum chip temperature below the thermal protection temperature level (165°C). No extra heatsink is necessary.

The small P-DSO-20-6 package is applicable if the device is mounted on a pcb having at least 900 mm² copper area close to the device. The pcb serves as heat sink, heat flowing off through the pins, particularly the Vbat pins. With a mounting like this, the IHPC performs as follows: a current of 50 mA is supplied for 5 sec, while the device is shorted to Vbat=100V. At an ambient temperature of 70°C the current pulse may be periodically repeated with a period of 32 sec.

#### **Electrical Parameters**

Typical values are defined at the following test conditions:

$V_{\rm DD}$ =5V± 1 % $C_{\rm HP}$ =4.7 $\mu$ F± 10 %(6.3 V)

$V_{\text{BAT}} = -100 \text{V} \pm 1 \% C_{\text{TP}} = 220 \text{nF} \pm 10 \% (6.3 \text{ V})$

$R_{LA} = 23\Omega \pm 1 \% T_{A} = 25 \pm 5 \text{ °C}$

$R_{\text{LB}}$ =23 $\Omega$ ± 1 % $R_{\text{Line}}$ =± 0.1 %

$R_{\text{REF}}$ =22k $\Omega$ ± 1 %no heatsink

Min. and max. values are in force within the whole operating range.

Table 7-3 Power-Supply

| No.  | Parameter                                   | Symbol                            | Limit ' | Limit Values |      |    | Test      | Test | Mode |

|------|---------------------------------------------|-----------------------------------|---------|--------------|------|----|-----------|------|------|

|      |                                             |                                   | min.    | typ.         | max. |    | Condition | Fig. |      |

| Supp | oly Currents ( $I_{\scriptscriptstyle{RE}}$ | $_{\mathrm{B}}=I_{\mathrm{RA}}=0$ |         |              |      |    |           |      |      |

| 1    | $V_{\scriptscriptstyle 	extsf{DD}}$ current | $I_{	extsf{DD}}$                  |         | 0.57         | 0.9  | mA |           | 7-1  | all  |

| 2    | $V_{\scriptscriptstyle \sf BAT}$ current    | $I_{\scriptscriptstyle BAT}$      |         | 0.13         | 0.25 | mA |           | 7-1  | all  |

#### Table 7-4 DC-Characteristics

| No.  | Parameter        | Symbol            | Limit Values |      |      | Unit | 1         | Test | Mode                |

|------|------------------|-------------------|--------------|------|------|------|-----------|------|---------------------|

|      |                  |                   | min.         | typ. | max. |      | Condition | Fig. |                     |

| Maxi | imal Line Curren | ts                |              |      |      |      |           |      |                     |

| 3    | Line current     | $I_{ m limit,ON}$ | 45           | 50   | 55   | mA   |           | 7-2  | ON,<br>Sta-<br>tus: |

| 4    | Line current     | $I_{\sf max,OFF}$ |              | 0    | 10   | μА   |           | 7-2  | OFF                 |

#### Logic Input Levels on PFEN and PFENQ

| 5 | H-input voltage | $V_{\scriptscriptstyleIH}$     | 2 |    |     | V  |                                                                                     | all |

|---|-----------------|--------------------------------|---|----|-----|----|-------------------------------------------------------------------------------------|-----|

| 6 | L-input voltage | $V_{\scriptscriptstyle  m IL}$ |   |    | 0.8 | V  |                                                                                     | all |

| 7 | Input current   | $I_{inp}$                      | 2 | 11 | 20  | μΑ | $\begin{array}{c} \text{0.8 V} < = \\ V_{\text{inp}} < = V_{\text{DD}} \end{array}$ | all |

Data Sheet 7-3 09.99

# **Table 7-4 DC-Characteristics** (cont'd)

| No.   | Parameter                                                        | Symbol                       | Limit V                                  | Limit Values                |              |          | Test                                | Test | Mode                          |

|-------|------------------------------------------------------------------|------------------------------|------------------------------------------|-----------------------------|--------------|----------|-------------------------------------|------|-------------------------------|

|       |                                                                  |                              | min.                                     | typ.                        | max.         |          | Condition                           | Fig. |                               |

| Logi  | c Output Levels                                                  | on APFI                      |                                          |                             |              |          |                                     |      |                               |

| 8     | H-output<br>voltage                                              | $V_{OH}$                     | $V_{\scriptscriptstyle 	extsf{DD}}-$ 0.4 |                             |              | V        | I <sub>Source</sub> = 100 μA        |      | ON                            |

| 9     | L-output voltage                                                 | $V_{OL}$                     |                                          |                             | 0.4          | V        | $I_{\rm Sink}$ = 100 $\mu$ A        |      | ON,<br>OFF                    |

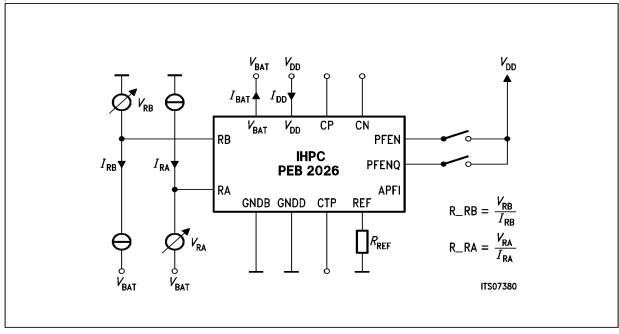

| Resi  | stance from GND                                                  | B to R <sub>B</sub>          |                                          |                             |              |          |                                     |      |                               |

| 10    | R: GNDB to RB                                                    | $R_{	t RB}$                  | 3                                        | 5                           | 7            | Ω        | $I_{\text{RB}}$ = 30 mA $\pm$ 5 %   | 7-3  | ON,<br>OFF                    |

| ON-ı  | esistance from $R$                                               | $I_{A}$ to $V_{BAT}$         |                                          |                             |              |          |                                     |      |                               |

| 11    | ON-R: RA to $V_{\rm BAT}$ ( $T_{\rm L}$ - $R_{\rm on}$ included) | $R_{\scriptscriptstyle{RA}}$ | 2.65                                     | 5                           | 7.35         | Ω        | $I_{RA} = 30 \text{ mA}$ $\pm 5 \%$ | 7-3  | ON,<br>Sta-<br>tus:<br>LIMOFF |

| Diffe | rence-resistance                                                 | between                      | $R_{\scriptscriptstyle RA}$ and          | $R_{\scriptscriptstyle RB}$ |              |          |                                     |      |                               |

| 12    | R <sub>RA</sub> - R <sub>RB</sub><br>PEB 2026<br>PEF 2026        | $R_{	extsf{DIFF}}$           | - 0.35<br>- 0.40                         | 0                           | 0.35<br>0.40 | $\Omega$ |                                     |      | ON,<br>Sta-<br>tus:           |

#### **Table 7-5** Indication of Current Limit

| No.  | Parameter        | Symbol           | Mode | Test Condition                 | Status                                                    | Test<br>Fig. |

|------|------------------|------------------|------|--------------------------------|-----------------------------------------------------------|--------------|

| Indi | cation of Curren | t Limit          |      |                                |                                                           |              |

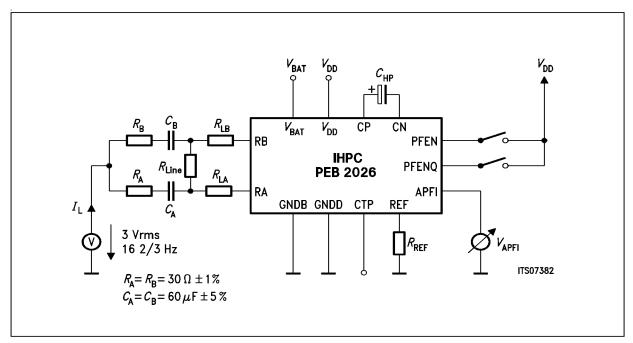

| 13   | Line Status      | $S_{\sf LIMON}$  | ON   | $R_{\rm Line} = 1762 \ \Omega$ | $\begin{array}{c} LIMON, \\ APFI = V_{OL} \end{array}$    | 7-4          |

| 14   | Line Status      | $S_{\sf LIMOFF}$ | ON   | $R_{\rm Line}$ = 2166 $\Omega$ | $ \begin{array}{l} LIMOFF, \\ APFI = V_{OH} \end{array} $ | 7-4          |

Data Sheet 7-4 09.99

#### Table 7-5 Indication of Current Limit (cont'd)

| No.  | Parameter       | Symbol                              | Mode      | Test Condition                    | Status                                                | Test<br>Fig. |

|------|-----------------|-------------------------------------|-----------|-----------------------------------|-------------------------------------------------------|--------------|

| Indi | cation of Curre | ent Limit und                       | der Super | imposed Longitud                  | dinal Current                                         |              |

| 15   | Line Status     | $S_{\scriptscriptstyle \sf LLIMON}$ | ON        | $R_{\text{Line}} = 1482 \ \Omega$ | $\begin{array}{c} LIMON,\\ APFI = V_{OL} \end{array}$ | 7-5          |

| 16   | Line Status     | $S_{\sf LLIMOFF}$                   | ON        | $R_{\text{Line}} = 2801 \ \Omega$ | LIMOFF,                                               | 7-5          |

#### Calculation and Values of $R_{\scriptscriptstyle \mathsf{Line}}$

$$R_{\rm Line} = \frac{V_{\rm BAT}}{I_{\rm Line}} - R_{\rm RA} - R_{\rm RB} - R_{\rm LA} - R_{\rm LB} = \frac{100 \, \rm V}{I_{\rm Line}} - 5 \, \, \Omega - 5 \, \, \Omega - 23 \, \, \Omega$$

where:

$R_{\rm LA},\,R_{\rm LB}$  ... referred to page 7-3, electrical parameters

$R_{\rm RA},\,R_{\rm RB}\,...$  referred to Spec.-No.: 10 and 11

| $I_{\sf Line}$ | $R_{Line}$ |

|----------------|------------|

| 35 mA          | 2801 Ω     |

| 45 mA          | 2166 Ω     |

| 55 mA          | 1762 Ω     |

| 65 mA          | 1482 Ω     |

Note: In some of these cases the IHPC will limit the line current to lower values.

Data Sheet 7-5 09.99

Table 7-6 Timing-Characteristics

| No | Paramete | Symbol | Limit Values |      | Unit | Test Condition | Tes | Mod  |   |

|----|----------|--------|--------------|------|------|----------------|-----|------|---|

| •  | r        |        | min          | typ. | max  |                |     | t    | е |

|    |          |        |              |      |      |                |     | Fig. |   |

#### Delay from Begin/End of Current Limiting to Status LIMON/LIMOFF

| 17 | Time to<br>LIMON  | t <sub>LIMON</sub>  | 10 | 20 | 30 | msec | R <sub>Line</sub> :<br>2166 Ω† 1762 Ω<br>==><br>APFI:<br>LIMOFF ✍✍サ<br>LIMON       | 7-6 | ON |

|----|-------------------|---------------------|----|----|----|------|------------------------------------------------------------------------------------|-----|----|

| 18 | Time to<br>LIMOFF | t <sub>LIMOFF</sub> | 10 | 20 | 30 | msec | R <sub>Line</sub> :<br>1762 Ω 必必计 2166<br>Ω<br>==><br>APFI:<br>LIMON 必必计<br>LIMOFF | 7-6 | ON |

Figure 7-1 Power Dissipation and Reference Voltage Output

Data Sheet 7-6 09.99

Figure 7-2 Maximal Line Currents

Figure 7-3 Resistances

Data Sheet 7-7 09.99

Figure 7-4 Line Status

Figure 7-5 Line Status under Superimposed Longitudinal Current

Data Sheet 7-8 09.99

Figure 7-6 Timing-Characteristics

Figure 7-7 Lightning Voltage Influence

Data Sheet 7-10 09.99

**Package Outlines**

# 8 Package Outlines

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

SMD = Surface Mounted Device

Dimensions in mm

Data Sheet 8-1 09.99

### **Package Outlines**

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

SMD = Surface Mounted Device

Dimensions in mm

Data Sheet 8-2 09.99