# RCV336ACF/SP and RCV144ACF/SP Modem Device

Designer's Guide (Preliminary)

> Order No. 1046 Rev. 3, August 2, 1996

#### 1. INTRODUCTION

#### 1.1 SUMMARY

The Rockwell RCV336ACF/SP and RCV144ACF/SP Modem Device Families support high speed data, high speed fax, AudioSpan, speakerphone, voice/audio, and VoiceView operation. They are intended for use with dial-up telephone lines in the U.S. or world-wide and are eacg family is offered in six device models (Table 1-1).

The RCV336ACF/SP supports data line rates to 33.6 kbps in data modem mode or data line rates from 4.8 to 14.4 kbps plus audio in AudioSpan mode; the RCV144ACF/SP supports data line rates to 14.4 kbps in data modem mode or data line rates from 4.8 to 9.6 kbps plus audio in AudioSpan mode;

These RCV336ACF/SP and RCV144ACF/SP F-class modem devices are pin compatible, allowing design of a common printed circuit board to support either V.34 or V.32 bis modem performance, respectively, with the only hardware difference being the installed modem device.

Analog simultaneous audio/voice and data (AudioSpan) operation supports data rates with audio of 4.8 kbps in V.61 modulation or 4.8 to 9.6 kbps in ML144 modulation. The RC336/RCV336 also supports data rates with audio of 4.8 to 14.4 kbps in ML288 modulation.

SP models support position-independent, full-duplex speakerphone (FDSP).

As a data modem, the modem operates at line speeds to 33600 bps. Error correction (V.42/MNP 2-4) and data compression (V.42 bis/MNP 5) maximize data transfer integrity and boost average data throughput up to 115.2 kbps. Non-error-correcting mode is also supported.

Error correction and data compression (ECC) is performed in the modem using 32k bytes of external RAM to increase data throughput typically by a factor of four.

The modem supports fax Group 3 send and receive rates up to 14400 bps and supports T.30 protocol.

In voice/audio mode, enhanced ADPCM coding and decoding supports efficient digital storage of voice/audio using 2-bit or 4-bit per sample compression and decompression with a 7200 Hz sample rate. This mode also supports 8-bit monophonic audio encoding at 11.025 kHz or 7200 Hz. This mode supports digital telephone answering machine (DTAM), voice annotation, and audio recording and playback applications.

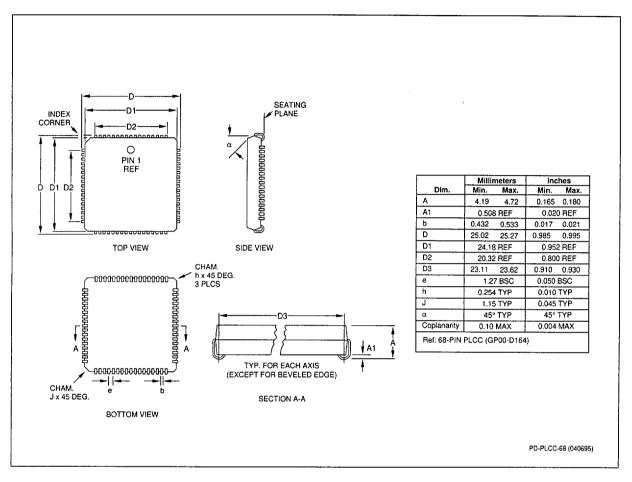

The modem device is packaged in a 68-pin PLCC.

Reference hardware designs are available with and without interface to sound chips (audio codecs). Voice/audio designs support functions such as music on hold and telephone/speakerphone conversation recording.

PC-based "ConfigurACE™ II for Windows" software allows modem firmware to be customized to application and country requirements. ConfigurACE™ II for Windows operation and programmable country call progress parameters are described in the on-line documentation accompanying the software.

This designer's guide describes the modem hardware capabilities and identifies the supporting AT commands. AT commands and S Registers are defined in the AT Command Reference Manual (Order No. 1048).

Table 1-1. Modem Models and Functions

|               |               | Suppor           | ted Function | s                        |         |

|---------------|---------------|------------------|--------------|--------------------------|---------|

| Model         | Data/Fax      | AudioSpan        | FDSP         | Voice/Audio<br>VoiceView | W-Class |

| RCV336ACF/SP  | V.34/V.17     | V.61/ML144/ML288 | S            | s                        | -       |

| RCV336ACFW/SP | V.34/V.17     | V.61/ML144/ML288 | S            | S                        | S       |

| RCV336ACF     | V.34/V.17     | V.61/ML144/ML288 | -            | S                        | •       |

| RCV336ACFW    | V.34/V.17     | V.61/ML144/ML288 | -            | S                        | S       |

| RC336ACF      | V.34/V.17     | V.61/ML144/ML288 | -            | -                        | -       |

| RC336ACFW     | V.34/V.17     | V.61/ML144/ML288 | -            | -                        | S       |

| RCV144ACF/SP  | V.32 bis/V.17 | V.61/ML144       | S            | S                        | -       |

| RCV144ACFW/SP | V.32 bis/V.17 | V.61/ML144       | S            | S                        | S       |

| RCV144ACF     | V.32 bis/V.17 | V.61/ML144       | _            | S                        | -       |

| RCV144ACFW    | V.32 bis/V.17 | V.61/ML144       | -            | S                        | S       |

| RC144ACF      | V.32 bis/V.17 | V.61/ML144       | •            | -                        | •       |

| RC144ACFW     | V.32 bis/V.17 | V.61/ML144       | -            | -                        | S       |

#### Notes:

1. Model options:

SP

Speakerphone.

٧

Voice, audio, and VoiceView.

W

World-class (W-class).

2. Supported functions (S = Supported; — = Not supported):

AudioSpan

Analog simultaneous audio/voice and data.

FDSP

Full-duplex speakerphone.

Voice/audio

Voice and audio functions.

VoiceView

VoiceView alternating voice and data.

W-Class

World-class functions supporting multiple country requirements.

#### 1.2 FEATURES

- AudioSpan (simultaneous audio/voice and data)

- ITU-T V.61 modulation (4.8 kbps data plus audio)

- ML144 modulation (4.8 to 9.6 kbps data plus audio)

- ML288 modulation (4.8 to 14.4 kbps data plus audio)

- Audio/silence detection (ML144) and handset echo cancellation

- Handset, headset, or half-duplex speakerphone

- Full-duplex speakerphone (FDSP) mode (option)

- Acoustic and line echo cancellation

- Microphone gain and muting

- Speaker volume control and muting

- Room monitor

- Data modem throughput up to 115.2 kbps

- 33.6 kbps and V.34 (RCV336 only)

- V.32 bis, V.32, V.22 bis, V.22A/B, V.23, and V.21; Bell 212A and 103

- V.42 LAPM, MNP 2-4, and MNP 10 error correction

- V.42 bis and MNP 5 data compression

- MNP 10EC™ enhanced cellular performance

- Hayes AutoSync (option)

- Fax modem send and receive rates up to 14400 bps

- V.33, V.17, V.29, V.27 ter, and V.21 channel 2

- Voice/audio mode (option)

- Enhanced ADPCM compression/decompression

- Tone detection/generation and call discrimination

- Concurrent DTMF detection

- 8-bit monophonic audio data encoding at 11.025 kHz or 7200 Hz

- VoiceView alternating voice and data (option)

- World-class operation (option)

- Call progress, blacklisting, multiple country support

- Communication software compatible AT command sets

- NVRAM directory and stored profiles

- Built-in DTE interfaces with speed up to 115.2 kbps

- Parallel 16550A UART-compatible interface

- Serial ITU-T V.24 (EIA/TIA-232-E)

- Supports Rockwell PnP ISA Bus Interface Device

- Supports Serial PnP interface per Plug and Play External COM Device Specification, Rev 1.00

- · Serial async data; parallel async data

- · Caller ID and distinctive ring detect

- Single package: 68-pin PLCC

- +5V operation

#### 1.3 TECHNICAL OVERVIEW

#### 1.3.1 General Description

The single device provides the processing core for a complete system design featuring data/fax modem, AudioSpan, speakerphone, audio, voice, and VoiceView support depending on model (Table 1-1). The OEM adds a crystal, discrete components, and a telephone line/telephone/audio interface circuit to complete the system.

The modem is packaged in a 68-pin PLCC.

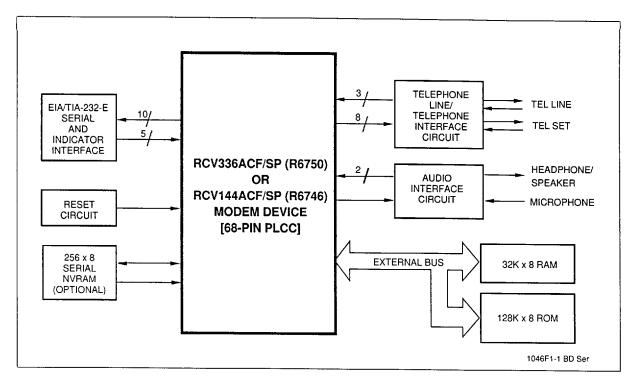

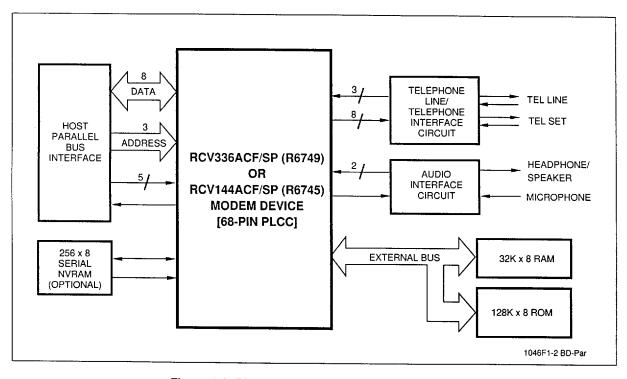

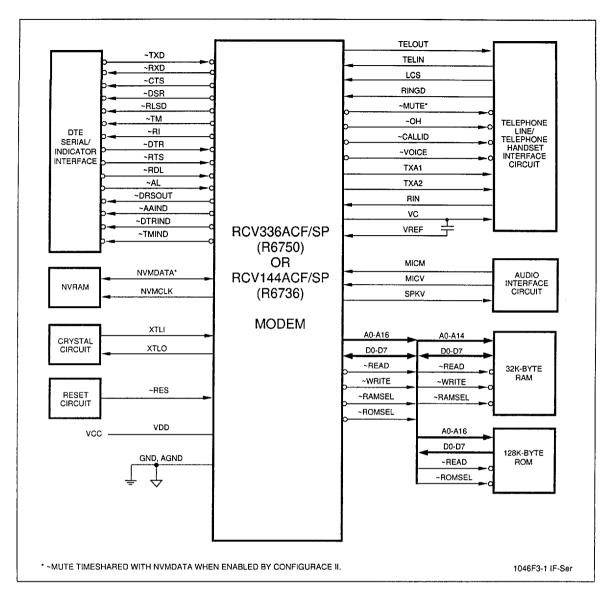

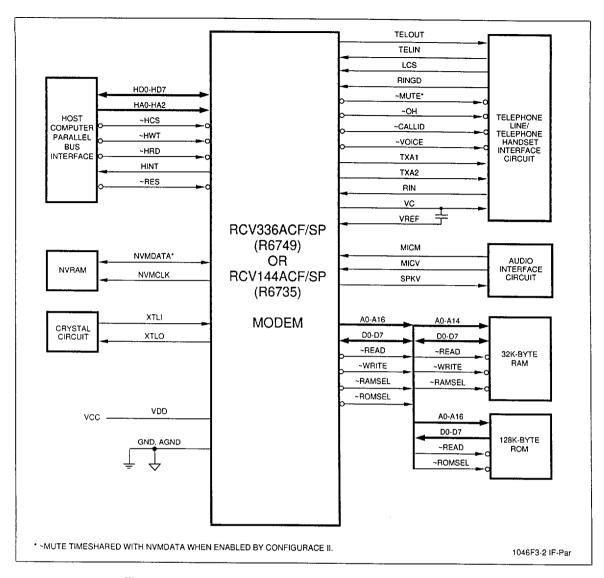

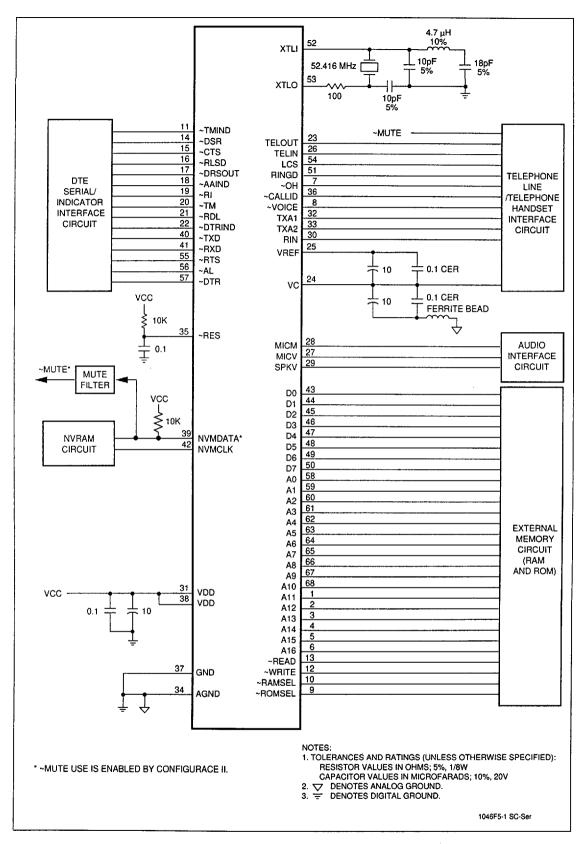

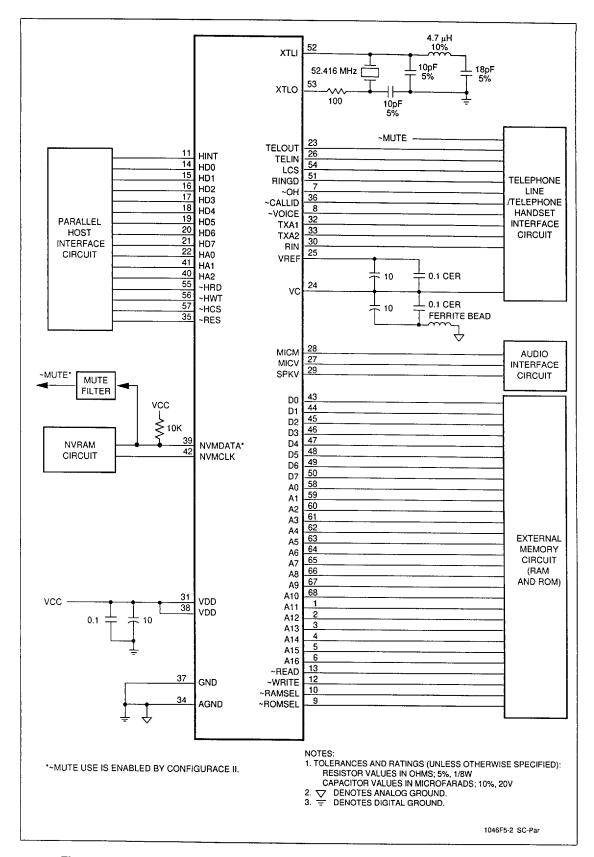

The modem is the full-featured, self-contained data modem/fax modem/voice/audio/speakerphone solution shown in Figure 1-1 (serial DTE interface) and Figure 1-2 (parallel host interface). Dialing, call progress, telephone line interface, AudioSpan, speakerphone, voice/audio, and VoiceView functions are supported and controlled through the AT command set.

The modem connects to the DTE via a V.24 (EIA/TIA-232-E) serial interface or to a host via a parallel microcomputer bus depending on modem model.

#### 1.3.2 Data/Fax Modes

In data modem modes, the modem can operate in 2-wire, full-duplex, asynchronous modes at line rates up to 33600 bps (RCV336) or 14400 bps (RCV144). Data modem modes perform complete handshake and data rate negotiations. All tone and pattern detection functions required by the applicable ITU or Bell standard are supported. For RCV336, using V.34 modulation to optimize modem configuration for line conditions, the modem can connect at the highest data rate that the channel can support from 33600 bps to 300 bps with automatic fallback. Automode operation in V.34 is provided in accordance with PN3320 and in V.32 bis in accordance with PN2330.

In fax modem modes, the modem fully supports Group 3 facsimile send and receive speeds of 14400, 12000, 9600, 7200, 4800, or 2400 bps. Fax modem modes support Group 3 fax requirements. Fax data transmission and reception performed by the modem is controlled and monitored through the fax EIA-578 Class 1 command interface. Full HDLC formatting, zero insertion/deletion, and CRC generation/checking is provided.

Both transmit and receive fax data are buffered within the modem. Data transfer to and from the DTE is flow controlled by XON/XOFF and RTS/CTS.

#### 1.3.3 AudioSpan Modes

AudioSpan provides full-duplex analog simultaneous audio/voice and data over a single telephone line. AudioSpan can send any type of audio waveform, including music. Data can be sent with or without error correction. The audio/voice interface can be in the form of a headset, handset, or a microphone and speaker (half-duplex speakerphone).

V.61 Modulation. AudioSpan can operate in V.61 modulation at a data rate with audio of 4800 bps.

ML144 Modulation. AudioSpan can operate in ML144 (V.32) modulation at a 4.8 to 9.6 kbps data rate with audio where lower data rates provide higher audio quality.

ML288 Modulation (RCV336/RC336 Only). AudioSpan can operate in ML288 (V.34 type) modulation at a 4.8 to 14.4 kbps data rate with audio where lower data rates provide higher audio quality.

#### 1.3.4 Speakerphone Mode (SP Models Only)

The speakerphone mode features an advanced proprietary speakerphone algorithm which supports full-duplex voice conversation with both acoustic and line echo cancellation. Parameters are constantly adjusted to maintain stability with automatic fallback from full-duplex to pseudo-duplex operation. The speakerphone algorithm allows position independent placement of microphone and speaker.

The speakerphone mode provides hands-free full-duplex telephone operation under host control. The host can separately control microphone gain and muting and speaker volume and muting.

Figure 1-1. Block Diagram - Serial DTE Interface

Figure 1-2. Block Diagram - Parallel Host Interface

#### 1.3.5 Modem Firmware

Modern firmware performs processing of general modern control, command sets, fax Class 1, AudioSpan, speakerphone, data modern, fax modern, voice/audio/TAM/speakerphone, VoiceView, W-class, and DTE/host interface functions.

Configurations of the modern firmware are provided to support parallel host bus interface operation or serial DTE interface operation.

The modem firmware is provided in object code form for the OEM to program into external ROM. The modem firmware may also be provided in source code form under a source code addendum license agreement.

#### 1.3.6 Supported Interfaces

The major hardware signal interfaces of the modem device are illustrated in Figure 1-1 (serial DTE interface) and Figure 1-2 (parallel host interface).

#### Parallel Host Bus Interface

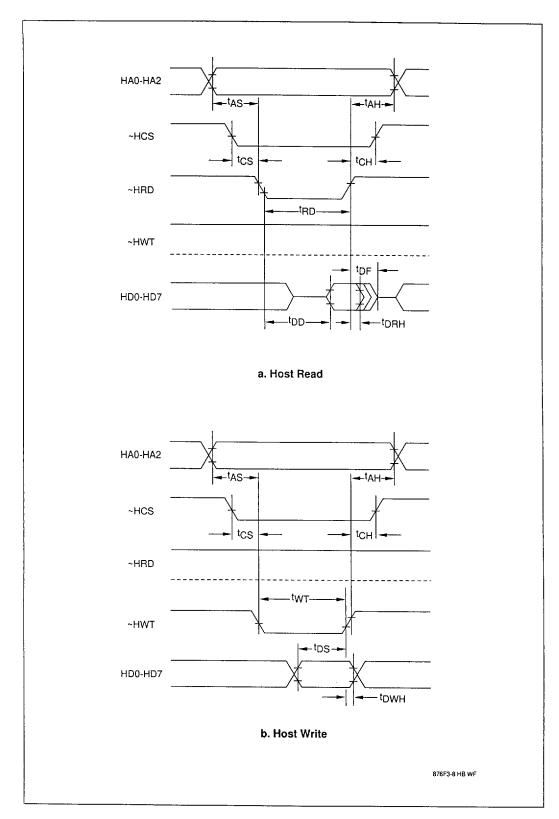

A 16550A UART-compatible parallel host bus interface is supported. The interface signals are: eight bidirectional data lines (HD0-HD7), three address input lines (HA0-HA2), three control input lines (~HCS, ~HRD, and ~HWT), one status output line (HINT), and a reset input line (-RESET).

#### Serial DTE Interface and Indicator Outputs

A V.24/EIA/TIA-232-E logic-compatible DTE serial interface is provided in the serial interface version. One serial transmit data input line (~TXD), one serial receive data output line (~RXD), four control input lines (~DTR, ~RTS, ~RDL, and ~AL), and six status output lines (~CTS, ~DSR, ~RLSD, ~TM, ~RI, and ~DRSOUT) are supported.

Three dedicated indicator output lines (~DTRIND, ~TMIND, and ~AAIND) are also provided.

#### **NVRAM** Interface

A two-line serial interface to an optional OEM-supplied non-volatile RAM (NVRAM) is provided. The interface signals are a bidirectional data line (NVMDATA) and a clock output line (NVMCLK). Data stored in NVRAM can take precedence over the factory default settings. A 256-byte NVRAM can store up to two user-selectable configurations and can store up to four 35-digit dial strings.

#### **External RAM and ROM Interface**

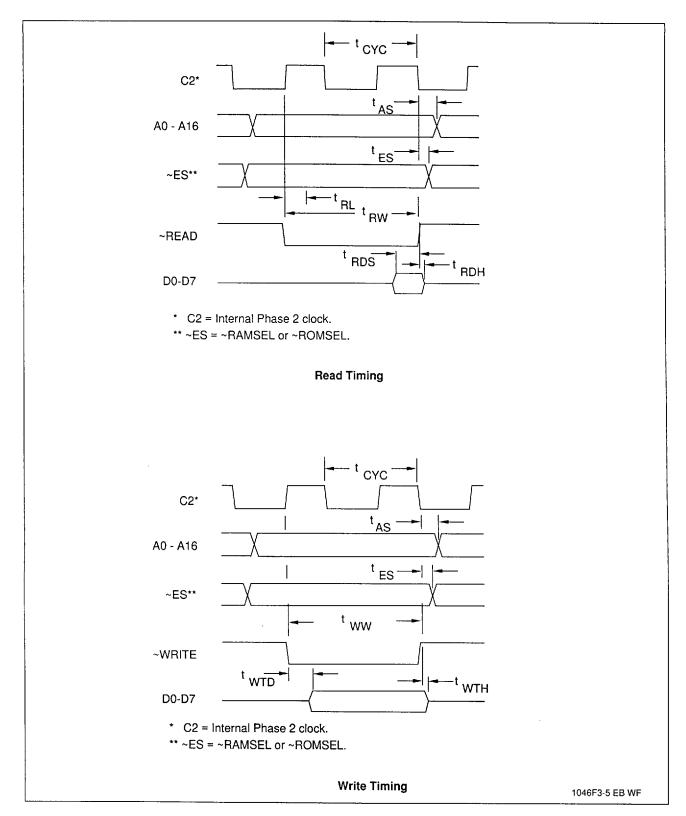

The modem external bus connects to OEM-supplied 128-kbyte ROM and 32-kbyte RAM. This non-multiplexed external bus supports eight bidirectional data lines (D0-D7), 17 address output lines (A0-A16), two read/write control output lines (~READ and ~WRITE), and two chip select output lines (~ROMSEL and ~RAMSEL).

External ROM and RAM access time must be 45 ns or faster.

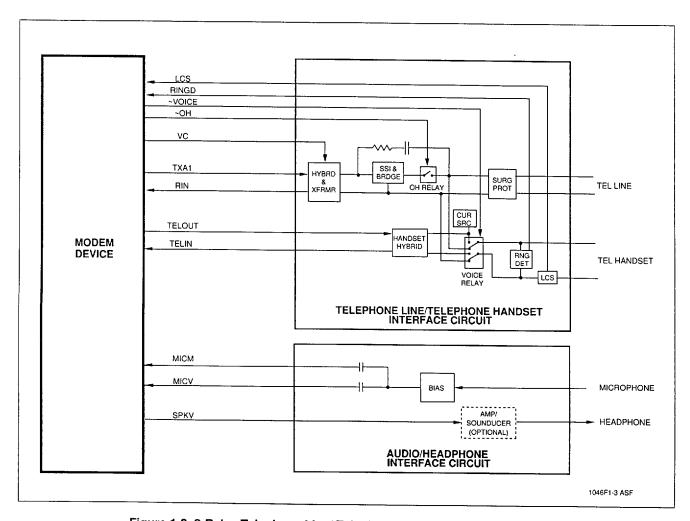

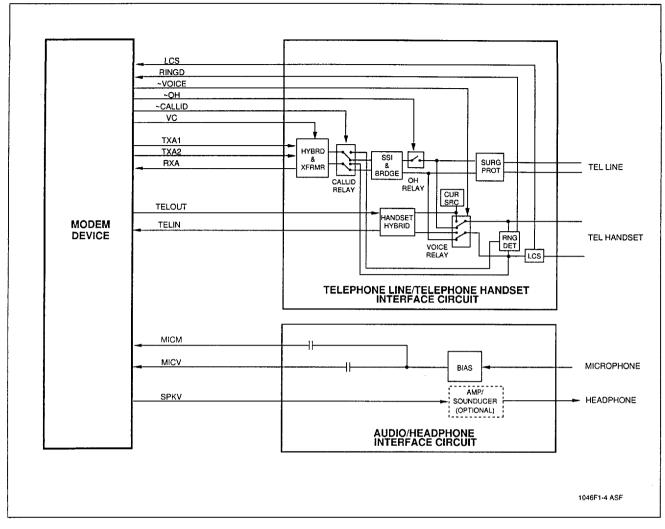

#### Telephone Line/Telephone/Audio Interface

The Telephone Line/Telephone/Audio Signal Interface can support either a 2-relay telephone line interface without Caller ID relay (Figure 1-3) or a 3-relay telephone line interface using a Caller ID relay (Figure 1-4). In either case, the Caller ID function is supported.

Receive/Transmit Data. A receive analog input (RIN) and a transmit analog output (TXA1) are supported.

Relay Controls. Relay control outputs to the line interface are supported:

- Off-hook (~RLY1)

- Caller ID (~CALLID) (The 2 relay design shown in Figure 1-3 supports the Caller ID function without using the ~CALLID relay control output.)

- Voice (~VOICE)

- Mute (~MUTE) (Enabled by ConfigurACE II.)

Signal routing for Voice mode is shown in Table 1-2.

Relay positions for VoiceView are shown in Table 1-3.

Ring Detect. A ring detect (RINGD) input is supported.

Loop Current Sense. A loop current sense (LCS) input is supported.

1-6 1046

Microphone Input and Speakerphone Output. Two microphone inputs are supported: one for voice input (MICV) and one for sound input (MICM), e.g., music-on-hold.

The MICV and SPKV lines connect to the handset and speaker to support functions such as AudioSpan headset and speakerphone modes, FDSP, telephone emulation, microphone voice record, speaker voice playback, and call progress monitor.

The MICM input can accept an external audio signal to support the music-on-hold function (selected by the #VLS=7 command) and routes it to the telephone line. In this case, the modem can be configured using ConfigurACE II to either bandlimit the signal to satisfy FCC part 68 requirements or allow DTMF detection during the music-on-hold function. If music-on-hold function is not required, the microphone signal can be connected to the MICM input to support telephone emulation mode (selected by the #VLS=5 command).

The speaker output (SPKV) carries the normal speakerphone audio or reflects the received analog signals in the modem.

**Telephone Input and Telephone Output.** An input from the telephone microphone (TELIN) and an output to the telephone speaker (TELOUT) are supported in AudioSpan modes. These lines connect voice record/playback and AudioSpan audio to the local handset.

Figure 1-3. 2-Relay Telephone Line/ Telephone/Audio Signal Interface (U.S.)

Figure 1-4. 3-Relay Telephone Line/ Telephone/Audio Signal Interface (U.S.)

Table 1-2. Signal Routing - Voice Mode (#CLS=8)

|       |                                                                          | 2-Relay D      | AA              |                                              |                                         |                                       |  |

|-------|--------------------------------------------------------------------------|----------------|-----------------|----------------------------------------------|-----------------------------------------|---------------------------------------|--|

| #VLS= | Mode Function                                                            | Input Selected | Output Selected | Off-Hook Re<br>(~OH)<br>Activated            | (-                                      | ice Relay<br>VOICE)<br>ctivated       |  |

| 0     | Modem with modem speaker output disabled                                 | RXA            | TXA             | Yes                                          |                                         | No                                    |  |

| 1     | Record from or playback to handset                                       | TELIN          | TELOUT          | No                                           |                                         | Yes                                   |  |

| 2     | Playback to modem speaker                                                | RXA            | TXA and SPKV    | No                                           |                                         | No                                    |  |

| 3     | Microphone input for local recording                                     | MICV           | TXA             | No                                           |                                         | Yes                                   |  |

| 4     | Modem with modem speaker output enabled                                  | RXA            | TXA and SPKV    | Yes                                          |                                         | No                                    |  |

| 5     | Reserved                                                                 |                |                 |                                              |                                         |                                       |  |

| 6     | Use speakerphone after dialing or answering                              | RXA and MICV   | TXA and SPKV    | Yes                                          |                                         | No                                    |  |

| 7     | Mute local handset; sound chips output to telephone line (music on hold) | MICM           | TXA and SPKV    | No <sup>1</sup>                              |                                         | Yes                                   |  |

| 8     | Record conversation through sound chips                                  | RXA            | SPKV            | No <sup>1</sup>                              | No                                      |                                       |  |

| 9     | Record/playback from local handset through sound chips                   | TELIN and MICV | TELOUT and SPKV | No                                           |                                         | Yes                                   |  |

|       |                                                                          | 3-Relay D      | AA              |                                              |                                         |                                       |  |

| #VLS= | Mode Function                                                            | Input Selected | Output Selected | Caller ID<br>Relay<br>(~CALLID)<br>Activated | Off-Hook<br>Relay<br>(~OH)<br>Activated | Voice<br>Relay<br>(~VOICE<br>Activate |  |

| 0     | Modem with modem speaker output disabled                                 | RXA            | TXA             | No                                           | Yes                                     | No                                    |  |

| 1     | Record from or playback to handset                                       | TELIN          | TELOUT          | Yes                                          | No                                      | Yes                                   |  |

| 2     | Playback to modem speaker                                                | RXA            | TXA and SPKV    | Yes                                          | No                                      | No                                    |  |

| 3     | Microphone input for local recording                                     | MICV           | TXA             | Yes                                          | No                                      | Yes                                   |  |

| 4     | Modem with modern speaker output enabled                                 | RXA            | TXA and SPKV    | No                                           | Yes                                     | No                                    |  |

| 5     | Reserved                                                                 |                |                 |                                              |                                         |                                       |  |

| 6     | Use speakerphone after dialing or answering                              | RXA and MICV   | TXA and SPKV    | No                                           | Yes                                     | No                                    |  |

| 7     | Mute local handset; sound chips output to telephone line (music on hold) | MICM           | TXA and SPKV    | No                                           | No No1                                  |                                       |  |

| 8     | Record conversation through sound chips                                  | RXA            | SPKV            | Yes                                          | No <sup>1</sup>                         | No                                    |  |

| 9     | Record/playback from local handset through sound chips                   | RXA and MICM   | TELOUT and SPKV | Yes                                          | No                                      | Yes                                   |  |

## NOTES:

<sup>1.</sup> The offhook relay should be previously activated, e.g., by an ATA or ATD command.

<sup>2.</sup> SPKV = SPKV output enabled.

Table 1-3. Relay Positions - VoiceView Mode (+FCLASS=80)

| 2-Relay DAA |                                                       |                                |                                |  |  |  |

|-------------|-------------------------------------------------------|--------------------------------|--------------------------------|--|--|--|

|             |                                                       | Off-Hook Relay (~OH) Activated | Voice Relay (~VOICE) Activated |  |  |  |

| Stage       | Function                                              |                                |                                |  |  |  |

| 1           | On-hook                                               | No                             | No                             |  |  |  |

| 2a          | Detected tone - on-hook                               | No .                           | No                             |  |  |  |

| 2b          | Detected tone - off-hook for handset and speakerphone | Yes                            | No                             |  |  |  |

| 3           | Off-hook                                              | Yes                            | Yes                            |  |  |  |

## 3-Relay DAA

| Stage | Function                                              | Caller ID Relay<br>(~CALLID)<br>Activated | Off-Hook Relay<br>(~OH)<br>Activated | Voice Relay<br>(~VOICE)<br>Activated |

|-------|-------------------------------------------------------|-------------------------------------------|--------------------------------------|--------------------------------------|

| 1     | On-hook                                               | No                                        | No                                   | No                                   |

| 2a    | Detected tone - on-hook                               | Yes                                       | No                                   | No                                   |

| 2b    | Detected tone - off-hook for handset and speakerphone | Yes                                       | Yes                                  | No                                   |

| 3     | Off-hook                                              | No                                        | Yes                                  | Yes                                  |

#### 1.3.7 Commands

The modem supports data modem, fax class 1 modem, voice/audio, full-duplex speakerphone (FDSP), MNP 10/MNP 10EC, and VoiceView commands, and S Registers in accordance with modem model options (see Section 7).

**Data Modem Operation.** Data modem functions operate in response to the AT commands when +FCLASS=0. Default parameters support US/Canada operation.

MNP 10 Operation. MNP 10 functions operate in response to MNP 10 commands.

MNP 10EC Operation. MNP 10EC is enabled by the -SEC=1 command.

AutoSync Operation. AutoSync operates in response to the &Q4 command.

Fax Modem Operation. Facsimile functions operate in response to fax class 1 commands when +FCLASS=1 or #CLS=1.

Voice Operation. Voice mode functions operate in response to voice/audio commands when #CLS=8, #VSR=7200 [default], and either #VBS=2 or #VBS=4 is selected.

**Audio Operation.** Audio mode functions operate in response to voice/audio commands when #CLS=8, #VSR=7200 [default] or #VSR=11025, and #VBS=8 is selected.

**Speakerphone Operation.** FDSP functions operate in response to speakerphone commands when #CLS=8 and #VLS=6 is selected.

World Class (W-Class) Operation. Models supporting W-class functions operate in response to W-class AT commands.

VoiceView Operation. VoiceView functions operate in response to VoiceView commands when +FCLASS=80.

#### 1.3.8 ConfigurACE II for Windows Utility Program

The PC-based ConfigurACE II for Windows utility program allows the OEM to customize the modem firmware to suit specific application and country requirements. ConfigurACE II for Windows allows programming of functions such as:

- · Loading of multiple sets of country parameters

- · Loading of NVRAM factory profiles

- · Call progress and blacklisting parameters

- Entry of S register maximum/minimum values

- · Limitation of transmit levels

- · Modification of factory default values

- Customization of the ATI4 response

- · Customization of fax OEM messages

This program modifies the hex object code which can be programmed directly into the system EPROM. Lists of the generated parameters can be displayed or printed.

Rockwell-provided country parameter files allow a complete set of country-specific call progress and blacklisting parameters to be selected.

Refer to the ConfigurACE II for Windows software for a detailed description of capabilities and the operating procedure.

#### 2. TECHNICAL SPECIFICATIONS

#### 2.1 SERIAL DTE INTERFACE OPERATION

#### 2.1.1 Automatic Speed/Format Sensing

Command Mode and Data Modem Mode. The modem can automatically determine the speed and format of the data sent from the DTE. The modem can sense speeds of 300, 600, 1200, 2400, 4800, 7200, 9600, 12000, 14400, 19200, 38400, and 57600 bps (RC144), or 300, 600, 1200, 2400, 4800, 7200, 9600, 12000, 14400, 16800, 19200, 21600, 24000, 26400, 28800, 38400, 57600, and 115200 bps (RC336), and the following data formats:

| Parity | Data Length<br>(No. of Bits) | No. of<br>Stop Bits | Character<br>Length<br>(No. of Bits) |

|--------|------------------------------|---------------------|--------------------------------------|

| None   | 7                            | 2                   | 10                                   |

| Odd    | 7                            | 1                   | 10                                   |

| Even   | 7                            | 1                   | 10                                   |

| None   | 8                            | 1                   | 10                                   |

| Odd    | 8                            | 1                   | 11*                                  |

| Even   | 8                            | 1                   | 11*                                  |

<sup>\* 11-</sup>bit characters are sensed, but the parity bits are stripped off during data transmission in Normal and Error Correction modes.

The modem can speed sense data with mark or space parity and configures itself as follows:

| DTE Configuration | Modem Configuration |

|-------------------|---------------------|

| 7 mark            | 7 none              |

| 7 space           | 8 none              |

| 8 mark            | 8 none              |

| 8 space           | 8 even              |

Fax Modem Mode. The DTE to modem data rate is 19200 bps.

#### 2.2 PARALLEL HOST BUS INTERFACE OPERATION

**Command Mode and Data Modem Mode.** The modem can operate at rates up to 57600 bps (RC144) or 115200 (RC336) by programming the Divisor Latch in the parallel interface registers.

Fax Modem Mode. The host to modem data rate is 19200 bps.

#### 2.3 ESTABLISHING DATA MODEM CONNECTIONS

#### **Telephone Number Directory**

The modem supports four telephone number entries in a directory that can be saved in a serial NVRAM. Each telephone number can be up to 35 characters in length. A telephone number can be saved using the &Zn=x command, and a saved telephone number can be dialed using the DS=n command.

#### Dialing

**DTMF Dialing.** DTMF dialing using DTMF tone pairs is supported in accordance with ITU-T Q.23. The transmit tone level complies with Bell Publication 47001.

Pulse Dialing. Pulse dialing is supported in accordance with EIA/TIA-496-A.

Blind Dialing. The modem can blind dial in the absence of a dial tone if enabled by the X0, X1, or X3 command.

#### Modem Handshaking Protocol

If a tone is not detected within the time specified in the S7 register after the last digit is dialed, the modem aborts the call attempt.

#### **Call Progress Tone Detection**

Ringback, equipment busy, and progress tones can be detected in accordance with the applicable standard.

#### **Answer Tone Detection**

Answer tone can be detected over the frequency range of 2100 ± 40 Hz in ITU-T modes and 2225 ± 40 Hz in Bell modes.

#### **Ring Detection**

A ring signal can be detected from a TTL-compatible 15.3 Hz to 68 Hz square wave input.

#### **Billing Protection**

When the modem goes off-hook to answer an incoming call, both transmission and reception of data are prevented for 2 seconds (data modem) or 4 seconds (fax adaptive answer) to allow transmission of the billing signal.

#### **Connection Speeds**

The modem functions as a data modem when the +FCLASS=0 or #CLS=0 command is active.

Line connection can be selected using the +MS command in accordance with the draft PN-3320 standard presented to the TR30-4 committee (which is a candidate for the definition of V.25 ter at the ITU). The +MS command selects modulation, enables/disables automode, and selects minimum and maximum line speeds (Table 2-1).

ATNn and S37=n commands are supported up to V.32 bis speeds (Table 2-2).

For RC144, the F command is also supported (Table 2-2).

#### **Automode**

Automode detection can be enabled by the +MS command to allow the modem to connect to a remote modem in accordance with draft PN-3320 for V.34 (Table 2-1).

Alternatively, N1 commands allow the modem to connect to a remote modem in accordance with EIA/TIA-PN2330 for V.32 bis speeds and lower (Table 2-2).

#### 2.4 DATA MODE

Data mode exists when a telephone line connection has been established between modems and all handshaking has been completed.

#### Speed Buffering (Normal Mode)

Speed buffering allows a DTE to send data to, and receive data from, a modem at a speed different than the line speed. The modem supports speed buffering at all line speeds.

#### Flow Control

**DTE-to-Modem Flow Control.** If the modem-to-line speed is less than the DTE-to-modem speed, the modem supports XOFF/XON or RTS/CTS flow control with the DTE to ensure data integrity.

#### **Escape Sequence Detection**

The "+++" escape sequence can be used to return control to the command mode from the data mode. Escape sequence detection is disabled by an S2 Register value greater than 127.

#### **BREAK Detection**

The modem can detect a BREAK signal from either the DTE or the remote modem. The \Kn command determines the modem response to a received BREAK signal.

#### **Telephone Line Monitoring**

**GSTN Cleardown (V.34, V.32 bis, V.32).** Upon receiving GSTN Cleardown from the remote modem in a non-error correcting mode, the modem cleanly terminates the call.

Loss of Carrier (V.22 bis and Below). If carrier is lost for a time greater than specified by the S10 register, the modem disconnects (except MNP 10).

Receive Space Disconnect (V.22 bis and Below). If selected by the Y1 command in non-error-correction mode, the modem disconnects after receiving 1.6 ± 10% seconds of continuous SPACE.

Table 2-1. +MS Command Automode Connectivity

| <mod> Modulation</mod> |          | Possible Rates (bps) <sup>1</sup>                                                         | Notes            |  |

|------------------------|----------|-------------------------------------------------------------------------------------------|------------------|--|

| 0                      | V.21     | 300                                                                                       |                  |  |

| 1                      | V.22     | 1200                                                                                      |                  |  |

| 2                      | V.22 bis | 2400 or 1200                                                                              |                  |  |

| 3                      | V.23     | 1200                                                                                      | See Note 2       |  |

| 9                      | V.32     | 9600 or 4800                                                                              |                  |  |

| 10                     | V.32 bis | 14400, 12000, 9600, 7200, or 4800                                                         | Default          |  |

| 11                     | V.34     | 33600, 31200, 28800, 26400, 24000, 21600, 19200, 16800, 14400, 12000, 9600, 7200, or 4800 | RCV336ACF family |  |

| 64                     | Bell 103 | 300                                                                                       |                  |  |

| 69                     | Bell 212 | 1200                                                                                      |                  |  |

#### Notes:

- 1. See optional <automode>, <min\_rate>, and <max\_rate> subparameters for the +MS command.

- 2. For V.23, originating modes transmit at 75 bps and receive at 1200 bps; answering modes transmit at 1200 bps and receive at 75 bps. The rate is always specified as 1200 bps.

- 3. If the DTE speed is set to less than the maximum supported DCE speed in automode, the maximum connection speed is limited to the DTE speed.

Table 2-2. Command Connections

| ATF Setting 1,2 | ATN Setting <sup>1,2</sup> | S37 Setting | ATB Setting | Speed Sensed | Connection         |

|-----------------|----------------------------|-------------|-------------|--------------|--------------------|

| Note 3          | 0                          | 0           | 0           | 300          | V.21               |

| Note 3          | 0                          | 0           | 0           | 1200         | V.22 1200          |

| Note 3          | 0                          | 0           | Х           | 2400         | V.22 bis 2400      |

| Note 3          | 0                          | 0           | X           | 4800         | V.32 bis/V.32 4800 |

| Note 3          | 0                          | 0           | Х           | 7200         | V.32 bis 7200      |

| Note 3          | 0                          | 0           | Х           | 9600         | V.32 bis/V.32 9600 |

| Note 3          | 0                          | 0           | Х           | 12000        | V.32 bis 12000     |

| Note 3          | 0                          | 0           | Х           | Higher       | V.32 bis 14400     |

| Note 3          | 0                          | 0           | 1           | 300          | Bell 103           |

| Note 3          | 0                          | 0           | 1           | 1200         | Beil 212A          |

| ATF1            | 0                          | 1-3         | 0           | X            | V.21               |

| ATF4            | 0                          | 5           | 0           | X            | V.22 1200          |

| ATF5            | 0                          | 6           | X           | X            | V.22 bis 2400      |

| ATF1            | 0                          | 1-3         | 1           | X            | Bell 103           |

| ATF4            | 0                          | 5           | 1           | X            | Bell 212A          |

| ATF3            | 0                          | · 7         | X           | X            | V.23               |

| ATF6            | 0                          | 8           | Х           | X            | V.32 bis/V.32 4800 |

| ATF8            | 0                          | 9           | X           | X            | V.32 bis/V.32 9600 |

| ATF7            | 0                          | 12          | Х           | X            | V.32 bis 7200      |

| ATF9            | 0                          | 10          | Х           | X            | V.32 bis 12000     |

| ATF10           | 0                          | 11          | Х           | X            | V.32 bis 14400     |

| ATF0            | 1                          | X           | X           | X            | Automode           |

#### Notes:

- 1. ATFn can be used in lieu of ATN0 and S37. ATFn (where n = valid number) sets ATN0 and S37 to the corresponding value.

- 2. ATF0 forces ATN1 and S37=0.

- 3. The connection speed is determined by DTE speed sensing (serial interface only). A subsequent ATFn command supersedes the ATN and S37 settings.

#### Send SPACE on Disconnect (V.22 bis and Below)

If selected by the Y1 command in non-error-correction mode, the modem sends  $4 \pm 10\%$  seconds of continuous SPACE when a locally commanded hang-up is issued by the &Dn or H command.

#### 2.4.2 Fall Forward/Fallback (V.34/V.32 bis/V.32)

During initial handshake, the modem will fallback to the optimal line connection within V.34/V.32 bis/V.32 mode depending upon signal quality if automode is enabled by the +MS or N1 command.

When connected in V.34/V.32 bis/V.32 mode, the modem will fall forward or fallback to the optimal line speed within the current modulation depending upon signal quality if fall forward/fallback is enabled by the %E2 command.

#### Retrain

The modern may lose synchronization with the received line signal under poor line conditions. If this occurs, retraining may be initiated to attempt recovery depending on the type of connection.

The modem initiates a retrain if line quality becomes unacceptable if enabled by the %E command. The modem continues to retrain until an acceptable connection is achieved, or until 30 seconds elapse resulting in line disconnect.

#### **Programmable Inactivity Timer**

The modem disconnects from the line if data is not sent or received for a specified length of time. In normal or error-correction mode, this inactivity timer is reset when data is received from either the DTE or from the line. This timer can be set to a value between 0 and 2550 seconds by using register S30. A value of 0 disables the inactivity timer.

#### DTE Signal Monitoring (Serial DTE Interface Only)

- ~DTR. When ~DTR is asserted, the modern responds in accordance with the &Dn and &Qn commands.

- ~RTS. ~RTS is used for flow control if enabled by the &K command in normal or error-correction mode.

- ~RDL. When ~RDL is asserted, the modem requests a remote digital loop if connected in non-error-correction mode.

- ~AL. When ~AL is asserted, the modern disconnects and enters analog loop.

#### 2.5 ERROR CORRECTION AND DATA COMPRESSION

#### **V.42 Error Correction**

V.42 supports two methods of error correction: LAPM and, as a fallback, MNP 4. The modem provides a detection and negotiation technique for determining and establishing the best method of error correction between two modems.

#### **MNP 2-4 Error Correction**

MNP 2-4 is a data link protocol that uses error correction algorithms to ensure data integrity. Supporting stream mode, the modem sends data frames in varying lengths depending on the amount of time between characters coming from the DTE.

#### V.42 bis Data Compression

V.42 bis data compression mode, enabled by the %Cn command or S46 register, operates when a LAPM or MNP 10 connection is established.

The V.42 bis data compression employs a "string learning" algorithm in which a string of characters from the DTE is encoded as a fixed length codeword. Two 2k-byte dictionaries are used to store the strings. These dictionaries are dynamically updated during normal operation.

#### **MNP 5 Data Compression**

MNP 5 data compression mode, enabled by the %Cn command, operates during an MNP connection.

In MNP 5, the modem increases its throughput by compressing data into tokens before transmitting it to the remote modem, and by decompressing encoded received data before sending it to the DTE.

#### 2.6 MNP 10 DATA THROUGHPUT ENHANCEMENT

MNP 10 protocol and MNP Extended Services enhance performance under adverse channel conditions such as those found in rural, long distance, or cellular environments. An MNP 10 connection is established when an MNP 2-4 connection is negotiated with a remote modem supporting MNP 10.

MNP Extended Services. The modem can quickly switch to MNP 10 operation when the remote modem supports MNP 10 and both modems are configured to operate in V.42.

V.42 bis/MNP 5 Support. V.42 bis/MNP 10 can operate with V.42 bis or MNP 5 data compression.

#### 2.7 MNP 10EC™ ENHANCED CELLULAR CONNECTION

A traditional landline modem, when used for high-speed cellular data transmission, typically encounters frequent signal interference and degradation in the connection due to the characteristics of the analog cellular network. In this case, cellular specific network impairments, such as non-linear distortion, fading, hand-offs, and high signal-to-noise ratio, contribute to an unreliable connection and lower data transfer performance. Implementations relying solely on protocol layer methods, such as MNP 10, generally cannot compensate for the landline modem's degraded cellular channel performance.

The modem achieves higher cellular performance by implementing enhanced cellular connection techniques at both the physical and protocol layers, depending on modem model. The modem enhances the physical layer within the modulation by optimizing its responses to sudden changes in the cellular connection. The MNP 10EC protocol layer implemented in the modem firmware improves data error identification/correction and maximizes data throughput by dynamically adjusting speed and packet size based on signal quality and data error performance.

#### 2.8 AUTOSYNC

Hayes AutoSync mode, when used with communications software incorporating the Hayes Synchronous Interface (HSI), provides synchronous communication capabilities from an asynchronous data terminal. In AutoSync, the modem places the call asynchronously then automatically switches to synchronous operation once the telephone connection has been established. AutoSync allows communication from an asynchronous DTE (typically a personal computer) to synchronous DTE (typically a mainframe computer or minicomputer).

#### 2.9 FAX CLASS 1 OPERATION

Facsimile functions operate in response to fax class 1 commands when +FCLASS=1 or #CLS=1.

In the fax mode, the on-line behavior of the modem is different from the data (non-fax) mode. After dialing, modem operation is controlled by fax commands. Some AT commands are still valid but may operate differently than in data modem mode.

Calling tone is generated in accordance with T.30.

#### 2.10 VOICE/AUDIO MODE

Voice and audio functions are supported by the Voice Mode. Voice Mode includes three submodes: Online Voice Command Mode, Voice Receive Mode, and Voice Transmit Mode.

## 2.10.1 Online Voice Command Mode

This mode results from the connection to the telephone line or a voice/audio I/O device (e.g., microphone, speaker, or handset) through the use of the #CLS=8 and #VLS commands. After mode entry, AT commands can be entered without aborting the connection.

#### 2.10.2 Voice Receive Mode

This mode is entered when the #VRX command is active in order to record voice or audio data input at the RXA pin, typically from a microphone/handset or the telephone line.

Received analog voice samples are converted to digital form and compressed for reading by the host. AT commands control the codec bits-per-sample rate.

Received analog mono audio samples are converted to digital form and formatted into 8-bit unsigned linear PCM format for reading by the host. AT commands control the bit length and sampling rate. Concurrent DTMF/tone detection is available at the 7200 Hz sample rate.

#### 2.10.3 Voice Transmit Mode

This mode is entered when the #VTX command is active in order to playback voice or audio data to the TXA1 output, typically to a speaker/handset or to the telephone line.

Digitized voice data is decompressed and converted to analog form at the original compression quantization sample-per-bits rate then output to the TXA1 output.

Digitized audio data is converted to analog form then output to the TXA1 output.

#### 2.10.4 Audio Mode

The audio mode enables the host to transmit and receive 8-bit audio signals. In this mode, the modem directly accesses the internal analog-to-digital (A/D) converter (ADC) and the digital-to-analog (D/A) converter (DAC). Incoming analog audio signals can then be converted to digital format and digital signals can be converted to analog audio output.

#### 2.10.5 Tone Detectors

The tone detector signal path is separate from the main received signal path thus enabling tone detection to be independent of the configuration status. In Tone Mode, all three tone detectors are operational.

#### 2.10.6 Speakerphone Modes

Speakerphone modes are selected in voice mode with the following #VLS= commands:

**Use Speakerphone After Dialing or Answering (#VLS=6).** #VLS=6 selects speakerphone mode while in #CLS=8 mode. Speakerphone operation is entered during Voice Online Command mode after completing dialing or answering.

Speakerphone Settings (#SPK = Parameters). The #SPK command can be used to control the microphone state (mute or on), adjust the speaker volume, and microphone gain. The #SPK parameters are valid only after the modem has entered the Voice Online mode while in the #VLS=6 setting. The command syntax is:

#SPK=<mute>,<spkr>,<mic> (See the AT Command Reference Manual for exact syntax.)

<mute> = Mute Mode Select (Range = 0-2)

0 = microphone mute

1 = microphone on (default)

2 = Room Monitor mode (microphone gain is maximum and speaker output is off)

<spkr> = Speaker Output Level Attenuation

Range = 0 to 15 (in 2 dB steps)

Default = 10 (20 dB)

Speaker mute = 16

<mic>= Microphone Gain Value (Range = 0-3)

0 = 0 dB gain

1 = 10 dB gain

2 = 15 dB gain (default)

3 = 20 dB gain

Room Monitor Feature. The Room Monitor function allows an application where a remote caller calls the computer to monitor sound in a room. For example, the #SPK=2,,, command selects a listen only mode where the microphone gain is set to maximum and the speaker output is off.

#### 2.10.7 Sound Card Support Modes

Sound card support modes are selected in voice mode with the following #VLS= commands:

Mute Handset; Route Sound Chips Output To Line (#VLS=7). #VLS=7 mutes the local handset and routes the sound chip output (such as music or messages during telephone hold) by switching the handset out of the telephone line path if in #VLS=0 or #VLS=4 mode (valid after the modem is offhook, e.g., from an ATA or ATD command).

Record Conversation through Sound Chips (#VLS=8). #VLS=8 engages the Caller ID relay to allow recording of conversation through sound chips (valid after the modem is offhook, e.g., from an ATA or ATD command).

Recording/Playback from Local Handset through Sound Chips (#VLS=9). #VLS=9 routes the handset lines to the sound chips to allow recording/playback of audio through the local handset.

#### 2.11 SIMULTANEOUS AUDIO/VOICE AND DATA (AUDIOSPAN)

The modem can operate in AudioSpan Mode if the remote modem is also configured for AudioSpan Mode operation.

AT commands are used to select the AudioSpan Mode (-SMS command), to enable automatic AudioSpan modulation selection or select a specific AudioSpan modulation (-SQS command), and to enable AudioSpan data burst operation (-SMC command).

ML288 Modulation. ML288 (V.34 type) modulation supports 4.8 to 14.4 kbps data speeds with audio where the lower data rates provide higher audio quality. The ML288 data speed with audio is six data speeds below the capability supported by telephone line quality (up to 28800 bps). For example, a connection that can support V.34 28800 bps data speed will cause a resulting AudioSpan ML288 data-only speed to be 28800 bps and the data speed with audio to be 14400 bps. A ML288 data speed with audio will upshift to its corresponding higher data-only speed when the handset is placed on-hook.

**ML144 Modulation.** ML144 (V.32 bis) modulation supports 4.8 to 9.6 kbps data speeds with audio where the lower data rates provide higher audio quality. The **ML144** data speed plus audio is at least two data speeds below the capability supported by telephone line quality. For example, a connection that can support V.32 bis 14400 bps data speed will cause a resulting AudioSpan data speed with audio to be between V.61/4800 and ML144/9600. A ML144 data speed with audio will upshift to higher data-only speed when no audio/voice is detected.

V.61 Modulation. V.61 modulation supports 4800 bps data speed with audio, and a data-only speed of 4800 bps.

#### 2.11.1 Supported Data Speeds

Table 2-3 lists the data speed when the handset is on-hook (ML288) or audio is not present (ML144), and the data speed when audio is present, based upon the selected AudioSpan modulation.

| AudioSpan<br>Modulation | Data Speed (bps) [When the Handset is On-hook (ML288) or Audio is Not Present (ML144)] | Data Speed (bps) with Audio<br>[When Audio is Present] |  |

|-------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------|--|

| ML288                   | 28800 (Note 2)                                                                         | 14400 (Note 2)                                         |  |

| ML288                   | 26400                                                                                  | 12000 (Note 2)                                         |  |

| ML288                   | 24000                                                                                  | 9600 (Note 2)                                          |  |

| ML288                   | 21600                                                                                  | 7200 (Note 2)                                          |  |

| ML288                   | 19200 to 4800                                                                          | 4800 (Note 2)                                          |  |

| ML144                   | 14400                                                                                  | 9600, 7200, or 4800                                    |  |

| ML144                   | 12000                                                                                  | 7200 or 4800                                           |  |

| ML144                   | 9600 to 4800                                                                           | 4800                                                   |  |

| V.61                    | 4800                                                                                   | 4800                                                   |  |

Table 2-3. AudioSpan Data Speeds

#### Notes

- 1. Applicable when the handset is on-hook (#VLS=0) or during headset operation (AT#VLS=5) or speakerphone operation (#VLS=6).

- 2. 28800 bps is the highest ML288 data-only speed supported.

#### 2.11.2 AudioSpan Mode Selection

AudioSpan Mode is selected with the -SMS=2 (AudioSpan Mode) or the -SMS=3 (Automatic DSVD/AudioSpan/Data Only Mode Select) command. The local modem should be set to the AudioSpan Mode (-SMS=2) when sending, and to the AudioSpan Mode (-SMS=2) or Automatic DSVD/AudioSpan/Data Only Mode Select (-SMS=3) when receiving. The -SMS command definition is:

## -SMS = x, y, z, t (Select AudioSpan/DSVD/Data Mode)

The x parameter selects Data, AudioSpan, or DSVD Mode, or enables automatic mode selection. The y, z, and t parameters are optional and are required only if the user wishes to control connection speeds. For example, AT-SMS=2 selects AudioSpan Mode.

x: Data/AudioSpan/DSVD mode select and automatic mode select enable

0 = Data Mode

(Default) (data-only mode, AudioSpan and DSVD are disabled)

1 = DSVD mode

(Note: AT-SMS=1 performs the same operation at AT-SSE=1)

2 = AudioSpan mode

3 = Automatic mode select

(Data/DSVD/AudioSpan)

y: Minimum data speed (bps) with audio for AudioSpan Mode (see y value in following table)

z: Maximum data speed (bps) with audio for AudioSpan Mode (see z value in following table)

|              | Modulation Selected (See -SQS Command) |               |               |  |  |  |

|--------------|----------------------------------------|---------------|---------------|--|--|--|

| y or z Value | V.61                                   | ML144         | ML288         |  |  |  |

| 4800         | S ( y and z Default)                   | S (y Default) | S (y Default) |  |  |  |

| 7200         |                                        | S             | S             |  |  |  |

| 9600         | _                                      | S (z Default) | S             |  |  |  |

| 12000        | _                                      | <u> </u>      | S             |  |  |  |

| 14400        | <u> </u>                               | _             | S (z Default) |  |  |  |

t: Symbol rate (ML288 modulation only)

0 = Auto Selection

(Default)

1 - 6 = Reserved

#### Examples

- 1. AT -SMS=2 selects AudioSpan Mode (the y, z, and t parameters are not required).

- 2. AT -SMS=2,4800,9600 selects AudioSpan Mode, specifies the minimum data speed with audio of 4800 bps, and specifies the maximum data speed with audio of 9600 bps.

#### 2.11.3 AudioSpan Modulation Select and Enable/Disable AudioSpan Automatic Modulation Selection

The host can enable the modern to select the optimal modulation or select a specific modulation. The -SQS command definition is:

#### -SQS = x, y (Select AudioSpan Modulation and Enable/Disable AudioSpan Automatic Modulation Selection)

#### x: Select AudioSpan modulation

V.61 0 =

1 = ML144

(Default for RCV144)

ML288 2 =

(Default for RCV336)

#### y: Enable/disable AudioSpan automatic modulation (automodulation) selection

0 =Disable AudioSpan automodulation (Host selects AudioSpan modulation specified by the x parameter.

> If the selected modulation is not supported by the modem. ERROR is reported and the x parameter is not changed. If the remote modem does not support the selected modulation, the modem disconnects.)

1 =

Enable AudioSpan automodulation (Default. The modem starts with the AudioSpan modulation specified by the x parameter and falls back from ML288, to ML144, to V.61, or to data mode (e.g., V.34 or V.32 bis) depending on the selected x parameter, the remote modem capability, and line conditions.)

The AT-SQS parameters should remain at default unless a particular modulation is preferred.

#### Examples

- 1. AT -SQS=2,1 enables AudioSpan automodulation starting with ML288 modulation.

- 2. AT -SQS=2,0 disables AudioSpan automodulation and selects ML288 modulation.

- AT -SQS=1,0 disables AudioSpan automodulation and selects ML144 modulation.

#### 2.11.4 ML144 Data Burst Option

ML144 data burst can be enabled using the -SMC command in ML144 modulation. Data burst will keep the audio channel open only when energy is detected on the handset or headset. When silence is detected in data burst mode, the connected modems will upshift in speed for higher throughput. Disabling data burst mode will keep the audio channel open at all times during the AudioSpan connection. The -SMC command definition is:

#### -SMC = x (Enable/Disable ML144 Data Burst)

0 =Disable data burst

1 = Enable data burst

(Default)

#### 2.11.5 AudioSpan Audio Interface

The AudioSpan audio interface defaults to the local handset connected to the modem (AT#VLS=0) and can be configured to interface through the modem microphone and speaker pins to support use of a headset (AT#VLS=5) or a speakerphone (AT#VLS=6).

## 2.11.6 Audio Quality Considerations.

AudioSpan audio quality is dependent upon modulation mode, data rate and telephone line quality. Some guidelines are:

- Higher quality telephone lines provide better audio quality than impaired telephone lines.

- A lower data speed with audio provides better audio quality than higher data speed with audio. For example, a ML288/9600 connection will be audibly superior to a ML288/14400 connection.

3. For identical data speed with audio using different modulations (e.g., ML144 vs. ML288), the audio quality at ML288 will be superior. For example, a ML288/9600 will be audibly superior to a ML144/9600 connection.

#### 2.12 FULL-DUPLEX SPEAKERPHONE (FDSP) MODE

The modem operates in FDSP mode when #CLS=8 and #VLS=6 (see 2.10.6).

In FDSP Mode, speech from a microphone or handset is converted to digital form, shaped, and output to the telephone line through the line interface circuit. Speech received from the telephone line is shaped, converted to analog form, and output to the speaker or handset. Shaping includes both acoustic and line echo cancellation.

#### 2.13 VOICEVIEW

Voice and data can be alternately sent and received in a time-multiplexed fashion over the telephone line whenever the +FCLASS=80 command is active. This command and other VoiceView commands embedded in host communications software control modem operation. Most VoiceView commands use an extended syntax starting with the characters "-S", which signifies the capability to switch between voice and data.

#### 2.14 CALLER ID

Caller ID can be enabled/disabled using the #CID command. When enabled, caller ID information (date, time, caller code, and name) can be passed to the DTE in formatted or unformatted form. Inquiry support allows the current caller ID mode and mode capabilities of the modem to be retrieved from the modem.

#### 2.15 WORLD CLASS COUNTRY SUPPORT

The W-class models include functions which support modem operation in multiple countries. The following capabilities are provided in addition to the data modem functions previously described. Country dependent parameters are all programmable by ConfigurACE II for Windows.

#### 2.15.1 Dialing

Dial Tone Detection. Dial tone detection levels and frequency ranges are programmable by ConfigurACE II for Windows.

**DTMF Dialing.** Transmit output level, DTMF signal duration, and DTMF interdigit interval parameters are programmable by ConfigurACE II for Windows.

**Pulse Dialing.** Parameters such as make/break times, set/clear times, and dial codes are programmable by ConfigurACE II for Windows.

Ring Detection. The frequency range is programmable by ConfigurACE II for Windows.

Blind Dialing. Blind dialing may be disabled by ConfigurACE II for Windows.

#### 2.15.2 Carrier Transmit Level

The carrier transmit level can be programmed through S91 for data and S92 for fax. The maximum, minimum, and default values can be defined by ConfigurACE II for Windows to match specific country and DAA requirements.

#### 2.15.3 Calling Tone

Calling tone is generated in accordance with V.25. Calling tone may be toggled (enabled/disabled) by inclusion of a "^" character in a dial string. It may also be disabled by programming a country specific parameter using ConfigurACE II for Windows.

#### 2.15.4 Call Progress Tone Detection

Frequency and cadence of tones for busy, ringback, congested, dial tone 1, and dial tone 2 are programmable by ConfigurACE II for Windows.

#### 2.15.5 Answer Tone Detection

The answer tone detection period is programmable by ConfigurACE II for Windows.

#### 2.15.6 Blacklist Parameters

The modem can operate in accordance with requirements of individual countries to prevent misuse of the network by limiting repeated calls to the same number when previous call attempts have failed. Call failure can be detected for reasons such as no dial tone, number busy, no answer, no ringback detected, voice (rather than modem) detected, and key abort (dial attempt aborted by user). Actions resulting from such failures can include specification of minimum inter-call delay, extended delay between calls, and maximum numbers of retries before the number is permanently forbidden ("blacklisted"). Up to 40 such numbers may be tabulated. The blacklist parameters are established by ConfigurACE II for Windows.

#### 2.15.7 Relay Control

On-hook/off-hook, make/break, and set/clear relay control parameters are programmable by ConfigurACE II for Windows.

The NVMDATA line can additionally be assigned as the ~MUTE relay control by ConfigurACE II for Windows.

#### 2.16 DIAGNOSTICS

#### 2.16.1 Commanded Tests

Diagnostics are performed in response to &T commands.

Analog Loopback (&T1 Command). Data from the local DTE is sent to the modem, which loops the data back to the local DTE.

Analog Loopback with Self Test (&T8 Command). An internally generated test pattern of alternating 1s and 0s (reversals) is sent to the modem. An error detector within the modem checks for errors in the string of reversals.

Remote Digital Loopback (RDL) (&T6 Command). Data from the local DTE is sent to the remote modem which loops the data back to the local DTE.

Remote Digital Loopback with Self Test (&T7 Command). An internally generated pattern is sent from the local modem to the remote modem, which loops the data back to the local modem.

**Local Digital Loopback (&T3 Command).** When local digital loop is requested by the local DTE, two data paths are set up in the local modem. Data from the local DTE is looped back to the local DTE (path 1) and data received from the remote modem is looped back to the remote modem (path 2).

#### 2.16.2 Power On Reset Tests

Upon power on, the modem performs tests of the modem, internal RAM, ROM, and NVRAM. If the modem, internal RAM, or ROM test fails, the ~TMIND output is pulsed (serial interface version) or the DCD bit in the parallel interface register is pulsed (parallel interface version) as follows:

Internal RAM test fails: One pulse cycle (pulse cycle = 0.5 sec. on, 0.5 sec. off) every 1.5 seconds.

ROM test fails: Two pulse cycles every 1.5 seconds.

Modem device test fails: Three pulse cycles every 1.5 seconds.

If the NVRAM test fails (due to NVRAM failure or if NVRAM is not installed), the test failure is reported by AT commands that normally use the NVRAM, e.g., the &V command.

#### 3. HARDWARE INTERFACE

#### 3.1 HARDWARE SIGNALS

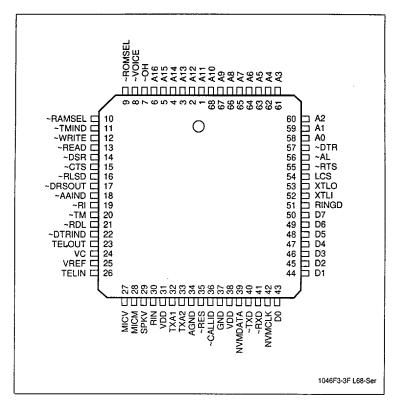

The modem hardware interface signals for the serial DTE interface configuration are shown in Figure 3-1.

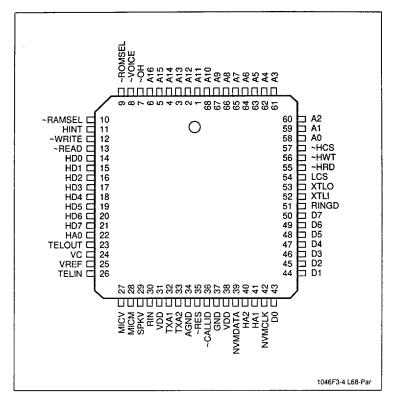

The modern hardware interface signals for the parallel host interface configuration are shown in Figure 3-2.

The modem pin assignments for the 68-pin PLCC with serial DTE interface are shown in Figure 3-3 and are listed in Table 3-1

The modem pin assignments for the 68-pin PLCC with parallel host interface are shown in Figure 3-4 and are listed in Table 3-2.

The modem hardware interface signals are defined in Table 3-3.

The digital electrical characteristics for the hardware interface signals are listed in Table 3-4.

The analog electrical characteristics for the hardware interface signals are listed in Table 3-5.

The current and power requirements are listed in Table 3-6.

The absolute maximum ratings are listed in Table 3-7.

Figure 3-1. Hardware Interface Signals - Serial DTE Interface

Figure 3-2. Hardware Interface Signals - Parallel Host Interface

Figure 3-3. Modem Pin Signals - 68-Pin PLCC - Serial DTE Interface

Table 3-1. Modem Pin Signals - 68-Pin PLCC - Serial DTE Interface

| Pin    | Signal Label | I/O Type | Interface                       | Pin | Signal Label      | I/O Type    | Interface                                   |

|--------|--------------|----------|---------------------------------|-----|-------------------|-------------|---------------------------------------------|

| 1      | A11          | OA       | EB: A11                         | 35  | ~RES              | IC          | HB: (Note 4)                                |

| 2      | A12          | OA       | EB: A12                         | 36  | ~CALLID           | OA          | DAA: ~CALLID                                |

| 3      | A13          | OA       | EB: A13                         | 37  | GND               | GND         | GND                                         |

| 4      | A14          | OA       | EB: A14                         | 38  | VDD               | PWR         | VCC and filter                              |

| 5      | A15          | OA       | EB: A15                         | 39  | NVMDATA/<br>~MUTE | IA/OA<br>OA | NVRAM: SDA (Note 3)/<br>DAA: ~MUTE (Note 5) |

| 6      | A16          | OA       | EB: A16                         | 40  | ~TXD              | IA          | DTE: ~TXD                                   |

| 7      | ~OH          | OA       | DAA: ~OH                        | 41  | ~RXD              | OA          | DTE: ~RXD                                   |

| 8      | ~VOICE       | OA       | DAA: ~VOICE                     | 42  | NVMCLK            | OA          | NVRAM: SCL                                  |

| 9      | ~ROMSEL      | OA       | ROM: ~CE                        | 43  | D0                | IA/OA       | EB: D0                                      |

| 10     | ~RAMSEL      | OA       | RAM: ~CS                        | 44  | D1                | IA/OA       | EB: D1                                      |

| 11     | ~TMIND       | OA       | Indicator Circuit               | 45  | D2                | IA/OA       | EB: D2                                      |

| 12     | ~WRITE       | OA       | EB: ~WRITE                      | 46  | D3                | IA/OA       | EB: D3                                      |

| 13     | ~READ        | OA       | EB: ~READ                       | 47  | D4                | IA/OA       | EB: D4                                      |

| 14     | ~DSR         | ОВ       | DTE: ~DSR                       | 48  | D5                | IA/OA       | EB: D5                                      |

| 15     | ~CTS         | ОВ       | DTE: ~CTS                       | 49  | D6                | IA/OA       | EB: D6                                      |

| 16     | ~RLSD        | ОВ       | DTE: ~RLSD                      | 50  | D7                | IA/OA       | EB: D7                                      |

| 17     | ~DRSOUT      | ОВ       | DTE: ~DRSOUT                    | 51  | RINGD             | IA          | DAA: RINGD                                  |

| 18     | ~AAIND       | OA       | Indicator Circuit               | 52  | XTLI              | IE          | XTLI                                        |

| 19     | ~RI          | ОВ       | DTE: ~RI                        | 53  | XTLO              | OE          | XTLO                                        |

| 20     | ~TM          | ОВ       | DTE: ~TM                        | 54  | LCS               | IA          | DAA: LCS                                    |

| 21     | ~RDL         | IA       | DTE: ~RDL                       | 55  | ~RTS              | IA          | DTE: ~RTS                                   |

| 22     | ~DTRIND      | OA       | Indicator Circuit               | 56  | ~AL               | IA          | DTE: ~AL                                    |

| 23     | TELOUT       | O(DD)    | Telephone Handset<br>Interface  | 57  | ~DTR              | IA          | DTE: ~DTR                                   |

| 24     | VC           | DI       | AGND through capacitors and DAA | 58  | A0                | OA          | EB: A0                                      |

| 25     | VREF         | DI       | VC through capacitors           | 59  | A1                | OA          | EB: A1                                      |

| 26     | TELIN        | I(DA)    | Telephone Handset<br>Interface  | 60  | A2                | OA          | EB: A2                                      |

| 27     | MICV         | I(DA)    | Audio Interface                 | 61  | A3                | OA          | EB: A3                                      |

| 28     | MICM         | I(DA)    | Audio Interface                 | 62  | A4                | OA          | EB: A4                                      |

| 29     | SPKV         | O(DD)    | Audio Interface                 | 63  | A5                | OA          | EB: A5                                      |

| 30     | RIN          | I(DA)    | DAA: RXA                        | 64  | A6                | OA          | EB: A6                                      |

| 31     | VDD          | PWR      | VCC and filter                  | 65  | A7                | OA          | EB: A7                                      |

| 32     | TXA1         | O(DD)    | DAA: TXA1                       | 66  | A8                | OA          | EB: A8                                      |

| 33     | TXA2         | O(DD)    | DAA: TXA2                       | 67  | A9                | OA          | EB: A9                                      |

| 34     | AGND         | GND      | AGND                            | 68  | A10               | OA          | EB: A10                                     |

| Notes: |              |          | 1)                              |     | _\                | 1 0         |                                             |

#### Notes:

I/O types:

DI = Device interconnect.

IA, IC = Digital input; IE = Crystal input (see Table 3-4).

OA, OB, = Digital output; OE = Crystal output (see Table 3-4).

I(DA) = Analog input (see Table 3-5).

O(DD), O(DF) = Analog output (see Table 3-5).

NC = No external connection allowed.

Connect to VCC through 10K ohms.

Connect to GND through 10K ohms.

~MUTE use can be enabled by ConfigurACE II for Windows.

Figure 3-4. Modem Pin Signals- 68-Pin PLCC - Parallel Host Interface

Table 3-2. Modem Pin Signals- 68-Pin PLCC - Parallel Host Interface

| Pin | Signal Label | I/O Type | Interface                       | Pin | Signal Label      | I/O Type    | Interface                                   |

|-----|--------------|----------|---------------------------------|-----|-------------------|-------------|---------------------------------------------|

| 1   | A11          | OA       | EB: A11                         | 35  | ~RES              | IC          | HB: (Note 4)                                |

| 2   | A12          | OA       | EB: A12                         | 36  | ~CALLID           | OA          | DAA: ~CALLID                                |

| 3   | A13          | OA       | EB: A13                         | 37  | GND               | GND         | GND                                         |

| 4   | A14          | OA       | EB: A14                         | 38  | VDD               | PWR         | VCC and filter                              |

| 5   | A15          | OA       | EB: A15                         | 39  | NVMDATA/<br>~MUTE | IA/OA<br>OA | NVRAM: SDA (Note 3)/<br>DAA: ~MUTE (Note 5) |

| 6   | A16          | OA       | EB: A16                         | 40  | HA2               | IA          | HB: HA2                                     |

| 7   | ОН           | OA       | DAA: ~OH                        | 41  | HA1               | IA          | HB: HA1                                     |

| 8   | ~VOICE       | OA       | DAA: ~VOICE                     | 42  | NVMCLK            | OA          | NVRAM: SCL                                  |

| 9   | ~ROMSEL      | OA       | ROM: ~CE                        | 43  | D0                | IA/OA       | EB: D0                                      |

| 10  | ~RAMSEL      | OA       | RAM: ~CS                        | 44  | D1                | IA/OA       | EB: D1                                      |

| 11  | HINT         | OA       | HB: HINT                        | 45  | D2                | IA/OA       | EB: D2                                      |

| 12  | ~WRITE       | OA       | EB: ~WRITE                      | 46  | D3                | IA/OA       | EB: D3                                      |

| 13  | ~READ        | OA       | EB: ~READ                       | 47  | D4                | IA/OA       | EB: D4                                      |

| 14  | HD0          | IA/OB    | HB: HD0                         | 48  | D5                | IA/OA       | EB: D5                                      |

| 15  | HD1          | IA/OB    | HB: HD1                         | 49  | D6                | IA/OA       | EB: D6                                      |

| 16  | HD2          | IA/OB    | HB: HD2                         | 50  | D7                | IA/OA       | EB: D7                                      |

| 17  | HD3          | IA/OB    | HB: HD3                         | 51  | RINGD             | IA          | DAA: RINGD                                  |

| 18  | HD4          | IA/OB    | HB: HD4                         | 52  | XTLI              | IE          | XTLI                                        |

| 19  | HD5          | IA/OB    | HB: HD5                         | 53  | XTLO              | OE          | XTLO                                        |

| 20  | HD6          | IA/OB    | HB: HD6                         | 54  | LCS               | IA          | DAA: LCS                                    |

| 21  | HD7          | IA/OB    | HB: HD7                         | 55  | ~HRD              | IA          | HB: ~RD                                     |

| 22  | HA0          | IA       | HB: HA0                         | 56  | ~HWT              | IA          | HB: ~WT                                     |

| 23  | TELOUT       | O(DD)    | Telephone Handset<br>Interface  | 57  | ~HCS              | IA          | HB: ~CS                                     |

| 24  | VC           | DI       | AGND through capacitors and DAA | 58  | A0                | OA          | EB: A0                                      |

| 25  | VREF         | DI       | VC through capacitors           | 59  | A1                | OA          | EB: A1                                      |

| 26  | TELIN        | I(DA)    | Telephone Handset<br>Interface  | 60  | A2                | OA          | EB: A2                                      |

| 27  | MICV         | I(DA)    | Audio Interface                 | 61  | A3                | OA          | EB: A3                                      |

| 28  | MICM         | I(DA)    | Audio Interface                 | 62  | A4                | OA          | EB: A4                                      |

| 29  | SPKV         | O(DD)    | Audio Interface                 | 63  | A5                | OA          | EB: A5                                      |

| 30  | RIN          | I(DA)    | DAA: RXA                        | 64  | A6                | OA          | EB: A6                                      |

| 31  | VDD          | PWR      | VCC and filter                  | 65  | A7                | OA          | EB: A7                                      |

| 32  | TXA1         | O(DD)    | DAA: TXA1                       | 66  | A8                | OA          | EB: A8                                      |

| 33  | TXA2         | O(DD)    | DAA: TXA2                       | 67  | A9                | OA          | EB: A9                                      |

| 34  | AGND         | GND      | AGND                            | 68  | A10               | OA          | EB; A10                                     |

#### Notes: