# Voltage Output PROGRAMMABLE SENSOR CONDITIONER

# **FEATURES**

- COMPLETE BRIDGE SENSOR CONDITIONER

- VOLTAGE OUTPUT

- Ratiometric or Absolute

- DIGITALLY CALIBRATED

- One-Wire and Two-Wire Digital Interface

- SENSOR ERROR COMPENSATION

- Span

- Offset

- Temperature Drift of Span and Offset

- ELIMINATES POTENTIOMETERS

- ELIMINATES SENSOR TRIMS

- LOW, TIME-STABLE, TOTAL ADJUSTED ERROR

- SENSOR LINEARIZATION CIRCUITRY

- TEMPERATURE SENSE SELECT – Internal/External

- CALIBRATION TABLE LOOKUP LOGIC

Includes Linear Interpolation Algorithm

- NONVOLATILE CALIBRATION CONSTANTS

External 1K EEPROM (SOT23-5)

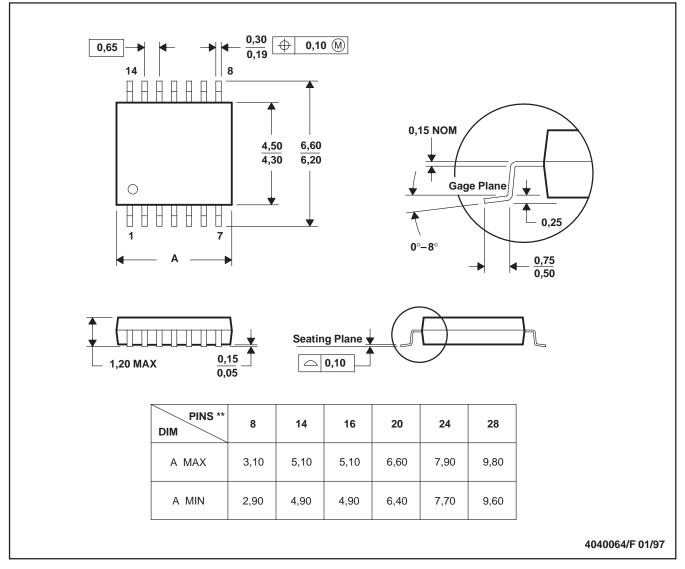

- SMALL TSSOP-16 PACKAGE

- -40°C to +125°C OPERATION

- +2.7V TO +5.5V OPERATION

# **APPLICATIONS**

- PRESSURE BRIDGE CONDITIONERS

With Digital Calibration

- SENSORS

- REMOTE 4-20mA TRANSMITTERS

- WEIGH SCALE BRIDGE TRANSMITTERS

- SCADA REMOTE DATA ACQUISITION

- INDUSTRIAL PROCESS CONTROL

- AUTOMOTIVE SENSORS

# **EVALUATION TOOLS**

- HARDWARE DESIGNER'S KIT (PGA309DK)

Evaluate PGA309 and Sensor

- Full Temperature Evaluation

- SOFTWARE CONTROL FOR DESIGNER'S KIT

- Program PGA309 for Evaluation

- Program PGA309 for First Production Run

- Sensor Computation Analysis Tool

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

# PACKAGE/ORDERING INFORMATION<sup>(1)</sup>

| PRODUCT | PACKAGE-LEAD | PACKAGE<br>DRAWING | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT MEDIA,<br>QUANTITY |

|---------|--------------|--------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| DO ADOD | T000D 40     | DW                 | 4000 4- + 40500                   | DO A 200           | PGA309AIPWR        | Tape and Reel, 2500          |

| PGA309  | TSSOP-16     | PW                 | –40°C to +125°C                   | PGA309             | PGA309AIPWT        | Tape and Reel, 250           |

(1) For the most current package and ordering information, refer to our web site at www.ti.com.

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

over operating free-air temperature range unless otherwise noted.

| Supply Voltage, V <sub>SD</sub> , V <sub>SD</sub> , +7.0V                                        |

|--------------------------------------------------------------------------------------------------|

| Input Voltage, V <sub>IN1</sub> , V <sub>IN2</sub> <sup>(2)</sup> –0.3V to V <sub>SA</sub> +0.3V |

| Input Current, V <sub>FB</sub> , V <sub>OUT</sub> ±150mA                                         |

| Input Current ±10mA                                                                              |

| Output Current Limit                                                                             |

| Storage Temperature Range –60°C to +150°C                                                        |

| Operating Temperature Range –55°C to +150°C                                                      |

| Junction Temperature+150°C                                                                       |

| Lead Temperature (soldering, 10s) +300°C                                                         |

| ESD Protection (Human Body Model) 4kV                                                            |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

(2) Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.5V beyond the supply rails should be current limited to 10mA or less.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

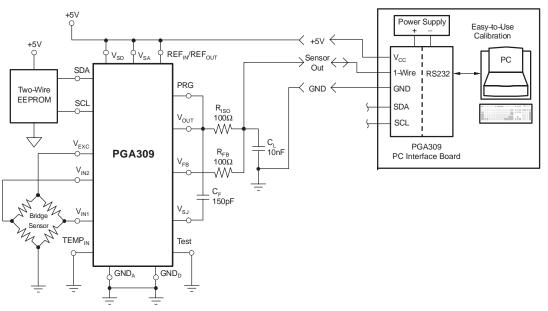

# DESCRIPTION

The PGA309 is a programmable analog signal conditioner designed for pressure bridge sensors. The analog signal path amplifies the sensor signal and provides digital calibration for zero, span, zero drift, span drift, and linearization errors. The calibration is done via a One-Wire digital serial interface or through a Two-Wire compatible connection. The calibration parameters are stored in external nonvolatile memory, to eliminate manual trimming and achieve long time stability.

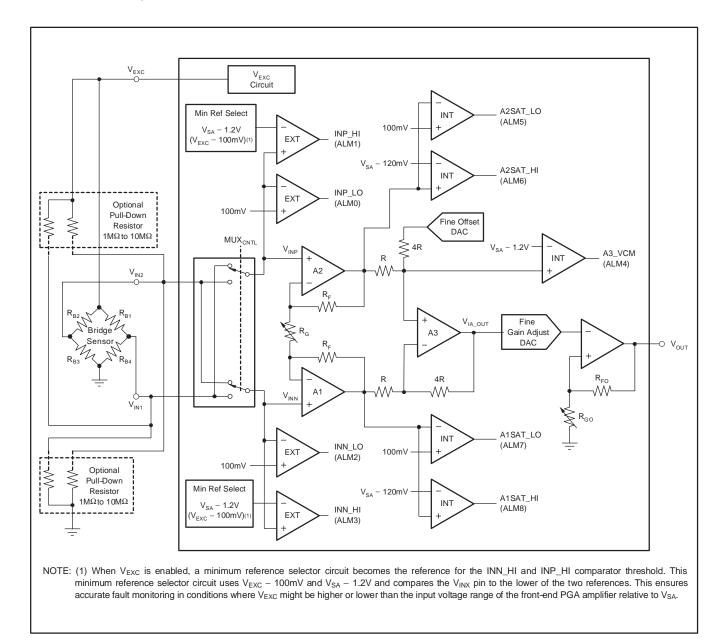

The all-analog signal path contains a 2X2 input mux, auto-zeroed programmable-gain instrumentation amplifier, linearization circuit, voltage reference, internal oscillator, control logic, and an output amplifier. Programmable level shifting compensates for sensor DC offsets. Automatic reset is initiated when supply is lost.

The core of the PGA309 is the precision low-drift and low-noise front-end programmable gain amplifier (PGA). The overall gain of the PGA + output amplifier can be adjusted from +2.7V/V to +1152V/V. The polarity of the inputs can be switched through the Input multiplexer (mux) to accommodate sensors with unknown polarity output. The fault monitor circuit detects and signals sensor burnout, overload, and system fault conditions.

# **ELECTRICAL CHARACTERISTICS**

BOLDFACE limits apply over the specified temperature range:  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$

$T_{A} = +25^{\circ}C, V_{SA} = V_{SD} = +5V (V_{SA} = V_{SUPPLY} \text{ ANALOG}, V_{SD} = V_{SUPPLY} \text{ DIGITAL}; V_{SA} \text{ must equal } V_{SD}), \text{ GND}_{D} = \text{GND}_{A} = 0, \text{ and } V_{REF} = \text{REF}_{IN}/\text{REF}_{OUT} = +5V, \text{ unless otherwise noted}.$

|                                                                                                                     |                                                                                                                                        | PGA309 |                         |                      |               |  |

|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------|----------------------|---------------|--|

| PARAMETER                                                                                                           | CONDITIONS                                                                                                                             | MIN    | TYP                     | MAX                  | UNITS         |  |

| FRONT-END PGA + OUTPUT AMPLIFIER<br>V <sub>OUT</sub> /V <sub>IN</sub> Differential Signal Gain Range <sup>(1)</sup> | Fine Gain Adjust = 1<br>Front-End PGA Gains: 4, 8, 16, 23, 27, 32, 42.67, 64, 128<br>Output Amplifier Gains: 2, 2.4, 3, 3.6, 4.5, 6, 9 |        | 8 to 1152               |                      | V/V           |  |

| V <sub>OUT</sub> Slew Rate                                                                                          |                                                                                                                                        |        | 0.5                     |                      | V/µs          |  |

| V <sub>OUT</sub> Settling Time (0.01%)                                                                              | $V_{OUT}/V_{IN}$ Differential Gain = 8, R <sub>L</sub> = 5k $\Omega$    200pF                                                          |        | 6                       |                      | μs            |  |

| V <sub>OUT</sub> Settling Time (0.01%)                                                                              | $V_{OUT}/V_{IN}$ Differential Gain = 191, R <sub>L</sub> = 5k $\Omega$    200pF                                                        |        | 4.1<br>0.002            |                      | μs<br>%FSR    |  |

| V <sub>OUT</sub> Nonlinearity<br>External Sensor Output Sensitivity                                                 | $V_{SA} = V_{SD} = V_{EXC} = +5V$                                                                                                      |        | 1 to 245                |                      | mV/V          |  |

| FRONT-END PGA                                                                                                       | VSA = VSD = VEXC = 10V                                                                                                                 |        | 1 10 240                |                      | 1110/0        |  |

| Auto-Zero Internal Frequency                                                                                        |                                                                                                                                        |        | 7                       |                      | kHz           |  |

| Offset Voltage (RTI) <sup>(2)</sup>                                                                                 | Coarse Offset Adjust Disabled                                                                                                          |        | ±3                      | ±50                  | μV            |  |

| vs Temperature                                                                                                      |                                                                                                                                        |        | ±0.2                    | _00                  | μ <b>ν/°C</b> |  |

| vs Supply Voltage, V <sub>SA</sub>                                                                                  |                                                                                                                                        |        | ±2                      |                      | μV/V          |  |

| vs Common-Mode Voltage                                                                                              | G <sub>F</sub> = Front-End PGA Gain                                                                                                    |        | 1500/G <sub>F</sub>     | 6000/G <sub>F</sub>  | μV/V          |  |

| Linear Input Voltage Range(3)                                                                                       |                                                                                                                                        | 0.2    |                         | V <sub>SA</sub> -1.5 | · v           |  |

| Input Bias Current                                                                                                  |                                                                                                                                        |        | 0.1                     | 1.5                  | nA            |  |

| Input Impedance: Differential                                                                                       |                                                                                                                                        |        | 30    6                 |                      | GΩ    pł      |  |

| Input Impedance: Common-Mode                                                                                        |                                                                                                                                        |        | 50    20                |                      | GΩ    pł      |  |

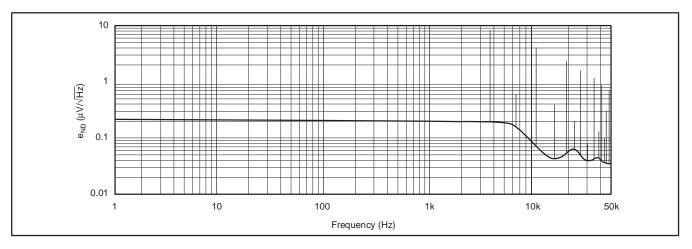

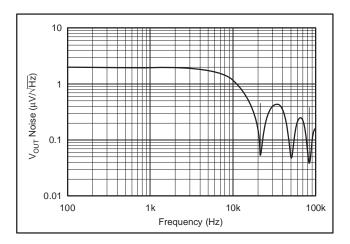

| Input Voltage Noise                                                                                                 | 0.1Hz to 10Hz, G <sub>F</sub> = 128                                                                                                    |        | 4                       |                      | μνρρ          |  |

| PGA Gain <sup>(1)</sup>                                                                                             |                                                                                                                                        |        |                         |                      |               |  |

| Gain Range Steps                                                                                                    | 4, 8, 16, 23.27, 32, 42.67, 64, 128                                                                                                    |        | 4 to 128                |                      | V/V           |  |

| Initial Gain Error                                                                                                  | $G_{F} = 4 \text{ to } 42$                                                                                                             |        | 0.2                     | ±1                   | %             |  |

|                                                                                                                     | G <sub>F</sub> = 64                                                                                                                    |        | 0.25                    | ±1.2                 | %             |  |

| vs Temperature                                                                                                      | G <sub>F</sub> = 128                                                                                                                   |        | 0.3<br>10               | ±1.6                 | %             |  |

| Output Voltage Range                                                                                                |                                                                                                                                        | 0      | 05 to V <sub>SA</sub> – | 0.1                  | ppm/°C<br>V   |  |

| Bandwidth                                                                                                           | Gain = 4                                                                                                                               | 0.     | 400                     |                      | kHz           |  |

| Danawath                                                                                                            | Gain = 128                                                                                                                             |        | 15.5                    |                      | kHz           |  |

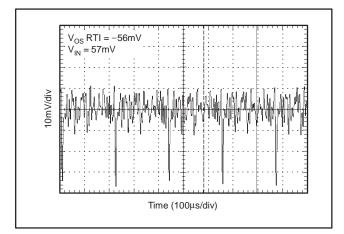

| COARSE OFFSET ADJUST<br>(RTI OF FRONT-END PGA)                                                                      |                                                                                                                                        |        |                         |                      |               |  |

| Range                                                                                                               | ±(15)(V <sub>REF</sub> /1250)                                                                                                          | ±56    | ±59.5                   | ±64                  | mV            |  |

| vs Temperature                                                                                                      |                                                                                                                                        |        | 0.004                   |                      | %/°C          |  |

| Resolution                                                                                                          | ±15 steps, 4-Bit + Sign                                                                                                                |        | 4                       |                      | mV            |  |

| FINE OFFSET ADJUST (ZERO DAC)<br>(RTO of the Front-End PGA) <sup>(2)</sup>                                          |                                                                                                                                        |        |                         |                      |               |  |

| Programming Range                                                                                                   |                                                                                                                                        | 0      |                         | VREF                 | V             |  |

| Output Range                                                                                                        |                                                                                                                                        | 0.1    |                         | V <sub>SA</sub> -0.1 | V             |  |

| Resolution                                                                                                          | 65,536 steps, 16-Bit DAC                                                                                                               |        | 73                      |                      | μV            |  |

| Integral Nonlinearity                                                                                               |                                                                                                                                        |        | 20                      |                      | LSB           |  |

| Differential Nonlinearity                                                                                           |                                                                                                                                        |        | 0.5                     |                      | LSB           |  |

| Gain Error                                                                                                          |                                                                                                                                        |        | 0.1                     | ļ                    | %<br>nnm/°C   |  |

| Gain Error Drift<br>Offset                                                                                          |                                                                                                                                        |        | 10<br>5                 |                      | ppm/°C<br>mV  |  |

| Offset Drift                                                                                                        |                                                                                                                                        |        | 10                      |                      | μV/°C         |  |

| OUTPUT FINE GAIN ADJUST (GAIN DAC)                                                                                  |                                                                                                                                        |        |                         |                      |               |  |

| Range                                                                                                               |                                                                                                                                        |        | 0.33 to 1               |                      | V/V           |  |

| Resolution                                                                                                          | 65,536 steps, 16-Bit DAC                                                                                                               |        | 10                      |                      | μV/V          |  |

| Integral NonLinearity                                                                                               |                                                                                                                                        |        | 20                      |                      | LSB           |  |

| Differential NonLinearity                                                                                           |                                                                                                                                        |        | 0.5                     |                      | LSB           |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

BOLDFACE limits apply over the specified temperature range:  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$

$T_{A} = +25^{\circ}C, V_{SA} = V_{SD} = +5V (V_{SA} = V_{SUPPLY} \text{ ANALOG}, V_{SD} = V_{SUPPLY} \text{ DIGITAL}; V_{SA} \text{ must equal } V_{SD}), \text{ GND}_{D} = \text{GND}_{A} = 0, \text{ and } V_{REF} = \text{REF}_{IN}/\text{REF}_{OUT} = +5V, \text{ unless otherwise noted}.$

|                                                         |                                                                | PGA309 |                       |                      |               |

|---------------------------------------------------------|----------------------------------------------------------------|--------|-----------------------|----------------------|---------------|

| PARAMETER                                               | CONDITIONS                                                     | MIN    | ТҮР                   | MAX                  | UNITS         |

| OUTPUT AMPLIFIER                                        |                                                                |        |                       |                      |               |

| Offset Voltage (RTI of Output Amplifier) <sup>(2)</sup> |                                                                |        | 3                     |                      | mV            |

| vs Temperature                                          |                                                                |        | 5                     |                      | μ <b>V/°C</b> |

| vs Supply Voltage, V <sub>SA</sub>                      |                                                                |        | 30                    |                      | μV/V          |

| Common-Mode Input Range                                 |                                                                | 0      |                       | V <sub>SA</sub> -1.5 | v             |

| Input Bias Current                                      |                                                                |        | 100                   | 0/1                  | pА            |

| Amplifier Internal Gain                                 |                                                                |        |                       |                      | -             |

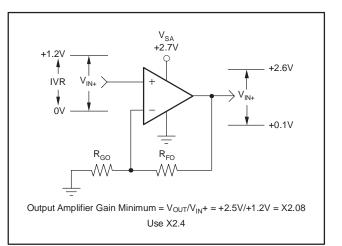

| Gain Range Steps                                        | 2, 2.4, 3, 3.6, 4.5, 6, 9                                      |        | 2 to 9                |                      | V/V           |

| Initial Gain Error                                      | 2, 2.4, 3.6                                                    |        | 0.25                  | ±1                   | %             |

|                                                         | 4.5                                                            |        | 0.3                   | ±1.2                 | %             |

|                                                         | 6                                                              |        | 0.4                   | ±1.5                 | %             |

|                                                         | 9                                                              |        | 0.6                   | ±2.0                 | %             |

| vs Temperature                                          | 2, 2.4, 3.6                                                    |        | 5                     |                      | ppm/°C        |

|                                                         | 4.5                                                            |        | 5                     |                      | ppm/°C        |

|                                                         | 6                                                              |        | 15                    |                      | ppm/°C        |

|                                                         | 9                                                              |        | 30                    |                      | ppm/°C        |

| Output Voltage Range <sup>(4)</sup>                     | $R_1 = 10k\Omega$                                              | 0.1    |                       | 4.9                  | v             |

| OpenLoop Gain                                           | -                                                              |        | 115                   |                      | dB            |

| Gain-Bandwidth Product                                  |                                                                |        | 2                     |                      | MHz           |

| Phase Margin                                            | Gain = 1                                                       |        | 45                    |                      | Degrees       |

| Output Resistance                                       | AC Small-Signal, Open-Loop, f = 1MHz                           |        | 675                   |                      | Ω             |

| OVER- AND UNDER-SCALE LIMITS                            | (V <sub>RFF</sub> = 4.096)                                     |        |                       |                      |               |

| Over-Scale Thresholds                                   | Ratio of $V_{REF}$ , Register 5—Bits D5, D4, D3 = '000'        |        | 0.9708                |                      |               |

|                                                         | Ratio of $V_{REF}$ , Register 5—Bits D5, D4, D3 = '001'        |        | 0.9610                |                      |               |

|                                                         | Ratio of $V_{REF}$ , Register 5—Bits D5, D4, D3 = '010'        |        | 0.9394                |                      |               |

|                                                         | Ratio of $V_{\text{REF}}$ , Register 5—Bits D5, D4, D3 = '011' |        | 0.9160                |                      |               |

|                                                         | Ratio of $V_{\text{REF}}$ , Register 5—Bits D5, D4, D3 = '100' |        | 0.9102                |                      |               |

|                                                         | Ratio of V <sub>REF</sub> , Register 5—Bits D5, D4, D3 = '101' |        | 0.7324                |                      |               |

|                                                         | Ratio of $V_{\text{REF}}$ , Register 5—Bits D5, D4, D3 = '110' |        | 0.5528                |                      |               |

| Over-Scale Comparator Offset                            | KEF,                                                           | +6     | +60                   | +114                 | mV            |

| Over-Scale Comparator Offset Drift                      |                                                                |        | +0.37                 |                      | mV/°C         |

| Under-Scale Thresholds                                  | Ratio of V <sub>REF</sub> , Register 5—Bits D2, D1, D0 = '111' |        | 0.0605                |                      |               |

|                                                         | Ratio of V <sub>REF</sub> , Register 5—Bits D2, D1, D0 = '110' |        | 0.0547                |                      |               |

|                                                         | Ratio of V <sub>RFF</sub> , Register 5—Bits D2, D1, D0 = '101' |        | 0.0507                |                      |               |

|                                                         | Ratio of V <sub>REF</sub> , Register 5—Bits D2, D1, D0 = '100' |        | 0.0449                |                      |               |

|                                                         | Ratio of V <sub>REF</sub> , Register 5—Bits D2, D1, D0 = '011' |        | 0.0391                |                      |               |

|                                                         | Ratio of $V_{\text{REF}}$ , Register 5—Bits D2, D1, D0 = '010' |        | 0.0352                |                      |               |

|                                                         | Ratio of $V_{\text{REF}}$ , Register 5—Bits D2, D1, D0 = '001' |        | 0.0293                |                      |               |

|                                                         | Ratio of $V_{\text{REF}}$ , Register 5—Bits D2, D1, D0 = '000' |        | 0.0254                |                      |               |

| Under-Scale Comparator Offset                           | KEF,                                                           | -7     | -50                   | +93                  | mV            |

| Under-Scale Comparator Offset Drift                     |                                                                |        | -0.15                 |                      | mV/°C         |

| FAULT MONITOR CIRCUIT                                   |                                                                |        |                       |                      |               |

| INP_HI, INN_HI Comparator Threshold                     | See Note 5                                                     |        | V <sub>SA</sub> -1.2  |                      | V             |

| - ·                                                     |                                                                |        | or                    |                      |               |

|                                                         |                                                                |        | V <sub>EXC</sub> -100 |                      |               |

| INP_LO, INN_LO Comparator Threshold                     |                                                                | 40     | 100                   |                      | mV            |

| A1SAT_HI, A2SAT_HI Comparator Threshold                 |                                                                |        | V <sub>SA</sub> -0.12 |                      | V             |

| A1SAT_LO, A2SAT_LO Comparator Threshold                 |                                                                |        | V <sub>SA</sub> -0.12 |                      | V             |

| A3_VCM Comparator Threshold                             |                                                                |        | V <sub>SA</sub> -1.2  |                      | V             |

| Comparator Hysteresis                                   |                                                                |        | 20                    |                      | mV            |

# **ELECTRICAL CHARACTERISTICS (continued)**

BOLDFACE limits apply over the specified temperature range:  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$

$T_{A} = +25^{\circ}C, V_{SA} = V_{SD} = +5V (V_{SA} = V_{SUPPLY ANALOG}, V_{SD} = V_{SUPPLY DIGITAL}; V_{SA} must equal V_{SD}), GND_{D} = GND_{A} = 0, and V_{REF} = REF_{IN}/REF_{OUT} = +5V, unless otherwise noted.$

|                                        |                                                                                                          | PGA309   |                        |                      |             |  |

|----------------------------------------|----------------------------------------------------------------------------------------------------------|----------|------------------------|----------------------|-------------|--|

| PARAMETER                              | CONDITIONS                                                                                               | MIN TYP  |                        | MAX                  | UNITS       |  |

| INTERNAL VOLTAGE REFERENCE             |                                                                                                          |          |                        |                      |             |  |

| V <sub>REF1</sub>                      | Register 3, Bit D9 = 1                                                                                   | 2.46     | 2.5                    | 2.53                 | V           |  |

| V <sub>REF1</sub> Drift vs Temperature |                                                                                                          | İ        | +10                    |                      | ppm/°C      |  |

| V <sub>REF2</sub>                      | Register 3, Bit D9 = 0                                                                                   |          | 4.096                  | 4.14                 | V           |  |

| V <sub>REF2</sub> Drift vs Temperature |                                                                                                          |          | +10                    |                      | ppm/°C      |  |

| Input Current REFIN/REFOUT             | Internal V <sub>RFF</sub> Disabled                                                                       | Ì        | 100                    |                      | μA          |  |

| Output Current REFIN/REFOUT            | $V_{SA} > 2.7V$ for $V_{REF} = 2.5V$                                                                     |          | 1                      |                      | mA          |  |

|                                        | $V_{SA} > 4.3V$ for $V_{REF} = 4.096V$                                                                   |          | 1                      |                      | mA          |  |

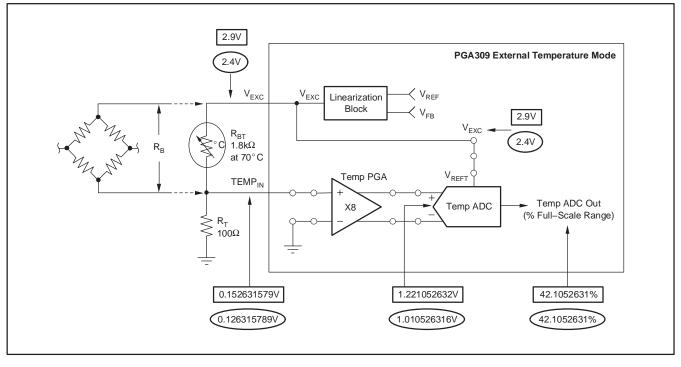

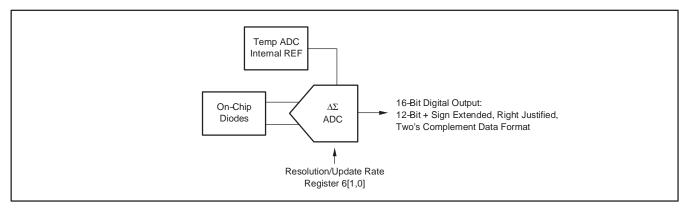

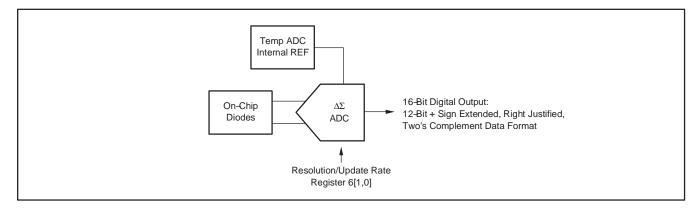

| TEMPERATURE SENSE CIRCUITRY (ADC)      |                                                                                                          |          |                        |                      |             |  |

| Internal Temperature Measurement       | Register 6, Bit D9 = 1                                                                                   |          |                        |                      |             |  |

| Accuracy                               |                                                                                                          |          | ±2                     |                      | °C          |  |

| Resolution                             | 12-Bit + Sign, Two's Complement Data Format                                                              |          | ±0.0625                |                      | °C          |  |

| Temperature Measurement Range          |                                                                                                          | -55      |                        | +150                 | °Č          |  |

| Conversion Rate                        | $R_1$ , $R_0$ = '11', 12-Bit + Sign Resolution                                                           |          | 24                     |                      | ms          |  |

| TEMPERATURE ADC                        |                                                                                                          | 1        |                        |                      |             |  |

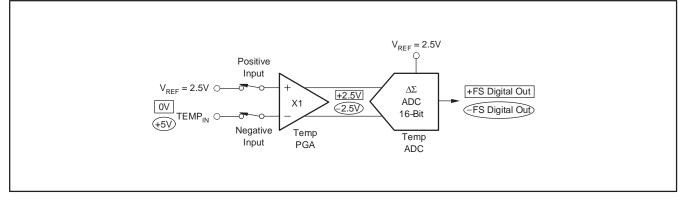

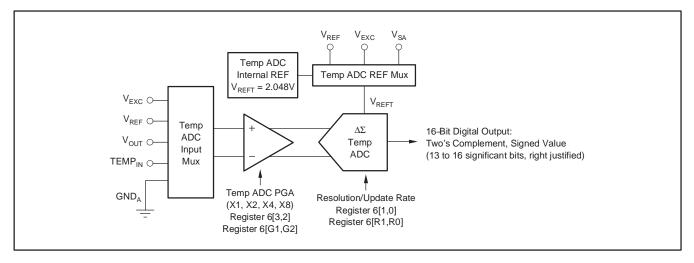

| External Temperature Mode              | Temp PGA + Temp ADC                                                                                      |          |                        |                      |             |  |

| Gain Range Steps                       | G <sub>PGA</sub> = 1, 2, 4, 8                                                                            |          | 1 to 8                 |                      | V/V         |  |

| Analog Input Voltage Range             | 0FGA ., _, ,, 0                                                                                          | GND-0.2  | 1.000                  | V <sub>SA</sub> +0.2 | V           |  |

| Temperature ADC Internal REF (2.048V)  | Register 6, Bit D8 = 1                                                                                   | 0110 0.2 |                        | *5A+0.2              | , i         |  |

| Full-Scale Input Voltage               | (+Input) – (–Input)                                                                                      |          | ±2.048/G <sub>PG</sub> |                      | V           |  |

| Differential Input Impedance           | (mpa) (mpa)                                                                                              | -        | 2.8/G <sub>PGA</sub>   | <b>\</b>             | MΩ          |  |

| Common-Mode Input Impedance            | G <sub>PGA</sub> = 1                                                                                     |          | 3.5                    |                      | MΩ          |  |

| Common mode input impedance            | $Gp_{GA} = 1$<br>$Gp_{GA} = 2$                                                                           |          | 3.5                    |                      | MΩ          |  |

|                                        | $Gp_{GA} = 2$<br>$Gp_{GA} = 4$                                                                           |          | 1.8                    |                      | MΩ          |  |

|                                        | $Gp_{GA} = 4$<br>$Gp_{GA} = 8$                                                                           |          | 0.9                    |                      | MΩ          |  |

| Resolution                             | $CP_{GA} = 0$<br>R1, R0 = '00', ADC2X = '0', Conversion Time = 8ms                                       |          | 11                     |                      | Bits + Sign |  |

| Resolution                             | R1, R0 = $(01)$ , ADC2X = $(0)$ , Conversion Time = $32ms$                                               |          | 13                     |                      | Bits + Sign |  |

|                                        | R1, R0 = '10', ADC2X = '0', Conversion Time = 52ms<br>R1, R0 = '10', ADC2X = '0', Conversion Time = 64ms |          | 13                     |                      | Bits + Sign |  |

|                                        | R1, R0 = '11', ADC2X = '0', Conversion Time = 04 ms                                                      |          | 15                     |                      | Bits + Sign |  |

| Integral Nonlinearity                  |                                                                                                          |          | 0.004                  |                      | %           |  |

| Offset Error                           | 6 1                                                                                                      |          | 1.2                    |                      | mV          |  |

| Oliset Endi                            | $G_{PGA} = 1$                                                                                            |          | 0.7                    |                      |             |  |

|                                        | $G_{PGA} = 2$                                                                                            |          | 0.7                    |                      | mV          |  |

|                                        | $G_{PGA} = 4$                                                                                            |          | 0.5                    |                      | mV<br>mV    |  |

|                                        | G <sub>PGA</sub> = 8                                                                                     |          |                        |                      |             |  |

| Offset Drift                           | G <sub>PGA</sub> = 1                                                                                     |          | 1.2                    |                      | μV/°C       |  |

|                                        | $G_{PGA} = 2$                                                                                            |          | 0.6                    |                      | μV/°C       |  |

|                                        | $G_{PGA} = 4$                                                                                            |          | 0.3                    |                      | μV/°C       |  |

| Offective V                            | $G_{PGA} = 8$                                                                                            |          | 0.3                    |                      | μV/°C       |  |

| Offset vs V <sub>SA</sub>              | $G_{PGA} = 1$                                                                                            |          | 800                    |                      | μV/V        |  |

|                                        | $G_{PGA} = 2$                                                                                            |          | 400                    |                      | μV/V        |  |

|                                        | $G_{PGA} = 4$                                                                                            |          | 200                    |                      | μV/V        |  |

| 0.5                                    | G <sub>PGA</sub> = 8                                                                                     |          | 150                    | 0.50                 | μV/V        |  |

| Gain Error                             |                                                                                                          |          | 0.05                   | 0.50                 | %           |  |

| Gain Error Drift                       |                                                                                                          |          | 5                      | 50                   | ppm/°C      |  |

| Gain vs V <sub>SA</sub>                |                                                                                                          |          | 80                     |                      | ppm/V       |  |

| Common-Mode Rejection                  | At DC and $G_{PGA} = 8$                                                                                  |          | 105                    |                      | dB          |  |

|                                        | At DC and G <sub>PGA</sub> = 1                                                                           |          | 100                    |                      | dB          |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

BOLDFACE limits apply over the specified temperature range:  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$

$T_{A} = +25^{\circ}C, V_{SA} = V_{SD} = +5V (V_{SA} = V_{SUPPLY} \text{ ANALOG}, V_{SD} = V_{SUPPLY} \text{ DIGITAL}; V_{SA} \text{ must equal } V_{SD}), \text{ GND}_{D} = \text{GND}_{A} = 0, \text{ and } V_{REF} = \text{REF}_{IN}/\text{REF}_{OUT} = +5V, \text{ unless otherwise noted}.$

|                                                                         |                                                     |           | PGA309                |                       |                |  |

|-------------------------------------------------------------------------|-----------------------------------------------------|-----------|-----------------------|-----------------------|----------------|--|

| PARAMETER                                                               | CONDITIONS                                          |           | MIN TYP MAX           |                       | UNITS          |  |

| TEMPERATURE ADC (CONTINUED)                                             |                                                     |           |                       |                       |                |  |

| Temp ADC Ext. REF ( $V_{REFT} = V_{REF}, V_{EXC}, \text{ or } V_{SA}$ ) | Register 6, Bit $D8 = 0$                            |           |                       |                       |                |  |

| Full-Scale Input Voltage                                                | (+Input) – (–Input)                                 | ±         | VREFT/GPG             | A                     | V              |  |

| Differential Input Impedance                                            |                                                     |           | 2.4/G <sub>PGA</sub>  |                       | MΩ             |  |

| Common-Mode Input Impedance                                             | G <sub>PGA</sub> = 1                                |           | 8                     |                       | MΩ             |  |

|                                                                         | $G_{PGA} = 2$                                       | İ         | 8                     |                       | MΩ             |  |

|                                                                         | $G_{PGA} = 4$                                       |           | 8                     |                       | MΩ             |  |

|                                                                         | $G_{PGA} = 8$                                       |           | 8                     |                       | MΩ             |  |

| Resolution                                                              | R1, R0 = '00', ADC2X = '0', Conversion Time = $6ms$ |           | 11                    |                       | Bits + Sign    |  |

|                                                                         | R1, R0 = '01', ADC2X = '0', Conversion Time = 24ms  |           | 13                    |                       | Bits + Sign    |  |

|                                                                         | R1, R0 = '10', ADC2X = '0', Conversion Time = 50ms  |           | 14                    |                       | Bits + Sign    |  |

|                                                                         | R1, R0 = '11', ADC2X = '0', Conversion Time = 100ms |           | 15                    |                       | Bits + Sign    |  |

| Integral Nonlinearity                                                   |                                                     |           | 0.01                  |                       | %              |  |

| Offset Error                                                            | G <sub>PGA</sub> = 1                                |           | 2.5                   |                       | mV             |  |

|                                                                         | G <sub>PGA</sub> = 2                                |           | 1.25                  |                       | mV             |  |

|                                                                         | GPGA = 4                                            |           | 0.7                   |                       | mV             |  |

|                                                                         | GPGA = 4<br>GPGA = 8                                |           | 0.3                   |                       | mV             |  |

| Offset Drift                                                            | $G_{PGA} = 0$<br>$G_{PGA} = 1$                      |           | 1.5                   |                       | μV/°C          |  |

|                                                                         | G <sub>PGA</sub> = 2                                |           | 1.0                   |                       | μV/°C          |  |

|                                                                         | $GP_{GA} = 2$<br>$G_{PGA} = 4$                      |           | 0.7                   |                       | μν/ C<br>μV/°C |  |

|                                                                         | GPGA = 4<br>GPGA = 8                                |           | 0.7                   |                       | μν/ C<br>μV/°C |  |

| Gain Error                                                              | Op <sub>GA</sub> = 8                                |           | -0.2                  |                       | μν/ C<br>%     |  |

| Gain Error Drift                                                        |                                                     |           |                       |                       |                |  |

|                                                                         |                                                     |           | 2<br>80               |                       | ppm/°C         |  |

| Gain vs V <sub>SA</sub>                                                 | At DC and C                                         |           |                       |                       | ppm/V          |  |

| Common-Mode Rejection                                                   | At DC and $G_{PGA} = 8$                             |           | 100                   |                       | dB             |  |

|                                                                         | At DC and $G_{PGA} = 1$                             |           | 85                    |                       | dB             |  |

| External Temperature Current Excitation ITEMP                           | Register 6, Bit D11 = 1                             | 5.0       | 7                     | 0                     |                |  |

| Current Excitation                                                      |                                                     | 5.8       | 7                     | 8                     | μA<br>nA/°C    |  |

| Temperature Drift                                                       |                                                     |           | -                     |                       | V              |  |

| Voltage Compliance                                                      |                                                     |           | V <sub>SA</sub> -1.2  |                       | V              |  |

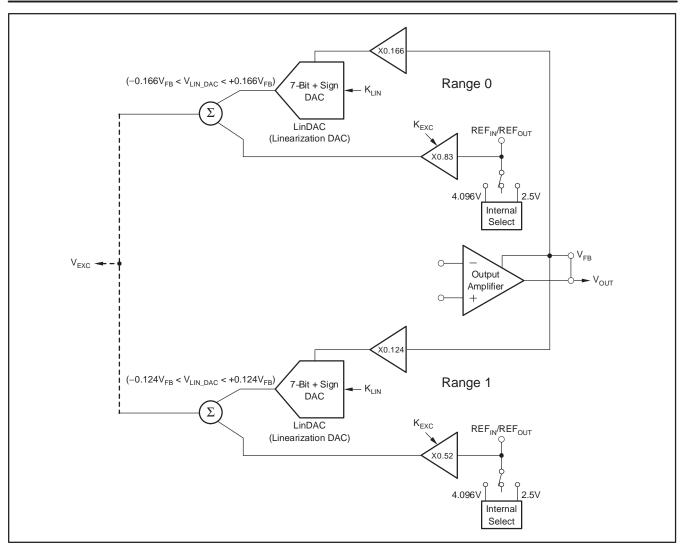

| LINEARIZATION ADJUST AND EXCITATION VOI                                 |                                                     |           |                       |                       |                |  |

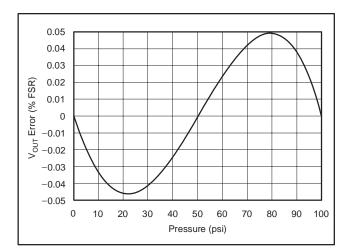

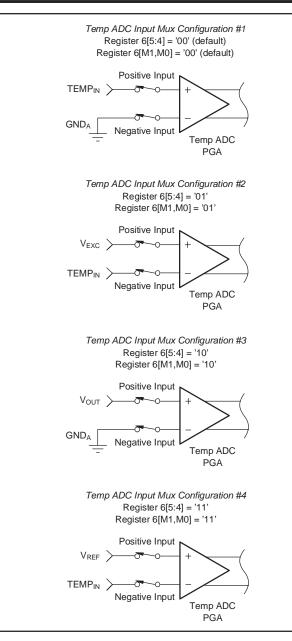

| Range 1                                                                 | Register 3, Bit D11 = 0                             |           |                       |                       |                |  |

| Linearization DAC Range                                                 | With Respect to V <sub>FB</sub>                     | _         | 0.166 to +0.10        | 56                    | V/V            |  |

| Linearization DAC Resolution                                            | ±128 Steps, 7-Bit + Sign                            |           | 1.3                   |                       | mV/V           |  |

| V <sub>EXC</sub> Gain                                                   | With Respect to VREF                                |           | 0.83                  |                       | V/V            |  |

| Gain Error Drift                                                        |                                                     |           | 25                    |                       | ppm/°C         |  |

| Range 2                                                                 | Register 3, Bit D11 = 1                             |           |                       |                       |                |  |

| Linearization DAC Range                                                 | With Respect to V <sub>FB</sub>                     | -         | 0.124 to +0.12        | 24                    | V/V            |  |

| Linearization DAC Resolution                                            | ±128 Steps, 7-Bit + Sign                            |           | 0.969                 |                       | mV/V           |  |

| V <sub>EXC</sub> Gain                                                   | With Respect to V <sub>REF</sub>                    |           | 0.52                  |                       | V/V            |  |

| Gain Error Drift                                                        |                                                     |           | 25                    |                       | ppm/°C         |  |

| V <sub>EXC</sub> Range Upper Limit                                      | I <sub>EXC</sub> = 5mA                              |           | V <sub>SA</sub> - 0.5 |                       | V              |  |

| EXC SHORT                                                               | Short-Circuit V <sub>EXC</sub> Output Current       |           | 50                    |                       | mA             |  |

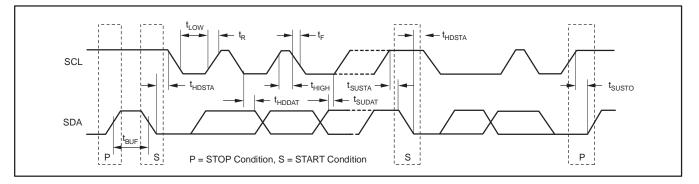

| DIGITAL INTERFACE                                                       |                                                     |           |                       |                       |                |  |

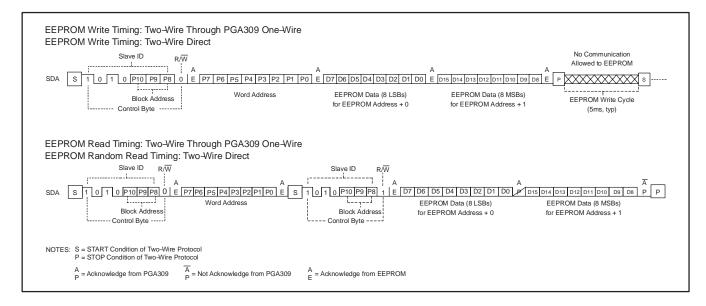

| Two-Wire Compatible                                                     | Bus Speed                                           | 1         |                       | 400                   | kHz            |  |

| One-Wire                                                                | Serial Speed Baud Rate                              | 4.8K      |                       | 38.4K                 | Bits/s         |  |

| Maximum Lookup Table Size <sup>(6)</sup>                                |                                                     |           | 17 x 3 x 16           |                       | Bits           |  |

| Two-Wire Data Rate                                                      | Communication Between PGA309 and EEPROM             |           | 65                    |                       | kHz            |  |

| LOGIC LEVELS                                                            |                                                     |           |                       |                       |                |  |

| Input Levels (SDA, SCL, PRG)                                            | Low                                                 |           |                       | 0.2 • V <sub>SD</sub> | V              |  |

|                                                                         | High                                                | 0.7 • VSD |                       | 00                    | V              |  |

|                                                                         | Hysteresis                                          |           | 0.1 • V <sub>SD</sub> |                       | V              |  |

| Output LOW Level (SDA, SCL)                                             | Open Drain w/90µA Internal                          |           |                       | 0.4                   | v              |  |

|                                                                         | Pull-Up to $V_{SD}$ , $I_{SINK} = 5mA$              |           |                       |                       |                |  |

| Output LOW Level (PRG)                                                  | Open Drain, I <sub>SINK</sub> = 5mA                 |           |                       | 0.4                   | V              |  |

| /                                                                       |                                                     | 1         | 1                     |                       | · · ·          |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

BOLDFACE limits apply over the specified temperature range:  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$

$T_{A} = +25^{\circ}C, V_{SA} = V_{SD} = +5V (V_{SA} = V_{SUPPLY} ANALOG, V_{SD} = V_{SUPPLY} DIGITAL; V_{SA} must equal V_{SD}), GND_{D} = GND_{A} = 0, and V_{REF} = REF_{IN}/REF_{OUT} = +5V, unless otherwise noted.$

|                                    |                                               | PGA309 |     |      |       |

|------------------------------------|-----------------------------------------------|--------|-----|------|-------|

| PARAMETER                          | CONDITIONS                                    | MIN    | TYP | MAX  | UNITS |

| POWER SUPPLY                       |                                               |        |     |      |       |

| VSA, VSD                           |                                               | 2.7    |     | 5.5  | V     |

| ISA + ISD, Quiescent Current       | $V_{SA} = V_{SD} = +5V$ , without Bridge Load |        | 1.2 | 1.6  | mA    |

| POWER-ON RESET                     |                                               |        |     |      |       |

| Power-Up Threshold                 | V <sub>SA</sub> Rising                        |        | 2.2 | 2.7  | v     |

| Power-Down Threshold               | V <sub>SA</sub> Falling                       |        | 1.7 |      | V     |

| TEMPERATURE RANGE                  |                                               |        |     |      |       |

| Specified Performance              |                                               | -40    |     | +125 | °C    |

| Operational – Degraded Performance |                                               | -55    |     | +150 | °C    |

(1) PGA309 total differential gain from input ( $V_{IN1}-V_{IN2}$ ) to output ( $V_{OUT}$ ).  $V_{OUT}/(V_{IN1}-V_{IN2}) =$  (PGA front-end gain) (output amplifier gain) (fine gain adjust).

(2) RTI = referred to input. RTO = referred to output.

(3) Linear input range is the allowed min/max voltage on the V<sub>IN1</sub> and V<sub>IN2</sub> pins for the input PGA to continue to operate in a linear region. The allowed common-mode and differential voltage is dependent upon gain and offset settings. Refer to the Gain Scaling section for more information.

(4) Unless limited by over/under-scale setting.

(5) When V<sub>EXC</sub> is enabled, a minimum reference selector circuit becomes the reference for the comparator threshold. This minimum reference selector circuit uses V<sub>EXC</sub> – 100mV and V<sub>SA</sub> – 1.2V and compares the V<sub>INX</sub> pin to the lower of the two references. This ensures accurate fault monitoring in conditions where V<sub>EXC</sub> might be higher or lower than the input CMR of the PGA input amplifier relative to V<sub>SA</sub>.

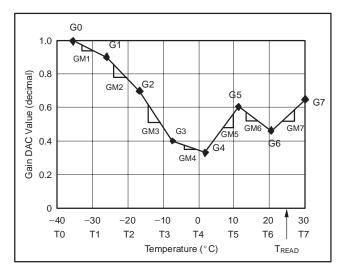

(6) Lookup Table allows multislope compensation over temperature. Lookup Table has access to 17 calibration points consisting of 3 adjustment values (Tx, Temperature, ZMx, Zero DAC, GMx, Gain) that are stored in 16-bit data format (17x3x16 = Lookup Table size).

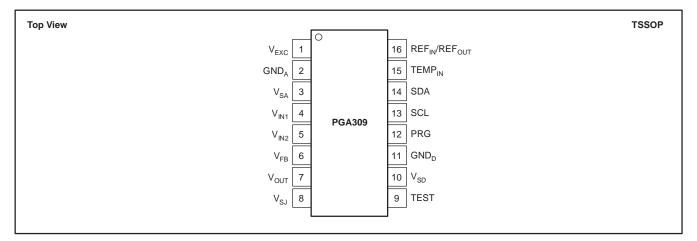

# **PIN CONFIGURATION**

### PIN DESCRIPTION

| PIN | NAME                                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>EXC</sub>                      | Bridge sensor excitation. Connect to bridge if linearization and/or internal reference for bridge excitation is to be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2   | GNDA                                  | Analog ground. Connect to analog ground return path for $V_{SA}$ . Should be same as $GND_D$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3   | V <sub>SA</sub>                       | Analog voltage supply. Connect to analog voltage supply. To be within 200mV of V <sub>SD</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4   | V <sub>IN1</sub>                      | Signal input voltage 1. Connect to + or – output of sensor bridge. Internal multiplexer can change connection internally to front-end PGA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5   | V <sub>IN2</sub>                      | Signal input voltage 2. Connect to + or – output of sensor bridge. Internal multiplexer can change connection internally to front-end PGA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

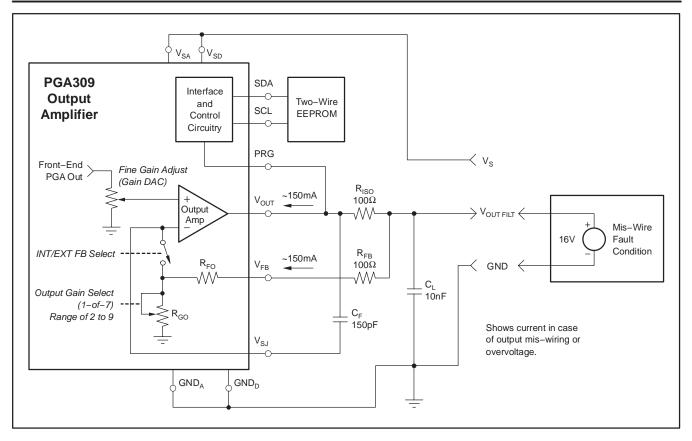

| 6   | V <sub>FB</sub>                       | $V_{OUT}$ feedback pin. Voltage feedback sense point for over/under-scale limit circuitry. When internal gain set resistors for the output amplifier are used, this is also the voltage feedback sense point for the output amplifier. $V_{FB}$ in combination with $V_{SJ}$ allows for ease of external filter and protection circuits without degrading the PGA309 $V_{OUT}$ accuracy. $V_{FB}$ must always be connected to either $V_{OUT}$ or the point of feedback for $V_{OUT}$ , if external protection is used.                                                                                         |

| 7   | VOUT                                  | Analog output voltage of conditioned sensor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

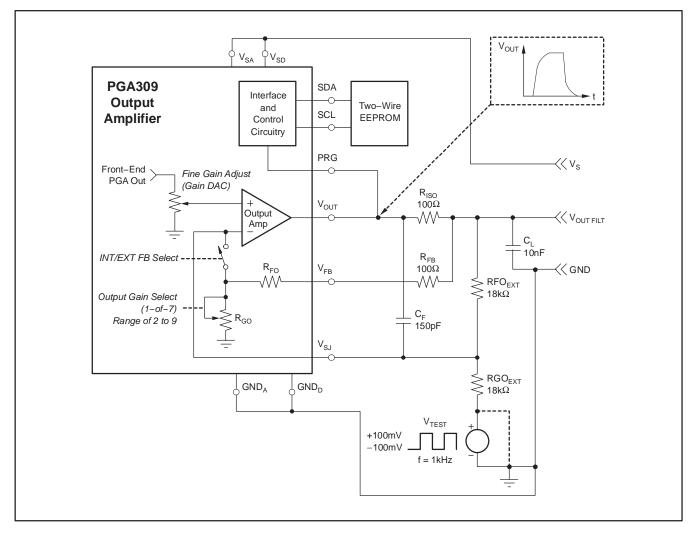

| 8   | V <sub>SJ</sub>                       | Output amplifier summing junction. Use for output amplifier compensation when driving large capacitive loads (> 100pF) and/or for using external gain setting resistors for the output amplifier.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9   | TEST                                  | Test/External Controller Mode pin. Pull to GND <sub>D</sub> in normal mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10  | V <sub>SD</sub>                       | Digital voltage supply. Connect to digital voltage supply. To be within 200mV of VSA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11  | GNDD                                  | Digital ground. Connect to digital ground return path for V <sub>SD</sub> . Should be same as GND <sub>A</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12  | PRG                                   | Single-wire interface program pin. UART-type interface for digital calibration of the PGA309 over a single wire. Can be connected to $V_{OUT}$ for a three-lead (V <sub>S</sub> , GND, $V_{OUT}$ ) smart programmable sensor assembly.                                                                                                                                                                                                                                                                                                                                                                          |

| 13  | SCL                                   | Clock input/output for Two-Wire, industry-standard compatible interface for reading digital calibration and configuration from external EEPROM. Can also communicate directly to the registers in the PGA309 through the Two-Wire, industry-standard compatible interface.                                                                                                                                                                                                                                                                                                                                      |

| 14  | SDA                                   | Data input/output for Two-Wire, industry-standard compatible interface for reading digital calibration and configuration from external EEPROM. Can also communicate directly to the registers in the PGA309 through the Two-Wire, industry-standard compatible interface.                                                                                                                                                                                                                                                                                                                                       |

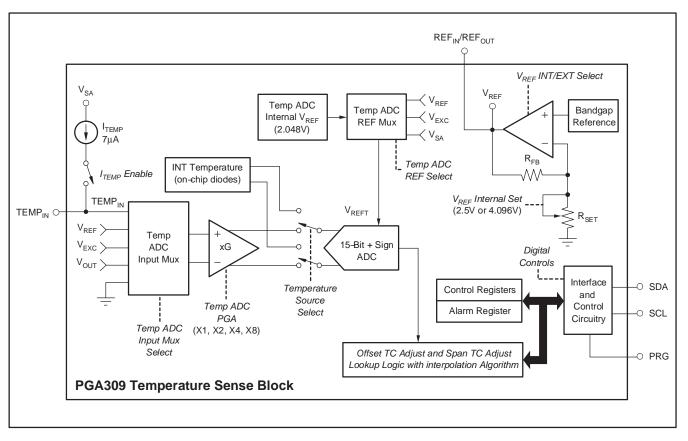

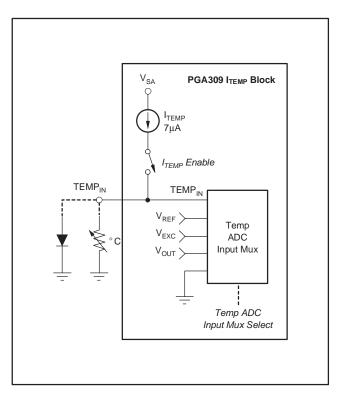

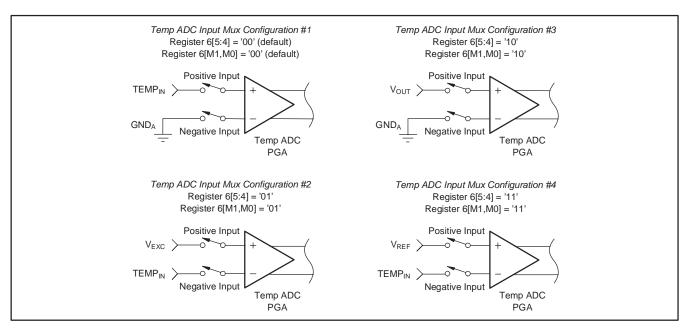

| 15  | TEMPIN                                | External temperature signal input. PGA309 can be configured to read a bridge current sense resistor as an indicator of bridge temperature, or an external temperature sensing device such as diode junction, or RTD, or thermistor. This input can be gained up internally by X1, X2, X4, or X8. In addition, this input can be read differentially with respect to $V_{GNDA}$ , $V_{EXC}$ , or the internal $V_{REF}$ . There is also an internal, register-selectable, 7µA current source (I <sub>TEMP</sub> ) that can be connected to TEMP <sub>IN</sub> as an RTD, thermistor, or diode excitation source. |

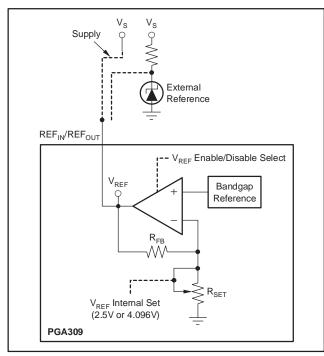

| 16  | REF <sub>IN</sub> /REF <sub>OUT</sub> | Reference input/output pin. As an output, the internal reference (selectable as 2.5V or 4.096V) is available for system use on this pin. As an input, the internal reference may be disabled and an external reference can then be applied as the reference for the PGA309.                                                                                                                                                                                                                                                                                                                                     |

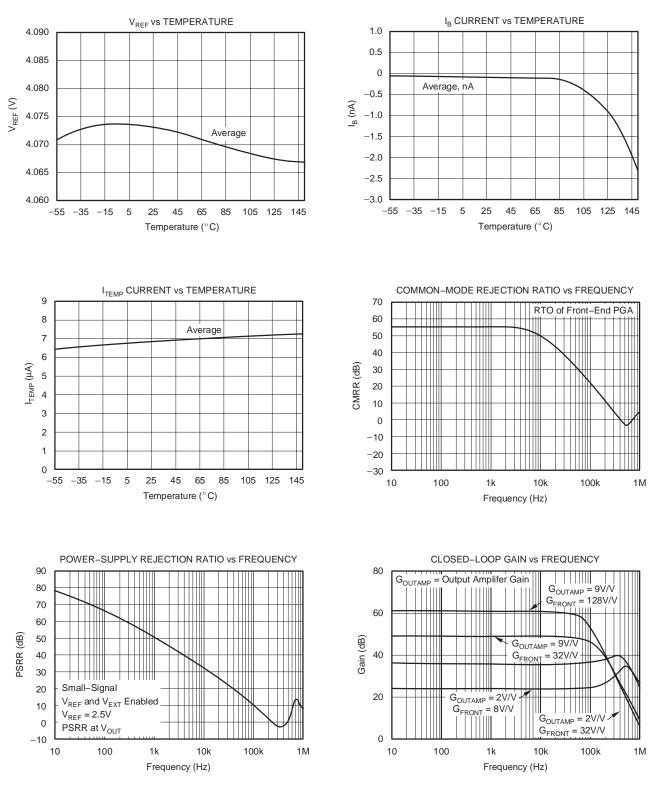

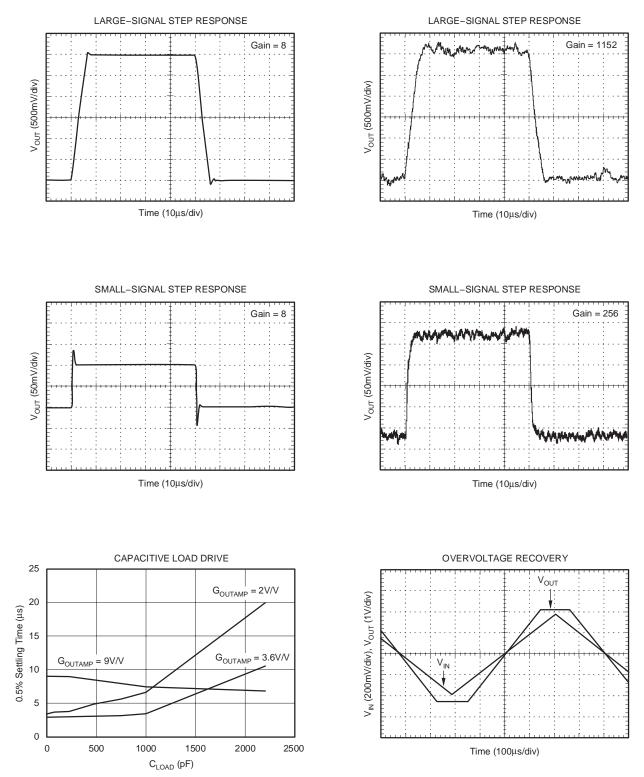

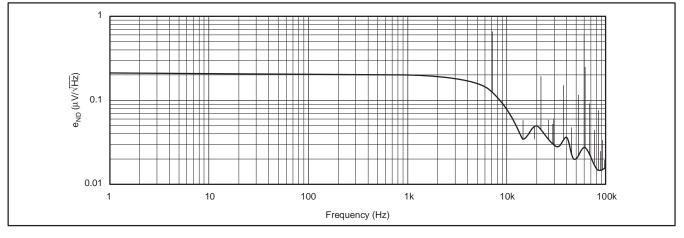

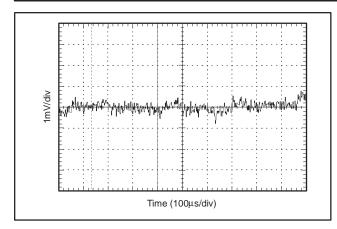

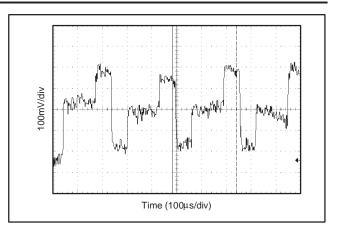

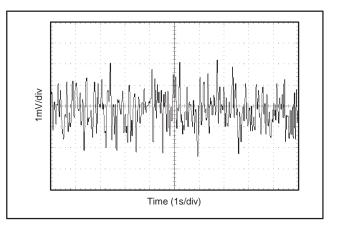

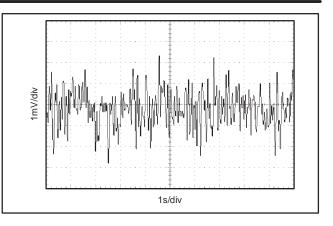

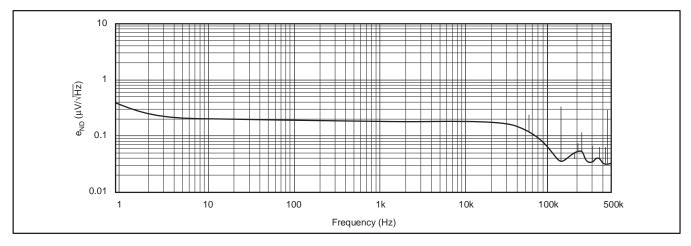

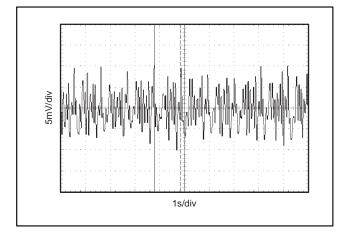

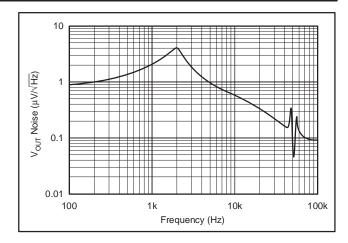

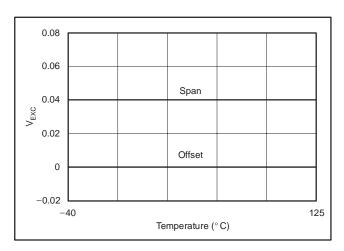

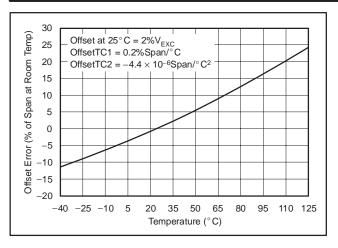

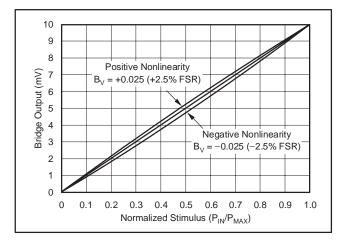

# TYPICAL CHARACTERISTICS

$T_{A} = +25^{\circ}C, V_{SA} = V_{SD} = +5V (V_{SA} = V_{SUPPLY} \text{ ANALOG}, V_{SD} = V_{SUPPLY} \text{ DIGITAL}, V_{SA} \text{ must equal } V_{SD}), \text{ GND}_{D} = \text{GND}_{A} = 0, \text{ and } V_{REF} = \text{REF}_{IN}/\text{REF}_{OUT} = +5V, \text{ unless otherwise noted}.$

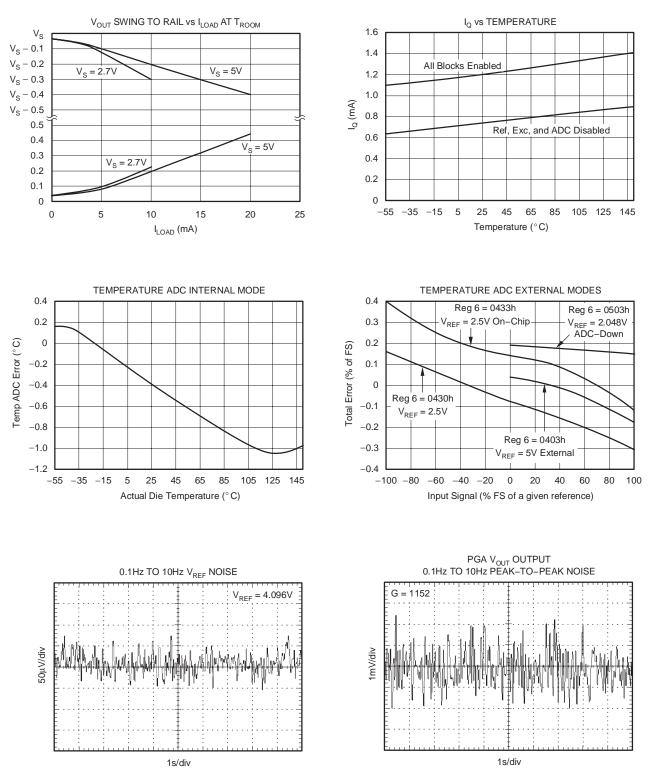

# **TYPICAL CHARACTERISTICS (Cont.)**

$T_{A} = +25^{\circ}C, V_{SA} = V_{SD} = +5V (V_{SA} = V_{SUPPLY} \text{ ANALOG}, V_{SD} = V_{SUPPLY} \text{ DIGITAL}, V_{SA} \text{ must equal } V_{SD}), \text{ GND}_{D} = \text{GND}_{A} = 0, \text{ and } V_{REF} = \text{REF}_{IN}/\text{REF}_{OUT} = +5V, \text{ unless otherwise noted}.$

### V TEXAS INSTRUMENTS www.ti.com

# TYPICAL CHARACTERISTICS (Cont.)

$T_{A} = +25^{\circ}C, V_{SA} = V_{SD} = +5V (V_{SA} = V_{SUPPLY} \text{ ANALOG}, V_{SD} = V_{SUPPLY} \text{ DIGITAL}, V_{SA} \text{ must equal } V_{SD}), \text{ GND}_{D} = \text{GND}_{A} = 0, \text{ and } V_{REF} = \text{REF}_{IN}/\text{REF}_{OUT} = +5V, \text{ unless otherwise noted}.$

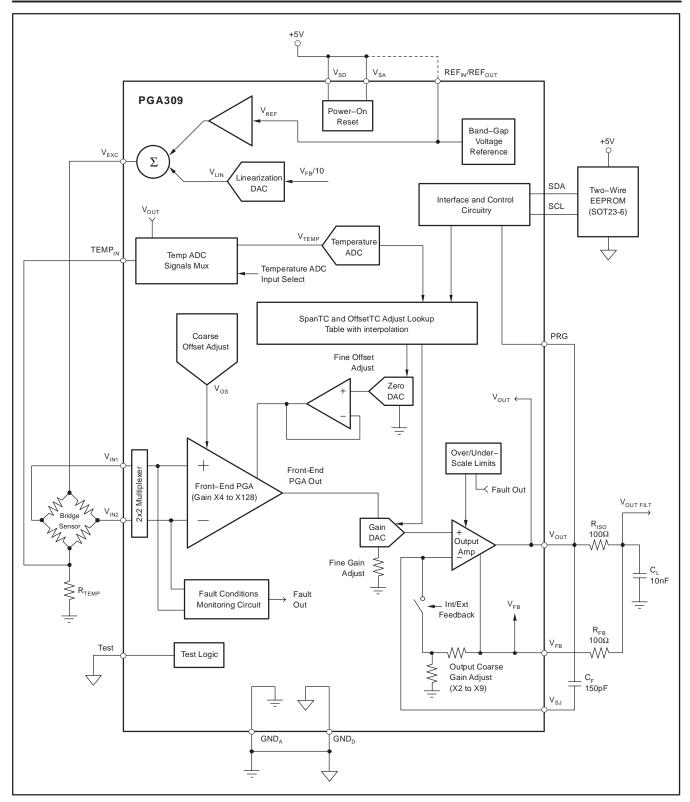

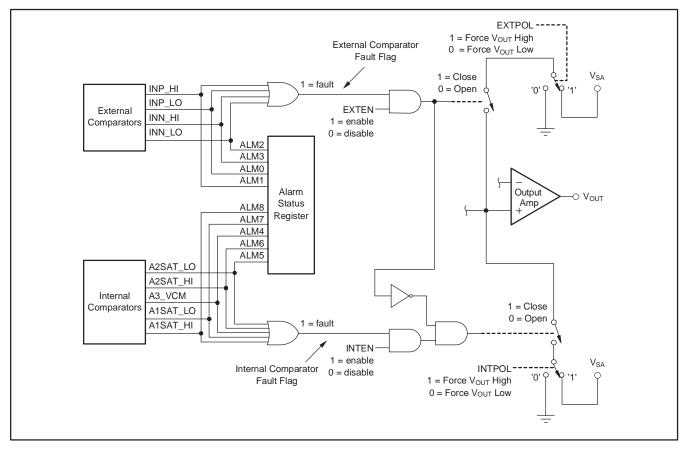

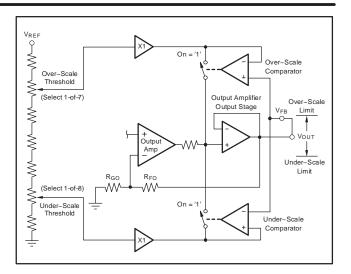

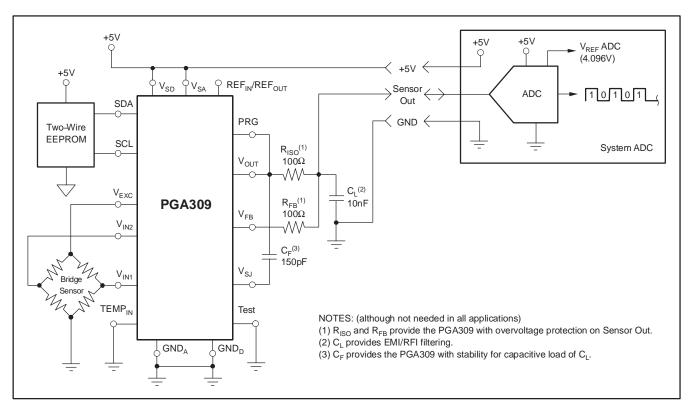

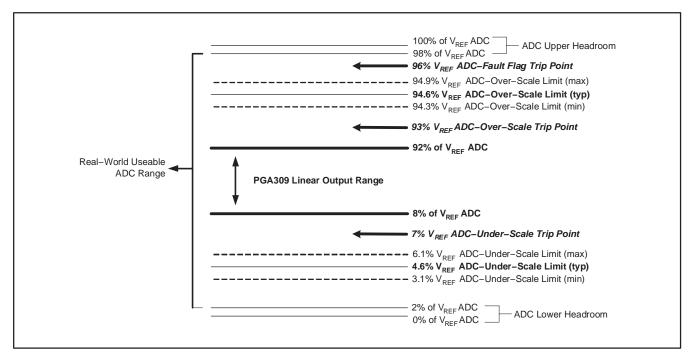

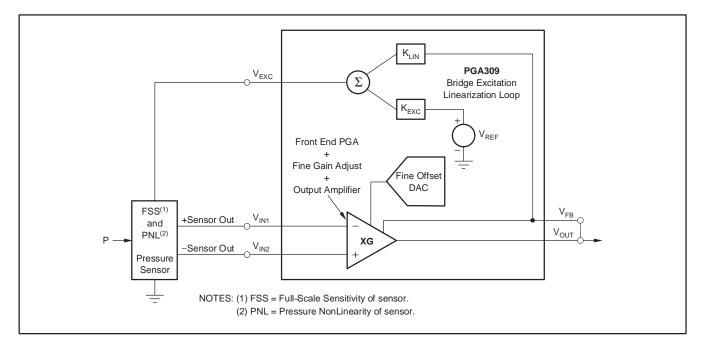

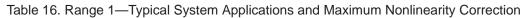

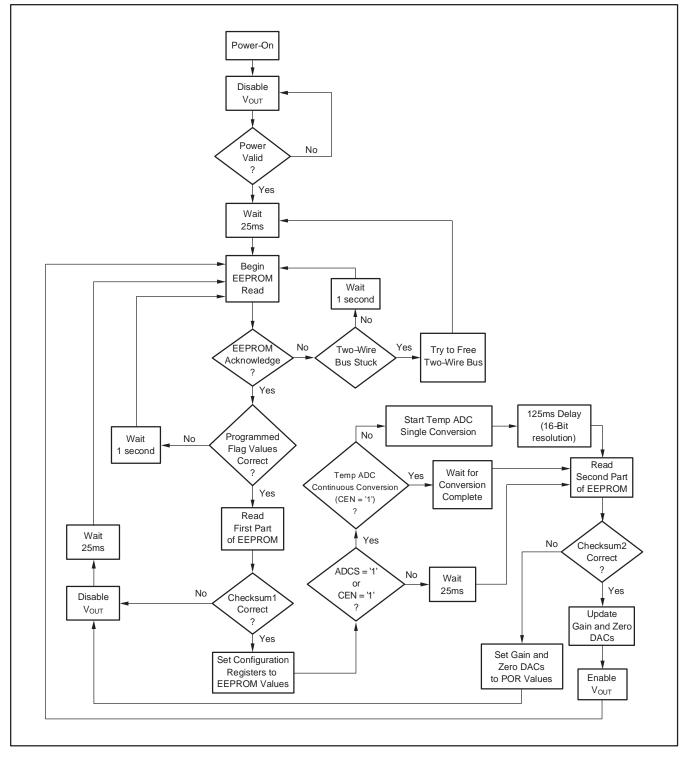

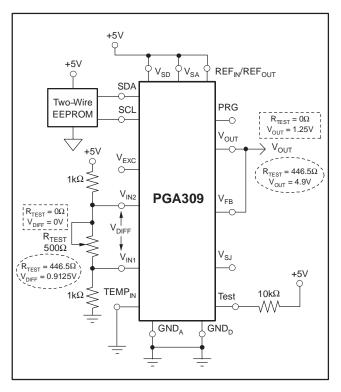

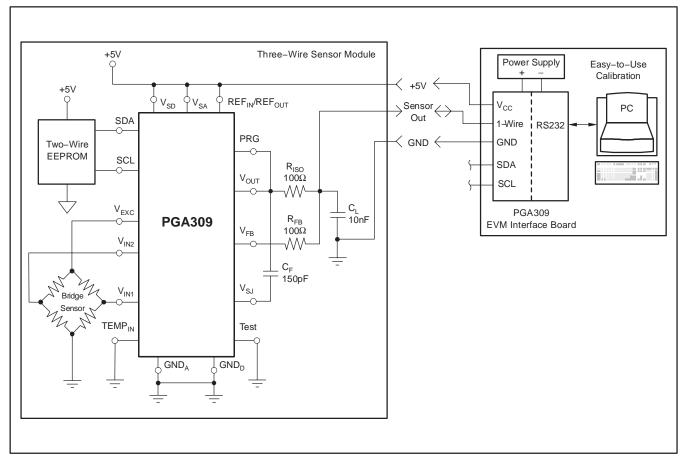

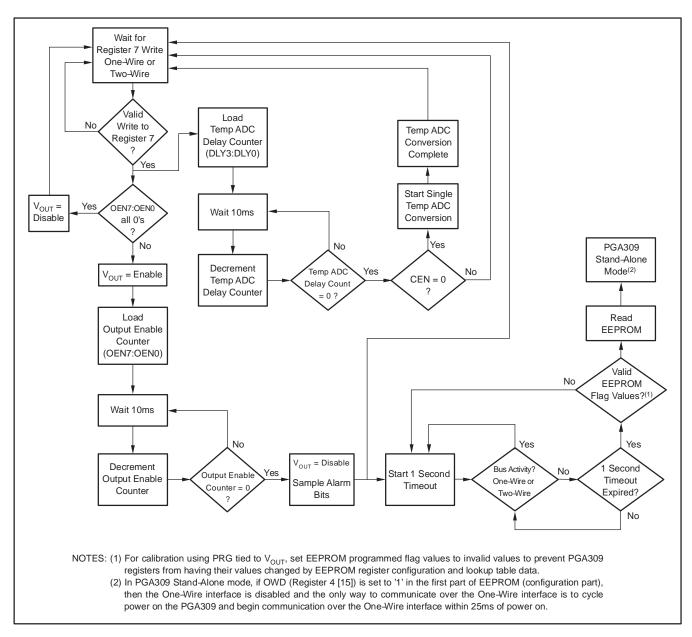

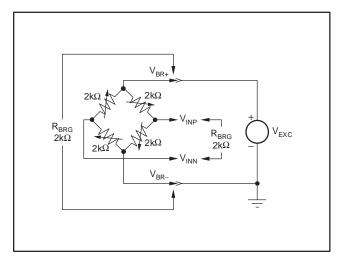

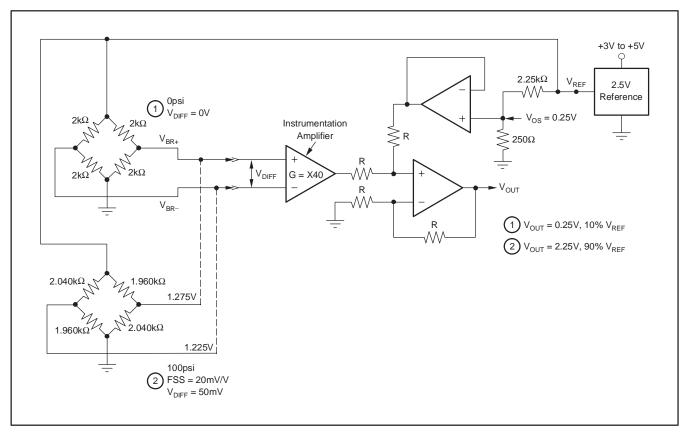

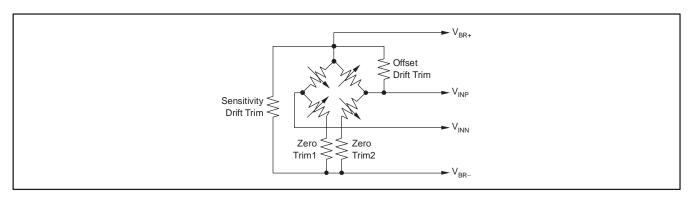

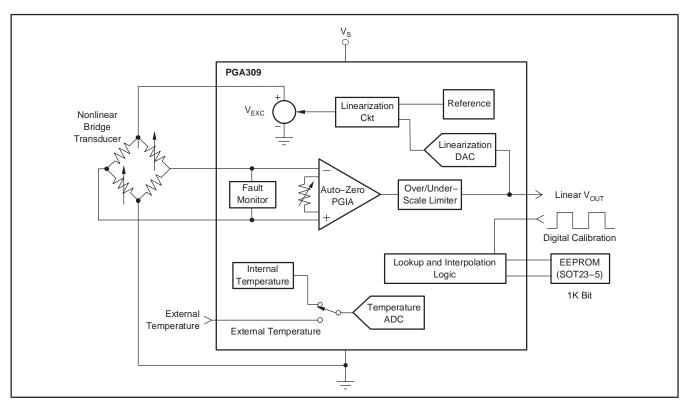

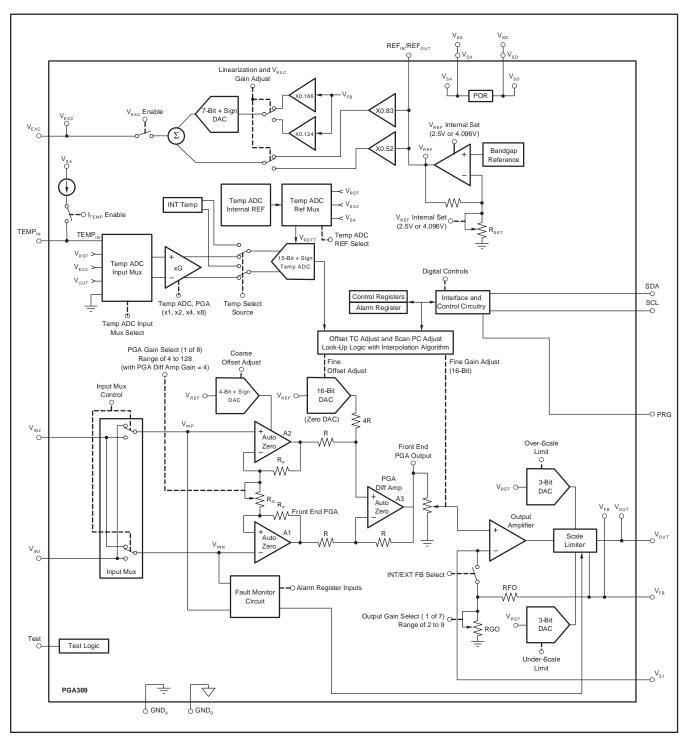

# FUNCTIONAL DESCRIPTION

The PGA309 is a smart programmable analog signal conditioner designed for resistive bridge sensor applications. It is a complete signal conditioner with bridge excitation, initial span and offset adjustment, temperature adjustment of span and offset, internal/external temperature measurement capability, output over-scale and under-scale limiting, fault detection, and digital calibration. The PGA309, in a calibrated sensor module, can reduce errors to the level approaching the bridge sensor repeatability. Figure 1 shows a block diagram of the PGA309. Following is a brief overview of each major function.

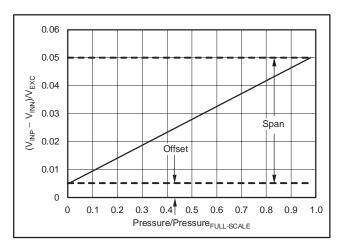

# SENSOR ERROR ADJUSTMENT RANGE

The adjustment capability of the PGA309 is summarized in Table 1.

| FSS (full-scale sensitivity)                                                                                                                                                                                | 1mV/V to 245mV/V       |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|--|--|

| Span TC                                                                                                                                                                                                     | Over ±3300ppmFS/°C(1)  |  |  |  |  |

| Span TC nonlinearity                                                                                                                                                                                        | <u>≥</u> 10%           |  |  |  |  |

| Zero offset                                                                                                                                                                                                 | ±200%FS <sup>(2)</sup> |  |  |  |  |

| Zero offset TC                                                                                                                                                                                              | Over ±3000ppmFS/°C(2)  |  |  |  |  |

| Zero offset TC nonlinearity                                                                                                                                                                                 | ≥ 10%                  |  |  |  |  |

| Sensor impedance Down to $200\Omega^{(3)}$                                                                                                                                                                  |                        |  |  |  |  |

| <ul> <li>(1) Depends on the temperature sensing scheme</li> <li>(2) Combined coarse and fine offset adjust</li> <li>(3) Lower impedance possible by using a dropping resistor in series with the</li> </ul> |                        |  |  |  |  |

(3) Lower impedance possible by using a dropping resistor in series with the bridge

Table 1. PGA309 Adjustment Capability

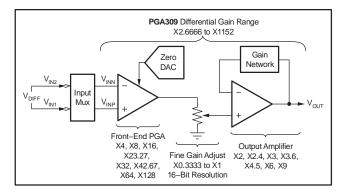

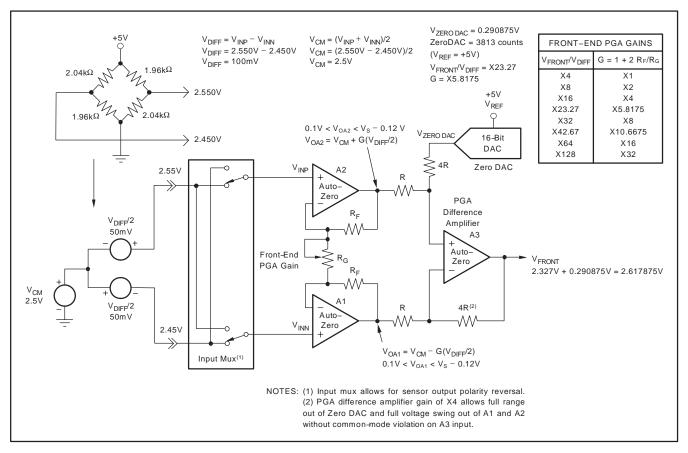

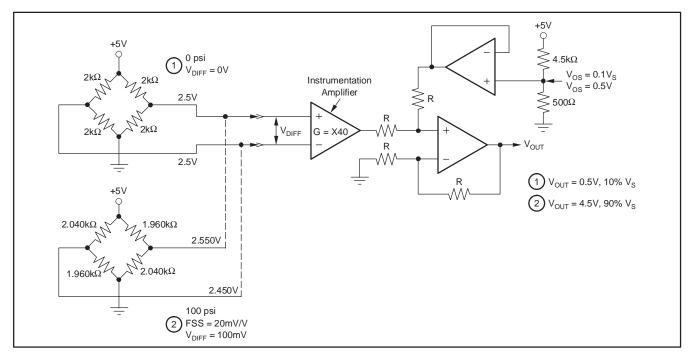

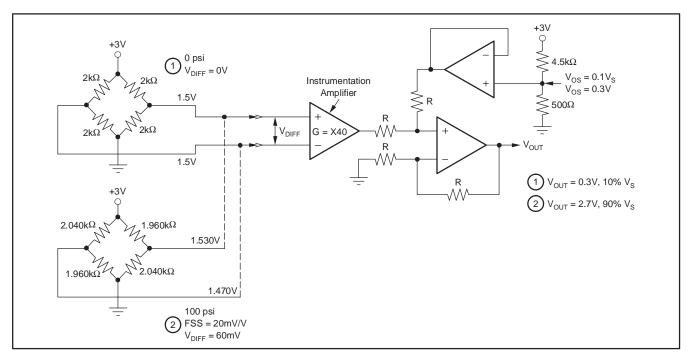

### GAIN SCALING

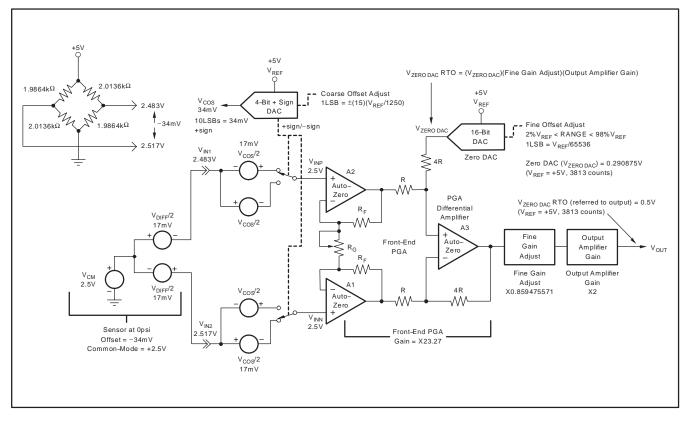

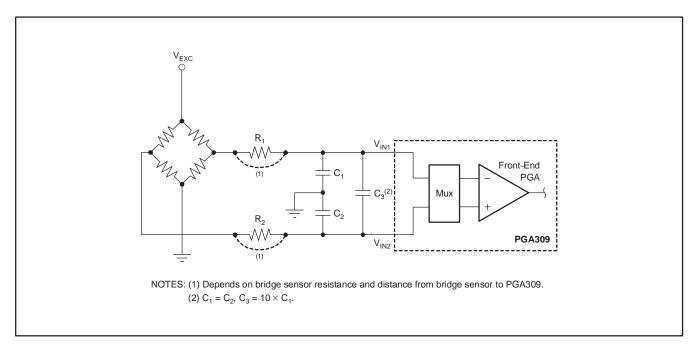

The core of the PGA309 is the precision low-drift and no 1/f noise front-end PGA. The overall gain of the front-end PGA + Output Amplifier can be adjusted from 2.7V/V to 1152V/V. The polarity of the inputs can be switched through the 2X2 input mux to accommodate sensors with unknown polarity output.

The front-end PGA provides initial coarse signal gain using a no 1/f noise, auto-zero instrumentation amplifier. The fine gain adjust is accomplished by the 16-bit attenuating gain digital-to-analog converter (DAC). The Gain DAC is controlled by the data in the Temperature Compensation Lookup Table driven by the temperature analog-to-digital converter (Temp ADC). In order to compensate for second-order drift nonlinearity, the span drift can be fitted to piecewise linear curves during calibration with the coefficients stored in an external nonvolatile EEPROM lookup table.

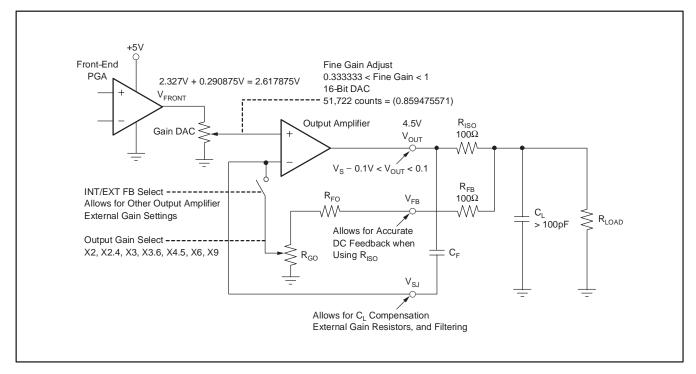

Following the fine gain adjust stage is the output amplifier that provides additional programmable gain. Two key output amplifier connections,  $V_{FB}$  and  $V_{SJ}$ , are brought out on the PGA309 for application flexibility. These connections allow for an accurate conditioned signal voltage while also providing a means for PGA309 output overvoltage and large capacitive loads for RFI/EMI filtering required in many end applications.

### OFFSET ADJUSTMENT

The sensor offset adjustment is performed in two stages. The input referred Coarse Offset Adjust DAC has approximately a  $\pm$ 60mV offset adjustment range for a selected V<sub>REF</sub> of 5V. The fine offset and the offset drift are canceled by the 16-bit Zero DAC that sums the signal with the output of the front-end instrumentation amplifier. Similar to the Gain DAC, the input digital values of the Zero DAC are controlled by the data in the Temperature Compensation Lookup Table, stored in external EEPROM, driven by the Temp ADC. The range of the Zero DAC is 0 to V<sub>REF</sub>.

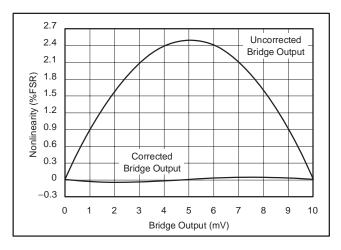

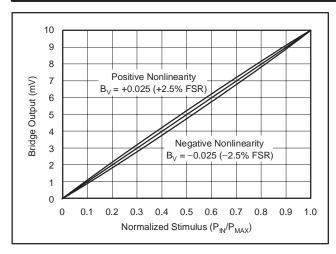

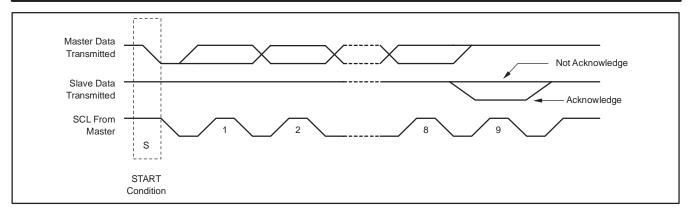

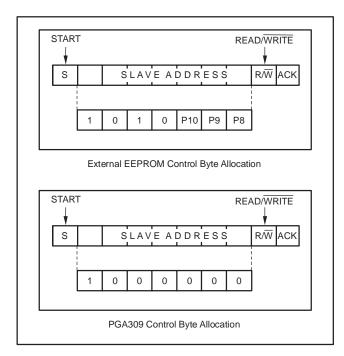

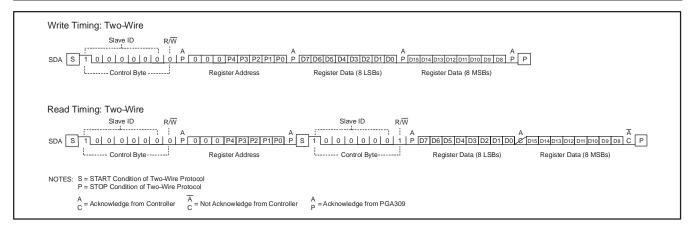

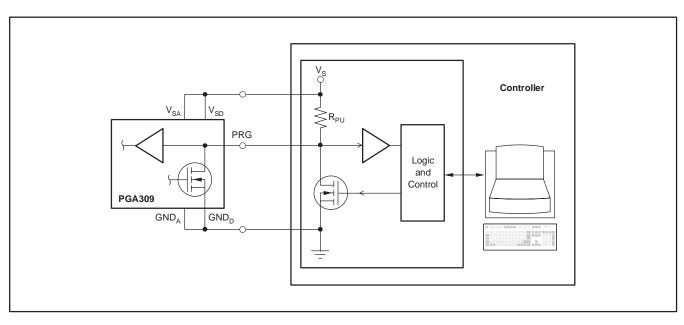

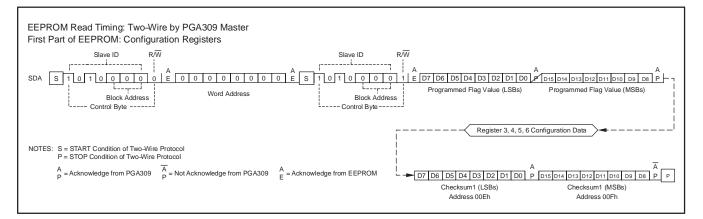

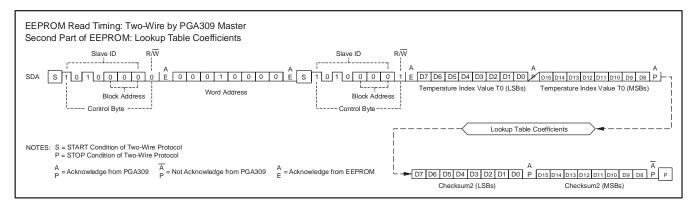

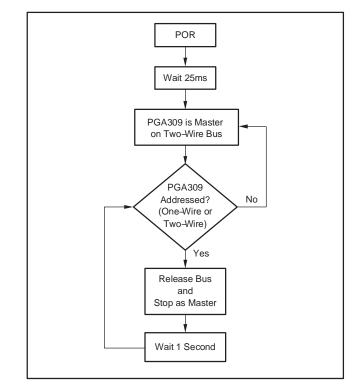

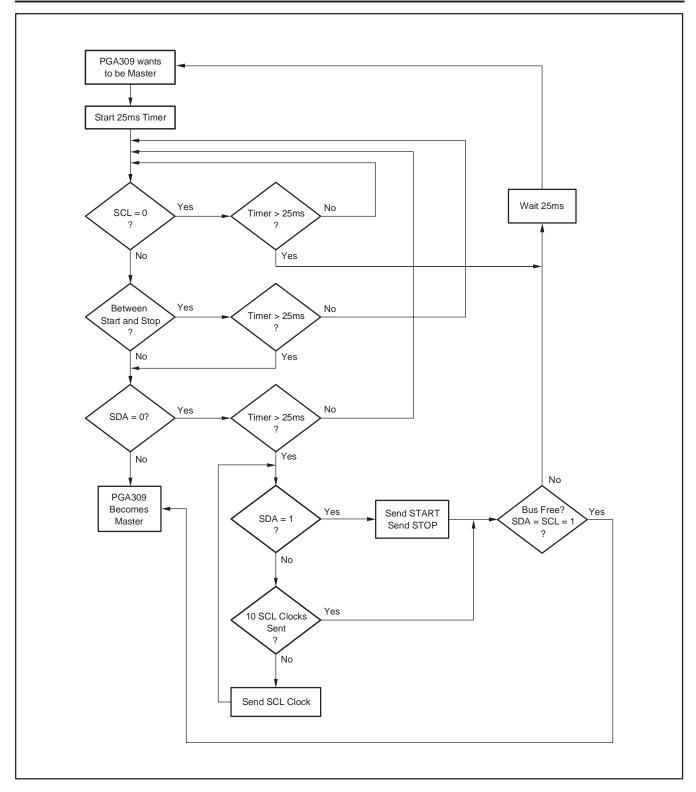

## VOLTAGE REFERENCE