# BIPOLAR ANALOG INTEGRATED CIRCUIT $\mu PC4091$

# J-FET INPUT LOW-OFFSET OPERATIONAL AMPLIFIER

The  $\mu$ PC4091 operational amplifier offers high input impedance, low offset voltage, high slew rate, and stable AC operating characteristics. NEC's unique high-speed PNP transistor (fr = 300 MHz) in the output stage solves the oscillation problem of current sinking with a large capacitive load. Zener-zap resistor trimming in the input stage produces excellent offset voltage and temperature drift characteristics.

# FEATURES

- Stable operation with 10000 pF capacitive load

- Low input offset voltage and offset voltage null capability

±2.5 mV (MAX.)

ORDERING INFORMATION

$\pm$ 7  $\mu$ V/°C (TYP.) temperature drift

· Very low input bias and offset currents

- Low noise :  $e_n = 19 \text{ nV} / \sqrt{\text{Hz}}$  (TYP.)

- Output short circuit protection

- High input impedance ... J-FET Input Stage

- Internal frequency compensation

- High slew rate: 15 V/µs (TYP.)

| Part Number | Package                     |

|-------------|-----------------------------|

| μPC4091C    | 8-pin plastic DIP (300 mil) |

| μPC4091G2   | 8-pin plastic SOP (225 mil) |

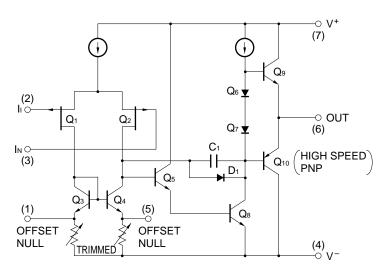

# EQUIVALENT CIRCUIT

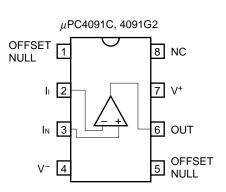

# PIN CONFIGURATION (Top View)

The information in this document is subject to change without notice.

# ABSOLUTE MAXIMUM RATINGS (TA = 25 °C)

| Parameter                                       |                              | Symbol    | Ratings           | Unit |

|-------------------------------------------------|------------------------------|-----------|-------------------|------|

| Voltage between $V^{+}$ and $V^{-Note 1}$       |                              | $V^*-V^-$ | -0.3 to +36       | V    |

| Differential Input Voltage                      |                              | Vid       | ±30               | V    |

| Input Voltage <sup>Note 2</sup>                 |                              | Vı        | V⁻–0.3 to V⁺ +0.3 | V    |

| Output Voltage <sup>Note 3</sup>                |                              | Vo        | V⁻–0.3 to V⁺ +0.3 | V    |

| Power Dissipation C Package <sup>Note 4</sup>   |                              | PT        | 350               | mW   |

|                                                 | G2 Package <sup>Note 5</sup> |           | 440               | mW   |

| Output Short Circuit Duration <sup>Note 6</sup> |                              |           | Indefinite        | sec  |

| Operating Ambient Temperature                   |                              | TA        | -20 to +80        | °C   |

| Storage Temperature                             |                              | Tstg      | -55 to +125       | °C   |

Notes 1. Reverse connection of supply voltage can cause destruction.

- 2. The input voltage should be allowed to input without damage or destruction. Even during the transition period of supply voltage, power on/off etc., this specification should be kept. The normal operation will establish when the both inputs are within the Common Mode Input Voltage Range of electrical characteristics.

- 3. This specification is the voltage which should be allowed to supply to the output terminal from external without damage or destructive. Even during the transition period of supply voltage, power on/off etc., this specification should be kept. The output voltage of normal operation will be the Output Voltage Swing of electrical characteristics.

- 4. Thermal derating factor is -5.0 mV/°C when operating ambient temperature is higher than 55 °C.

- 5. Thermal derating factor is -4.4 mV/°C when operating ambient temperature is higher than 25 °C.

- **6.** Pay careful attention to the total power dissipation not to exceed the absolute maximum ratings, Note 4 and Note 5.

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter                                    | Symbol         | MIN. | TYP. | MAX.  | Unit |

|----------------------------------------------|----------------|------|------|-------|------|

| Supply Voltage                               | V <sup>±</sup> | ±5   |      | ±16   | V    |

| Output Current                               | lo             |      |      | ±10   | mA   |

| Capacitive Load (Av = +1, $R_f = 0 \Omega$ ) | C∟             |      |      | 10000 | pF   |

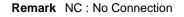

# OFFSET VOLTAGE NULL CIRCUIT

**Remark** The OFFSET NULL pins should be left open or connected to V<sup>-</sup> via a resistor as shown in the left figure. Don't connect to any lines other than V<sup>-</sup>, otherwise mulfunction, degradation, or failure may occur.

| Parameter                              | Symbol                    | Conditions                                                             | MIN.  | TYP.   | MAX. | Unit   |

|----------------------------------------|---------------------------|------------------------------------------------------------------------|-------|--------|------|--------|

| Input Offset Voltage                   | Vio                       | Rs ≤ 50 Ω                                                              |       | ±1     | ±2.5 | mV     |

| Input Offset Current <sup>Note 7</sup> | Ію                        |                                                                        |       | ±25    | ±100 | pА     |

| Input Bias Current <sup>Note 7</sup>   | Ів                        |                                                                        |       | 50     | 200  | pА     |

| Large Signal Voltage Gain              | Av                        | $R_{\text{L}} \geq 2 \; k\Omega$ , $V_{\text{O}} = \pm 10 \; \text{V}$ | 25000 | 200000 |      |        |

| Supply Current                         | Icc                       | Io = 0 A                                                               |       | 2.5    | 3.4  | mA     |

| Common Mode Rejection Ratio            | CMR                       |                                                                        | 70    | 100    |      | dB     |

| Supply Voltage Rejection Ratio         | SVR                       |                                                                        | 70    | 100    |      | dB     |

| Output Voltage Swing                   | Vom                       | $R_L \ge 10 \ k\Omega$                                                 | ±12   | +14.0  |      | V      |

|                                        |                           |                                                                        |       | -13.3  |      |        |

|                                        |                           | $R_L \ge 2 \ k\Omega$                                                  | ±10   | +13.5  |      | V      |

|                                        |                           |                                                                        |       | -12.8  |      |        |

| Common Model Input Voltage Range       | VICM                      |                                                                        | ±11   | +14    |      | V      |

|                                        |                           |                                                                        |       | -12    |      |        |

| Slew Rate                              | SR                        | A∨ = 1                                                                 |       | 15     |      | V/µs   |

| Unity Gain Frequency                   | funity                    |                                                                        |       | 4      |      | MHz    |

| Input Equivalent Noise Voltage Density | en                        | Rs = 100 Ω, f = 1 kHz                                                  |       | 19     |      | nV/√Hz |

| Input Offset Voltage                   | Vio                       | $Rs \leq 50~\Omega,~T_{\text{A}}$ = –20 to +70 °C                      |       |        | ±5   | mV     |

| Average Vio Temperature Drift          | $\Delta V$ io/ $\Delta T$ | T <sub>A</sub> = −20 to +70 °C                                         |       | ±7     |      | μV/°C  |

| Input Offset Current <sup>Note 7</sup> | Ію                        | T <sub>A</sub> = −20 to +70 °C                                         |       |        | ±2   | nA     |

| Input Bias Current <sup>Note 7</sup>   | Ів                        | T <sub>A</sub> = −20 to +70 °C                                         |       |        | 7    | nA     |

# ELECTRICAL CHARACTERISTICS (TA = 25 °C, V<sup>±</sup> = ±15 V)

**Notes 7.** Input bias currents flow into IC. Because each currents are gate leak current of P-channel J-FET on input stage. And that are temperature sensitive. Short time measuring method is recommendable to maintain the junction temperature close to the operating ambient temperature.

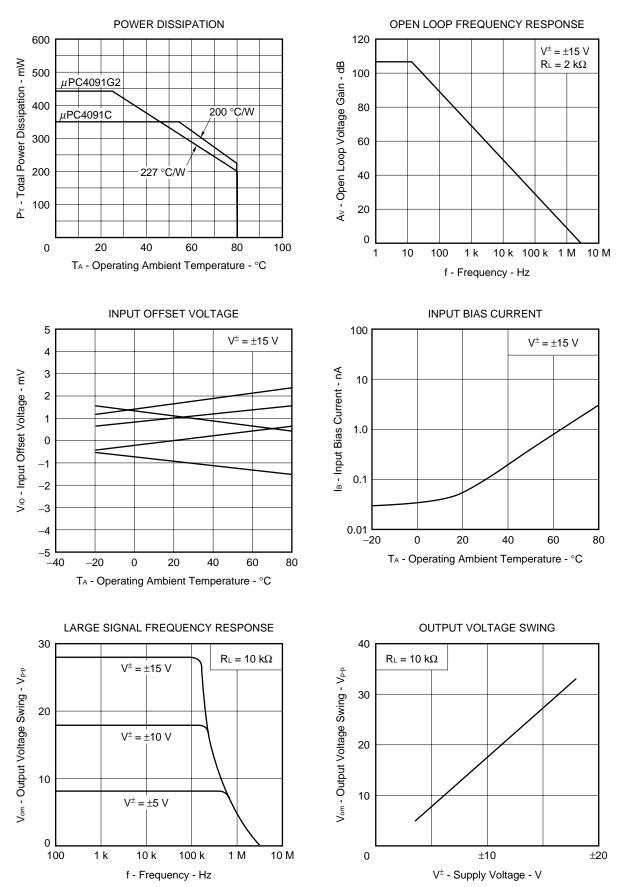

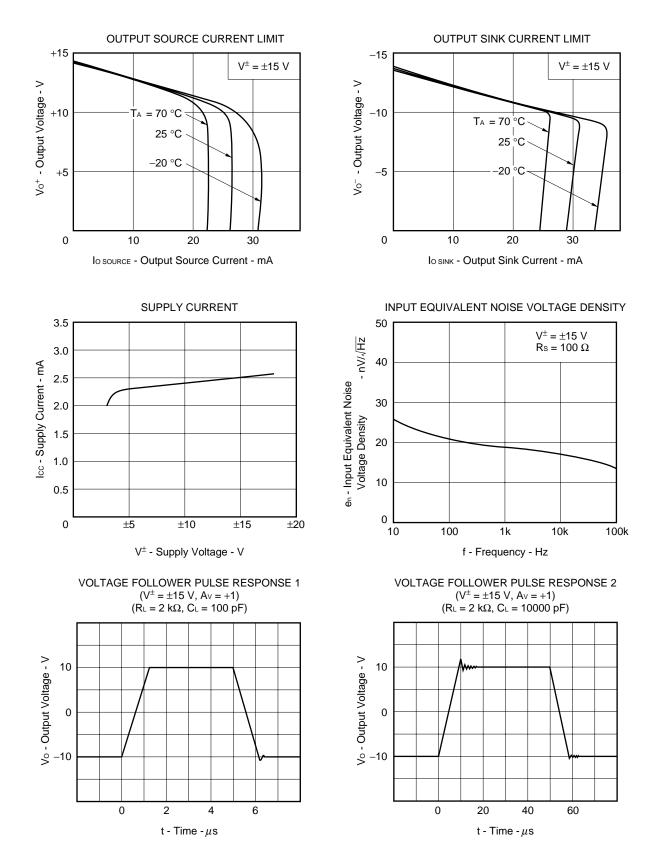

# TYPICAL PERFORMANCE CHARACTERISTICS (TA = 25 °C, TYP.)

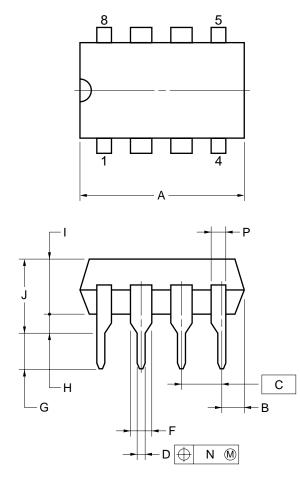

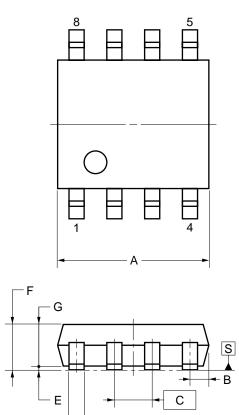

# PACKAGE DRAWINGS

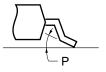

# 8PIN PLASTIC DIP (300 mil)

#### NOTES

- 1) Each lead centerline is located within 0.25 mm (0.01 inch) of its true position (T.P.) at maximum material condition.

- 2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS            | INCHES                    |

|------|------------------------|---------------------------|

| А    | 10.16 MAX.             | 0.400 MAX.                |

| В    | 1.27 MAX.              | 0.050 MAX.                |

| С    | 2.54 (T.P.)            | 0.100 (T.P.)              |

| D    | 0.50±0.10              | $0.020^{+0.004}_{-0.005}$ |

| F    | 1.4 MIN.               | 0.055 MIN.                |

| G    | 3.2±0.3                | 0.126±0.012               |

| Н    | 0.51 MIN.              | 0.020 MIN.                |

| I    | 4.31 MAX.              | 0.170 MAX.                |

| J    | 5.08 MAX.              | 0.200 MAX.                |

| К    | 7.62 (T.P.)            | 0.300 (T.P.)              |

| L    | 6.4                    | 0.252                     |

| М    | $0.25^{+0.10}_{-0.05}$ | $0.010^{+0.004}_{-0.003}$ |

| N    | 0.25                   | 0.01                      |

| Р    | 0.9 MIN.               | 0.035 MIN.                |

| R    | 0~15°                  | 0~15°                     |

|      |                        | P8C-100-300B,C-1          |

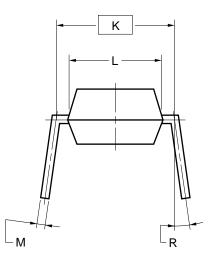

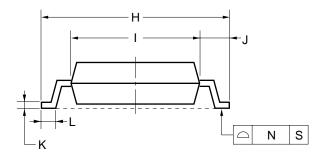

# 8 PIN PLASTIC SOP (225 mil)

detail of lead end

#### NOTE

-

Each lead centerline is located within 0.12 mm of its true position (T.P.) at maximum material condition.

MM

D⊕

| ITEM | MILLIMETERS                           |

|------|---------------------------------------|

| А    | $5.2^{+0.17}_{-0.20}$                 |

| В    | 0.78 MAX.                             |

| С    | 1.27 (T.P.)                           |

| D    | $0.42\substack{+0.08\\-0.07}$         |

| E    | 0.1±0.1                               |

| F    | 1.59±0.21                             |

| G    | 1.49                                  |

| Н    | 6.5±0.3                               |

| 1    | 4.4±0.15                              |

| J    | 1.1±0.2                               |

| к    | $0.17\substack{+0.08 \\ -0.07}$       |

| L    | 0.6±0.2                               |

| М    | 0.12                                  |

| N    | 0.10                                  |

| Р    | $3^{\circ}^{+7^{\circ}}_{-3^{\circ}}$ |

|      | S8GM-50-225B-5                        |

# **RECOMMENDED SOLDERING CONDITIONS**

When soldering this product, it is highly recommended to observe the conditions as shown below. If other soldering processes are used, or if the soldering is performed under different conditions, please make sure to consult with our sales offices.

For more details, refer to our document "SEMICONDUCTOR DEVICE MOUNTING TECHNOLOGY MANUAL"(C10535E).

### **Type of Surface Mount Device**

#### µPC4091G2: 8-pin plastic SOP (225 mil)

| Process                | Conditions                                                                                                                                                                                  | Symbol    |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Infrared Ray Reflow    | Peak temperature: 230 °C or below (Package surface temperature),<br>Reflow time: 30 seconds or less (at 210 °C or higher),<br>Maximum number of reflow processes: 1 time.                   | IR30-00-1 |

| Vapor Phase Soldering  | Peak temperature: 215 °C or below (Package surface temperature),<br>Reflow time: 40 seconds or less (at 200 °C or higher),<br>Maximum number of reflow processes: 1 time.                   | VP15-00-1 |

| Wave Soldering         | Solder temperature: 260 °C or below, Flow time: 10 seconds or less,<br>Maximum number of flow processes: 1 time,<br>Pre-heating temperature: 120 °C or below (Package surface temperature). | WS60-00-1 |

| Partial Heating Method | Pin temperature: 300 °C or below,<br>Heat time: 3 seconds or less (Per each side of the device).                                                                                            | -         |

# Caution Apply only one kind of soldering condition to a device, except for "partial heating method", or the device will be damaged by heat stress.

Type of Through-hole Device

### µPC4091C: 8-pin plastic DIP (300 mil)

| Process                | Conditions                                    |

|------------------------|-----------------------------------------------|

| Wave Soldering         | Solder temperature: 260 °C or below,          |

| (only to leads)        | Flow time: 10 seconds or less.                |

| Partial Heating Method | Pin temperature: 300 °C or below,             |

|                        | Heat time: 3 seconds or less (per each lead). |

Caution For through-hole device, the wave soldering process must be applied only to leads, and make sure that the package body does not get jet soldered.

# **REFERENCE DOCUMENTS**

| QUALITY GRADES ON NEC SEMICONDUCTOR DEVICES                 | C11531E  |

|-------------------------------------------------------------|----------|

| SEMICONDUCTOR DEVICE MOUNTING TECHNOLOGY MANUAL             | C10535E  |

| NEC IC PACKAGE MANUAL (CD-ROM)                              | C13388E  |

| GUIDE TO QUALITY ASSURANCE FOR SEMICONDUCTOR DEVICES        | MEI-1202 |

| SEMICONDUCTORS SELECTION GUIDE                              | X10679E  |

| NEC SEMICONDUCTOR DEVICE RELIABILITY/QUALITY CONTROL SYSTEM | IEI-1212 |

| (STANDARD LINEAR IC)                                        |          |

[MEMO]

[MEMO]

[MEMO]

NEC

The application circuits and their parameters are for reference only and are not intended for use in actual design-ins.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

M4 96.5