# MT93L04A

September 2001

# **128-Channel Voice Echo Canceller**

ISSUE 2

Preliminary Information

## Features

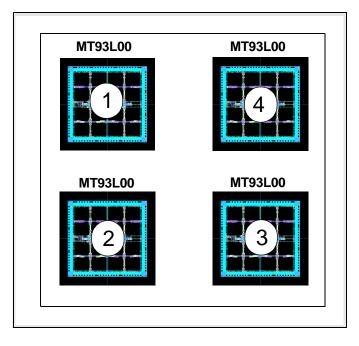

- MT93L04 is a Multi-chip Module (MCM) consisting of 4 MT93L00 devices thus providing 128 channels of 64 msec Echo Cancellation.

- Each device (MT93L00) is independent of the each other.

- Each device has the capability of cancelling echo over 32 channels.

- The MCM module provides more than 40% board space savings.

- Each device (MT93L00) can be programmed independently in any mode e.g back to back or extended delay to provide capability of cancelling different echo tails.

- Each device has the same Jtag identification code.

# Applications

- Voice over IP network gateways

- Voice over ATM, Frame Relay

- T1/E1/J1 multichannel echo cancellation

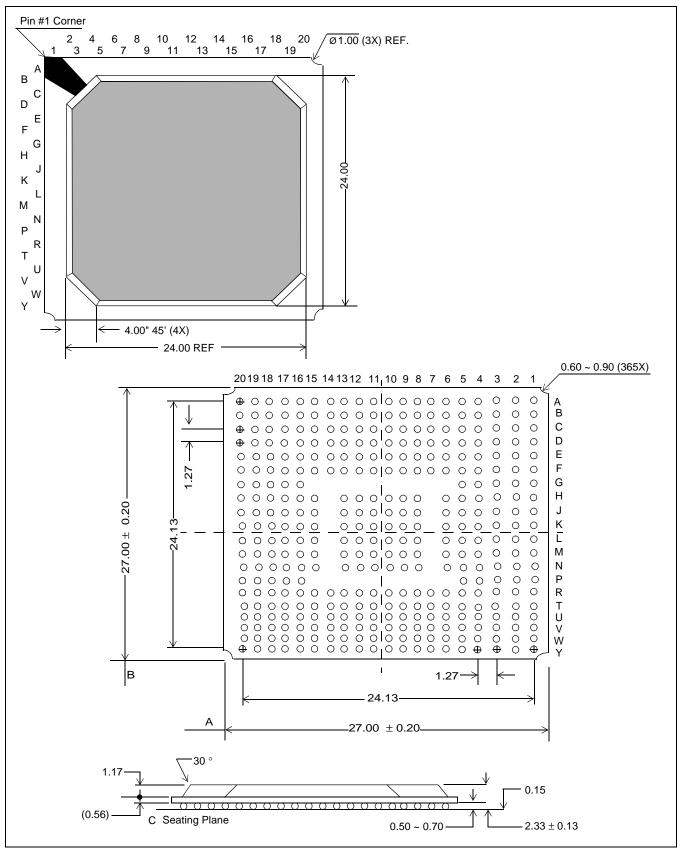

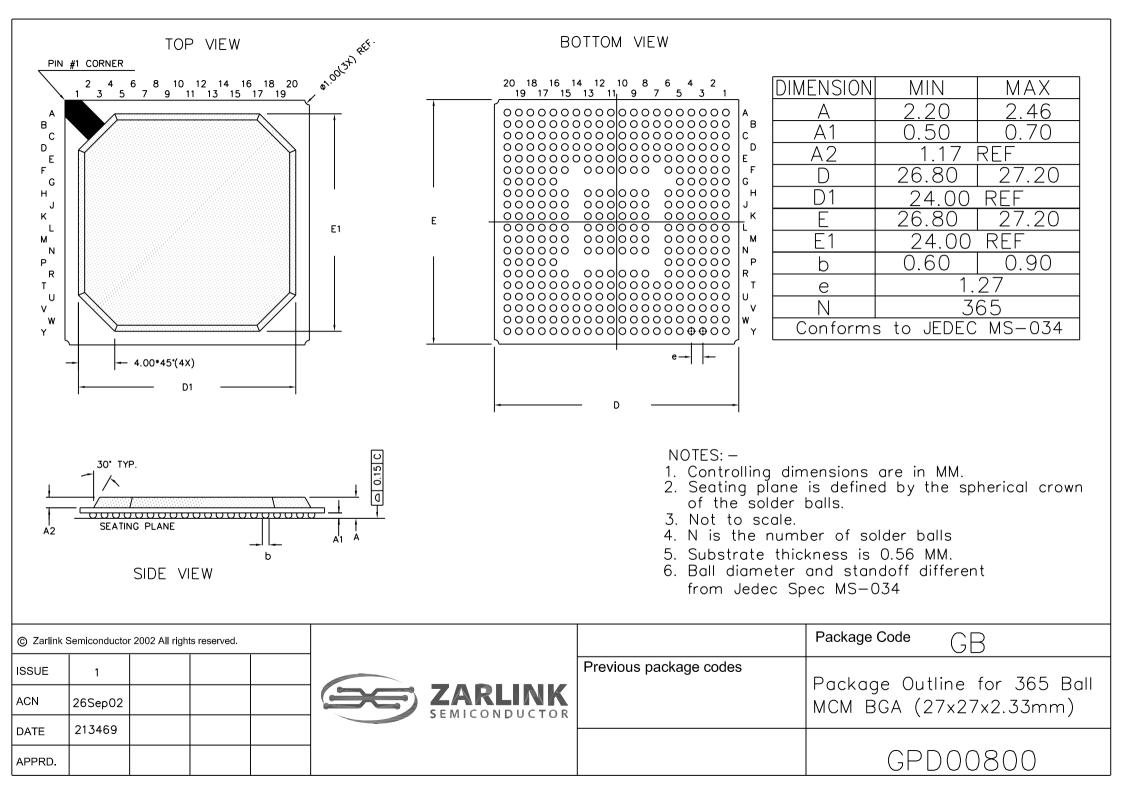

Ordering Information MT93L04AG 365 Ball BGA 40°C to +85°C

- Wireless base stations

- Echo Canceller pools

- DCME, satellite and multiplexer systems

# Description

DS5524

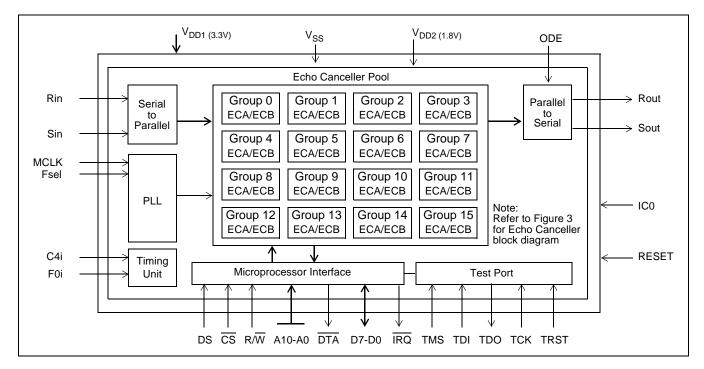

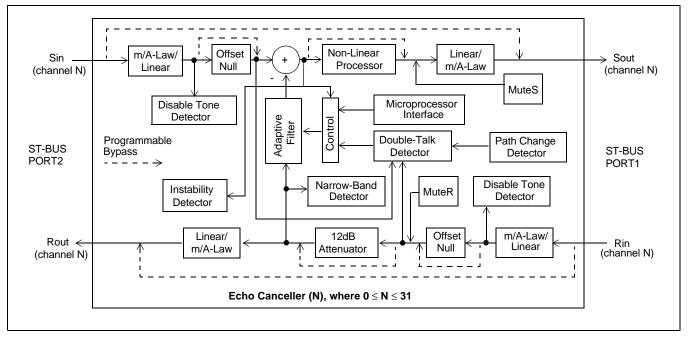

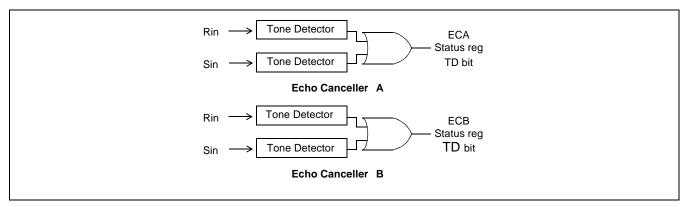

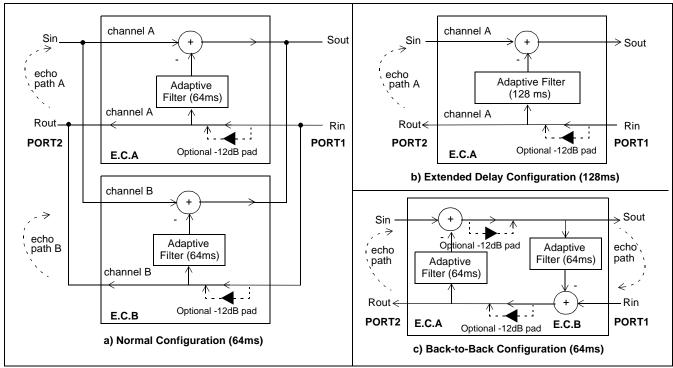

The MT93L04 Voice Echo Canceller implements a cost effective solution for telephony voice-band echo cancellation conforming to ITU-T G.168 requirements. The MT93L04 architecture contains 64 groups of two echo cancellers (ECA and ECB) which can be configured to provide two channels of 64 milliseconds or one channel of 128 milliseconds echo cancellation. This provides 128 channels of 64 milliseconds to 64 channels of 128 milliseconds echo cancellation or any combination of the two configurations. The MT93L04 supports ITU-T G.165 and G.164 tone disable requirements.

MT93L04 is MULTI-CHIP module consiting of 4 MT93L00 devices

Figure 1 - Functional Block Diagram for single MT93L00 (32 channels)

## Features of Single MT93L00

- Independent multiple channels of echo cancellation; from 32 channels of 64ms to 16 channels of 128ms with the ability to mix channels at 128ms or 64ms in any combination

- Independent Power Down mode for each group of 2 channels for power management

- ITU-T G.165 and G.168 compliant

- Field proven, high quality performance

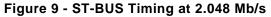

- Compatible to ST-BUS and GCI interface at 2Mb/s serial PCM

- PCM coding, μ/A-Law ITU-T G.711 or sign magnitude

- Per channel Fax/Modem G.164 2100Hz or G.165 2100Hz phase reversal Tone Disable

- Per channel echo canceller parameters control

- Transparent data transfer and mute

- Fast reconvergence on echo path changes

- Non-Linear Processor with high quality subjective performance

- Protection against narrow band signal divergence

- Offset nulling of all PCM channels

- 10 MHz or 20 MHz master clock operation

- 3.3 V pads and 1.8V Logic core operation with 5-Volt tolerant inputs

- No external memory required

- Non-multiplexed microprocessor interface

- IEEE-1149.1 (JTAG) Test Access Port

| ^        | 1         | 2                   | 3                   | 4                  | 5                   | 6             | 7          | 8              | 9               | 10              | 11              | 12                 | 13                    | 14             | 15         | 16                    | 17                  | 18                  | 19         | 20                    | - |

|----------|-----------|---------------------|---------------------|--------------------|---------------------|---------------|------------|----------------|-----------------|-----------------|-----------------|--------------------|-----------------------|----------------|------------|-----------------------|---------------------|---------------------|------------|-----------------------|---|

| <u>م</u> | Tsig(12)_ |                     | SC_in_d1            |                    | FOIB_d1             |               | sig(7)_d1  |                | sig(1)_d1       | O di            | Fsel_d4         | O <sup>Ts</sup>    | ig(14)_d4             | 0              | SC_in_d4   | O                     | 6C_set_d4           |                     | Sout_d4    | 0                     | A |

| в        | Tsig(15)_ |                     | SC_reset            |                    | C_set_d1            | O<br>Sin d1   | ODE_d1     | 0              | Tsig(2)_d1      | O               | DT1_d4          |                    | TM2 d4                |                | _mclk_d4   | OIB d4                | Sin d4              |                     | ig(6)_d4   | )<br>(2) d4           | в |

| с        | TM2_d1    | 1<br>Sig(13) d      | Tsig(9)_d           | Tsia(8) d1         | C_en_d1             | O<br>C4IB     | Sout_d1    | O<br>Tsig(5) d | 1 sig(3)_a1     | O<br>A(9) d1    |                 | Ts<br>(12) d4      | sig(8)_d4<br>0<br>1 S | O<br>C_en_d4   | 0          | Rout_d4               | 0                   | D0 d4               | Fsig(3)_d4 | O<br>sig(1)_d4        | с |

| D        | Fsel_d1   | O<br>Tm1_d1         | Tsig(10)_           | d1<br>             | 0                   | O<br>Rin_d1   |            | O<br>A(7) d1   |                 | O<br>A(8) d1    | Tm1_d4          | O<br>Tsig(9)_d     |                       | O<br>Step_d4   |            | _d4<br>O<br>PLLVSS2   |                     | O<br>Tsig(4)_d4     |            | 4<br>A_IC1_d4         | D |

| Е        | Halt_d1   | O<br>Mclk_d         | Tsig(14)_c          | 51<br>SG1(d1)      | D(7)_d              | 1<br>A(1)_d1  | A(3)_d1    | O<br>A(5)_d1   | A_IC1_d1        | O<br>A(6)_d1    | Tsig(13)_d      | 4<br>              | Halt_d4               |                | AT1_d4     | O<br>TMS_d            | Trstb_c             | I4<br>A_IC2_0       | A(10)_d4   | O<br>A(9)_d4          | E |

| F        |           | _d1<br>O<br>Step_d1 | DT1_d1              | O<br>D(5)_d        | D(6)_d              | 1             |            |                | $\bigcirc$      | O<br>Vdd2       |                 |                    | O<br>Vdd1             |                |            | O<br>TCK_d4           |                     | _d4<br>O<br>A(8)_d4 | A(7)_d4    | A(6)_d4               | F |

| G        |           |                     |                     | • /=               |                     |               |            | Vee            | Vee             | Vee             | 1/22            |                    | 1/20                  |                |            | O<br>Test_en          | IRQB_d4<br>O<br>_d4 | O<br>A(5)_d4        | 0          | O<br>A(3)_d4          | G |

| н        | 0         |                     | 0                   | _d1<br>            | Õ                   | Vdd1          |            | Vss            | Vss             | Vss             | Vss             | Vss                | Vss<br>O              |                | Vdd1       | O<br>Dsb_d4           | R/WB_d4             | O (0) d4            | 0          | (2) d4                | н |

| J        | 0         |                     | 0                   | TMS_d1             | 0                   | $\circ$       |            | Vss            | Vss             | Vss             | Vss             | Vss                | Vss                   |                | Vdd2       | (1)_d4                | D(7)_d4             | ()<br>D(6) d4       | 0          | O<br>D(4)_d4          | J |

| к        |           |                     | CSB_d1<br>O<br>B_d1 | DTAB_d             | D(1)_d1             | Vdd2          |            | Vss            | Vss             | Vss             | Vss             | Vss                | Vss                   |                | Vdd2       | O<br>Csh. di          |                     |                     | D(2)_d4    | D(3) d4               | к |

| L        | Sout_d2   |                     | C4IB_               |                    | SC_en_d             |               |            | Vss            | Vss<br>O<br>Vss | Vss<br>O<br>Vss | Vss<br>O<br>Vss | Vss<br>O<br>Vss    | Vss<br>O<br>Vss       |                | Vdd2       |                       | C4IB_d3             |                     | Rin_d3     | 0                     | L |

| М        | SC_in_d   | 2<br>SC_reset       | SC_Fclk_            | d2 S<br>Tsig(8)_d2 | T_mclk_d            | 2 Vdd2        |            | Vss            | 0               | 0               | 0               | 0                  | 0                     |                | $\circ$    |                       |                     | C<br>Tsig(6) d      | 0          |                       | м |

| N        | SC_set_d  | FOIB_d              | Rin_d2<br>2         | Rout_d2            | Ode_d2              | Vdd1          |            | Vss            | Vss             | Vss             | Vss             | Vss                | Vss                   |                | Vdd1       | ST mclk               | SC_set_d3           | Tsig(4)_d3          |            | Rout_d3               | N |

| Ρ        | 0         | O<br>Tsig(10)_      | _d2                 | _d2<br>            |                     |               |            |                |                 |                 |                 |                    |                       |                |            | SC_in_d3              | SC_en_d3            | A_IC2_0             | I sig(1)_0 | d3<br>O<br>Tsig(2)_d3 | Р |

| R        | 0.        | ()<br>Tsig(12)_     | _d2 ()              | O<br>SG1_d2        | $\bigcirc$          | $\bigcirc$    |            |                | 0               | 0               |                 | Vdd2               | Vdd1                  |                |            | SC_reset_             | A(10)_d3<br>_d3     | A(8)_d3             | A_ICI_d    | 3<br>Tsig(0)_d3       | R |

| т        | 0         | TM1 d               | , O                 | Tsig(5)_d2         | 0.                  | Tsig(1)_d2    | 0          | A IC1 d        | 2               | A(5) d2         | 0               | Fsel d3            | 0                     | sig(13) d      | , O        | 13 S(<br>Tsig(10)_c   | <sub>із</sub> О     | A(4) d3             | 0          | O<br>A(9) d3          | т |

| U        | Tsig(15)_ | d2<br>Mclk_d2       | PLLVSS              | 2_d2<br>Tsig(2)_d  | lrqb_d2<br>d2       | DTAB_d        | 2 Tsig(0)_ | _d2<br>A(9)_d2 | A(0)_d2         | O<br>A(4)_d2    | Mclk_d3         | AT1_d3             | Tm2_d3                | )<br>sig(14)_d | Tsig(12)_0 | i3<br>O<br>Tsig(9)_d3 | Tsig(8)_d           | A(0)_d3             | A(5)_d3    | O<br>A(6)_d3          | U |

| v        | DT1_d2    |                     | AT1_d2              |                    | Test_en             | _d2<br>R/WB_d | 2          | O<br>D(7)_d2   | A(1)_d2         | O<br>A(7)_d2    | DT1_d           | 3<br>Opllvss2_     | d3                    | O<br>Test_en_  | R/WB_d     | l3<br>D(2)_d3         | D(6)_d3             | O<br>D(7)_d3        | A(1)_d3    | O<br>A(3)_d3          | v |

| w        | Fsel_d2   |                     |                     | O<br>Trstb_d2      | DSB_d2              | O<br>D(0)_d2  | D(3)_d2    | O<br>D(6)_d2   | A(2)_d2         | O<br>A(8)_d2    | SG1_d3          | PLLVDD_            | TMS_d3                | TCK_d3         | RESET      | B_d3<br>O<br>CSB_d3   | D(0)_d3             | O<br>D(3)_d3        | D(5)_d3    | O<br>A(2)_d3          | w |

| Y        |           | 1_d2<br>O<br>TDI_d2 | Tck_d2              |                    | Csb_d2<br>O<br>B_d2 | O<br>D(1)_d2  | D(4)_d2    | O<br>D(5)_d2   | A(3)_d2         | O<br>A(10)_d2   | TM1_d3          | B<br>O<br>PLLVSS1_ | Halt_d                | TDO_d3         | Trstb_d    | IRQB_d3               | DSB_d3              | O<br>DTAB_d         | D(1)_d3    | O<br>D(4)_d3          | Y |

|          | 1         | 2<br>^              | 3                   | 4                  | 5                   | 6             | 7          | 8              | 9               | 10              | 11              | 12                 | 13                    | 14             | 15         | 16                    | 17                  | 18                  | 19         | 20                    | - |

|          |           | $\Box$              | - A1                | corner             | is iden             | tified b      | y meta     | allized        | markin          | gs.             |                 |                    |                       |                |            |                       |                     |                     |            |                       |   |

Figure 2 - 365 Ball BGA

# **Pin Description**

| Signal Name             | Signal Type    | BGA Ball #                                                                                                                                                      | Signal Description                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD1</sub> = 3.3V | Power          | R6, R8, R13, R15, N15,H15,<br>F15,F13,F8,F6,H6,N6, P6,                                                                                                          | Positive Power Supply. Nominally 3.3 volt.<br>V <sub>DD1</sub> = I/O Voltage                                                                                                                                                                                                                                                                                                            |

| V <sub>DD2</sub> = 1.8V | Power          | R9,R10,R11,R12,M15,<br>L15,K15,J15,F12,F11,<br>F10,F9,J6, K6, L6,M6,                                                                                            | Positive Power Supply. Nominally 1.8 volt.<br>V <sub>DD2</sub> = Core Voltage                                                                                                                                                                                                                                                                                                           |

| VSS                     | Power          | H8,H9,H10,H11,H12, H13,<br>J8, J9,J10,J11,<br>J12,J13,K8,K9,K10,K11,K1<br>2,K13 L8,L9,L10,<br>L11,L12,L13,M8,M9,M10,M<br>11,M12, M13, N8,<br>N9,N10,N11,N12,N13 | Ground                                                                                                                                                                                                                                                                                                                                                                                  |

| DEVICE 1                |                |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                         |

| TMS_d1                  | User Signal    | J4                                                                                                                                                              | <b>Test Mode Select (3.3V Input).</b> JTAG signal that controls the state transitions of the TAP controller. This pin is pulled high by an internal pull-up when not driven.                                                                                                                                                                                                            |

| TDI_d1                  | User Signal    | J3                                                                                                                                                              | <b>Test Serial Data In (3.3V Input).</b> JTAG serial test instructions and data are shifted in on this pin. This pin is pulled high by an internal pull-up when not driven.                                                                                                                                                                                                             |

| TDO_d1                  | User Signal    | J2                                                                                                                                                              | <b>Test Serial Data Out (Output).</b> JTAG serial data<br>is output on this pin on the falling edge of TCK.<br>This pin is held in high impedance state when<br>JTAG scan is not enabled.                                                                                                                                                                                               |

| TCK_d1                  | User Signal    | J1                                                                                                                                                              | <b>Test Clock (3.3V Input).</b> Provides the clock to the JTAG test logic.                                                                                                                                                                                                                                                                                                              |

| TRSTB_d1                | User Signal    | K1                                                                                                                                                              | <b>Test Reset (3.3V Input).</b> Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be pulsed low on power-up or held low, to ensure that the MT93L00 is in the normal functional mode. This pin is pulled by an internal pull-down when not driven.                                                                        |

| Test_En_d1              | ICO            | H1                                                                                                                                                              | Internal Connection. Connected to VSS for normal operation                                                                                                                                                                                                                                                                                                                              |

| RESETB_d1               | User<br>Signal | K2                                                                                                                                                              | Device Reset (Schmitt Trigger Input). An active<br>low resets the device and puts the MT93L00 into a<br>low-power stand-by mode.<br>When the RESET pin is returned to logic high<br>and a clock is applied to the MCLK pin, the<br>device will automatically execute initialization<br>routines, which preset all the Control and Status<br>Registers to their default power-up values. |

| Signal Name | Signal Type | BGA Ball # | Signal Description                                                                                                                                                                                                                                                |

|-------------|-------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQB_d1     | User Signal | J5         | <b>Interrupt Request (Open Drain Output).</b> This output goes low when an interrupt occurs in any channel. IRQ returns high when all the interrupts have been read from the Interrupt FIFO Register. A pull-up resistor (1K typical) is required at this output. |

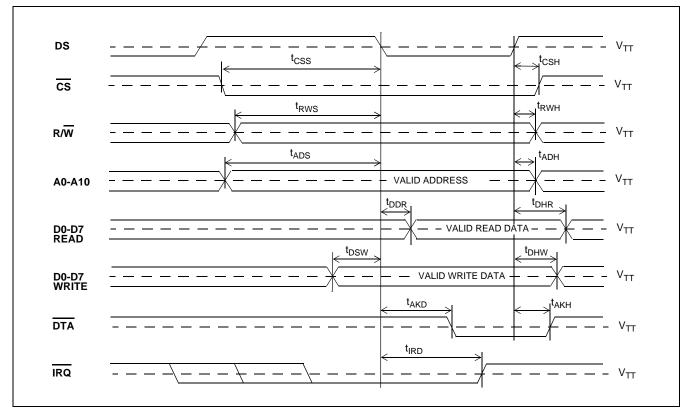

| DSB_d1      | User Signal | H2         | <b>Data Strobe (Input).</b> This active low input works in conjunction with CS to enable the read and write operations.                                                                                                                                           |

| CSB_d1      | User Signal | КЗ         | <b>Chip Select (Input).</b> This active low input is used<br>by a microprocessor to activate the<br>microprocessor port.                                                                                                                                          |

| R/WB_d1     | User Signal | H3         | <b>Read/Write (Input).</b> This input controls the direction of the data bus lines (D7-D0) during a microprocessor access.                                                                                                                                        |

| DTAB_d1     | User Signal | K4         | Data Transfer Acknowledgment (Open Drain<br>Output). This active low output indicates that a<br>data bus transfer is completed. A pull-up resistor<br>(1K typical) is required at this output.                                                                    |

| D(0)_d1     | User Signal | H4         |                                                                                                                                                                                                                                                                   |

| D(1)_d1     | User Signal | K5         |                                                                                                                                                                                                                                                                   |

| D(2)_d1     | User Signal | H5         | Data Bus D0 - D7 (Bidirectional). These pins                                                                                                                                                                                                                      |

| D(3)_d1     | User Signal | G4         | form the 8-bit bidirectional data bus of the microprocessor port.                                                                                                                                                                                                 |

| D(4)_d1     | User Signal | G5         |                                                                                                                                                                                                                                                                   |

| D(5)_d1     | User Signal | F4         |                                                                                                                                                                                                                                                                   |

| D(6)_d1     | User Signal | F5         |                                                                                                                                                                                                                                                                   |

| D(7)_d1     | User Signal | E5         |                                                                                                                                                                                                                                                                   |

| A(0)_d1     | User Signal | D4         |                                                                                                                                                                                                                                                                   |

| A(1)_d1     | User Signal | E6         |                                                                                                                                                                                                                                                                   |

| A(2)_d1     | User Signal | D5         | Address A0 to A10 (Input). These inputs provide                                                                                                                                                                                                                   |

| A(3)_d1     | User Signal | E7         | the A10 - A0 address lines to the internal registers.                                                                                                                                                                                                             |

| A(4)_d1     | User Signal | D7         |                                                                                                                                                                                                                                                                   |

| A(5)_d1     | User Signal | E8         |                                                                                                                                                                                                                                                                   |

| A(6)_d1     | User Signal | E10        |                                                                                                                                                                                                                                                                   |

| A(7)_d1     | User Signal | D8         | ]                                                                                                                                                                                                                                                                 |

| A(8)_d1     | User Signal | D10        | ]                                                                                                                                                                                                                                                                 |

| A(9)_d1     | User Signal | C10        | ]                                                                                                                                                                                                                                                                 |

| A(10)_d1    | User Signal | B10        | ]                                                                                                                                                                                                                                                                 |

| A_IC1_d1    | ICO         | E9         | Internal Connection. Connected to VSS for normal operation                                                                                                                                                                                                        |

| A_IC2_d1    | ICO         | A8         | Internal Connection. Connected to VSS for normal operation                                                                                                                                                                                                        |

| Signal Name | Signal Type | BGA Ball # | Signal Description                                                                                                                                                                                                                                                                                                                      |

|-------------|-------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tsig(0)_d1  | NC          | A10        | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                   |

| Tsig(1)_d1  | NC          | A9         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                   |

| Tsig(2)_d1  | NC          | B9         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                   |

| Tsig(3)_d1  | NC          | C9         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                   |

| Tsig(4)_d1  | NC          | D9         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                   |

| Tsig(5)_d1  | NC          | C8         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                   |

| Tsig(6)_d1  | NC          | B8         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                   |

| Tsig(7)_d1  | NC          | A7         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                   |

| ODE_d1      | User Signal | Β7         | Output Drive Enable (Input). This input pin is<br>logically AND'd with the ODE bit-6 of the Main<br>Control Register. When both ODE bit and ODE<br>input pin are high, the Rout and Sout ST-BUS<br>outputs are enabled.When the ODE bit is low or<br>the ODE input pin is low, the Rout and Sout ST-<br>BUS outputs are high impedance. |

| Sout_d1     | User Signal | C7         | Send PCM Signal Output (Output). Port 1 TDM data output streams.Sout pin outputs serial TDM data streams at 2.048 Mb/s with 32 channels per stream.                                                                                                                                                                                     |

| Rout_d1     | User Signal | A6         | Receive PCM Signal Output (Output). Port 2<br>TDM data output streams. Rout pin outputs serial<br>TDM data streams at 2.048 Mb/s with 32 channels<br>per stream.                                                                                                                                                                        |

| Sin_d1      | User Signal | B6         | Send PCM Signal Input (Input). Port 2 TDM data<br>input streams.<br>Sin pin receives serial TDM data streams at 2.048<br>Mb/s with 32 channels per stream.                                                                                                                                                                              |

| Rin_d1      | User Signal | D6         | <b>Receive PCM Signal Input (Input).</b> Port 1 TDM data input streams.Rin pin receives serial TDM data streams at 2.048 Mb/s with 32 channels per stream.                                                                                                                                                                              |

| FOIb_d1     | User Signal | A5         | Frame Pulse (Input). This input accepts and automatically identifies frame synchronization signals formatted according to ST-BUS or GCI interface specifications.                                                                                                                                                                       |

| C4IB_d1     | User Signal | C6         | Serial Clock (Input). 4.096 MHz serial clock for shifting data in/out on the serial streams (Rin, Sin, Rout, Sout).                                                                                                                                                                                                                     |

| Signal Name  | Signal Type | BGA Ball # | Signal Description                                                                                                                                            |

|--------------|-------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SC_set_d1    | ICO         | B5         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| SM_mclk_d1   | ICO         | A4         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| ST_mclk_d1   | ICO         | B4         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| SC_en_d1     | ICO         | C5         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| SC_In_d1     | ICO         | A3         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| SC_Reset:_d1 | ICO         | B3         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| SC_Fclk_d1   | ICO         | A2         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| Tsig(8)_d1   | NC          | C4         | Internal Connection. The pin must be left open for normal operation.                                                                                          |

| Tsig(9)_d1   | NC          | C3         | Internal Connection. The pin must be left open for normal operation.                                                                                          |

| Tsig(10)_d1  | NC          | D3         | Internal Connection. The pin must be left open for normal operation.                                                                                          |

| Tsig(11)_d1  | NC          | B2         | Internal Connection. The pin must be left open for normal operation.                                                                                          |

| Tsig(12)_d1  | NC          | A1         | Internal Connection. The pin must be left open for normal operation.                                                                                          |

| Tsig(13)_d1  | NC          | C2         | Internal Connection. The pin must be left open for normal operation.                                                                                          |

| Tsig(14)_d1  | NC          | E3         | Internal Connection. The pin must be left open for normal operation.                                                                                          |

| Tsig(15)_d1  | NC          | B1         | Internal Connection. The pin must be left open for normal operation.                                                                                          |

| Tm1_d1       | ICO         | D2         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| Tm2_d1       | ICO         | C1         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| Sg1_d1       | ICO         | E4         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| DT1_d1       | NC          | F3         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                         |

| MCLK_d1      | User Signal | E2         | <b>Master Clock (Input).</b> Nominal 10MHz or 20MHz<br>Master Clock input. May be connected to an<br>asynchronous (relative to frame signal) clock<br>source. |

| Signal Name | Signal Type | BGA Ball # | Signal Description                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fsel_d1     | User Signal | D1         | <b>Frequency select (Input).</b> This input selects the Master Clock frequency operation. When Fsel pin is low, nominal 19.2MHz Master Clock input must be applied. When Fsel pin is high, nominal 9.6MHz Master Clock input must be applied.                                                                                                                                                  |

| Halt_d1     | ICO         | E1         | Internal Connection. Connected to VSS for normal operation                                                                                                                                                                                                                                                                                                                                     |

| Step_d1     | ICO         | F2         | Internal Connection. Connected to VSS for normal operation                                                                                                                                                                                                                                                                                                                                     |

| PLLVSS1_d1  | Power       | G3         | PLL Ground. Must be connected to VSS                                                                                                                                                                                                                                                                                                                                                           |

| PLLVDD_d1   | Power       | F1         | PLL Power Supply. Must be connected to VDD2                                                                                                                                                                                                                                                                                                                                                    |

| PLLVSS2_d1  | Power       | G2         | PLL Ground. Must be connected to VSS                                                                                                                                                                                                                                                                                                                                                           |

| AT1_d1      | NC          | G1         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                                                                          |

| DEVICE 2    |             |            |                                                                                                                                                                                                                                                                                                                                                                                                |

| TMS_d2      | Signal      | V4         | <b>Test Mode Select (3.3V Input).</b> JTAG signal that controls the state transitions of the TAP controller. This pin is pulled high by an internal pull-up when not driven.                                                                                                                                                                                                                   |

| TDI_d2      | Signal      | Y2         | <b>Test Serial Data In (3.3V Input).</b> JTAG serial test instructions and data are shifted in on this pin. This pin is pulled high by an internal pull-up when not driven.                                                                                                                                                                                                                    |

| TDO_d2      | Signal      | W3         | <b>Test Serial Data Out (Output).</b> JTAG serial data<br>is output on this pin on the falling edge of TCK.<br>This pin is held in high impedance state when<br>JTAG scan is not enabled.                                                                                                                                                                                                      |

| TCK_d2      | Signal      | Y3         | <b>Test Clock (3.3V Input).</b> Provides the clock to the JTAG test logic.                                                                                                                                                                                                                                                                                                                     |

| TRSTB_d2    | Signal      | W4         | <b>Test Reset (3.3V Input).</b> Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be pulsed low on power-up or held low, to ensure that the MT93L00 is in the normal functional mode. This pin is pulled by an internal pull-down when not driven.                                                                               |

| Test_En_d2  | ICO         | V5         | Internal Connection. Connected to VSS for normal operation                                                                                                                                                                                                                                                                                                                                     |

| RESETB_d2   | Signal      | Y4         | <b>Device Reset (Schmitt Trigger Input).</b> An active<br>low resets the device and puts the MT93L00 into a<br>low-power stand-by mode.<br>When the RESET pin is returned to logic high<br>and a clock is applied to the MCLK pin, the<br>device will automatically execute initialization<br>routines, which preset all the Control and Status<br>Registers to their default power-up values. |

| Signal Name | Signal Type | BGA Ball # | Signal Description                                                                                                                                                                                                                                                |

|-------------|-------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQB_d2     | Signal      | U5         | <b>Interrupt Request (Open Drain Output).</b> This output goes low when an interrupt occurs in any channel. IRQ returns high when all the interrupts have been read from the Interrupt FIFO Register. A pull-up resistor (1K typical) is required at this output. |

| DSB_d2      | Signal      | W5         | <b>Data Strobe (Input).</b> This active low input works in conjunction with CS to enable the read and write operations.                                                                                                                                           |

| CSB_d2      | Signal      | Y5         | <b>Chip Select (Input).</b> This active low input is used<br>by a microprocessor to activate the<br>microprocessor port.                                                                                                                                          |

| R/WB_d2     | Signal      | V6         | <b>Read/Write (Input).</b> This input controls the direction of the data bus lines (D7-D0) during a microprocessor access.                                                                                                                                        |

| DTAB_d2     | Signal      | U6         | Data Transfer Acknowledgment (Open Drain<br>Output). This active low output indicates that a<br>data bus transfer is completed. A pull-up resistor<br>(1K typical) is required at this output.                                                                    |

| D(0)_d2     | Signal      | W6         |                                                                                                                                                                                                                                                                   |

| D(1)_d2     | Signal      | Y6         |                                                                                                                                                                                                                                                                   |

| D(2)_d2     | Signal      | V7         | Data Bus D0 - D7 (Bidirectional). These pins                                                                                                                                                                                                                      |

| D(3)_d2     | Signal      | W7         | form the 8-bit bidirectional data bus of the microprocessor port.                                                                                                                                                                                                 |

| D(4)_d2     | Signal      | Y7         |                                                                                                                                                                                                                                                                   |

| D(5)_d2     | Signal      | Y8         |                                                                                                                                                                                                                                                                   |

| D(6)_d2     | Signal      | W8         |                                                                                                                                                                                                                                                                   |

| D(7)_d2     | Signal      | V8         |                                                                                                                                                                                                                                                                   |

| A(0)_d2     | Signal      | U9         |                                                                                                                                                                                                                                                                   |

| A(1)_d2     | Signal      | V9         |                                                                                                                                                                                                                                                                   |

| A(2)_d2     | Signal      | W9         | Address A0 to A10 (Input). These inputs provide                                                                                                                                                                                                                   |

| A(3)_d2     | Signal      | Y9         | the A10 - A0 address lines to the internal<br>registers.                                                                                                                                                                                                          |

| A(4)_d2     | Signal      | U10        |                                                                                                                                                                                                                                                                   |

| A(5)_d2     | Signal      | T10        |                                                                                                                                                                                                                                                                   |

| A(6)_d2     | Signal      | Т9         |                                                                                                                                                                                                                                                                   |

| A(7)_d2     | Signal      | V10        | ]                                                                                                                                                                                                                                                                 |

| A(8)_d2     | Signal      | W10        |                                                                                                                                                                                                                                                                   |

| A(9)_d2     | Signal      | U8         | ]                                                                                                                                                                                                                                                                 |

| A(10)_d2    | Signal      | Y10        |                                                                                                                                                                                                                                                                   |

| A_IC1_d2    | ICO         | Т8         | Internal Connection. Connected to VSS for normal operation                                                                                                                                                                                                        |

| A_IC2_d2    | ICO         | Τ7         | Internal Connection. Connected to VSS for normal operation                                                                                                                                                                                                        |

| Signal Name | Signal Type | BGA Ball # | Signal Description                                                                                                                                                                                                                                                                                                                      |

|-------------|-------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tsig(0)_d2  | NC          | U7         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                   |

| Tsig(1)_d2  | NC          | Т6         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                   |

| Tsig(2)_d2  | NC          | U4         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                   |

| Tsig(3)_d2  | NC          | Τ5         | No connection. The pin must be left open for normal operation.                                                                                                                                                                                                                                                                          |

| Tsig(4)_d2  | NC          | R5         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                   |

| Tsig(5)_d2  | NC          | Τ4         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                   |

| Tsig(6)_d2  | NC          | P5         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                   |

| Tsig(7)_d2  | NC          | P4         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                   |

| ODE_d2      | Signal      | N5         | Output Drive Enable (Input). This input pin is<br>logically AND'd with the ODE bit-6 of the Main<br>Control Register. When both ODE bit and ODE<br>input pin are high, the Rout and Sout ST-BUS<br>outputs are enabled.When the ODE bit is low or<br>the ODE input pin is low, the Rout and Sout ST-<br>BUS outputs are high impedance. |

| Sout_d2     | Signal      | L1         | Send PCM Signal Output (Output). Port 1 TDM data output streams.Sout pin outputs serial TDM data streams at 2.048 Mb/s with 32 channels per stream.                                                                                                                                                                                     |

| Rout_d2     | Signal      | N4         | Receive PCM Signal Output (Output). Port 2<br>TDM data output streams. Rout pin outputs serial<br>TDM data streams at 2.048 Mb/s with 32 channels<br>per stream.                                                                                                                                                                        |

| Sin_d2      | Signal      | L2         | Send PCM Signal Input (Input). Port 2 TDM data<br>input streams.<br>Sin pin receives serial TDM data streams at 2.048<br>Mb/s with 32 channels per stream.                                                                                                                                                                              |

| Rin_d2      | Signal      | N3         | <b>Receive PCM Signal Input (Input).</b> Port 1 TDM data input streams.Rin pin receives serial TDM data streams at 2.048 Mb/s with 32 channels per stream.                                                                                                                                                                              |

| FOIb_d2     | Signal      | N2         | Frame Pulse (Input). This input accepts and automatically identifies frame synchronization signals formatted according to ST-BUS or GCI interface specifications.                                                                                                                                                                       |

| C4IB_d2     | Signal      | L3         | Serial Clock (Input). 4.096 MHz serial clock for shifting data in/out on the serial streams (Rin, Sin, Rout, Sout).                                                                                                                                                                                                                     |

| Signal Name  | Signal Type | BGA Ball # | Signal Description                                                                                                                                            |

|--------------|-------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SC_set_d2    | ICO         | N1         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| SM_mclk_d2   | ICO         | L4         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| ST_mclk_d2   | ICO         | M5         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| SC_en_d2     | ICO         | L5         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| SC_In_d2     | ICO         | M1         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| SC_Reset:_d2 | ICO         | M2         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| SC_Fclk_d2   | ICO         | М3         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| Tsig(8)_d2   | NC          | M4         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                         |

| Tsig(9)_d2   | NC          | P1         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                         |

| Tsig(10)_d2  | NC          | P2         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                         |

| Tsig(11)_d2  | NC          | R1         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                         |

| Tsig(12)_d2  | NC          | R2         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                         |

| Tsig(13)_d2  | NC          | P3         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                         |

| Tsig(14)_d2  | NC          | T1         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                         |

| Tsig(15)_d2  | NC          | U1         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                         |

| Tm1_d2       | ICO         | T2         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| Tm2_d2       | ICO         | R3         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| Sg1_d2       | ICO         | R4         | Internal Connection. Connected to VSS for normal operation                                                                                                    |

| DT1_d2       | NC          | V1         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                         |

| MCLK_d2      | Signal      | U2         | <b>Master Clock (Input).</b> Nominal 10MHz or 20MHz<br>Master Clock input. May be connected to an<br>asynchronous (relative to frame signal) clock<br>source. |

| Signal Name | Signal Type | BGA Ball # | Signal Description                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|-------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fsel_d2     | Signal      | W1         | <b>Frequency select (Input).</b> This input selects the Master Clock frequency operation. When Fsel pin is low, nominal 19.2MHz Master Clock input must be applied. When Fsel pin is high, nominal 9.6MHz Master Clock input must be applied.                                                                                                                                           |

| Halt_d2     | ICO         | Т3         | Internal Connection. Connected to VSS for normal operation                                                                                                                                                                                                                                                                                                                              |

| Step_d2     | ICO         | V2         | Internal Connection. Connected to VSS for normal operation                                                                                                                                                                                                                                                                                                                              |

| PLLVSS1_d2  | Power       | Y1         | PLL Ground. Must be connected to VSS                                                                                                                                                                                                                                                                                                                                                    |

| PLLVDD_d2   | Power       | W2         | PLL Power Supply. Must be connected to VDD2                                                                                                                                                                                                                                                                                                                                             |

| PLLVSS2_d2  | Power       | U3         | PLL Ground. Must be connected to VSS                                                                                                                                                                                                                                                                                                                                                    |

| AT1_d2      | NC          | V3         | <b>No connection.</b> The pin must be left open for normal operation.                                                                                                                                                                                                                                                                                                                   |

| DEVICE 3    | 1 1         |            |                                                                                                                                                                                                                                                                                                                                                                                         |

| TMS_d3      | Signal      | W13        | <b>Test Mode Select (3.3V Input).</b> JTAG signal that controls the state transitions of the TAP controller. This pin is pulled high by an internal pull-up when not driven.                                                                                                                                                                                                            |

| TDI_d3      | Signal      | V13        | <b>Test Serial Data In (3.3V Input).</b> JTAG serial test instructions and data are shifted in on this pin. This pin is pulled high by an internal pull-up when not driven.                                                                                                                                                                                                             |

| TDO_d3      | Signal      | Y14        | <b>Test Serial Data Out (Output).</b> JTAG serial data<br>is output on this pin on the falling edge of TCK.<br>This pin is held in high impedance state when<br>JTAG scan is not enabled.                                                                                                                                                                                               |

| TCK_d3      | Signal      | W14        | <b>Test Clock (3.3V Input).</b> Provides the clock to the JTAG test logic.                                                                                                                                                                                                                                                                                                              |

| TRSTB_d3    | Signal      | Y15        | <b>Test Reset (3.3V Input).</b> Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be pulsed low on power-up or held low, to ensure that the MT93L00 is in the normal functional mode. This pin is pulled by an internal pull-down when not driven.                                                                        |

| Test_En_d3  | ICO         | V14        | Internal Connection. Connected to VSS for normal operation                                                                                                                                                                                                                                                                                                                              |

| RESETB_d3   | Signal      | W15        | Device Reset (Schmitt Trigger Input). An active<br>low resets the device and puts the MT93L00 into a<br>low-power stand-by mode.<br>When the RESET pin is returned to logic high<br>and a clock is applied to the MCLK pin, the<br>device will automatically execute initialization<br>routines, which preset all the Control and Status<br>Registers to their default power-up values. |

| Signal Name | Signal Type | BGA Ball # | Signal Description                                                                                                                                                                                                                                                        |

|-------------|-------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQB_d3     | Signal      | Y16        | Interrupt Request (Open Drain Output). This<br>output goes low when an interrupt occurs in any<br>channel. IRQ returns high when all the interrupts<br>have been read from the Interrupt FIFO Register.<br>A pull-up resistor (1K typical) is required at this<br>output. |

| DSB_d3      | Signal      | Y17        | <b>Data Strobe (Input).</b> This active low input works in conjunction with CS to enable the read and write operations.                                                                                                                                                   |

| CSB_d3      | Signal      | W16        | Chip Select (Input). This active low input is used<br>by a microprocessor to activate the<br>microprocessor port.                                                                                                                                                         |

| R/WB_d3     | Signal      | V15        | <b>Read/Write (Input).</b> This input controls the direction of the data bus lines (D7-D0) during a microprocessor access.                                                                                                                                                |

| B_d3        | Signal      | Y18        | Data Transfer Acknowledgment (Open Drain<br>Output). This active low output indicates that a<br>data bus transfer is completed. A pull-up resistor<br>(1K typical) is required at this output.                                                                            |

| D(0)_d3     | Signal      | W17        |                                                                                                                                                                                                                                                                           |

| D(1) _d3    | Signal      | Y19        |                                                                                                                                                                                                                                                                           |

| D(2)_d3     | Signal      | V16        | Data Bus D0 - D7 (Bidirectional). These pins                                                                                                                                                                                                                              |

| D(3)_d3     | Signal      | W18        | form the 8-bit bidirectional data bus of the microprocessor port.                                                                                                                                                                                                         |

| D(4)_d3     | Signal      | Y20        |                                                                                                                                                                                                                                                                           |

| D(5)_d3     | Signal      | W19        |                                                                                                                                                                                                                                                                           |

| D(6)_d3     | Signal      | V17        |                                                                                                                                                                                                                                                                           |

| D(7)_d3     | Signal      | V18        |                                                                                                                                                                                                                                                                           |

| A(0)_d3     | Signal      | U18        |                                                                                                                                                                                                                                                                           |

| A(1)_d3     | Signal      | V19        |                                                                                                                                                                                                                                                                           |

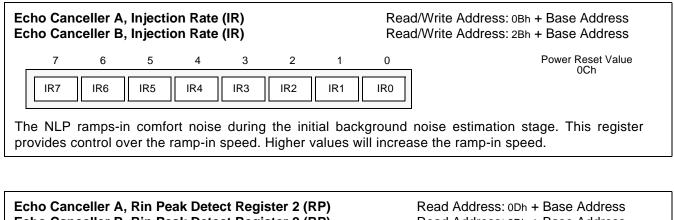

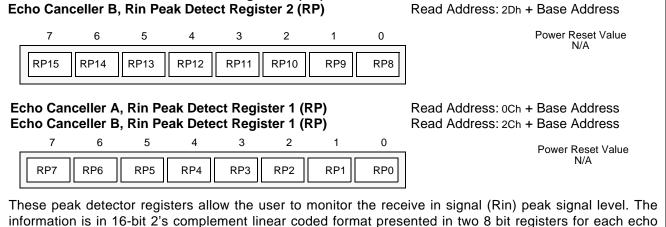

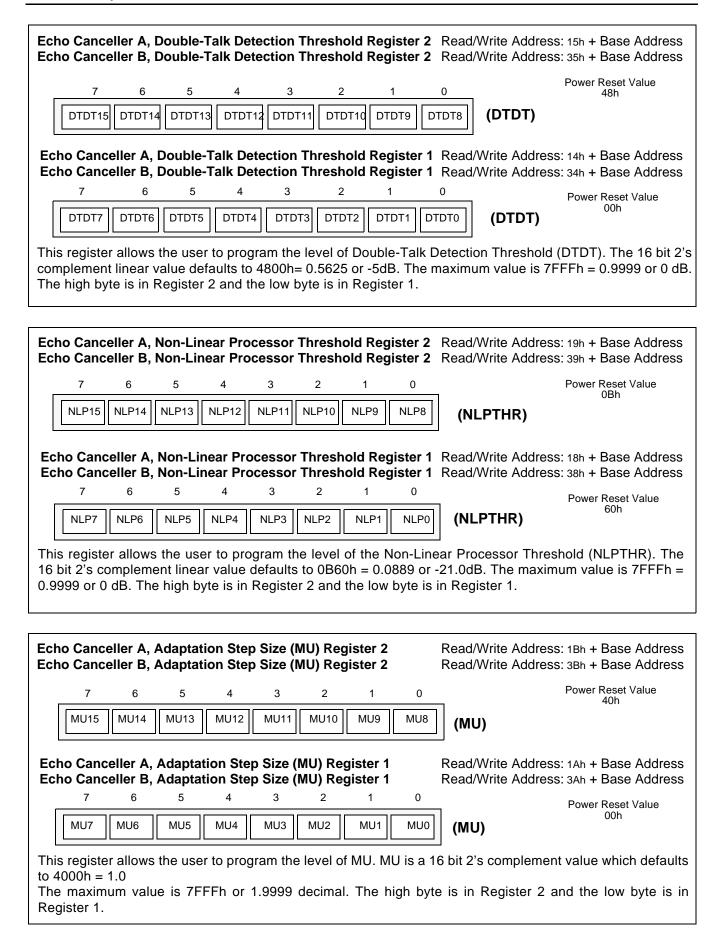

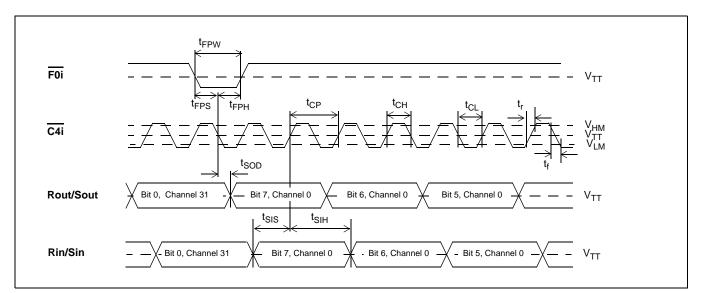

| A(2)_d3     | Signal      | W20        | Address A0 to A10 (Input). These inputs provide                                                                                                                                                                                                                           |