# T9000 ISDN Network Termination Node (NTN) Device

## 1 Description

The T9000 is an ISDN network termination node device that is highly integrated and provides a low-cost solution to support the following:

- All standard NT1 functions required to attach an S/T interface device to an ISDN network. In addition, the T9000 also supports attachment of two standard analog (POTS) telephones for communications over an ISDN network.

- Intelligent network termination (INT/Smart NT1) functions, with its built-in controller and support for attachment of two analog phones for communications over an ISDN network.

- A variation of the V5.1 signaling protocol called narrowband multiservice delivery system (NMDS) adopted by countries using the V5 signaling protocol (e.g., United Kingdom)

In addition, the T9000 can also be used for pair-gain applications where support for more than one telephone line is required without the installation of an additional pair of wires from the telephone central office to the customer premises.

### 2 Features

- Complete interface to basic rate ISDN networks at the S/T-interface and U-interface reference points.

- U-interface (LT or NT operation) conforms to ANSI\* T1.601 and ETSI TS 080 standards.

- S/T-interface conforms to ANSI T1.605 standard, ITU-T I.430 recommendation, and ETSI ETS 300 012 standard for the network termination (NT) side of the network.

- Low power consumption.

- D-channel HDLC formatter with address recognition and integrated contention resolution scheme.

- 64-byte D-channel FIFOs.

- GCI+ interface supporting GCI and generic TDM modes for interfacing to a wide variety of POTS circuits.

- General-purpose I/O (GPIO) ports with interrupt capability for interfacing to SLICs, codecs, DTMF decoders, and other peripheral devices.

- Three low-power, general-purpose comparators.

- Two 100 kHz programmable PWM outputs with an automatic sine wave generation mode to support ringing, pulse metering, etc.

- 20 kHz—200 kHz programmable dc/dc converter synchronization output.

- JTAG boundary scan on all digital pins.

- Power-saving mode.

- In this mode, the unused interfaces of the T9000, such as, microcontroller, PWMs, and comparator can remain in powerdown mode, thus resulting in significant reduction in power consumption (see Section 20.2, Power Consumption).

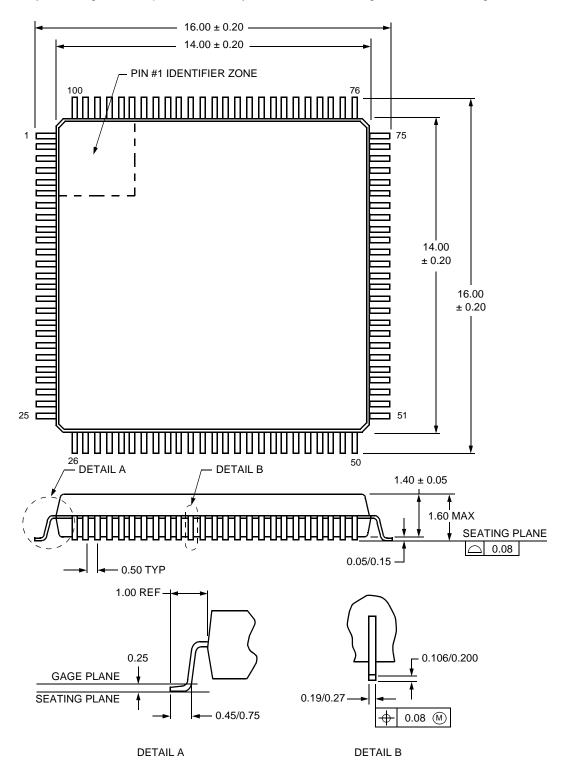

- Packaged in a 100-pin TQFP (thin quad flat pkg).

- 5 V power supply.

- Operating temperature range: -40 °C to +85 °C.

- Integrated 80C32 microcontroller with the following features:

- Programmable clock rates (MHz): 15.36, 7.68, 3.84, 1.92, 0.96.

- 4K internal SRAM.

- 64K internal ROM.

- Supports external ROM/RAM.

- Can be disabled via pin strap (sleep mode) for use with an external emulator.

- Programmable watchdog timer.

External ROM and RAM (64K x 8 maximum each) are accessed through an external data/address bus.

Support for ROM and RAM space above the 64K limit can be accomplished by memory paging using one or more GPIO signals as an external chip select. Power management routines may be implemented through the microcontroller to power down most of the internal submodules, including the microcontroller itself. An autosleep mode is also included, allowing the microcontroller to stop its internal clock and be automatically restarted (microcontroller wake-up) whenever any interrupt is triggered.

<sup>\*</sup> ANSI is a registered trademark of American National Standards Institute, Inc.

## **Table of Contents**

| Contents                                      | Page   | Contents                                  | Page |

|-----------------------------------------------|--------|-------------------------------------------|------|

| 1 Description                                 | 1      | 10 GCI+ Interface Module                  | 69   |

| 2 Features                                    |        | 10.1 TDM Mode (GCCF, GMODE[1:0] = 1x).    | 69   |

| 3 Block Diagram                               | 6      | 10.2 GCI Modes (GCCF[GMODE(1:0)] = $0x$ ) | 73   |

| 4 Pin Information                             |        | 10.3 GCI-NT Mode (GCCF[GMODE(1:0)] = $0$  |      |

| 5 Control Register Memory Space               |        | 10.3.1 GCI-SCIT Mode (GCCF,               | ,    |

| 6 Functional Modules                          |        | GMODE[1:0] = 01)                          | 75   |

| 6.1 80C32 Microcontroller Module (80C32 Blo   | ock)17 | 10.3.2 Monitor Message Transfer           |      |

| 6.2 Program Address Space                     | ,      | 10.4 C/I Message Transfer                 |      |

| 6.3 Data Address Space                        |        | 10.5 GCI+ Powerdown Mode                  |      |

| 6.4 Timers                                    |        | 10.6 GCI+ Loopbacks                       | 78   |

| 6.5 Interrupts                                | 17     | 10.7 GCI+ Register Set                    |      |

| 6.6 Interrupt Register Set                    |        | 11 GPIO Ports                             |      |

| 6.7 Clock Generator                           |        | 11.1 GPIO Register Set                    | 86   |

| 6.8 Watchdog Timer                            | 22     | 12 PWM Module                             |      |

| 6.9 On-Circuit Emulation (ONCE) Mode          |        | 12.1 PWM Manual/Timer Operation Mode      | 94   |

| 6.10 Emulation                                |        | 12.2 PWM Auto Operation (Sine) Mode       |      |

| 6.11 Module I/O                               |        | 12.3 PWSM ROM                             |      |

| 6.12 Special Instructions for Using the Lucen | t      | 12.4 PWM Auto Mode Example                | 97   |

| 80C32 Block                                   |        | 12.5 PWM Powerdown Mode                   |      |

| 6.12.1 Port Configuration                     | 24     | 12.6 PWM Module Register Set              | 100  |

| 6.12.1.1 Ports 0 and 2                        |        | 13 dc/dc Control Generator                |      |

| 6.12.1.2 Port 1                               | 24     | 13.1 dc/dc Control Generator Register Set |      |

| 6.12.1.3 Port 3                               | 24     | 14 Comparators                            |      |

| 6.13 Serial Port Timing                       |        | 14.1 Comparators Register Set             |      |

| 6.14 External Program Memory Characteristic   |        | 14.2 Configuration Sequence               |      |

| 7 Transmission Superblock                     |        | 15 Test Mode                              |      |

| 7.1 U-Interface Block (U Block)               |        | 16 Loopbacks                              | 109  |

| 7.2 S/T-Interface Block (S Block)             |        | 17 Absolute Maximum Ratings               |      |

| 7.3 Data Flow/Activation Control Module (DF.  |        | 18 Handling Precautions                   |      |

| 7.3.1 EOC State Machine (EOCSM)               |        | 19 Recommended Operating Conditions       |      |

| 7.3.2 Automatic EOC (AUTOEOC) Mode            |        | 20 Electrical Characteristics             |      |

| 7.3.3 Manual EOC Mode                         |        | 20.1 Power Supply                         | 111  |

| 7.3.4 Data Flow Control                       | 32     | 20.2 Power Consumption                    |      |

| 7.4 Microcontroller Access to Upstream and    |        | 20.3 S/T-Interface Receiver Common-Mode   |      |

| Downstream B1 and B2 Channels                 | 32     | Rejection                                 |      |

| 7.5 LT Mode                                   | 32     | 20.4 Pin Electrical Characteristics       | 112  |

| 7.6 DFAC Register Set                         | 33     | 21 Crystal Characteristics                | 113  |

| 8 Device Operation Control                    | 47     | 22 Timing Characteristics                 |      |

| 8.1 Device Operation Register                 |        | 23 Application Diagrams                   |      |

| 9 HDLC with FIFO Module                       | 52     | 24 Outline Diagram                        |      |

| 9.1 HDLC Transmitter                          | 52     | 24.1 100-Pin TQFP                         |      |

| 9.1.1 HDLC Transmitter Initialization         | 52     | 25 Ordering Information                   |      |

| 9.2 HDLC Transmitter D-Channel Access         | 53     | 26 Register Set Summary                   |      |

| 9.3 HDLC Receiver                             |        |                                           |      |

| 9.3.1 HDLC Receiver Initialization            | 54     |                                           |      |

| 9.3.1.1 Overrun Condition                     | 56     |                                           |      |

| 9.4 Address Recognition                       | 56     |                                           |      |

| 9.5 HDLC Register Set                         |        |                                           |      |

# Table of Contents (continued)

| Tables                                         | Page  | Tables                                          | Page |

|------------------------------------------------|-------|-------------------------------------------------|------|

| Table 1. S/T-Interface Pins (6)                |       | Table 34. SSR: S-Interface Status Register      |      |

| Table 2. U-Interface Pins (7)                  | 8     | (0x11)                                          | 42   |

| Table 3. GCI+ Pins (5)                         |       | Table 35. MFR0: Multiframe Register, Q-Chan-    |      |

| Table 4. GPIO Pins (24)                        |       | nel Data (0x12)                                 | 43   |

| Table 5. 80C32 External Access Pins (27)       | 11    | Table 36. MFR1: Multiframe Register, S-Sub-     |      |

| Table 6. Comparators (6)                       |       | channel Data (0x13)                             | 43   |

| Table 7. JTAG Pins (4)                         |       | Table 37. UIR: U-Interface Interrupt Register   |      |

| Table 8. Miscellaneous Pins (2)                |       | (0x14)                                          | 44   |

| Table 9. Oscillator Pins (2)                   |       | Table 38. UIE: U-Interface Interrupt Enable     |      |

| Table 10. Power and Ground Pins                |       | (0x15)                                          | 45   |

| Table 11. Control Register Memory Space        | 15    | Table 39. SIR: S-Interface Interrupt Register   |      |

| Table 12. GIR0: Global Interrupt Register 0    |       | (0x16)                                          |      |

| (0x00)                                         | 18    | Table 40. SIE: S-Interface Interrupt Enable Reg |      |

| Table 13. GIR1: Global Interrupt Register 1    |       | (0x17)                                          | 46   |

| (0x01)                                         |       | Table 41. DOCR: Device Operation Control        |      |

| Table 14. GIE: Global Interrupt Enable Registe |       | Register (0x50)                                 | 47   |

| _(0x02)                                        |       | Table 42. B1UP: B1-Channel Upstream Data        |      |

| Table 15. UPCK: Microcontroller Clock Control  |       | from GCI to U-interface (0x51)                  | 47   |

| Register (0x03)                                |       | Table 43. B2UP: B2-Channel Upstream Data        |      |

| Table 16. WDT: Microcontroller Watchdog Time   |       | from GCI to U-interface (0x52)                  |      |

| Control (0x04)                                 |       | Table 44. B1DN: B1-Channel Downstream Data      |      |

| Table 17. Port Direction Registers             |       | from U-Interface to GCI (0x53)                  |      |

| Table 18. Standard 80C32 RCLK/TCLK Option      |       | Table 45. B2DN: B2-Channel Downstream Data      |      |

| Table 19. Lucent 80C32 RCLK/TCLK Options       | 25    | from U-Interface to GCI (0x54)                  | 48   |

| Table 20. External Program Memory              |       | Table 46. Reserved 1: Reserved Register for     |      |

| Characteristics                                | 26    | Internal Use (0x55)                             | 49   |

| Table 21. AUTOEOC = 1 Messages                 |       | Table 47. Reserved 2: Reserved Register for     |      |

| (Data/Messages = 1) That Initiate Actions      |       | Internal Use (0x56)                             | 49   |

| Table 22. DFCF: DFAC Configuration Register    |       | Table 48. Reserved 3: Reserved Register for     |      |

| _(0x05)                                        | 33    | Internal Use (0x57)                             | 49   |

| Table 23. DFR: Data Flow Register              |       | Table 49. Reserved 4: Reserved Register for     |      |

| (0x06)                                         |       | Internal Use (0x58)                             | 50   |

| Table 24. UCR0: U-Interface Control Register # |       | Table 50. Reserved 5: Reserved Register for     |      |

| (0x07)                                         |       | Internal Use (0x59)                             | 50   |

| Table 25. UCR1: U-Interface Control Register # |       | Table 51. Reserved 6: Reserved Register for     |      |

| (0x08)                                         |       | Internal Use (0x5A)                             | 50   |

| Table 26. USR0: U-Interface Status Register #0 |       | Table 52. Reserved 7: Reserved Register for     |      |

| (0x09)                                         |       | Internal Use (0x5B)                             | 50   |

| Table 27. USR1: U-Interface Status Register #  |       | Table 53. Reserved 8: Reserved Register for     | - 4  |

| (0x0A)                                         |       | Internal Use (0x5C)                             | 51   |

| Table 28. ECR0: EOC Control Register 0—Cor     | nmand | Table 54. Reserved 9: Reserved Register for     |      |

| and Address (0x0B)                             |       | Internal Use (0x5D)                             | 51   |

| Table 29. ECR1: EOC Control Register 1—Mes     |       | Table 55. HTCF: HDLC Transmitter Configuration  |      |

| (0x0C)                                         |       | Register (0x18)                                 |      |

| Table 30. ESR0: EOC Status Register 0—Com      |       | Table 56. HRCF: HDLC Receiver Configuration     |      |

| and Address (0x0D)                             |       | Register (0x19)                                 | 59   |

| Table 31. ESR1: EOC Status Register 1—Mes      |       | Table 57. HTTH: HDLC Transmit FIFO Thresho      |      |

| (0x0E)                                         |       | (0x1A)                                          |      |

| Table 32. SCR0: S-Interface Control Register # |       | Table 58. HRTH: HDLC Receive FIFO Threshol      |      |

| (0x0F)                                         |       | (0x1B)                                          | 60   |

| Table 33. SCR1: S-Interface Control Register # |       | Table 59. HTSA: HDLC Transmit FIFO Space        |      |

| (0x10)                                         | 41    | Available (0x1C)                                | 61   |

# Table of Contents (continued)

| Tables                                        | Page   | Tables                                         | Page |

|-----------------------------------------------|--------|------------------------------------------------|------|

| Table 60. HRDA: HDLC Receive FIFO Data        |        | Table 91. GPDIR1: GPIO Port 1 Pin Direction    |      |

| Available (0x1D)                              | 61     | (0x39)                                         | 87   |

| Table 61. HTX: HDLC Transmit Data (0x1E)      | 61     | Table 92. GPDIR2: GPIO Port 2 Pin Direction    |      |

| Table 62. HTXL: HDLC Transmit Data Last By    |        | (0x3A)                                         | 87   |

| (0x1F)                                        |        | Table 93. GPAF0: GPIO Alternate Function       |      |

| Table 63. HRX: HDLC Receive Data (0x20) .     |        | Register #0 (0x3B)                             | 88   |

| Table 64. HSCR: HDLC SAPI C/R Bit Mask        |        | Table 94. GPAF1: GPIO Alternate Function       |      |

| (0x21)                                        | 62     | Register #1 (0x3C)                             | 89   |

| Table 65. HSM0: HDLC SAPI Match Pattern 0     |        | Table 95. GPD0: GPIO Port 0 Data Register      |      |

| (0x22)                                        | 63     | (0x3D)                                         | 89   |

| Table 66. HTM0: HDLC TEI Match Pattern 0      |        | Table 96. GPD1: GPIO Port 1 Data Register      |      |

| (0x23)                                        | 63     | (0x3E)                                         | 90   |

| Table 67. HSM1: HDLC SAPI Match Pattern 1     |        | Table 97. GPD2: GPIO Port 2 Data Register      |      |

| (0x24)                                        |        | (0x3F)                                         | 90   |

| Table 68. HTM1: HDLC TEI Match Pattern 1      |        | Table 98. GPLEI: GPIO Level-Edge-Triggered     |      |

| (0x25)                                        | 64     | Interrupt Control (0x40)                       | 90   |

| Table 69. HSM2: HDLC SAPI Match Pattern 2     |        | Table 99. GPPOL: GPIO Interrupt Polarity       |      |

| (0x26)                                        | 64     | Control (0x41)                                 | 91   |

| Table 70. HTM2: HDLC TEI Match Pattern 2      |        | Table 100. GPIR: GPIO Interrupt Register       |      |

| (0x27)                                        | 64     | (0x42)                                         | 91   |

| Table 71. HSM3: HDLC SAPI Match Pattern 3     |        | Table 101. GPIE: GPIO Interrupt Enable         |      |

| (0x28)                                        |        | (0x43)                                         | 92   |

| Table 72. HTM3: HDLC TEI Match Pattern 3      |        | Table 102. ROM Code                            |      |

| (0x29)                                        |        | Table 103. PWM Sine Modulator Programming      |      |

| Table 73. HSMOD: HDLC SAPI Modifier Regi      |        | Example                                        | 98   |

| (0x2A)                                        |        | Table 104. PW0CF: Pulse-Width Modulator 0      |      |

| Table 74. HTMOD: HDLC TEI Modifier Regist     |        | Configuration (0x44)                           | 100  |

| (0x2B)                                        |        | Table 105. PW0VH: Pulse-Width Modulator 0      |      |

| Table 75. HIR: HDLC Interrupt Register (0x2C  |        | Pulse-Width Value, High Byte (0x45)            | 101  |

| Table 76. HIE: HDLC Interrupt Enable 15 (0x2  |        | Table 106. PW0VL: Pulse-Width Modulator 0      |      |

| Table 77. GCI+ Interface Signals              |        | Pulse-Width Value, Low Byte (0x46)             | 101  |

| Table 78. TDM Data Rate and Clock Options     |        | Table 107. PW1CF: Pulse-Width Modulator 1      |      |

| Table 79. GCI-TE Data-Slot Association        |        | Configuration (0x47)                           | 102  |

| Table 80. GCCF: GCI+ Configuration Register   | r      | Table 108. PW1VH: Pulse-Width Modulator 1      |      |

| (0x2E)                                        |        | Pulse-Width Value, High Byte (0x48)            | 103  |

| Table 81. GCOF1: GCI PFS1 Offset Select       |        | Table 109. PW1VL: Pulse-Width Modulator 1      |      |

| (0x2F)                                        | 80     | Pulse-Width Value, Low Byte (0x49)             | 103  |

| Table 82. GCOF2: GCI PFS2 Offset Select       |        | Table 110. PWIR: Pulse-Width Modulator Interru |      |

| (0x30)                                        | 80     | Register (0x4A)                                | 103  |

| Table 83. GCDMD: GCI Downstream (Transm       | nit)   | Table 111. DCCF: dc/dc Configuration Register  |      |

| Monitor Data (0x31)                           | 81     | (0x4B)                                         | 104  |

| Table 84. GCDML: GCI Downstream (Transm       | it)    | Table 112. Comparator Characteristics          | 106  |

| Monitor Data Last (0x32)                      | 81     | Table 113. CME: Comparator Enable (0x4C)       |      |

| Table 85. GCUMD: GCI Upstream (Receive) I     |        | Table 114. CMT: Comparator Transition Polarity |      |

| Data (0x33)                                   |        | (0x4D)                                         |      |

| Table 86. GCDCI: GCI Downstream (Transmit     | t) C/I | Table 115. CMIR: Comparator Interrupt Registe  | r    |

| Data (0x34)                                   | •      | (0x4E)                                         |      |

| Table 87. GCUCI: GCI Upstream (Receive) C     |        | Table 116. CMIE: Comparator Interrupt Enable   |      |

| Data (0x35)                                   |        | (0x4F)                                         | 107  |

| Table 88. GCIR: GCI Interrupt Register (0x36) |        | •                                              |      |

| Table 89. GCIE: GCI Interrupt Enable (0x37)   |        |                                                |      |

| Table 90. GPDIR0: GPIO Port 0 Pin Direction   |        |                                                |      |

| (0x38)                                        | 86     |                                                |      |

# Table of Contents (continued)

| Tables                                      | Page    | Figures                                        | Page  |

|---------------------------------------------|---------|------------------------------------------------|-------|

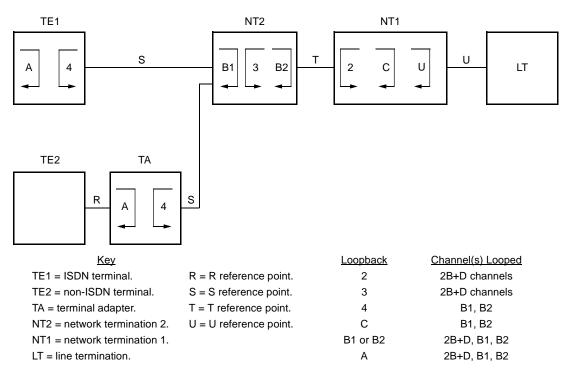

| Table 117. Absolute Maximum Ratings         | 110     | Figure 1. NTN Block Diagram                    | 6     |

| Table 118. ESD Threshold Voltage            |         | Figure 2. T9000 Pinout                         | 7     |

| Table 119. Recommended Operating Condition  | ns .110 | Figure 3. NTN Data Memory Address Space        | 18    |

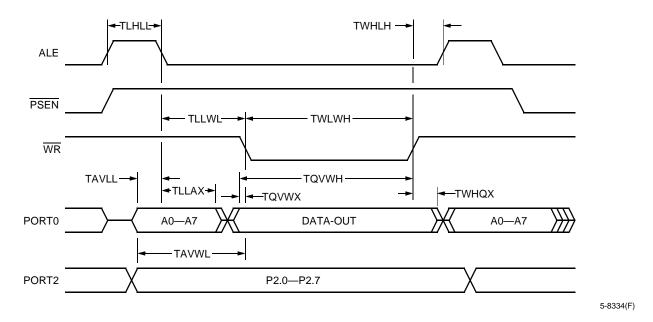

| Table 120. Power Consumption                |         | Figure 4. External Program Memory Read Cycle   | 27    |

| Table 121. S/T-Interface Receiver Common-M  |         | Figure 5. External Data Memory Read Cycle      | 27    |

| Rejection                                   | 111     | Figure 6. External Data Memory Write Cycle     | 28    |

| Table 123. Digital dc Characteristics (Over |         | Figure 7. Downstream EOC Analysis (AUTOEO)     | C = 1 |

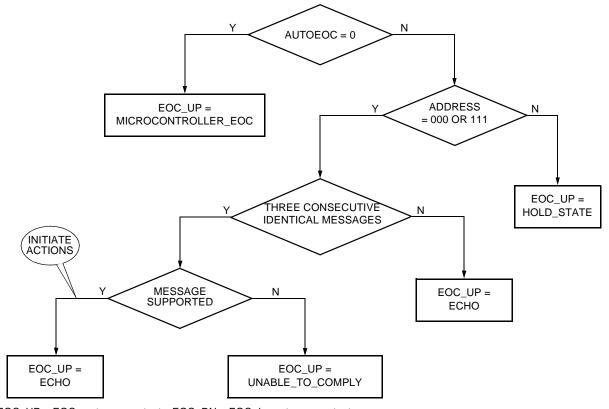

| Operating Ranges)                           | 112     | and Upstream EOC Processing                    | 31    |

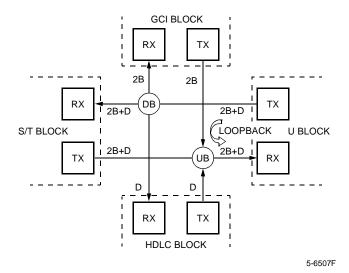

| Table 123. Fundamental Mode Crystal         |         | Figure 8. 2B+D Data Flow Block Diagram         | 32    |

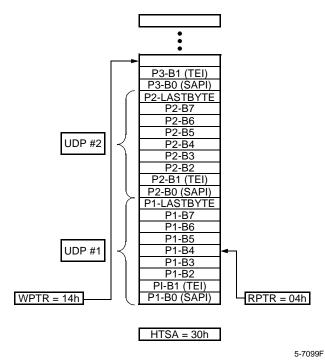

| Characteristics                             | 113     | Figure 9. HDLC Transmitter FIFO                | 53    |

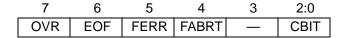

| Table 124. Internal PLL Characteristics     | 113     | Figure 10. HDLC Receiver Status Word           | 54    |

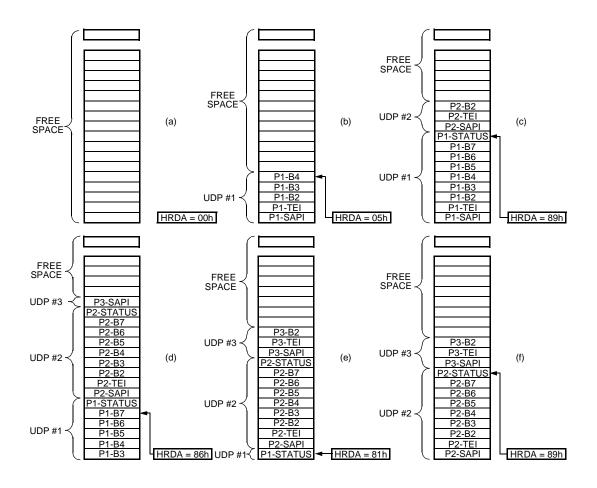

| Table 126. MTC (Master Timing Clock)        |         | Figure 11. HDLC Receiver FIFO Snapshot         |       |

| Requirements and Characteristics (LT Mode   | e)113   | Sequence                                       | 55    |

| Table 126. Register Set Summary Global      |         | Figure 12. DLCI Extension and Function of      |       |

| Registers                                   | 118     | SAPI0M-TEI0M Bits                              | 57    |

| Table 127. Register Set Summary DFAC        |         | Figure 13. GCI+ Interface, TDM Mode Timing,    |       |

| Registers                                   | 118     | Double Clock Mode: GCCF[CKMODE] = 0,           |       |

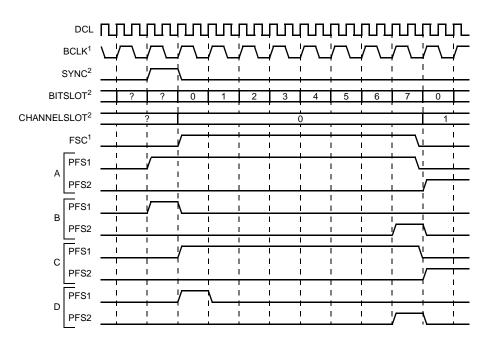

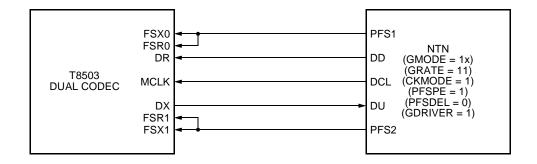

| Table 128. Register Set Summary U-Interface |         | GCCF[GMODE(1:0)] = 1x                          | 71    |

| Control Registers                           | 118     | Figure 14. GCI+ Interface, TDM Mode Timing,    |       |

| Table 129. Register Set Summary EOC         |         | Single Clock Mode: GCCF[CKMODE] = 1,           |       |

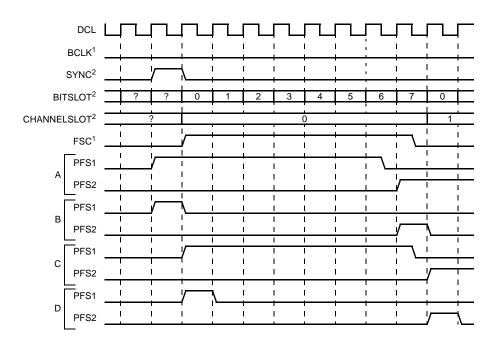

| Control Registers                           | 119     | GCCF[GMODE(1)] = 1                             | 72    |

| Table 130. Register Set Summary S-Interface |         | Figure 15. NTN/T8503 Glueless TDM              |       |

| Registers                                   | 119     | Interconnection                                |       |

| Table 131. Register Set Summary Multiframe  |         | Figure 16. GCI-NT Frame Structure              |       |

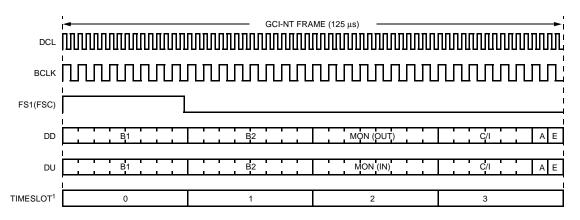

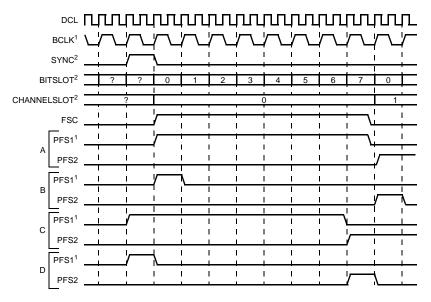

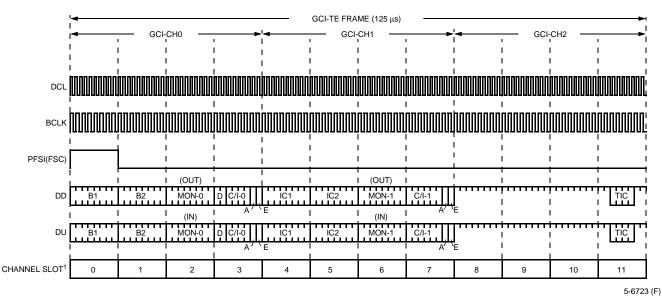

| Registers                                   |         | Figure 17. GCI-NT Timing Diagram               |       |

| Table 132. Register Set Summary U-Interface |         | Figure 18. GCI-TE Mode Frame Structure         |       |

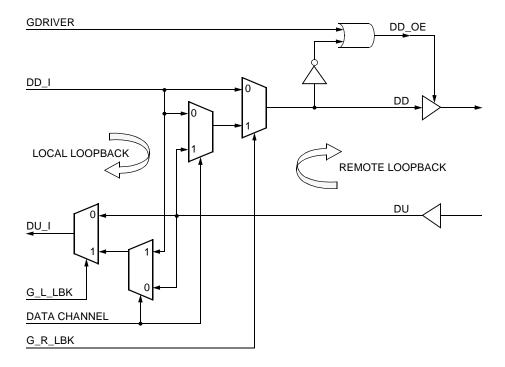

| Interrupt Registers                         |         | Figure 19. GCI Loopback Logic                  |       |

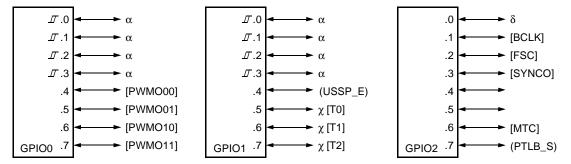

| Table 133. Register Set Summary S-Interface |         | Figure 20. GPIO Pin Capabilities Summary       |       |

| Interrupt Registers                         | 120     | Figure 21. Pulse-Width Modulated Output Signal |       |

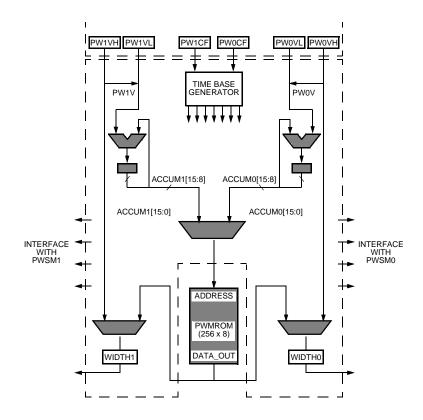

| Table 134. Register Set Summary HDLC        |         | Figure 22. PWMCNTRL Architecture               |       |

| Registers                                   | 121     | Figure 23. Widths of PWM Pulses Generated wit  |       |

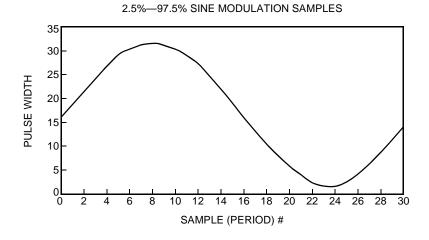

| Table 135. Register Set Summary GCI+        |         | a 2.5%—97.5% Modulation Width                  | 99    |

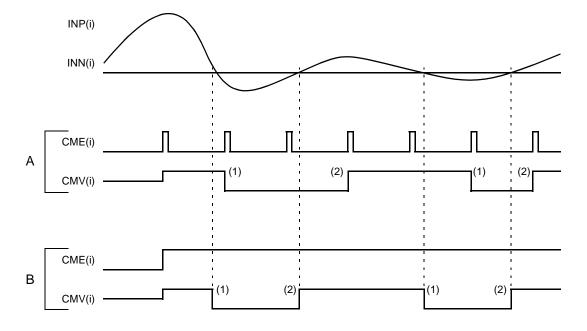

| Registers                                   | 123     | Figure 24. (A) CMV When CME Is a Periodic      |       |

| Table 136. Register Set Summary GPIO        |         | Pulse and (B) CMV When CMV Is Static           | 105   |

| Registers                                   | 124     | Figure 25. Location of the Loopback            |       |

| Table 137. Register Set Summary PWM         |         | Configurations                                 |       |

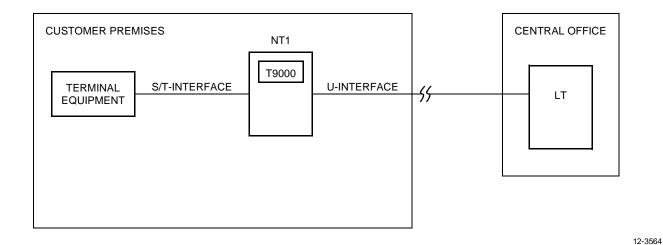

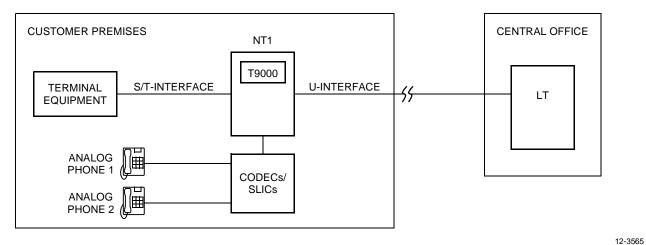

| Registers                                   | 125     | Figure 26. NT1 Application                     |       |

| Table 138. Register Set Summary dc/dc       |         | Figure 27. NT1+ Application                    |       |

| Register                                    |         | Figure 28. Pair Gain Application               | 115   |

| Table 139. Register Set Summary Comparato   |         |                                                |       |

| Registers                                   | 126     |                                                |       |

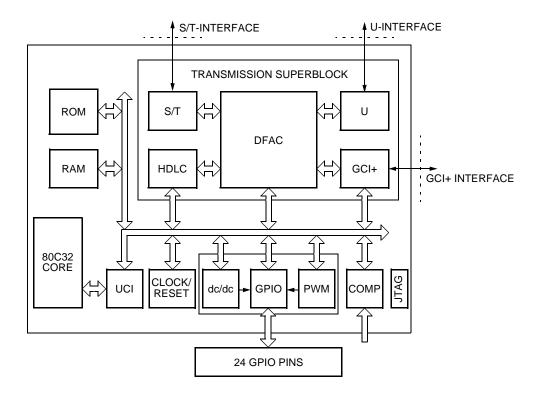

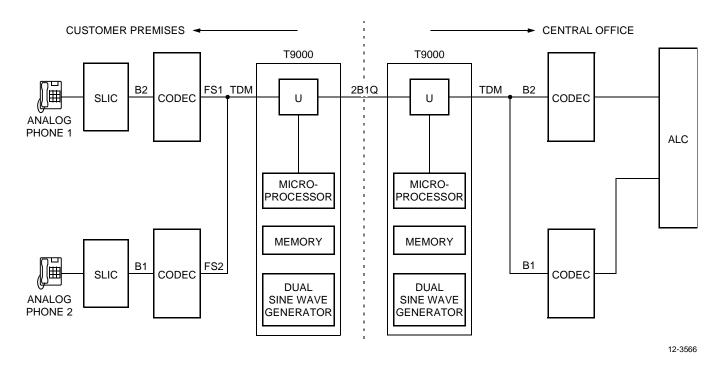

# 3 Block Diagram

Figure 1 shows the architecture of the NTN device.

5-6494aF

### LEGEND:

dc/dc: Square wave signal generator with programmable period

COMP: Comparator

DFAC: Data flow/activation control

GCI+: General control interface

GPIO: General-purpose input/output

HDLC: High-level datalink controller

JTAG: Boundary-scan interface

PWM: Pulse-width modulator

UCI: Microcontroller interface

Figure 1. NTN Block Diagram

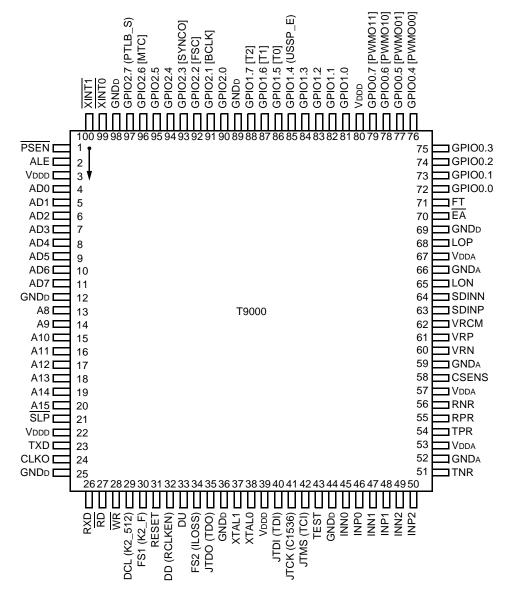

### 4 Pin Information

5-6495.bF

Note: Alternate pin functions, shown in parentheses (), are selected when the TEST pin is asserted.

Alternate pin functions, shown in brackets [], are selected when the corresponding register bits are set.

Figure 2. T9000 Pinout

Table 1. S/T-Interface Pins (6)

| Pin Name | Pin# | Туре | Pin Description                                                                                                                                                                                                                                                                                                                 |

|----------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSENS    | 58   | _    | <b>Current Sense.</b> Connect an 11.5 k $\Omega$ , 1%, resistor from this pin to GNDA.                                                                                                                                                                                                                                          |

| FT       | 71   | I    | <b>Fixed Timing Control.</b> Upon exiting from RESET, the state of this pin is sampled internally and written to register SCR0[FT] to control whether the S-block receiver uses fixed or adaptive timing (note that the 80C32 is free to overwrite register bit SCR0[FT] subsequent to this). Internal 50 k $\Omega$ pull-down. |

|          |      |      | <ul><li>0: Adaptive Timing. Incoming data at S/T-interface is sampled at a point defined by an adaptive timing algorithm.</li><li>1: Fixed Timing. Incoming data at the S/T-interface is sampled with a fixed delay relative to the S/T transmitter clock.</li></ul>                                                            |

| TPR      | 54   | 0    | <b>Transmit Positive Rail for S/T-Interface.</b> Positive output of S/T-interface analog transmitter. Connect to transformer through a 121 $\Omega$ , 1% resistor.                                                                                                                                                              |

| TNR      | 51   | 0    | <b>Transmit Negative Rail for S/T-Interface.</b> Negative output of S/T-interface analog transmitter. Connect to transformer through a 121 $\Omega$ , 1% resistor.                                                                                                                                                              |

| RPR      | 55   | I    | Receive Positive Rail for S/T-Interface. Positive input of S/T-interface analog receiver. Connect to transformer through a 10 k $\Omega$ , 10% resistor.                                                                                                                                                                        |

| RNR      | 56   | Ι    | Receive Negative Rail for S/T-Interface. Negative input of S/T-interface analog receiver. Connect to transformer through a 10 k $\Omega$ , 10% resistor.                                                                                                                                                                        |

**Table 2. U-Interface Pins (7)**

| Pin Name | Pin# | Туре | Pin Description                                                                                                                                            |

|----------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOP      | 68   | 0    | <b>Line Driver Positive Output for U-Interface.</b> Connect to U-interface transformer through a 16.9 $\Omega$ , 1% resistor.                              |

| LON      | 65   | 0    | Line Driver Negative Output for U-Interface. Connect to U-interface transformer through a 16.9 $\Omega$ , 1% resistor.                                     |

| VRP      | 61   | _    | Positive Voltage Reference for U-Interface Circuits. Connect a 0.1 $\mu$ F, 20% capacitor to GND <sub>A</sub> (as close to the device pins as possible).   |

| VRN      | 60   | _    | <b>Negative Voltage Reference for U-Interface Circuits.</b> Connect a 0.1 μF, 20% capacitor to GND <sub>A</sub> (as close to the device pins as possible). |

| VRCM     | 62   | _    | Common-Mode Voltage Reference for U-Interface Circuits. Connect a 0.1 $\mu$ F, 20% capacitor to GNDA (as close to the device pins as possible).            |

| SDINN    | 64   | I    | Sigma-Delta A/D Negative Input for U-Interface. Connect via an 820 pF, 20% capacitor to SDINP.                                                             |

| SDINP    | 63   | I    | Sigma-Delta A/D Positive Input for U-Interface. Connect via an 820 pF, 20% capacitor to SDINN.                                                             |

Table 3. GCI+ Pins (5)

| Pin Name      | Pin# | Type*             | Pin Description                                                                                                                                                                                                                                                                              |

|---------------|------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DU            | 33   | I                 | Data Upstream. GCI+ data input.                                                                                                                                                                                                                                                              |

| DD            | 32   | OD                | Data Downstream. GCI+ data output. Open-drain <sup>†</sup> output (typical).                                                                                                                                                                                                                 |

| (RCLKEN)      |      | (O)               | <b>80 kHz Receive Clock</b> . When the TEST pin is asserted, this pin assumes the alternate function RCLKEN. This output is a buffered version of the internal 80 kHz baud clock that is locked to the received data on the U-interface (or free-running if the U-interface is inactive).    |

| DCL           | 29   | 0                 | GCI Data Clock. Rate defined by GCCF[GRATE(1:0)].                                                                                                                                                                                                                                            |

| (K2_512)      |      | (O)               | <b>K2_512K Clock</b> . When the TEST pin is asserted, this pin assumes the alternate function K2_512. This is the 512 kHz internal data clock from the U block, and is synchronous to the received data on the U-interface.                                                                  |

| FS1<br>(K2_F) | 30   | O<br>(O)          | <b>Programmable Frame Sync 1</b> . Envelope of channel #0 (GCI mode) or frame sync pulse for B1 channel (TDM mode). See Table 28.                                                                                                                                                            |

|               |      |                   | <b>K2_Frame Clock</b> . When the TEST pin is asserted, this pin assumes the alternate function K2_F. This is the 8 kHz frame clock from the U block, and is synchronous to the received data on the U-interface.                                                                             |

| FS2           | 34   | 0                 | Programmable Frame Sync 2. Frame sync pulse for B2 channel. See Table 28.                                                                                                                                                                                                                    |

| (ILOSS)       |      | (I <sup>d</sup> ) | <b>Insertion Loss</b> . When the TEST pin is asserted, this pin assumes the alternate function ILOSS. The ILOSS pin causes the device to continuously transmit an SN1 pattern. This is useful for performing certain tests such as power spectral density. Internal 50 k $\Omega$ pull-down. |

|               |      |                   | No effect on device operation.     I: U transmitter sends SN1 tone continuously.                                                                                                                                                                                                             |

<sup>\*</sup> OD = open-drain output,  $I^d$  = input with an internal 50  $k\Omega$  pull-down.

<sup>†</sup> Depending on the setting of register bit GCCF[GDRIVER], this output can be programmed to either open drain or push-pull.

Table 4. GPIO Pins (24)

| Pin Name F                        | Pin#     | Type*                     | Pin Description                                                                      |  |       |

|-----------------------------------|----------|---------------------------|--------------------------------------------------------------------------------------|--|-------|

| GPIO0.0                           | 72       | I <sup>U</sup> /O         | General-Purpose Programmable I/O Port 0. All of these pins may be con-               |  |       |

| GPIO0.1                           | 73       | I <sup>U</sup> /O         | figured as inputs or outputs (see register GPDIR0). When programmed as               |  |       |

| GPIO0.2                           | 74       | I <sup>U</sup> /O         | inputs, GPIO0.[3:0] may be configured as level or edge-triggered interrupt           |  |       |

| GPIO0.3                           | 75       | I <sup>U</sup> /O         | sources for the 80C32 block (see register GPLEI). GPIO0.[3:0] have                   |  |       |

| GPIO0.4 [PWMO00]                  | 76       | I <sup>U</sup> /O         | Schmitt trigger input buffers. Internal 100 k $\Omega$ pull-up.                      |  |       |

| GPIO0.5 [PWMO01]                  | 77       | I <sup>U</sup> /O         | GPIO0.[7:6] and [5:4] may be alternatively configured (see register GPAF0)           |  |       |

| GPIO0.6 [PWMO10]                  | 78       | I <sup>U</sup> /O         | as outputs from PWM modules 1 and 0, respectively.                                   |  |       |

| GPIO0.7 [PWMO11]                  | 79       | I <sup>U</sup> /O         |                                                                                      |  |       |

| GPIO1.0                           | 81       | I <sup>U</sup> /O         | General-Purpose Programmable I/O Port 1. All of these pins may be con-               |  |       |

| GPIO1.1                           | 82       | I <sup>U</sup> /O         | figured as inputs or outputs (see register GPDIR1). When programmed as               |  |       |

| GPIO1.2                           | 83       | I <sup>U</sup> /O         | inputs, GPIO1.[3:0] may be configured as level- or edge-triggered interrupt          |  |       |

| GPIO1.3                           | 84       | I <sub>0</sub> /O         | sources for the 80C32 block (see register GPLEI). GPIO1.[3:0] have                   |  |       |

| GPIO1.4 (USSP_E)                  | 85       | I⁴/O<br>I <sup>∪</sup> /O | Schmitt trigger input buffers. Internal 100 kΩ pull-up.                              |  |       |

| GPIO1.5 [T0]<br>GPIO1.6 [T1]      | 86<br>87 | I <sup>U</sup> /O         | GPIO1.[7:5] may be alternatively configured (see register GPAF1) as the              |  |       |

| GPIO1.7 [T2]                      | 88       | I <sup>U</sup> /O         | external trigger sources, T2, T1, and T0, respectively, for timers 2:0 on the        |  |       |

| GF101.7 [12]                      | 00       | 1 /0                      | 80C32 block.                                                                         |  |       |

|                                   |          |                           | U-Interface Send Single Pulses—Enable. When the TEST pin is                          |  |       |

|                                   |          |                           | asserted, this pin assumes the alternate function USSP E. This function is           |  |       |

|                                   |          |                           | identical to that controlled by bit UCR1[USSP_E]. This input causes the              |  |       |

|                                   |          |                           | U-interface to continuously transmit single 2B1Q pulses on the U-interface.          |  |       |

|                                   |          |                           | The pulses occur at a rate of 1 pulse per 125 µs and alternate between pos-          |  |       |

|                                   |          |                           | itive and negative polarity. The magnitude of the pulses is controlled by bit        |  |       |

|                                   |          |                           | UCR1[USPMAG].                                                                        |  |       |

|                                   |          |                           | 0: No effect on device operation.                                                    |  |       |

|                                   |          |                           | 1: U transmitter sends single pulses continuously.                                   |  |       |

| GPIO2.0                           | 90       | I <sup>U</sup> /O         | General-Purpose Programmable I/O Port 2. All of these pins may be con-               |  |       |

| GPIO2.1 [BCLK]                    | 91       | I <sup>U</sup> /O         | figured as inputs or outputs (see register GPDIR2). Internal 100 k $\Omega$ pull-up. |  |       |

| GPIO2.2 [FSC]                     | 92       | I <sup>U</sup> /O         | When programmed as an output, GPIO2.0 has a 6 mA current sinking                     |  |       |

| GPIO2.3 [SYNCO]                   | 93       | I <sup>U</sup> /O         | capability.                                                                          |  |       |

| GPIO2.4                           | 94       | I <sup>U</sup> /O         | GPIO2.6 becomes an input to the 8 kHz MTC signal when DOCR[NT-LT] bit                |  |       |

| GPIO2.5                           | 95       | I <sup>U</sup> /O         | is set to 1 (register 0x50).                                                         |  |       |

| GPIO2.6 [MTC]<br>GPIO2.7 (PTLB_S) | 96<br>97 | I <sup>∪</sup> /O         | GPIO2.3 may be alternatively configured (see register GPAF1) as the dc/dc            |  |       |

| GFIOZ.7 (FILB_3)                  | 91       | 1-70                      | output signal SYNCO (see Section 13.1, dc/dc Control Generator Register              |  |       |

|                                   |          |                           |                                                                                      |  | Set). |

|                                   |          |                           |                                                                                      |  |       |

|                                   |          |                           | GPIO2.2 may be alternatively configured (see register GPAF1) as the GCI+             |  |       |

|                                   |          |                           | signal FSC (see Section 10, GCI+ Interface Module).                                  |  |       |

|                                   |          |                           | GPIO2.1 may be alternatively configured (see register GPAF1) as the GCI+             |  |       |

|                                   |          |                           | signal BCLK (see Section 10, GCI+ Interface Module).                                 |  |       |

|                                   |          |                           | Pulse Template/Loopback, S-Interface. When the TEST pin is asserted,                 |  |       |

|                                   |          |                           | this pin assumes the alternate function PTLB_S. This input causes the                |  |       |

|                                   |          |                           | device to perform an S/T-only activation (equivalent to setting SCR0[STOA]           |  |       |

|                                   |          |                           | = 1), and enables a remote loopback towards the TE on the 2B+D channels              |  |       |

|                                   |          |                           | (equivalent to setting SCR1[RLB_D, RLB_B2, RLB_B1] = 1). This is useful              |  |       |

|                                   |          |                           | for performing pulse template and other tests on the S/T-interface. The U-           |  |       |

|                                   |          |                           | interface should be maintained inactive while this function is enabled.              |  |       |

<sup>\*</sup> I = input, O = output, I<sup>d</sup> = input with an internal 50 k $\Omega$  pull-down, I<sup>U</sup> = input with an internal 100 k $\Omega$  pull-up.

## Table 5. 80C32 External Access Pins (27)

The 80C32 external access pins change function when the 80C32 block is placed in on-circuit emulation (ONCE) mode (see Section 6.9, On-Circuit Emulation (ONCE) Mode). The following table lists the normal function for each pin or group of pins first, followed by the function when in ONCE mode.

| Pin Name | Pin#  | Type* | Pin Description                                                                                                                                                                                                                                                                                                                                          |

|----------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[7:0]  | 11—4  | I/O   | <b>Multiplexed Low-Order Address/Data Bus.</b> Used when accessing external memory. AD[7:0] are open-drain bidirectional I/O ports requiring external pull-ups.                                                                                                                                                                                          |

|          |       | I/O   | ONCE mode. AD[7:0] are inputs in all cases except during the read phase of an internal RAM access, where they become outputs to allow the internal RAM to drive data onto the bus to be read by the emulator.                                                                                                                                            |

| A[15:8]  | 20—13 | 0     | <b>Upper Address Bus.</b> Used when accessing external memory. A[15:8] are opendrain, bidirectional I/O ports requiring external pull-ups. In normal mode, they are outputs.                                                                                                                                                                             |

|          | _     | I     | ONCE mode. A[15:8] are inputs. If the address is within the range 0K—4K, the chip will execute the read/write operation on the address indicated. The NTN will not respond to addresses above 4K.                                                                                                                                                        |

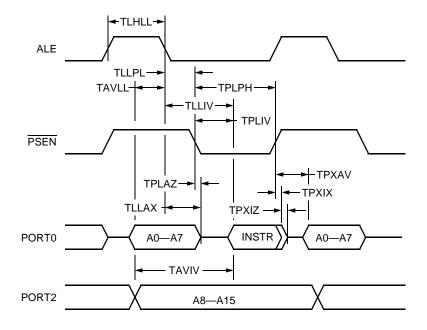

| ALE      | 2     | 0     | <b>Address Latch Enable.</b> Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory.          |

|          | _     | I     | ONCE mode. ALE is an input that is driven directly by the emulator's ALE signal and is used to latch the address applied on A[15:7], AD[7:0].                                                                                                                                                                                                            |

| PSEN     | 1     | 0     | Program Store Enable (Active-Low). Read strobe output to external program memory. When the 80C32 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory. |

|          | _     | HZ    | ONCE mode. PSEN is 3-stated.                                                                                                                                                                                                                                                                                                                             |

| RD       | 27    | 0     | Read Strobe (Active-Low). External data memory read strobe output.                                                                                                                                                                                                                                                                                       |

|          | _     | l     | ONCE mode. $\overline{RD}$ is an input that is driven directly by the emulator's ALE signal and used to access internal memory locations from 0K—4K. The NTN will not respond to addresses above 4K.                                                                                                                                                     |

| WR       | 28    | 0     | Write Strobe (Active-Low). External data memory write strobe output.                                                                                                                                                                                                                                                                                     |

|          |       | I     | ONCE mode. WR is an input that is driven directly by the emulator's ALE signal and used to access internal memory locations from 0K—4K. The NTN will not respond to addresses above 4K.                                                                                                                                                                  |

| XINT0    | 99    | I     | <b>External Interrupt 0 (Active-Low).</b> Input for driving external interrupt #0 signal on 80C32. This signal is fed to the UCI module where it is combined with the rest of the type 0 interrupts from the internal NTN circuitry (i.e., those in register GIR0), and the result is presented to the 80C32 INTO_B input.                               |

|          | _     | OD    | ONCE mode. Interrupt source 0 output. Open-drain output. The UCI module drives this signal low whenever an internal interrupt type 0 condition occurs.                                                                                                                                                                                                   |

<sup>\*</sup> I = input, O = output, HZ = high-impedance, OD = open-drain output, I<sup>d</sup> = input with an internal 50 kΩ pull-down, I<sup>U</sup> = input with an internal 100 kΩ pull-up.

Table 5. 80C32 External Access Pins (27) (continued)

| Pin Name | Pin# | Type*          | Pin Description                                                                                                                                                                                                                                                                                                             |

|----------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XINT1    | 100  | I              | <b>External Interrupt 1 (Active-Low).</b> Input for driving external interrupt #1 signal on 80C32. This signal is fed to the UCI module where it is collapsed with the rest of the type 1 interrupts from the internal NTN circuitry (i.e., those in register GIR1), and the result is presented to the 80C32 INT1_B input. |

|          | _    | OD             | ONCE mode. Interrupt source 1 output. Open-drain output. The UCI module drives this signal low whenever an internal interrupt type 1 condition occurs.                                                                                                                                                                      |

| CLKO     | 24   | 0              | <b>Microcontroller Clock Output.</b> Outputs clock based on settings in register UPCK (see Section 6.7, Clock Generator).                                                                                                                                                                                                   |

|          | _    | 0              | ONCE mode. Same behavior as in normal mode. Can be used to supply clock to external emulator.                                                                                                                                                                                                                               |

| SLP      | 21   | Iυ             | Internal Microsleep Input (Active-Low). Activates ONCE mode when $\overline{\text{SLP}}$ is low upon an exit from RESET. Internal 100 k $\Omega$ pull-up.                                                                                                                                                                   |

|          |      | Ι <sup>υ</sup> | ONCE mode. Same behavior as in normal mode. Internal pull-up.                                                                                                                                                                                                                                                               |

| RXD      | 26   | Ιd             | <b>80C32 Serial Input Port.</b> Connected directly to P3.0 of 80C32 block. Can also be used as a programmable I/O by appropriate programming of the SFR direction register DIR3 and the SFR port register P3. Internal 50 k $\Omega$ pull-down.                                                                             |

|          | _    | HZ             | ONCE mode. RXD is 3-stated.                                                                                                                                                                                                                                                                                                 |

| TXD      | 23   | <b>I</b> d     | <b>80C32 Serial Output Port.</b> Connected directly to P3.1 of 80C32 block. Can also be used as a programmable I/O by appropriate programming of the SFR direction register DIR3 and the SFR port register P3 (see Section 6.12, Special Instructions for Using the Lucent 80C32 Block). Internal 50 k $\Omega$ pull-down.  |

|          | _    | HZ             | ONCE mode. TXD is 3-stated.                                                                                                                                                                                                                                                                                                 |

| ĒĀ       | 70   | I              | <b>External Access (Active-Low).</b> When $\overline{EA}$ is held high, the microcontroller executes instructions from the internal program memory. Holding $\overline{EA}$ low forces the microcontroller to execute instructions from external program memory. Internal 100 k $\Omega$ pullup.                            |

|          | _    | _              | ONCE mode. Holding EA low disables access to the internal memory in the NTN device.                                                                                                                                                                                                                                         |

<sup>\*</sup> I = input, O = output, HZ = high-impedance, OD = open-drain output, I<sup>d</sup> = input with an internal 50 k $\Omega$  pull-down, I<sup>U</sup> = input with an internal 100 k $\Omega$  pull-up.

Table 6. Comparators (6)

| Pin Name | Pin# | Type* | Pin Description                                                        |

|----------|------|-------|------------------------------------------------------------------------|

| INP0     | 46   | I     | <b>Input Positive, Comparator 0.</b> Connect to 5 V via 1 k $\Omega$ . |

| INN0     | 45   | I     | Input Negative, Comparator 0. Connect to GND via 1 k $\Omega$ .        |

| INP1     | 48   | I     | <b>Input Positive, Comparator 1.</b> Connect to 5 V via 1 k $\Omega$ . |

| INN1     | 47   | I     | <b>Input Negative, Comparator 1.</b> Connect to GND via 1 k $\Omega$ . |

| INP2     | 50   | I     | <b>Input Positive, Comparator 2.</b> Connect to 5 V via 1 kΩ.          |

| INN2     | 49   | I     | Input Negative, Comparator 2. Connect to GND via 1 k $\Omega$ .        |

<sup>\*</sup> I = input.

## Table 7. JTAG Pins (4)

| Pin Name        | Pin# | Type*              | Pin Description                                                                                                                                                                                                        |

|-----------------|------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTCK<br>(C1536) | 41   | I <sup>U</sup>     | <b>JTAG TAP Clock.</b> It is recommended that this pin be externally pulled to V <sub>DD</sub> during normal operation. Internal 100 k $\Omega$ pull-up.                                                               |

|                 |      |                    | <b>15.36 MHz System Clock</b> . When the TEST pin is asserted, this pin assumes the alternate function C1536. This output is a buffered version of the internal 15.36 MHz system clock that is used by the NTN device. |

| JTMS<br>(TCI)   | 42   | I <sup>U</sup> (O) | <b>JTAG TAP Mode Select.</b> This pin is externally pulled to V <sub>DD</sub> through approximately 20 k $\Omega$ . Internal 100 k $\Omega$ pull-up.                                                                   |

|                 |      |                    | <b>Test Control In</b> . When the TEST pin is asserted, this pin assumes the alternate function TCI. This pin is used for factory testing.                                                                             |

|                 |      |                    | <b>Note:</b> When in test mode, TCI must not be pulled low by the user when not being actively driven.                                                                                                                 |

| JTDI<br>(TDI)   | 40   | Ιυ                 | <b>JTAG Serial Data Input.</b> This pin is internally pulled to V <sub>DD</sub> through approximately 20 k $\Omega$ . Internal 100 k $\Omega$ pull-up.                                                                 |

|                 |      |                    | <b>Test Data In.</b> When the TEST pin is asserted, the GPIO1.7 pin assumes the alternate function TDI. This pin is used for factory testing.                                                                          |

| JTDO            | 35   | 0                  | JTAG Serial Data Output.                                                                                                                                                                                               |

| (TDO)           |      |                    | <b>Test Data Out</b> . When the TEST pin is asserted, this pin assumes the alternate function TDO. This pin is used for factory testing.                                                                               |

<sup>\*</sup> I = input, O = output,  $I^U$  = input with an internal 100 k $\Omega$  pull-up.

Table 8. Miscellaneous Pins (2)

| Pin Name | Pin# | Type*      | Pin Description                                                                                                                                                                                                                                                                                                                                                            |

|----------|------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET    | 31   | ľα         | Reset Input (Active-High). This signal resets the entire device. During RESET, the U transmitter produces 0 V. This puts the U-interface in the QUIET maintenance mode as described in $ANSI$ T1.601 Section 6.5. RESET should be asserted whenever return loss and longitudinal balance measurements are being made on the U-interface. Internal 50 k $\Omega$ pull-down. |

| TEST     | 43   | <b>l</b> q | <b>Test Input (Active-High).</b> During normal operation, this signal should be maintained high. Internal 50 k $\Omega$ pull-down. Please see Section 15, Test Mode for more details.                                                                                                                                                                                      |

<sup>\*</sup> I = input, O = output, I d = input with an internal 50 k $\Omega$  pull-down.

## Table 9. Oscillator Pins (2)

| Pin Name | Pin# | Type* | Pin Description                                                                                                                                                                                                  |

|----------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTAL1    | 37   | I     | <b>Crystal In</b> . 15.36 MHz oscillator input. When using an external crystal, one of the crystal pins is connected to this pin. This pin may also be driven by an external oscillator with CMOS output levels. |

| XTAL0    | 38   | 0     | <b>Crystal Out</b> . 15.36 MHz oscillator output. When using an external crystal, one of the crystal pins is connected to this pin. When using an external oscillator, this pin is left unconnected.             |

<sup>\*</sup> I = input, O = output.

### **Table 10. Power and Ground Pins**

| Pin Name | Pin #                         | Туре | Pin Description                                                                |

|----------|-------------------------------|------|--------------------------------------------------------------------------------|

| VDDD     | 3, 22, 39, 80                 | _    | <b>Digital Power</b> . 5 V $\pm$ 5% power supply pins for digital circuitry.   |

| GND□     | 12, 25, 36, 44, 69,<br>89, 98 | _    | Digital Ground. Ground leads for digital circuitry.                            |

| VDDA     | 53, 57, 67                    | _    | <b>Analog Power</b> . 5 V $\pm$ 5% power supply lead for the analog circuitry. |

| GNDA     | 52, 59, 66                    | _    | Analog Ground. Ground leads for analog circuitry.                              |

# **5 Control Register Memory Space**

**Table 11. Control Register Memory Space**

| Register Address | Register Mnemonic | Description                                | Refer To            |

|------------------|-------------------|--------------------------------------------|---------------------|

| 0x00             | GIR0              | Global Interrupt Register 0                | Table 12 on page 18 |

| 0x01             | GIR1              | Global Interrupt Register 1                | Table 13 on page 19 |

| 0x02             | GIE               | Global Interrupt Enable Register           | Table 14 on page 20 |

| 0x03             | UPCK              | Microcontroller Clock Control Register     | Table 15 on page 21 |

| 0x04             | WDT               | Microcontroller Watchdog Timer Control     | Table 16 on page 22 |

| 0x05             | DFCF              | DFAC Configuration Register                | Table 22 on page 33 |

| 0x06             | DFR               | Data Flow Register                         | Table 23 on page 34 |

| 0x07             | UCR0              | U-Interface Control Register #0            | Table 24 on page 35 |

| 0x08             | UCR1              | U-Interface Control Register #1            | Table 25 on page 36 |

| 0x09             | USR0              | U-Interface Status Register #0             | Table 26 on page 37 |

| 0x0A             | USR1              | U-Interface Status Register #1             | Table 27 on page 37 |

| 0x0B             | ECR0              | EOC Control Register 0—Command and Address | Table 28 on page 38 |

| 0x0C             | ECR1              | EOC Control Register 1—Message             | Table 29 on page 39 |

| 0x0D             | ESR0              | EOC Status Register 0—Command and Address  | Table 30 on page 39 |

| 0x0E             | ESR1              | EOC Status Register 1—Message              | Table 31 on page 39 |

| 0x0F             | SCR0              | S-Interface Control Register #0            | Table 32 on page 40 |

| 0x10             | SCR1              | S-Interface Control Register #1            | Table 33 on page 41 |

| 0x11             | SSR               | S-Interface Status Register                | Table 34 on page 42 |

| 0x12             | MFR0              | Multiframe Register, Q-Channel Data        | Table 35 on page 43 |

| 0x13             | MFR1              | Multiframe Register, S-Subchannel Data     | Table 36 on page 43 |

| 0x14             | UIR               | U-Interface Interrupt Register             | Table 37 on page 44 |

| 0x15             | UIE               | U-Interface Enable Register                | Table 38 on page 45 |

| 0x16             | SIR               | S-Interface Interrupt Register             | Table 39 on page 46 |

| 0x17             | SIE               | S-Interface Enable Register                | Table 40 on page 46 |

| 0x18             | HTCF              | HDLC Transmitter Configuration Register    | Table 55 on page 58 |

| 0x19             | HRCF              | HDLC Receiver Configuration Register       | Table 56 on page 59 |

| 0x1A             | HTTH              | HDLC Transmit FIFO Threshold               | Table 57 on page 60 |

| 0x1B             | HRTH              | HDLC Receive FIFO Threshold                | Table 58 on page 60 |

| 0x1C             | HTSA              | HDLC Transmit FIFO Space Available         | Table 59 on page 61 |

| 0x1D             | HRDA              | HDLC Receive FIFO Data Available           | Table 60 on page 61 |

| 0x1E             | HTX               | HDLC Transmit Data                         | Table 61 on page 61 |

| 0x1F             | HTXL              | HDLC Transmit Data Last Byte               | Table 62 on page 62 |

| 0x20             | HRX               | HDLC Receive Data                          | Table 63 on page 62 |

| 0x21             | HSCR              | HDLC SAPI C/R Bit Mask                     | Table 64 on page 62 |

| 0x22             | HSM0              | HDLC SAPI Match Pattern 0                  | Table 65 on page 63 |

| 0x23             | HTM0              | HDLC TEI Match Pattern 0                   | Table 66 on page 63 |

| 0x24             | HSM1              | HDLC SAPI Match Pattern 1                  | Table 67 on page 63 |

| 0x25             | HTM1              | HDLC TEI Match Pattern 1                   | Table 68 on page 64 |

| 0x26             | HSM2              | HDLC SAPI Match Pattern 2                  | Table 69 on page 64 |

| 0x27             | HTM2              | HDLC TEI Match Pattern 2                   | Table 70 on page 64 |

| 0x28             | HSM3              | HDLC SAPI Match Pattern 3                  | Table 71 on page 64 |

| 0x29             | HTM3              | HDLC TEI Match Pattern 3                   | Table 72 on page 65 |

| 0x2A             | HSMOD             | HDLC SAPI Modifier Register                | Table 73 on page 65 |

| 0x2B             | HTMOD             | HDLC TEI Modifier Register                 | Table 74 on page 66 |

| 0x2C             | HIR               | HDLC Interrupt Register                    | Table 75 on page 67 |

| 0x2D             | HIE               | HDLC Interrupt Enable 15                   | Table 76 on page 68 |

| 0x2E             | GCCF              | GCI+ Configuration Register                | Table 80 on page 79 |

# **5 Control Register Memory Space** (continued)

**Table 11. Control Register Memory Space** (continued)

| Register Address | Register Mnemonic | Description                                          | Refer To              |

|------------------|-------------------|------------------------------------------------------|-----------------------|

| 0x2F             | GCOF1             | GCI PFS1 Offset Select                               | Table 81 on page 80   |

| 0x30             | GCOF2             | GCI PFS2 Offset Select                               | Table 82 on page 80   |

| 0x31             | GCDMD             | GCI Downstream (Transmit) Monitor Data               | Table 83 on page 81   |

| 0x32             | GCDML             | GCI Downstream (Transmit) Monitor Data Last          | Table 84 on page 81   |

| 0x33             | GCUMD             | GCI Upstream (Receive) Monitor Data                  | Table 85 on page 81   |

| 0x34             | GCDCI             | GCI Downstream (Transmit) C/I Data                   | Table 86 on page 82   |

| 0x35             | GCUCI             | GCI Upstream (Receive) C/I Data                      | Table 87 on page 82   |

| 0x36             | GCIR              | GCI Interrupt Register                               | Table 88 on page 83   |

| 0x37             | GCIE              | GCI Interrupt Enable                                 | Table 89 on page 84   |

| 0x38             | GPDIR0            | GPIO Port 0 Pin Direction                            | Table 90 on page 86   |

| 0x39             | GPDIR1            | GPIO Port 1 Pin Direction                            | Table 91 on page 87   |

| 0x3A             | GPDIR2            | GPIO Port 2 Pin Direction                            | Table 92 on page 87   |

| 0x3B             | GPAF0             | GPIO Alternate Function Register #0                  | Table 93 on page 88   |

| 0x3C             | GPAF1             | GPIO Alternate Function Register #1                  | Table 94 on page 89   |

| 0x3D             | GPD0              | GPIO Port 0 Data Register                            | Table 95 on page 89   |

| 0x3E             | GPD1              | GPIO Port 1 Data Register                            | Table 96 on page 90   |

| 0x3F             | GPD2              | GPIO Port 2 Data Register                            | Table 97 on page 90   |

| 0x40             | GPLEI             | GPIO Level-Edge-Triggered Interrupt Control          | Table 98 on page 90   |

| 0x41             | GPPOL             | GPIO Interrupt Polarity Control                      | Table 99 on page 91   |

| 0x42             | GPIR              | GPIO Interrupt Register                              | Table 100 on page 91  |

| 0x43             | GPIE              | GPIO Interrupt Enable                                | Table 101 on page 92  |

| 0x44             | PW0CF             | Pulse-Width Modulator 0 Configuration                | Table 104 on page 100 |

| 0x45             | PW0VH             | Pulse-Width Modulator 0 Pulse-Width Value, High Byte | Table 105 on page 101 |

| 0x46             | PW0VL             | Pulse-Width Modulator 0 Pulse-Width Value, Low Byte  | Table 106 on page 101 |

| 0x47             | PW1CF             | Pulse-Width Modulator 1 Configuration                | Table 107 on page 102 |

| 0x48             | PW1VH             | Pulse-Width Modulator 1 Pulse-Width Value, High Byte | Table 108 on page 103 |

| 0x49             | PW1VL             | Pulse-Width Modulator 1 Pulse-Width Value, Low Byte  | Table 109 on page 103 |

| 0x4A             | PWIR              | Pulse-Width Modulator Interrupt Register             | Table 110 on page 103 |

| 0x4B             | DCCF              | dc/dc Configuration Register                         | Table 111 on page 104 |

| 0x4C             | CME               | Comparator Enable                                    | Table 113 on page 106 |

| 0x4D             | CMT               | Comparator Transition Polarity                       | Table 114 on page 106 |

| 0x4E             | CMIR              | Comparator Interrupt Register                        | Table 115 on page 107 |

| 0x4F             | CMIE              | Comparator Interrupt Enable                          | Table 116 on page 107 |

| 0x50             | DOCR              | Device Operation Control Register                    | Table 41 on page 47   |

| 0x51             | B1UP              | B1-Channel Upstream Data from GCI to U-Interface     | Table 42 on page 47   |

| 0x52             | B2UP              | B2-Channel Upstream Data from GCI to U-Interface     | Table 43 on page 48   |

| 0x53             | B1DN              | B1-Channel Downstream Data from GCI to U-Interface   | Table 44 on page 48   |

| 0x54             | B2DN              | B2-Channel Downstream Data from GCI to U-Interface   | Table 45 on page 48   |

| 0x55             | Reserved1         | Reserved Register for Internal Use                   | Table 46 on page 49   |

| 0x56             | Reserved2         |                                                      | Table 47 on page 49   |

| 0x57             | Reserved3         |                                                      | Table 48 on page 49   |

| 0x58             | Reserved4         |                                                      | Table 49 on page 50   |

| 0x59             | Reserved5         |                                                      | Table 50 on page 50   |

| 0x5A             | Reserved6         |                                                      | Table 51 on page 50   |

| 0x5B             | Reserved7         |                                                      | Table 52 on page 50   |

| 0x5C             | Reserved8         |                                                      | Table 53 on page 51   |

| 0x5D             | Reserved9         |                                                      | Table 54 on page 51   |

### **6 Functional Modules**

This section covers the functionality of the NTN core modules.

# 6.1 80C32 Microcontroller Module (80C32 Block)

The NTN IC includes an embedded 80C32 microcontroller, incorporating a 256-byte internal RAM, three 16-bit timer/counters, six interrupt sources, and one serial port I/O.

Typical functions of the microcontroller module are as follows:

- Definition of operation modes for all other NTN modules (U-interface, S/T-interface, etc.)

- Configuration of the 2B+D data flow paths in the DFAC module

- Layer 2 and layer 3 processing of the D channel for POTS calls

- Supervision of the POTS circuitry

- Device power management

## 6.2 Program Address Space

The on-chip 64K x 8 mask-programmable ROM occupies the full program memory space addressable by the 80C32. The 80C32 addresses this memory via the microcontroller interface (UCI) module.

The internal ROM can be disabled so that code from an external ROM can be executed by tying the EA pin low. The microcontroller then fetches the program instructions through its external access port (see Table 5). Applications requiring a larger program space than the 64K x 8 available with the standard 80C32 may use GPIO ports to extend the address space using a paging scheme.

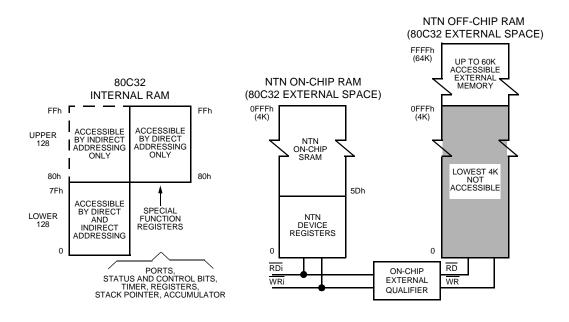

### 6.3 Data Address Space