The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

SH7706 Group Hardware Manual

Renesas 32-Bit RISC Microcomputer SuperH™ RISC engine Family/SH7700 Series

Jardware Manua

Rev.4.00 Revision Date: Mar. 22, 2004 RenesasTechnology www.renesas.com

## Keep safety first in your circuit designs!

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any thirdparty's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

# **General Precautions on Handling of Product**

#### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are they are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

### 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

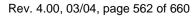

## 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

#### 4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

# Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. Appendix

- 10. Main Revisions and Additions in this Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier versions. This does not include all of the revised contents. For details, see the actual locations in this manual.

11. Index

# **Preface**

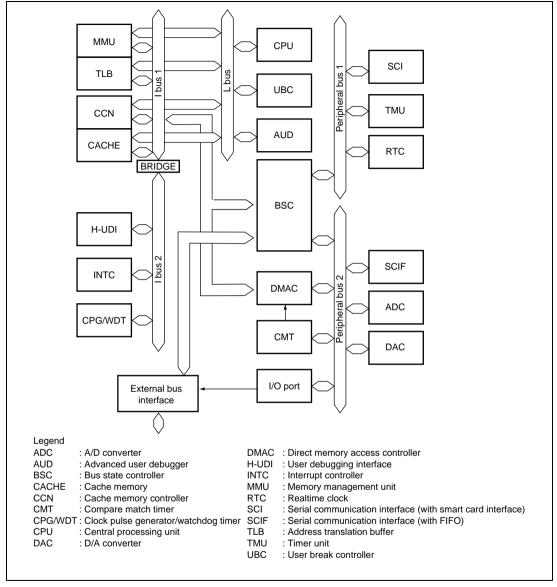

The SH7706 RISC (Reduced Instruction Set Computer) microcomputer includes a Renesas Technology-original RISC CPU as its core, and the peripheral functions required to configure a system.

Target Users: This manual was written for users who will be using this LSI in the design of

application systems. Users of this manual are expected to understand the fundamentals of electrical circuits, logical circuits, and microcomputers.

Objective: This manual was written to explain the hardware functions and electrical

characteristics of this LSI to the above users.

Refer to the SH-3/SH-3E/SH3-DSP Programming Manual for a detailed description

of the instruction set.

#### Notes on reading this manual:

Product names

The following products are covered in this manual.

#### **Product Classifications and Abbreviations**

| Basic Classification           | Product Code    |

|--------------------------------|-----------------|

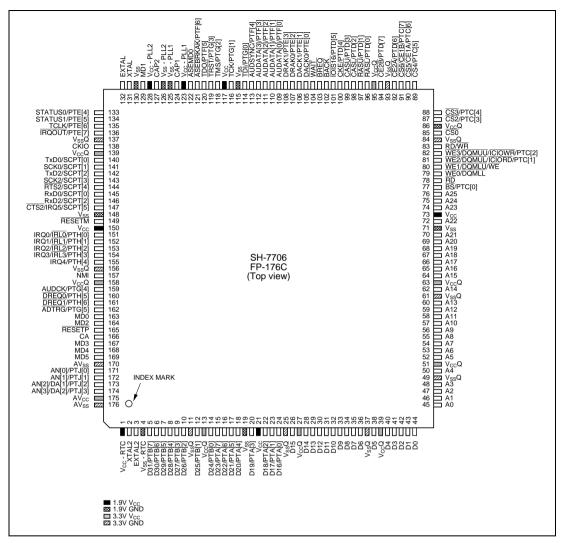

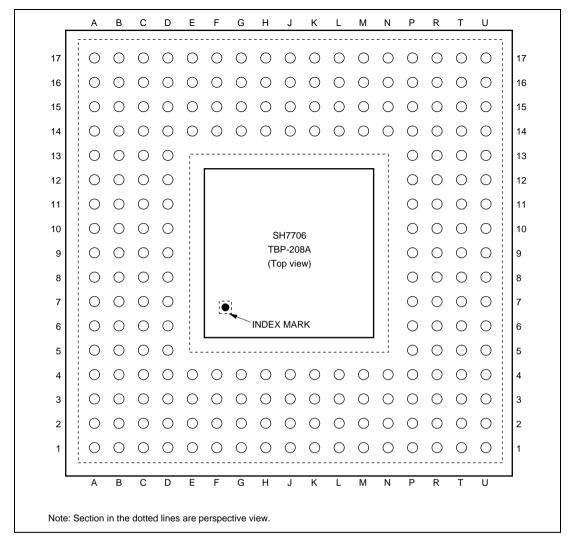

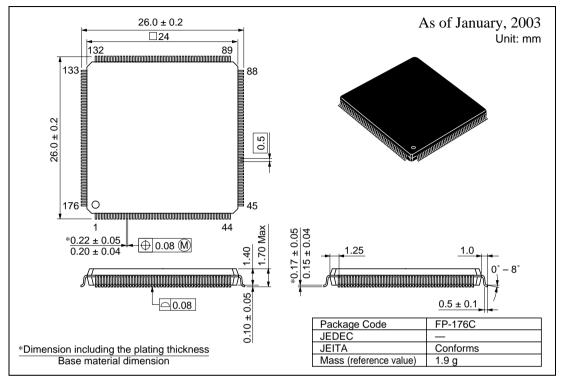

| SH7706 (176-pin plastic LQFP)  | HD6417706F133   |

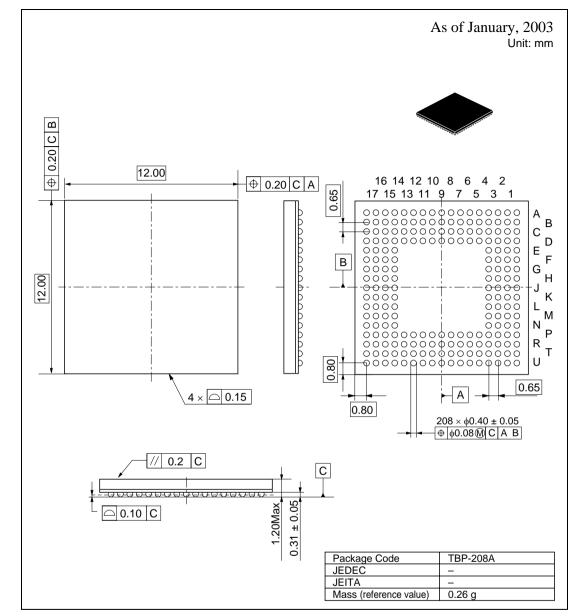

| SH7706 (208-pin plastic TFBGA) | HD6417706BP133V |

In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized into parts on the CPU, system control functions, peripheral functions and electrical characteristics.

• In order to understand the details of the CPU's functions

Read the SH-3/SH-3E/SH3-DSP Programming Manual.

Rules: Register name: The following notation is used for cases when the same or a

similar function, e.g. serial communication, is implemented

on more than one channel:

XXX\_N (XXX is the register name and N is the channel

number)

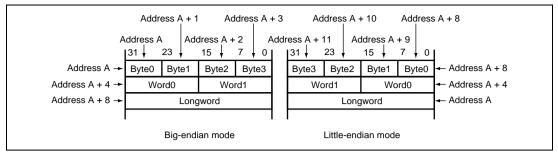

Bit order: The MSB (most significant bit) is on the left and the LSB

(least significant bit) is on the right.

Number notation: Binary is B'xxxx, hexadecimal is H'xxxx, decimal is xxxx.

Signal notation: An overbar is added to a low-active signal:  $\overline{xxxx}$

Related Manuals: The latest versions of all related manuals are available from our web site.

Please ensure you have the latest versions of all documents you require.

http://www.renesas.com/eng/

#### SH7706 manuals:

| Document Title                        | Document No. |

|---------------------------------------|--------------|

| SH7706 Hardware Manual                | This manual  |

| SH-3/SH-3E/SH3-DSP Programming Manual | ADE-602-096  |

## Users manuals for development tools:

| Document Title                                                                                 | Document No. |

|------------------------------------------------------------------------------------------------|--------------|

| SH Series C/C++ Compiler, Assembler, Optimizing Linkage Editor User's Manual                   | ADE-702-246  |

| SH Series Simulator/Debugger (for Windows) User's Manual                                       | ADE-702-186  |

| SH Series Simulator/Debugger (for UNIX) User's Manual                                          | ADE-702-203  |

| High-performance Embedded Workshop User's Manual                                               | ADE-702-201  |

| SH Series High-performance Embedded Workshop,<br>High-performance Debugging Interface Tutorial | ADE-702-230  |

Abbreviations

ACIA Asynchronous Communication Interface Adapter

ADC Analog to Digital Converter

AUD Advanced User Debugger

BSC Bus State Controller

CPG Clock Pulse Generator

CMT Compare Match Timer

DAC Digital to Analog Converter

DMA Direct Memory Access

DMAC Direct Memory Access Controller

DRAM Dynamic Random Access Memory

ETU Elementary Time Unit

FIFO First-In First-Out

H-UDI User Debugging Interface

INTC Interrupt Controller

JEIDA Japan Electronic Industry Development Association

JTAG Joint Test Action Group

LRU Least Recently Used

LSB Least Significant Bit

MMU Memory Management Unit

MSB Most Significant Bit

PCMCIA Personal Computer Memory Card International Association

PFC Pin Function Controller

PLL Phase Locked Loop

RISC Reduced Instruction Set Computer

ROM Read Only Memory

RTC Realtime Clock

SCI Serial Communication Interface

SCIF Serial Communication Interface with FIFO

SRAM Static Random Access Memory

TLB Translation Lookaside Buffer

TMU Timer Unit

UART Universal Asynchronous Receiver/Transmitter

UBC User Break Controller

WDT Watchdog Timer

# Main Revisions and Additions in this Edition

| Item                                               | Page    | Revision (See                                                                                                                                                                                                                                                                                                                                                             | Manual for Deta                                                  | ils)              |                                 |  |  |

|----------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------|---------------------------------|--|--|

| 1.2 Block Diagram                                  | 4       | Figure 1.1 title                                                                                                                                                                                                                                                                                                                                                          | amended                                                          |                   |                                 |  |  |

| Figure 1.1 Pin Assignment (TBP-208A)               |         |                                                                                                                                                                                                                                                                                                                                                                           |                                                                  |                   |                                 |  |  |

| 1.4 Pin Function                                   | 6 to 12 | Package name                                                                                                                                                                                                                                                                                                                                                              | amended                                                          |                   |                                 |  |  |

|                                                    |         | Number of P                                                                                                                                                                                                                                                                                                                                                               | Pins                                                             | <del></del>       |                                 |  |  |

|                                                    |         | FP-176C                                                                                                                                                                                                                                                                                                                                                                   | TBP-208A                                                         | Pin Name          |                                 |  |  |

|                                                    | 9       | Description am                                                                                                                                                                                                                                                                                                                                                            | ended                                                            |                   |                                 |  |  |

|                                                    |         | Chip select 0                                                                                                                                                                                                                                                                                                                                                             |                                                                  |                   |                                 |  |  |

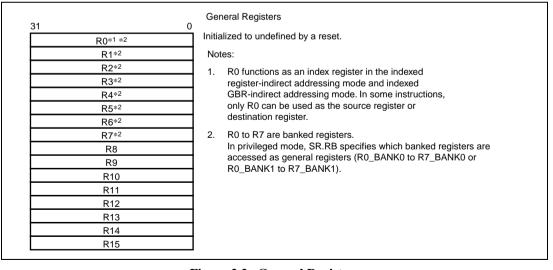

| 2.1.4 Control Registers                            | 18      | Status Regis                                                                                                                                                                                                                                                                                                                                                              | ster (SR)                                                        |                   |                                 |  |  |

|                                                    |         | Description of bit 29 amended                                                                                                                                                                                                                                                                                                                                             |                                                                  |                   |                                 |  |  |

|                                                    |         | Register bank b                                                                                                                                                                                                                                                                                                                                                           | oit                                                              |                   |                                 |  |  |

|                                                    |         | Determines the mode                                                                                                                                                                                                                                                                                                                                                       | bank of general                                                  | registers R0 to R | 7 used in privileged            |  |  |

| 2.3.2 Addressing Modes                             | 26      | Note amended                                                                                                                                                                                                                                                                                                                                                              |                                                                  |                   |                                 |  |  |

| Table 2.2 Addressing Modes and Effective Addresses |         | Note: For the addressing modes below that use a displacement (disp), the assembler descriptions in this manual show the value before scaling ( $\times$ 1, $\times$ 2, or $\times$ 4) is performed according to the operand size. This is done to clarify the operation of the LSI. Refer to the relevant assembler notation rules for the actual assembler descriptions. |                                                                  |                   |                                 |  |  |

| 2.4.1 Instruction Set                              | 38      | Table 2.7 amer                                                                                                                                                                                                                                                                                                                                                            | nded                                                             |                   |                                 |  |  |

| Classified by Function                             |         | Instruction                                                                                                                                                                                                                                                                                                                                                               | Operation                                                        | Code              | Privileged<br>Mode Cycles T Bit |  |  |

| Table 2.7 Logic Operation<br>Instructions          |         | TAS.B @Rn*                                                                                                                                                                                                                                                                                                                                                                | If (Rn) is 0, 1 $\rightarrow$ T;<br>1 $\rightarrow$ MSB of (Rn)* | 0100nnnn00011011  | — 4 Test result                 |  |  |

# 2.4.1 Instruction Set Classified by Function

Table 2.10 System Control Instructions

#### Table 2.10 amended

41 to

43

|           |                  |                                                                                                                                                       |                  | Privileged |        |       |

|-----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|--------|-------|

| Instructi | ion              | Operation                                                                                                                                             | Code             | Mode       | Cycles | T Bit |

| CLRMAC    | 2                | $0 \to MACH,MACL$                                                                                                                                     | 000000000101000  | _          | 1      | _     |

| CLRS      |                  | $0 \rightarrow S$                                                                                                                                     | 000000001001000  | _          | 1      | _     |

| CLRT      |                  | $0 \to T$                                                                                                                                             | 0000000000001000 | _          | 1      | 0     |

| LDC       | Rm,SR            | $Rm \to SR$                                                                                                                                           | 0100mmmm00001110 | √          | 5      | LSB   |

| LDC       | Rm,GBR           | $Rm \to GBR$                                                                                                                                          | 0100mmmm00011110 | _          | 3      | _     |

| LDC       | Rm, VBR          | $Rm \to VBR$                                                                                                                                          | 0100mmmm00101110 | <b>V</b>   | 3      | _     |

| LDC       | Rm,SSR           | $Rm \to SSR$                                                                                                                                          | 0100mmmm00111110 | √          | 3      | _     |

| LDC       | Rm,SPC           | $Rm \to SPC$                                                                                                                                          | 0100mmmm01001110 | √          | 3      | _     |

| LDC       | Rm,R0_BANK       | $Rm \to R0\_BANK$                                                                                                                                     | 0100mmmm10001110 | √          | 3      | _     |

| LDC       | Rm,R1_BANK       | $Rm \to R1\_BANK$                                                                                                                                     | 0100mmmm10011110 | <b>V</b>   | 3      | _     |

| LDC       | Rm,R2_BANK       | $Rm \to R2\_BANK$                                                                                                                                     | 0100mmmm10101110 | √          | 3      | _     |

| LDC       | Rm,R3_BANK       | $Rm \rightarrow R3\_BANK$                                                                                                                             | 0100mmmm10111110 | √          | 3      | _     |

| LDC       | Rm,R4_BANK       | $Rm \to R4\_BANK$                                                                                                                                     | 0100mmmm11001110 | √          | 3      | _     |

| LDC       | Rm,R5_BANK       | $Rm \to R5\_BANK$                                                                                                                                     | 0100mmmm11011110 | √          | 3      | _     |

| LDC       | Rm,R6_BANK       | $Rm \to R6\_BANK$                                                                                                                                     | 0100mmmm11101110 | √          | 3      | _     |

| LDC       | Rm,R7_BANK       | $Rm \rightarrow R7\_BANK$                                                                                                                             | 0100mmmm11111110 | √          | 3      | _     |

| LDC.L     | @Rm+,SR          | $(Rm) \rightarrow SR, Rm + 4 \rightarrow Rm$                                                                                                          | 0100mmmm00000111 | √          | 7      | LSB   |

| LDC.L     | @Rm+,GBR         | $(Rm) \rightarrow GBR, Rm + 4 \rightarrow Rm$                                                                                                         | 0100mmmm00010111 | _          | 5      | _     |

| LDC.L     | @Rm+,VBR         | $(Rm) \rightarrow VBR, Rm + 4 \rightarrow Rm$                                                                                                         | 0100mmmm00100111 | √          | 5      | _     |

| LDC.L     | @Rm+,SSR         | $(Rm) \rightarrow SSR, Rm + 4 \rightarrow Rm$                                                                                                         | 0100mmmm00110111 | √          | 5      | _     |

| LDC.L     | @Rm+,SPC         | $(Rm) \rightarrow SPC, Rm + 4 \rightarrow Rm$                                                                                                         | 0100mmmm01000111 | √          | 5      | _     |

| LDC.L     | @Rm+,<br>RO_BANK | $(Rm) \rightarrow R0\_BANK,$<br>$Rm + 4 \rightarrow Rm$                                                                                               | 0100mmmm10000111 | 1          | 5      | _     |

| LDC.L     | @Rm+,<br>R1_BANK | $(Rm) \rightarrow R1\_BANK,$<br>$Rm + 4 \rightarrow Rm$                                                                                               | 0100mmmm10010111 | √          | 5      | _     |

| LDC.L     | @Rm+,<br>R2_BANK | $(Rm) \rightarrow R2\_BANK,$<br>$Rm + 4 \rightarrow Rm$                                                                                               | 0100mmmm10100111 | 1          | 5      | _     |

| LDC.L     |                  | $(Rm) \rightarrow R3\_BANK,$<br>$Rm + 4 \rightarrow Rm$                                                                                               | 0100mmmm10110111 | √          | 5      | _     |

| LDC.L     |                  | (Rm) → R4_BANK,                                                                                                                                       | 0100mmmm11000111 | <i>√</i>   | 5      | _     |

|           | R4_BANK          | Rm + 4 → Rm                                                                                                                                           | 010000000111     | ,          |        |       |

| LDC.L     | @Rm+,<br>R5_BANK | $(Rm) \rightarrow R5\_BANK,$<br>$Rm + 4 \rightarrow Rm$                                                                                               | 0100mmmm11010111 | <b>V</b>   | 5      | _     |

| LDC.L     | @Rm+,<br>R6_BANK | $(Rm) \rightarrow R6\_BANK,$<br>$Rm + 4 \rightarrow Rm$                                                                                               | 0100mmmm11100111 | √          | 5      | _     |

| LDC.L     | R7_BANK          | $(Rm) \rightarrow R7\_BANK,$<br>$Rm + 4 \rightarrow Rm$                                                                                               | 0100mmmm11110111 | 1          | 5      | _     |

| PREF      | @Rm              | (Rm) → cache                                                                                                                                          | 0000mmmm10000011 | _          | 2      | _     |

|           |                  |                                                                                                                                                       |                  |            |        |       |

|           | SR,@-Rn          | $Rn-4 \rightarrow Rn, SR \rightarrow (Rn)$                                                                                                            | 0100nnnn00000011 | √          | 2      |       |

|           | GBR,@-Rn         | Rn–4 → Rn, GBR → (Rn)                                                                                                                                 | 0100nnnn00010011 | _          | 2      |       |

|           | VBR,@—Rn         | $Rn-4 \rightarrow Rn, VBR \rightarrow (Rn)$                                                                                                           | 0100nnnn00100011 | √<br>/     | 2      |       |

| STC.L     | SSR,@-Rn         | $Rn-4 \rightarrow Rn, SSR \rightarrow (Rn)$                                                                                                           | 0100nnnn00110011 | √          | 2      | _     |

| STC.L     | SPC,@-Rn         | $Rn4 \to Rn,  SPC \to (Rn)$                                                                                                                           | 0100nnnn01000011 | √          | 2      | _     |

| TRAPA     | #imm             | $\label{eq:pc} \begin{split} \text{PC} &\rightarrow \text{SPC},  \text{SR} \rightarrow \text{SSR}, \\ \text{imm} &\rightarrow \text{TRA} \end{split}$ | 11000011iiiiiiii | _          | 8      | -     |

#### 2.4.2 Instruction Code Map

Table 2.11 Instruction Code Map

Table 2.11 amended

45

| Ir   | Instruction Code |      | nstruction Code Fx: 0000 |       |             | Fx: 0001 |             | Fx: 0010 |             | Fx: 0011 to 1111 |           |

|------|------------------|------|--------------------------|-------|-------------|----------|-------------|----------|-------------|------------------|-----------|

| MSB  |                  |      | LSB                      |       | MD: 00      |          | MD: 01      |          | MD: 10      | MD: 11           |           |

| 0000 | Rn               | Fx   | 0000                     |       |             |          |             |          |             |                  |           |

| 0000 | Rn               | Fx   | 0001                     |       |             |          |             |          |             |                  |           |

| 0000 | Rn               | 00MD | 0010                     | STC   | SR,Rn       | STC GBF  | t,Rn        | STC VBF  | R,Rn        | STC SSI          | R,Rn      |

| 0000 | Rn               | 01MD | 0010                     | STC   | SPC,Rn      |          |             |          |             |                  |           |

| 0000 | Rn               | 10MD | 0010                     | STC   | R0_BANK,Rn  | STC      | R1_BANK,Rn  | STC      | R2_BANK,Rn  | STC              | R3_BANK,R |

| 0000 | Rn               | 11MD | 0010                     | STC   | R4_BANK,Rn  | STC      | R5_BANK,Rn  | STC      | R6_BANK,Rn  | STC              | R7_BANK,R |

| 0000 | Rm               | 00MD | 0011                     | BSRF  | Rm          |          |             | BRAF     | Rm          |                  |           |

| 0000 | Rm               | 10MD | 0011                     | PREF  | @Rm         |          |             |          |             |                  |           |

| 0000 | Rn               | Rm   | 01MD                     | MOV.B | Rm,@(R0,Rn) | MOV.W    | Rm,@(R0,Rn) | MOV.L    | Rm,@(R0,Rn) | MUL.L            | Rm,Rn     |

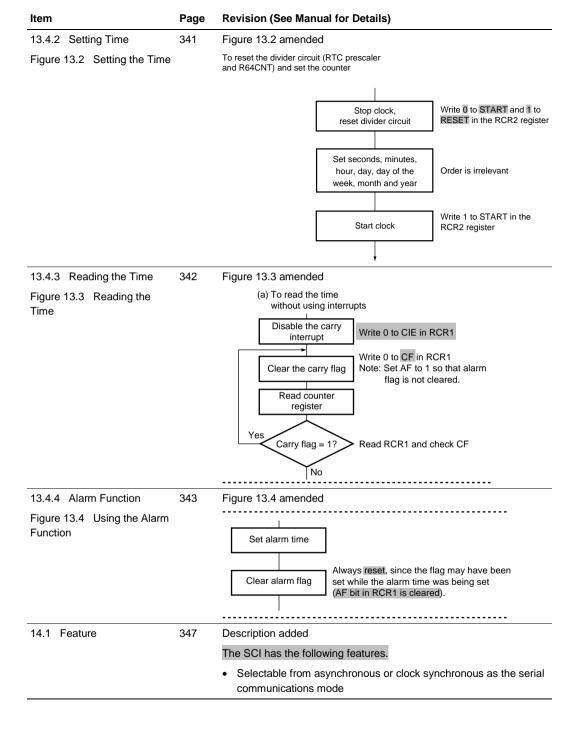

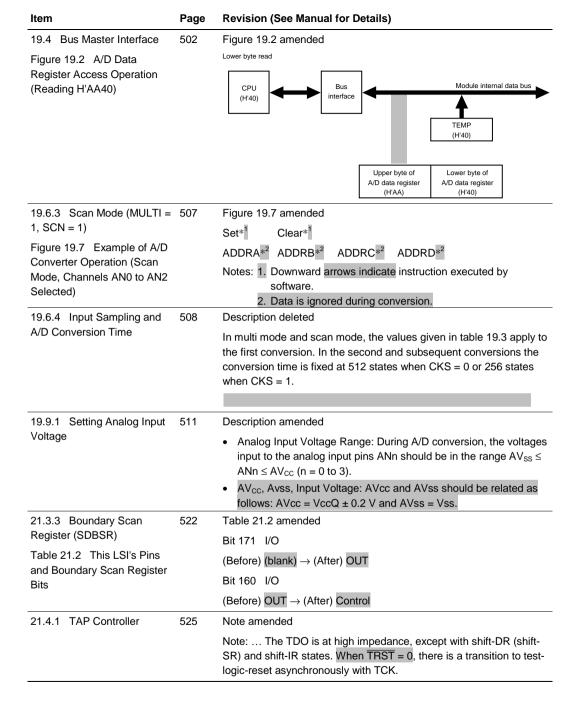

| Item                                                                               | Page                                                                                                                                                                                                                                                                                                                                                                  | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

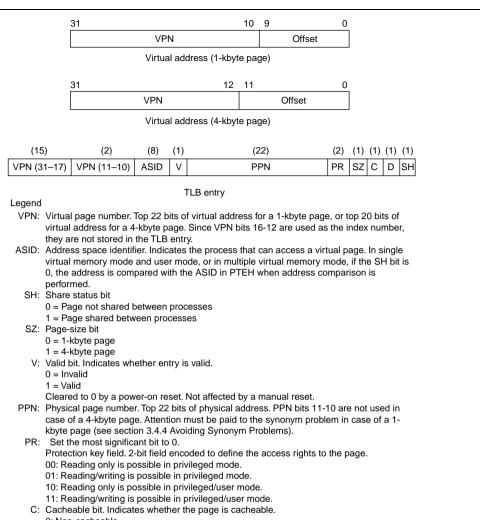

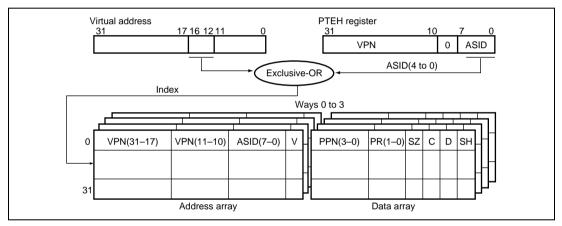

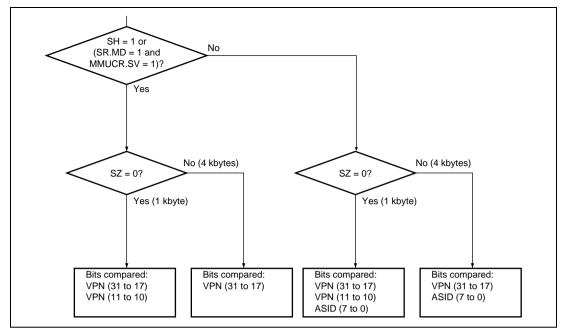

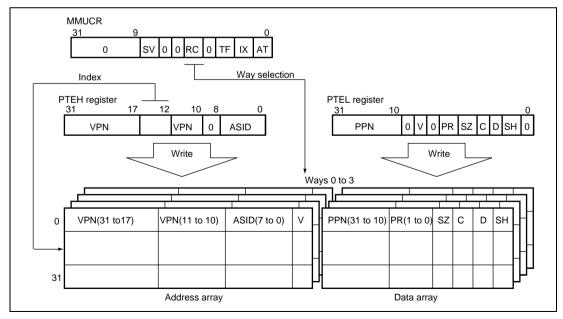

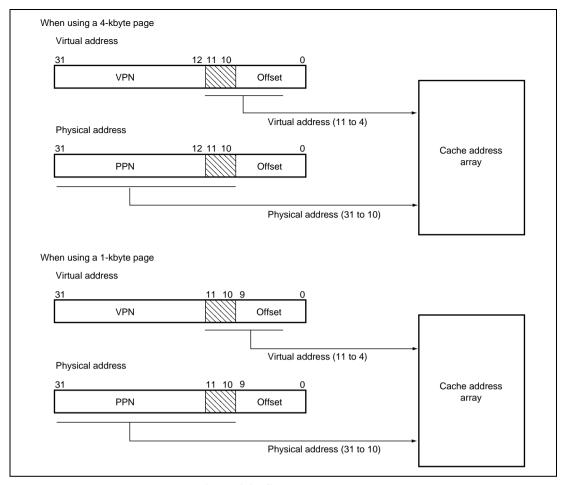

| 3.3.2 TLB Indexing                                                                 | 61                                                                                                                                                                                                                                                                                                                                                                    | Description added                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                                                                                    |                                                                                                                                                                                                                                                                                                                                                                       | The TLB uses a 4-way set associative scheme, so entries must be selected by index. VPN bits 16 to 12 and ASID bits in PTEH 4 to 0 are used as the index number regardless of the page size                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

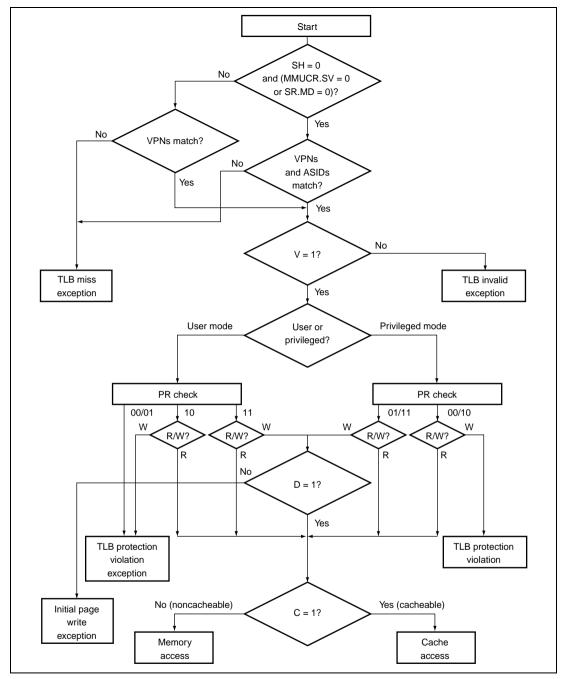

| 3.5.2 TLB Protection                                                               | 71                                                                                                                                                                                                                                                                                                                                                                    | Description added                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Violation Exception                                                                |                                                                                                                                                                                                                                                                                                                                                                       | Software (TLB Protection Violation Handler) Operations: Software resolves the TLB protection violation and issues the RTE (return from exception handler) instruction to terminate the handler and return to the instruction stream. Note that the RTE instruction should be issued after the two instructions following the LDTLB instruction.                                                                                                       |  |  |  |  |  |  |

| 3.6.3 Usage Examples                                                               | 78                                                                                                                                                                                                                                                                                                                                                                    | Description deleted                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                                                                                    |                                                                                                                                                                                                                                                                                                                                                                       | Invalidating Specific Entries: Specific TLB entries can be invalidated by writing 0 to the entry's V bit. R0 specifies the write data and R1 specifies the address.                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 6.4.4 Interrupt Request                                                            | 126                                                                                                                                                                                                                                                                                                                                                                   | Bit 5 R/W amended                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Register 0 (IRR0)                                                                  |                                                                                                                                                                                                                                                                                                                                                                       | (Before) $R \rightarrow (After) R/W$                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

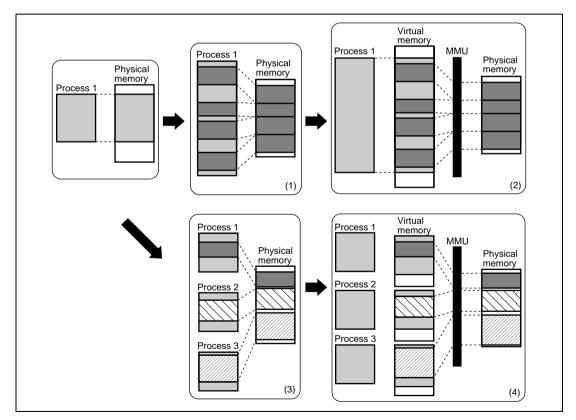

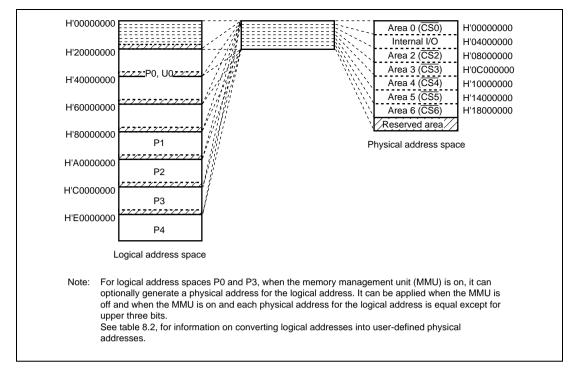

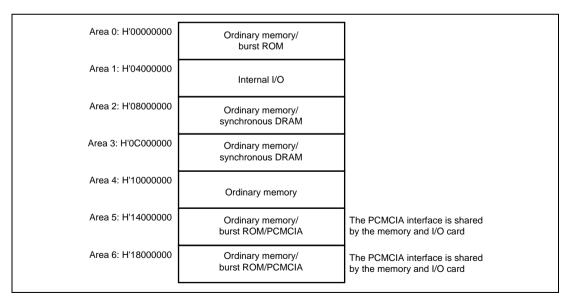

| 8.3 Area Overview                                                                  | 163                                                                                                                                                                                                                                                                                                                                                                   | Note amended                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Figure 8.2 Corresponding to<br>Logical Address Space and<br>Physical Address Space |                                                                                                                                                                                                                                                                                                                                                                       | Note: For logical address spaces P0 and P3, when the memory management unit (MMU) is on, it can optionally generate a physical address for the logical address. It can be applied when the MMU is off and when the MMU is on and each physical address for the logical address is equal except for upper three bits. See table 8.2, Physical Address Space Map, for information on converting logical addresses into user-defined physical addresses. |  |  |  |  |  |  |

| 8.4.6 PCMCIA Control                                                               | 185                                                                                                                                                                                                                                                                                                                                                                   | Bit table of bits 11, 7, 6 amended                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Register (PCR)                                                                     |                                                                                                                                                                                                                                                                                                                                                                       | Bit* Bit Name Initial Value R/W                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                                                                                    |                                                                                                                                                                                                                                                                                                                                                                       | 13, 12 — All 0 R                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                                                                                    |                                                                                                                                                                                                                                                                                                                                                                       | 11 A5TED2 0 R/W                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                                                                                    |                                                                                                                                                                                                                                                                                                                                                                       | 7 A5TED1 0 R/W                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|                                                                                    |                                                                                                                                                                                                                                                                                                                                                                       | 6 A5TED0 0 R/W                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 8.5.2 Description of Areas                                                         | 197                                                                                                                                                                                                                                                                                                                                                                   | Description added                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                                                                                    | The number of bus cycles is selected between 0 and 10 wait cycles using the A0W2 to A0W0 bits of WCR2. In addition, any number of waits can be inserted in each bus cycle by means of the external wait pin (WAIT). When the burst function is used, the bus cycle pitch of the burst cycle is determined within a range of 2 to 10 according to the number of waits. |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

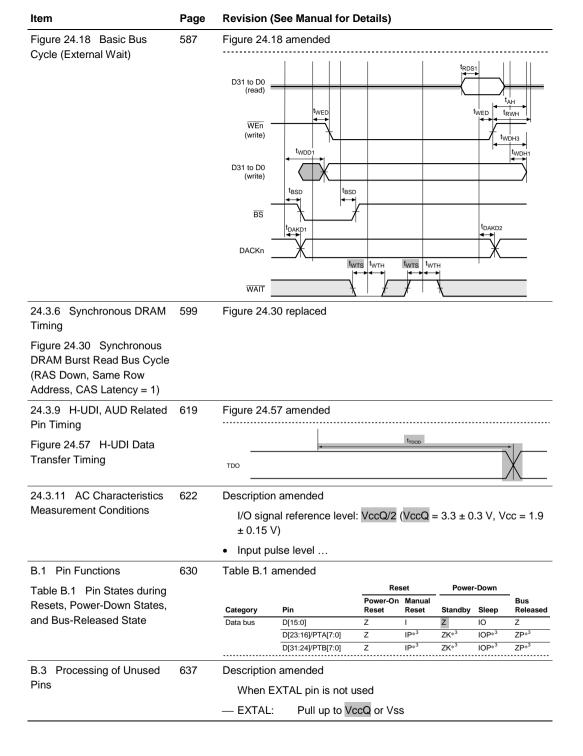

| Item                                                            | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|-----------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

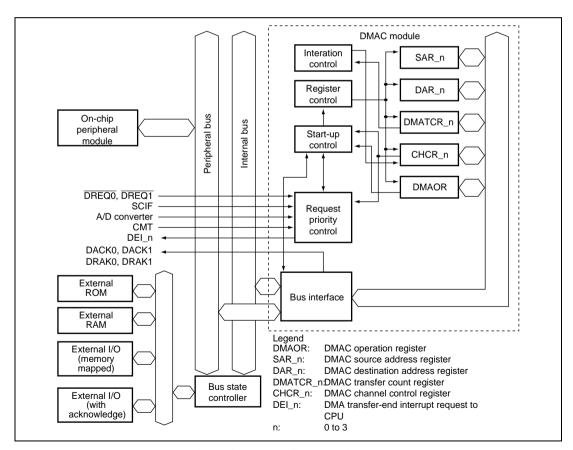

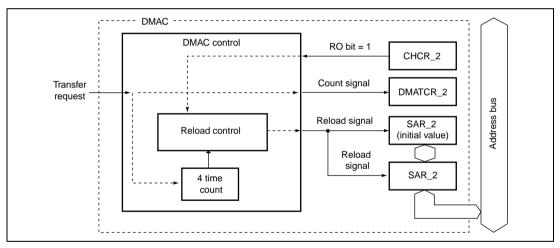

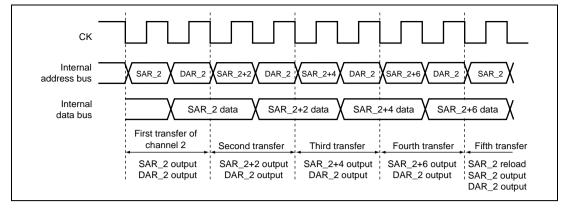

| 9.3 Register Description                                        | 246  | Description added Channel 3  DMA source address register 3 (SAR3)  DMA destination address register 3 (DAR3)  DMA transfer count register 3 (DMATCR3)  DMA channel control register 3 (CHCR3)  Any Channel                                                                                                                                                                                                                              |  |  |  |  |

|                                                                 |      | DMA operation register (DMAOR)                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

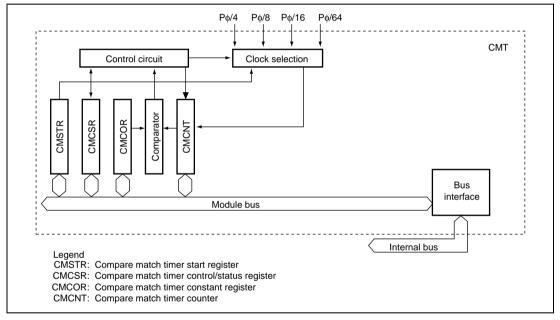

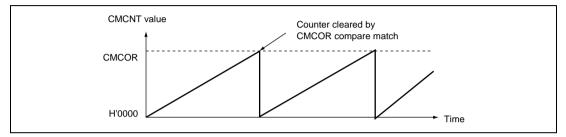

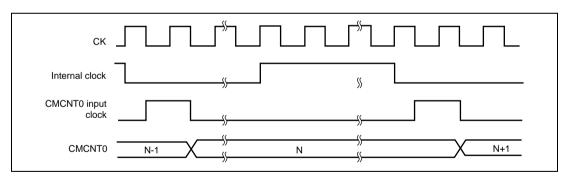

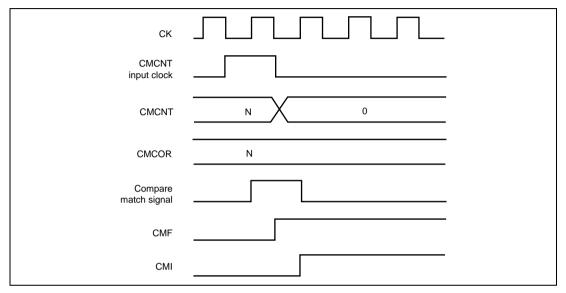

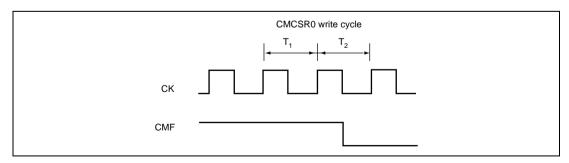

| 9.5.3 Operation Figure 9.27 Counter Operation                   | 285  | Figure 9.27 amended (Before) CMCNT0 value $\rightarrow$ (After) CMCNT value (Before) CMCOR0 $\rightarrow$ (After) CMCOR                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

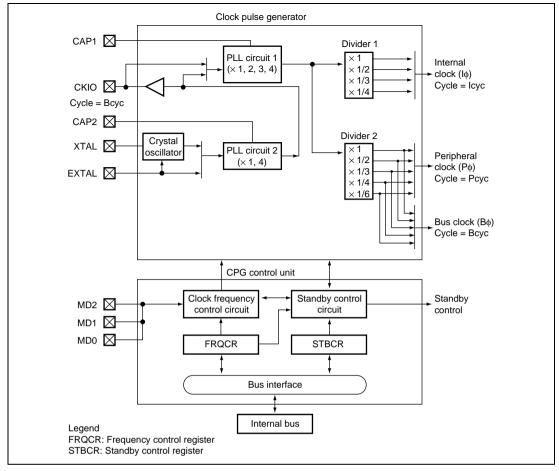

| 10.1 Feature Figure 10.1 Block Diagram of Clock Pulse Generator | 292  | CAP1  CAP1  CIOCK pulse generator  CAP1  PLL circuit 1  (x 1, 2, 3, 4)  Cycle = Bcyc  CAP2  XTAL  Crystal oscillator  CTycle = Bcyc  CAP2  XTAL  Divider 1  X 1/2  X 1/3  X 1/4  Peripheral clock (Pe)  Cycle = Pcyc  Cycle = Bcyc  Cycle = Bcyc                                                                                                                                                                                        |  |  |  |  |

|                                                                 | 293  | <ol> <li>description amended</li> <li>Divider 2: Divider 2 generates a clock at the operating frequency used by the bus clock (Bφ) and peripheral clock (Pφ). The operating frequency of the peripheral clock can be 1, 1/2, 1/3, 1/4, or 1/6 times the output frequency of PLL Circuit 1, as long as it stays at or below the clock frequency of the CKIO pin. The division ratio is set in the frequency control register.</li> </ol> |  |  |  |  |

| Item                                    | Page | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|-----------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 10.3 Clock Operating Modes              | 294  | Description amended                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|                                         |      | Table 10.2 shows the relationship between the mode control pin (MD2 to MD0) combinations and the clock operating modes. Table 10.3 shows the usable frequency ranges in the clock operating modes and frequency ranges of the input clock (crystal oscillation). Operation cannot be guaranteed if settings other than those listed in table 10.3 are used. |  |  |  |  |  |  |  |

|                                         | 297  | Caution 4 amended                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|                                         |      | 4. The frequency of the peripheral clock $(P\phi)$ :                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|                                         |      | <ul> <li>The frequency of the peripheral clock (Pφ) is the product of the<br/>frequency of the CKIO pin, the frequency multiplication ratio of<br/>PLL circuit 1, and the division ratio of divider 2.</li> </ul>                                                                                                                                           |  |  |  |  |  |  |  |

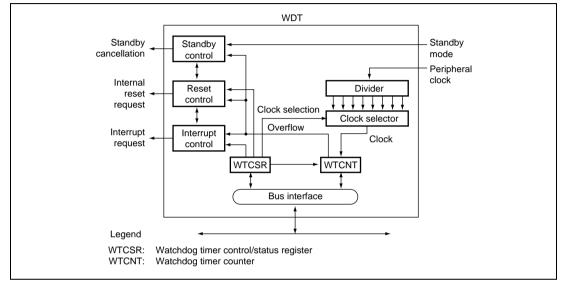

| Section 11 Watchdog Timer               | 303  | Figure 11.1 amended                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| (WDT)                                   |      | WDT                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Figure 11.1 Block Diagram of the WDT    |      | Standby cancellation  Internal reset request  Interrupt request  Interrupt request  Bus interface  Standby mode  Peripheral clock  Clock selector  Clock selector  WTCSR  WTCNT  Bus interface                                                                                                                                                              |  |  |  |  |  |  |  |

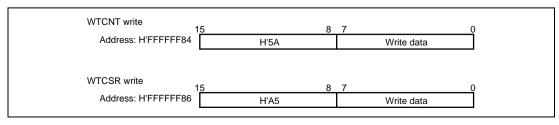

| 11.2.1 Watchdog Timer                   | 304  | Description amended                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Counter (WTCNT)                         |      | $\dots$ The WTCNT is initialized to H'00 only by a power-on reset through the $\overline{\text{RESETP}}$ pin. $\dots$                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| 11.2.2 Watchdog Timer                   | 304  | Description amended                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Control/Status Register<br>(WTCSR)      |      | $\dots$ The WTCSR is initialized to H'00 only by a power-on reset through the $\overline{\text{RESETP}}$ pin. $\dots$                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

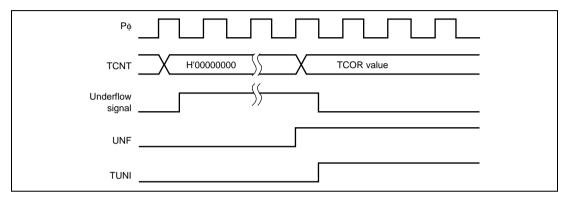

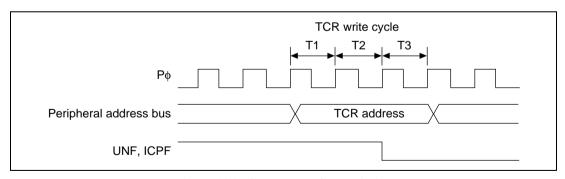

| 12.5.2 Status Flag Clear<br>Timing      | 323  | Figure 12.9 amended  TCR write cycle                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Figure 12.9 Status Flag<br>Clear Timing |      | P\$                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|                                         |      | Peripheral address bus TCR address                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|                                         |      | UNF, ICPF                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| 13.3.9 Second Alarm                     | 333  | Bit 7 R/W amended                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Register (RSECAR)                       |      | (Before) $R \rightarrow (After) RW$                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Item                                                        | Page | Revisi               | on (See    | Manual fo     | r Deta | ails)                                                                                                                                                                                                |  |

|-------------------------------------------------------------|------|----------------------|------------|---------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

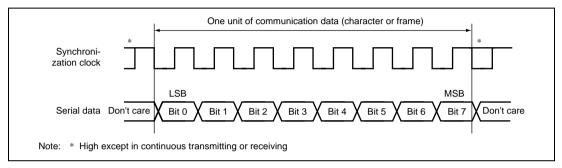

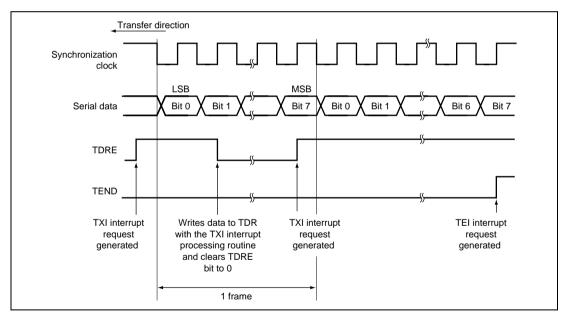

| 14.4.3 Clock Synchronous Operation                          | 389  | Figure 14.17 amended |            |               |        |                                                                                                                                                                                                      |  |

| Figure 14.17 Data Format in Clock Synchronous Communication |      | Serial data          | Don't care | Bit 0 Bit 1   | Bit 2  | Bit 3  Bit 4  Bit 5  Bit 6  Bit 7  Don't care                                                                                                                                                        |  |

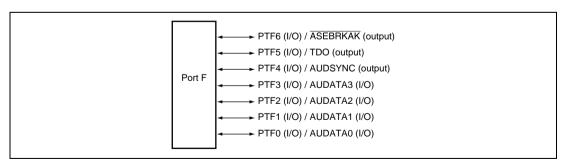

| 17.1.6 Port F Control                                       | 470  | Bit tabl             | e amend    | ed            |        |                                                                                                                                                                                                      |  |

| Register (PFCR)                                             |      | Bit                  | Bit Name   | Initial Value | R/W    | Description                                                                                                                                                                                          |  |

|                                                             |      | 15                   | -          | 1/0           | R      | Reserved  When $\overline{ASEMD0} = 0$ , this bit is always read as 0 and must only be written with 0.  When $\overline{ASEMD0} = 1$ , this bit is always read as 1 and must only be written with 1. |  |

|                                                             |      | 14                   | _          | 0             | R      | Reserved                                                                                                                                                                                             |  |

|                                                             |      |                      |            |               |        | This bit is always read as 0 and must only be written with 0.                                                                                                                                        |  |

|                                                             |      | 13                   | PF6MD1     | 1/0           | R/W    | PF6 Mode                                                                                                                                                                                             |  |

|                                                             |      | 12                   | PF6MD0     | 0             | R/W    | 00: Other function (See table 17.1)                                                                                                                                                                  |  |

|                                                             |      |                      |            |               |        | 01: Port output                                                                                                                                                                                      |  |

|                                                             |      |                      |            |               |        | 10: Port input (Pull-up MOS: on)                                                                                                                                                                     |  |

|                                                             |      | 11                   | DESMO      | 1 10          | DAM    | 11: Port input (Pull-up MOS: off)                                                                                                                                                                    |  |

|                                                             |      |                      | PF5MD1     | 1/0           | R/W    | PF5 Mode                                                                                                                                                                                             |  |

|                                                             |      | 10                   | PF5MD0     | 0             | R/W    | 00: Other function (See table 17.1)                                                                                                                                                                  |  |

|                                                             |      |                      |            |               |        | 01: Port output 10: Port input (Pull-up MOS: on)                                                                                                                                                     |  |

|                                                             |      |                      |            |               |        | 11: Port input (Pull-up MOS: off)                                                                                                                                                                    |  |

|                                                             |      |                      |            |               |        |                                                                                                                                                                                                      |  |

|                                                             | 471  | Bit                  | Bit Name   | Initial Value | R/W    | Description                                                                                                                                                                                          |  |

|                                                             |      | 9                    | PF4MD1     | 1/0           | R/W    | PF4 Mode                                                                                                                                                                                             |  |

|                                                             |      | 8                    | PF4MD0     | 0             | R/W    | 00: Other function (See table 17.1)                                                                                                                                                                  |  |

|                                                             |      |                      |            |               |        | 01: Port output                                                                                                                                                                                      |  |

|                                                             |      |                      |            |               |        | 10: Port input (Pull-up MOS: on) 11: Port input (Pull-up MOS: off)                                                                                                                                   |  |

|                                                             |      | 7                    | PF3MD1     | 1/0           | R/W    | PF3 Mode                                                                                                                                                                                             |  |

|                                                             |      | 6                    | PF3MD0     | 0             | R/W    | 00: Other function (See table 17.1)                                                                                                                                                                  |  |

|                                                             |      | Ü                    | TTOMEO     | O .           | 10,11  | 01: Port output                                                                                                                                                                                      |  |

|                                                             |      |                      |            |               |        | 10: Port input (Pull-up MOS: on)                                                                                                                                                                     |  |

|                                                             |      |                      |            |               |        | 11: Port input (Pull-up MOS: off)                                                                                                                                                                    |  |

|                                                             |      | 5                    | PF2MD1     | 1/0           | R/W    | PF2 Mode                                                                                                                                                                                             |  |

|                                                             |      | 4                    | PF2MD0     | 0             | R/W    | 00: Other function (See table 17.1)                                                                                                                                                                  |  |

|                                                             |      |                      |            |               |        | 01: Port output                                                                                                                                                                                      |  |

|                                                             |      |                      |            |               |        | 10: Port input (Pull-up MOS: on)                                                                                                                                                                     |  |

|                                                             |      |                      |            |               |        | 11: Port input (Pull-up MOS: off)                                                                                                                                                                    |  |

|                                                             |      | 3                    | PF1MD1     | 1/0           | R/W    | PF1 Mode 1                                                                                                                                                                                           |  |

|                                                             |      | 2                    | PF1MD0     | 0             | R/W    | 00: Other function (See table 17.1)                                                                                                                                                                  |  |

|                                                             |      |                      |            |               |        | 01: Port output                                                                                                                                                                                      |  |

|                                                             |      |                      |            |               |        | 10: Port input (Pull-up MOS: on)                                                                                                                                                                     |  |

|                                                             |      |                      |            |               |        | 11: Port input (Pull-up MOS: off)                                                                                                                                                                    |  |

|                                                             |      | 1                    | PF0MD1     | 1/0           | R/W    | PF0 Mode 1                                                                                                                                                                                           |  |

|                                                             |      | 0                    | PF0MD0     | 0             | R/W    | 00: Other function (See table 17.1)                                                                                                                                                                  |  |

|                                                             |      |                      |            |               |        | 01: Port output                                                                                                                                                                                      |  |

|                                                             |      |                      |            |               |        | 10: Port input (Pull-up MOS: on)                                                                                                                                                                     |  |

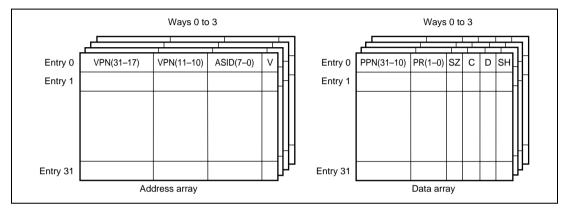

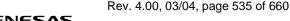

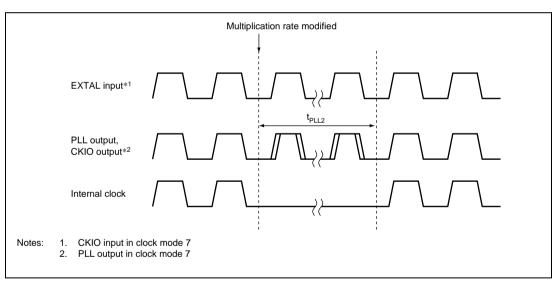

11: Port input (Pull-up MOS: off)