♦ STRUCTURE Silicon Monolithic Integrated Circuit

♦ PRODUCT DDC2<sup>TM</sup> DISPLAY ID ROM

♦ PART NUMBER BU9882-W Series

| PART NUMBER | PACKAGE |

|-------------|---------|

| BU9882-W    | DIP14   |

| BU9882F-W   | SOP14   |

| BU9882FV-W  | SSOP14  |

♦ FEATURES For DDC2<sup>TM</sup>

2kbit (128word × 8bit × 2port) EEPROM Single power supply (2.5V ~ 5.5V) 100,000 erase/write cycles endurance

## ♦ ABSOLUTE MAXIMUM RATING (Ta=25°C)

| Parameter             | Symbol | nbol Rating       |    | Unit |

|-----------------------|--------|-------------------|----|------|

| Supply Voltage        | Vcc    | -0.3~6.5          |    | V    |

| -                     | Pd     | 950 (BU9882-W) *1 |    |      |

| Power Dissipation     |        | 450 (BU9882F-W)   | *2 | mW   |

|                       |        | 350 (BU9882FV-W)  | *3 | 1    |

| Storage Temperature   | Tstg   | -65 <b>~</b> 125  |    | °C   |

| Operating Temperature | Topr   | -40 <b>~</b> 85   |    | °C   |

| Terminal Voltage      | _      | -0.3∼Vcc+1.0 *4   |    | V    |

<sup>\*</sup> Degradation is done at 9.5mW/°C(\*1), 4.5mW/°C(\*2), 3.5mW/°C(\*3) for operation above 25°C

## ♦ RECOMMENDED OPERATING CONDITION

| Parameter      | Symbol | Rating    | Unit |

|----------------|--------|-----------|------|

| Supply Voltage | Vcc    | 2.5~5.5   | ٧    |

| Input Voltage  | VIN    | 0~Vcc+1.0 | ٧    |

Status of this document

The Japanese version of this document is the fomal specification.

A customer may use this translation version only for a reference to help reading the formal version.

If there are any differences in translation version of this document, formal version takes priority.

<sup>\*4</sup> Max 6.8V

♦ MEMORY CELL CHARACTERISTICS(Ta=25°C,Vcc=2.5~5.5V)

| Parameter         |    | Min.    | Тур. | Max. | Unit  |

|-------------------|----|---------|------|------|-------|

| Write/Erase Cycle | *1 | 100,000 | -    | -    | Cycle |

| Data Retention    | *1 | 10      | -    | -    | Year  |

OInitial Data: Memory array FFh \*1 Not 100% TESTED

### ♦ DC OPERATING CHARACTERISTICS

(Unless otherwise specified Ta=-40~85°C, Vcc=2.5~5.5V)

| (0111000 04110            | Offices Outlet Wise specifica Tu |      |        | _      | 10 00 0, 100 2.0 0.017 |                                   |

|---------------------------|----------------------------------|------|--------|--------|------------------------|-----------------------------------|

| Parameter                 | Symbol                           | Spe  | cifica | tion   | Unit                   |                                   |

| , sramoto                 |                                  | Min. | Тур.   | Max.   | •                      |                                   |

| "H" Input Voltage1        | VIHI                             | 2    | -      | 1      | ٧                      |                                   |

| "L" Input Voltage I       | VIL1                             | -    | -      | 0.8    | ٧                      | Vcc≧4.0V                          |

| "L" Input Voltage2        | VIL2                             | -    | -      | 0.2Vcc | ٧                      | Vcc <4.0V                         |

| "L" Output Voitage        | VOL                              | -    | -      | 0.4    | >                      | SDA_PC0/1, IOL=3.0mA *1           |

| Input Leakage             | ILIT                             | -1   |        | 1      | μА                     | SCL_PC0/1, DDCENA, BANKSEL        |

| Current1                  | ILII                             | -'   |        | . '    | μΑ                     | VIN=0V~Vcc+1.0                    |

| Input Leakage<br>Current2 | IL12                             | -1   | -      | 50     | μА                     | WPB                               |

| Output Leakage            | ilo                              | -1   |        | 1      | μА                     | SDA_PC0/1.SCL/SDA_MON(DDCENA=GND) |

| Current                   | ILO                              | -1   | _      | '      | μА                     | VOUT= <b>0</b> V∼Vcc+1.0          |

| Operating Current         | icc                              |      | 1.5    | 3      | mA                     | fSCL=400kHz, Vcc=5.5V             |

| Operating Current         | 100                              | _    | 1.3    | 3      | mA                     | tWR=10ms                          |

|                           |                                  |      |        |        |                        | SCL/SDA_PC0/1=Vcc                 |

| Sharatha Carran           | ISB                              |      | 0.1    | 5      |                        | SCL/SDA_MON=High=Z                |

| Standby Current           | 198                              | _    | "."    |        | μА                     | DDCENA=WPB=BANKSEL=GND            |

|                           |                                  |      |        |        |                        | DUALPCB=Vcc                       |

- OThis product is not designed for protection against radioactive rays.

- \*1 IOL at monitor mode (DDCENA=HIGH) is sum of current flowed from Pull up resistor on SDA\_MON Side, and Pull up resistance on SDA\_PC0/PC1.

# ♦ AC OPERATING CHARACTERISTICS

(Unless otherwise specified Ta=-40~85°C)

| Parameter                       | Symbol  | Fast=mode<br>2.5≦Voc≦5.5V |      |      | Standard-mode<br>2.5≦Vcc≨5.5V |      |      | Unit |

|---------------------------------|---------|---------------------------|------|------|-------------------------------|------|------|------|

|                                 |         | Min.                      | Тур. | Max. | Min.                          | Тур. | Max. | ]    |

| Clock Frequency                 | fSCL    |                           | -    | 400  | -                             | -    | 100  | kHz  |

| Data Clock High Period          | tHIGH   | 0.6                       | -    | -    | 40                            | -    | _    | μs   |

| Data Clock Low Period           | tLOW    | 1.3                       | _    | -    | 47                            | -    | -    | μs   |

| SDA and SCL Rise Time           | tR      | -                         | -    | 0.3  | -                             | -    | 1.0  | μs   |

| SDA and SCL Fall Time           | tF      | -                         | -    | 0.3  | -                             | -    | 0.3  | μs   |

| Start Condition Hold Time       | tHD:STA | 0.6                       | -    | -    | 4.0                           | -    | -    | με   |

| Start Condition Setup Time      | tSU:STA | 06                        | -    | -    | 4.7                           | -    | -    | μs   |

| Input Data Hold Time            | tHD:DAT | 0                         | -    | -    | 0                             | -    | -    | ns   |

| Input Data Setup Time           | tSU:DAT | 100                       | -    | -    | 250                           | -    | -    | r:s  |

| Output Data Delay Time          | t₽D     | -                         | -    | 0.9  | -                             | -    | 3.5  | μs   |

| Stop Condition Setup Time       | tSU:STO | 0.6                       | -    | -    | 4.0                           | -    | -    | μs   |

| Bus Free Time                   | tBUF    | 1.3                       | -    | -    | 4.7                           | -    | -    | μѕ   |

| Write Cycle Time                | tWR     | -                         | -    | 10   | -                             | -    | 10   | ms   |

| Noise Spike Width (SDA and SCL) | tl      | -                         | -    | 01   | -                             | -    | 0.1  | μs   |

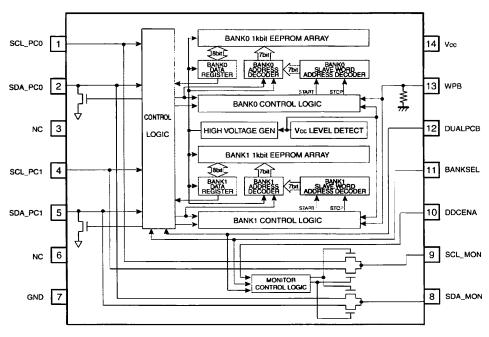

## ♦ BLOCK DIAGRAM

◇ PIN No./PIN NAME

| PIN No. | PIN NAME |

|---------|----------|

| 1       | SCL_PC0  |

| 2       | SDA_PC0  |

| 3       | NC       |

| 4       | SCL_PC1  |

| 5       | SDA_PC1  |

| 6       | NC       |

| 7       | GND      |

| 8       | SDA_MON  |

| 9       | SCL_MON  |

| 10      | DDCENA   |

| 11      | BANKSEL  |

| 12      | DUALPCB  |

| 13      | WPB      |

| 14      | Vcc      |

|         |          |

Fig.1 BLOCK DIAGRAM

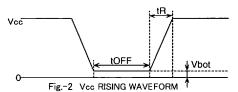

#### **♦NOTES FOR POWER SUPPLY**

Vcc rises through the low voltage region in which internal circuit of IC and the controller are unstable, so that device may not work properly due to an incomplete reset of internal circuit. To prevent this, the device has the feature of P.O.R. and LVCC. In the case of power up, keep the following conditions to ensure functions of P.O.R. and LVCC.

- 1. It is necessary for SDA\_PC0 and SDA\_PC1 to be "HIGH", for SCL\_PC0 and SCL\_PC1 to be either "HIGH" or "LOW".

- 2. Follow the recommended conditions of tR, tOFF, Vbot for the function of P.O.R. during power up.

| ♦ Recommended conditions of tR, tOFF, Vbot |            |            |  |  |  |

|--------------------------------------------|------------|------------|--|--|--|

| tR                                         | tOFF       | Vbot       |  |  |  |

| Below 10ms                                 | Above 10ms | Below 0.2V |  |  |  |

| Below 100ms                                | Above 10ms | Below 0.1V |  |  |  |

- 3. Prevent SDA\_PC0, SDA\_PC1, SCL\_PC0 and SCL\_PC1 from being "High-Z". In case that condition 1. and/or 2. cannot be met, take following actions.

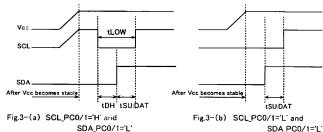

- A) Unable to keep condition 1. (SDA\_PC0 is "LOW" during power up, for example.)

- → Control SDA\_PC0 and SCL\_PC0 to be "HIGH" as figure below. It applies to SDA\_PC1 and SCL\_PC1 also.

- B) Unable to keep condition 2.

- → After power become stable, execute software reset.

- C) Unable to keep both conditions 1 and 2.

- → Follow the instruction A first, then the instruction B.

SDA PC0/1='L'

## **CAUTIONS ON USE**

(1) Absolute maximum ratings

If the absolute maximum ratings such as impressed voltage and operating temperature range and so forth are exceeded, LSI may be destructed. Do not impress voltage and temperature exceeding the absolute maximum ratings. In the case of fear exceeding the absolute maximum ratings, take physical safety countermeasures such as fuses, and see to it that conditions exceeding the absolute maximum ratings should not be impressed to LSI.

- (2) GND electric potential

- Set the voltage of GND terminal lowest at any action condition. Make sure that each terminal voltages is lower than that of GND terminal.

- (3) Heat design

- In consideration of permissible dissipation in actual use condition, carry out heat design with sufficient margin.

- (4) Terminal to terminal shortcircuit and wrong packaging

- When to package LSI onto a board, pay sufficient attention to LSI direction and displacement. Wrong packaging may destruct LSI. And in the case of shortcircuit between LSI terminals and terminals and power source, terminal and GND owing to foreign matter, LSI may be destructed.

- (5) Strong electromagnetic field

- Use in a strong electromagnetic field may cause malfunction, therefore, evaluated design sufficiently.

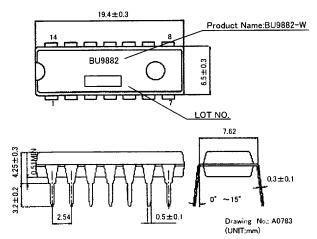

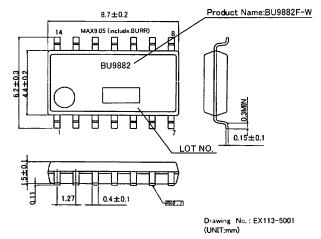

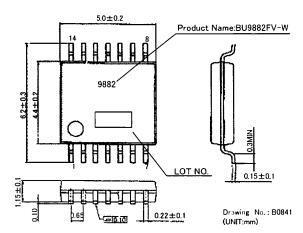

### ♦ PHYSICAL DIMENSION

Fig.4-(a) PHYSICAL DIMENSION DIP14 (BU9882-W)

Fig.4-(b) PHYSICAL DIMENSION SOP14 (BU9882F-W)

Fig.4-(c) PHYSICAL DIMENSION SSOP14(BU9882FV-W)

### Notes

- No technical content pages of this document may be reproduced in any form or transmitted by any

means without prior permission of ROHM CO.,LTD.

- The contents described herein are subject to change without notice. The specifications for the

product described in this document are for reference only. Upon actual use, therefore, please request

that specifications to be separately delivered.

- Application circuit diagrams and circuit constants contained herein are shown as examples of standard

use and operation. Please pay careful attention to the peripheral conditions when designing circuits

and deciding upon circuit constants in the set.

- Any data, including, but not limited to application circuit diagrams information, described herein are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO.,LTD. disclaims any warranty that any use of such devices shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes no liability of whatsoever nature in the event of any such infringement, or arising from or connected with or related to the use of such devices.

- Upon the sale of any such devices, other than for buyer's right to use such devices itself, resell or

otherwise dispose of the same, no express or implied right or license to practice or commercially

exploit any intellectual property rights or other proprietary rights owned or controlled by

- ROHM CO., LTD. is granted to any such buyer.

- Products listed in this document are no antiradiation design.

The products listed in this document are designed to be used with ordinary electronic equipment or devices (such as audio visual equipment, office-automation equipment, communications devices, electrical appliances and electronic toys).

Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of with would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

### About Export Control Order in Japan

Products described herein are the objects of controlled goods in Annex 1 (Item 16) of Export Trade Control Order in Japan.

In case of export from Japan, please confirm if it applies to "objective" criteria or an "informed" (by MITI clause) on the basis of "catch all controls for Non-Proliferation of Weapons of Mass Destruction.