# M5913

# COMBINED SINGLE CHIP PCM CODEC AND FILTER

- SYNCHRONOUS CLOCKS ONLY

- AT&T D3/D4 AND CCITT COMPATIBLE

- TWO TIMING MODES:

- FIXED DATA RATE MODE 1.536MHz, 1.544MHz, 2.048MHz VARIABLE DATA MODE: 64KHz - 4.096MHz

- PIN SELECTABLE μ-LAW OR A-LAW OP-ERATION

- NO EXTERNAL COMPONENTS FOR SAM-PLE-AND-HOLD AND AUTO ZERO FUNC-TIONS

- LOW POWER DISSIPATION:

0.5mW POWER DOWN

70mW OPERATING

- EXCELLENT POWER SUPPLY REJECTION

#### DESCRIPTION

The M5913 is fully integrated PCM (pulse code modulation) codecs and transmit/receive filter using CMOS silicon gate technology.

The primary applications for the M5913 are telephone systems :

- Switching - M5913-Digital PBX's and Central

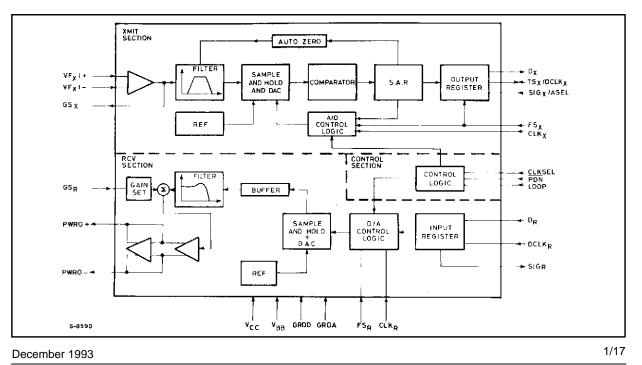

### **BLOCK DIAGRAM**

Office Switching Systems

- Concentration - M5913 Subscriber Carrier and Concentrators.

The wide dynamic range (78dB) and the minimal conversion time make it ideal products for other applications such as:

- Voice Store and Forward

- Secure Communications Systems

- Digital Echo Cancellers

- Satellite Earth Stations.

This is advanced information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol             | Parameter                                                        | Value                                                                                                                                             | Unit |

|--------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Vcc                | With Respect GRDD, GRDA = 0V                                     | - 0.6 to 7                                                                                                                                        | V    |

| V <sub>BB</sub>    | With Respect GRDD, GRDA = 0V                                     | - 0.6 to - 7                                                                                                                                      | V    |

| GRDD, GRDA         | In Such Case : $0 \le V_{CC} \le + 7V$ , $-7V \le V_{BB} \le 0V$ | ± 0.3                                                                                                                                             | V    |

| V <sub>I/O</sub>   | Analog Inputs, Analog Outputs and Digital Inputs                 | $\label{eq:VBB} \begin{array}{l} \text{VBB} - 0.3 \leq \text{V}_{\text{IN}} \text{V}_{\text{OUT}} \leq \text{V}_{\text{CC}} + \\ 0.3 \end{array}$ | V    |

| V <sub>O DIG</sub> | Digital Outputs                                                  | $GRDD - 0.3 \le V_{OUT} \le V_{CC} + 0.3$                                                                                                         | V    |

| P <sub>tot</sub>   | Total Power Dissipation                                          | 1                                                                                                                                                 | W    |

| T <sub>stg</sub>   | Storage Temperature Range                                        | -65 to 150                                                                                                                                        | °C   |

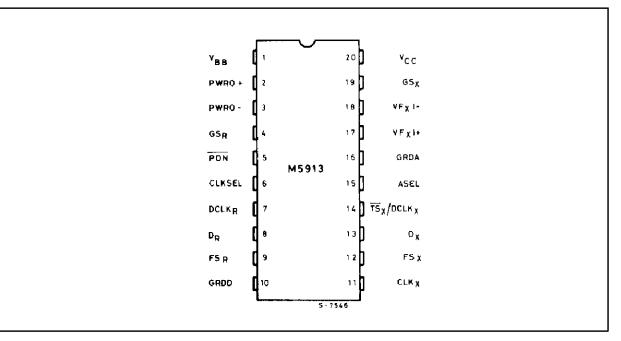

### **PIN CONNECTION** (Top view)

#### **PIN NAMES**

| Symbol            | Parameter                              | Symbol                                 | Parameter                            |

|-------------------|----------------------------------------|----------------------------------------|--------------------------------------|

| V <sub>BB</sub>   | Power (-5V)                            | GS <sub>X</sub>                        | Gain Control                         |

| PWRO+, PWRO-      | Power Amplifier Outputs                | VF <sub>X</sub> I-, VF <sub>X</sub> I+ | Analog Inputs                        |

| GS <sub>R</sub>   | Gain Setting Input for receive Channel | GRDA                                   | Analog Ground                        |

| PDN               | Power Pown Select                      | NC                                     | No Connected                         |

| CLKSEL            | Master Clock Select                    | SIGx                                   | Transmit Digital Signaling Input     |

| LOOP              | Analog Loop Back                       | ASEL                                   | μ or A-law Select                    |

| SIG <sub>R</sub>  | Signaling Bit Output                   | TS <sub>X</sub>                        | Digital Output - Timeslot Strobe     |

| DCLK <sub>R</sub> | Receive Data Rate Clock                | DCLK <sub>X</sub>                      | Transmit Data Rate Clock             |

| D <sub>R</sub>    | Receive Channel Input                  | Dx                                     | Transmit (Digital) Output            |

| FS <sub>R</sub>   | Receive Frame Synchronization Clock    | FSx                                    | Transmit Frame Synchronization Clock |

| GRDD              | Digital Ground                         | CLKx                                   | Transmit Master Clock                |

| Vcc               | Power (+5V)                            | CLK <sub>R</sub>                       | Receive Master Clock                 |

## **PIN DESCRIPTION**

| Symbol                             | Function                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>BB</sub>                    | Most Negative Supply. Input voltage is -5 volts ±5%.                                                                                                                                                                                                                                                                                                                                                                                 |

| PWRO+                              | Non-inverting Output of Power Amplifier. Can drive transformer hybrids or high impedance loads directly in either a differential or single ended configuration.                                                                                                                                                                                                                                                                      |

| PWRO -                             | Inverting Output of Power Amplifier. Functionally identical and complementary to PWRO+.                                                                                                                                                                                                                                                                                                                                              |

| GS <sub>R</sub>                    | Input to the gain Setting Network on the Output Power Amplifier, Transmission level can be adjusted over a 12dB range depending on the voltage at $GS_R$ .                                                                                                                                                                                                                                                                           |

| PDN                                | Power Down Select. When PDN is TTL high, the device is active. When low, the device is powered down.                                                                                                                                                                                                                                                                                                                                 |

| CLKSEL                             |                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LOOP                               | Analog Loopback. When this pin is TTL high, the receive output (PWRO+) is internally connected to $VF_XI+$ , $GS_R$ is internally connected to PWRO-, and $VF_XI-$ is internally connected to $GS_X$ .<br>A 0dBm0 digital signal input at $D_R$ is returned as a +3dBm0 digital signal output at $D_X$ .                                                                                                                             |

| SIG <sub>R</sub>                   | Signalling Bit Output, Receive Channel. In fixed data rate mode. SIG <sub>R</sub> outputs the logical state of the eighth bit of the PCM word in the most recent signaling frame.                                                                                                                                                                                                                                                    |

| DCLK <sub>R</sub>                  | Selects the fixed or variable data rate mode. When DCLKR is connected to $V_{BB}$ , the fixed data rate mode is selected.<br>When DCLK <sub>R</sub> is not connected to $V_{BB}$ , the device operates in the variable data rate mode. In this mode DCLK <sub>R</sub> becomes the receive data clock wich operates at TTL levels from 64kB to 4.096MB data rates                                                                     |

| D <sub>R</sub>                     | Receive PCM Input. PCM data is clocked in on this lead on eight consecutive negative transitions of the receive data clock: CLKR in the fixed data rate mode and DCLK <sub>R</sub> in variable data rate mode.                                                                                                                                                                                                                       |

| FS <sub>R</sub>                    | 8kHz frame synchronization clock input/timeslot enable, receive channel. A multifunction input which in fixed data rate mode distinguishes between signaling and non-signaling frames by means of a double or single wide pulse respectively. In variable data rate mode this signal must remain high for the entire length of the timeslot. The receive channel enters the standby state whenever FSR is TTL low for 30 miliseconds |

| GRDD                               | Digital Ground for all Internal Logic Circuits. Not internally tied to GRDA.                                                                                                                                                                                                                                                                                                                                                         |

| CLK <sub>R</sub>                   | Receive master and data clock for the fixed data rate mode; receive master clock only in variable data rate mode.                                                                                                                                                                                                                                                                                                                    |

| CLK <sub>X</sub>                   | Transmit master and data clock for the fixed data rate mode; transmit master clock only in variable data rate mode.                                                                                                                                                                                                                                                                                                                  |

| FS <sub>X</sub>                    | 8kHz frame synchronization clock input/timeslot enable, transmit channel. Operates independently but in an analogous manner to FSR. The transmit channel enters the standby state whenever $FS_X$ is TTL low for 30 milliseconds.                                                                                                                                                                                                    |

| D <sub>X</sub>                     | Transmit PCM Output. PCM data is clocked out on this lead on eight consecutive positive transitions of the transmit data clock : CLK in fixed data rate mode and DCLK <sub>X</sub> in variable data rate mode.                                                                                                                                                                                                                       |

| TS <sub>X</sub> /DCLK <sub>X</sub> | Transmit channel timeslot strobe (output) or data clock (input) for the transmit channel. In fixed data rate mode, this pin becomes the transmit data clock which operates at TTL levels from 64kB to 4.096MB data rates.                                                                                                                                                                                                            |

| SIGx/ASEL                          | A dual purpose selects $\mu$ -law and pin. When connected to V <sub>BB</sub> . A law operation is selected. When i is not connected to V <sub>BB</sub> pin is a TTL level input for signaling operation. This input is transmitted as the eighth bit of the PCM word during signaling frames on the D <sub>X</sub> lead.                                                                                                             |

| NC                                 | Not Connected.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GRDA                               | Analog ground return for all internal voice circuits. Not internally connected to GRDD.                                                                                                                                                                                                                                                                                                                                              |

| VF <sub>X</sub> I+                 | Non inverting analog input to uncommitted transmit operational amplifier.                                                                                                                                                                                                                                                                                                                                                            |

| VF <sub>X</sub> I-                 | Inverting analog input to uncommitted transmit operational amplifier.                                                                                                                                                                                                                                                                                                                                                                |

| GS <sub>X</sub>                    | Output terminal of on-chip uncommitted op amp. Internally, this is the voice signal input to the transmit filter.                                                                                                                                                                                                                                                                                                                    |

| Vcc                                | Most positive supply ; input voltage is + 5 volts ±5%                                                                                                                                                                                                                                                                                                                                                                                |

#### FUNCTIONAL DESCRIPTION

The M5913 provides the analog-to-digital and the digital-to-analog conversion and the transmit and receive filtering necessary to interface a full duplex (4 wires) voice telephone circuit with the PCM highway of a time division multiplexed (TDM) system. It is intended to be used at the analog termination of a PCM line.

The following major functions are provided :

- Bandpass filtering of the analog signals prior to encoding and after decoding

- Encoding and decoding of voice and call progress information

- Encoding and decoding of the signaling and supervision information

#### **GENERAL OPERATION**

#### **System Reliability Features**

The combo-chip can be powered up by pulsing  $FS_X$  and/or  $FS_R$  while a TTL high voltage is applied to  $\overline{PDN}$ , provided that all clocks and supplies are connected. The M5913 has internal resets on power up (or when  $V_{BB}$  or  $V_{CC}$  are re-applied) in order to ensure validity of the digital outputs and thereby maintain integrity of the PCM highway.

<u>On</u> the transmit channel, digital outputs  $D_X$  and  $\overline{TS}_X$  are held in a high impedance state for approximately four frames (500µs) after power up or application of V<sub>BB</sub> or V<sub>CC</sub>. After this delay,  $D_X$  and  $\overline{TS}_X$  will be functional and will occur in the proper timeslot. The analog circuits on the transmit side require approximately 40 milliseconds to reach their equilibrium value due to the autozero circuit setting time. Thus, valid digital information, such as for on/off hook detection, is available almost immediately, while analog information is available after some delay.

On the receive channel, the digital output SIG<sub>R</sub> is also held low for a maximum of four frames after power up or application of  $V_{BB}$  or  $V_{CC}$ , SIG<sub>R</sub> will remain low thereafter until it is updated by a signaling frame.

To further enhance system reliability,  $\overline{TS}_X$  and  $\overline{Dx}$  will be placed in a high impedance state approximately 20µs after an interruption of CLK<sub>X</sub>. Simi-

larly SIG<sub>R</sub> will be held low approximately  $20\mu$ s after an interruption of CLK<sub>R</sub>. These interruptions could possibly occur with some kind of fault condition.

#### **Power Down And Standby Modes**

To minimize power consumption, two power down modes are provided in which most M5913 functions are disabled. Only the power down, clock, and frame sync buffers, which are required to power up the device, are enabled in these modes. As shown in table 1, the digital outputs on the appropriate channels are placed in a high impedance state until the device returns to the active mode.

The Power Down mode utilizes an external control signal to the PDN pin. In this mode, power consumption is reduced to an average of 0.5mW. The device is active when the signal is high and inactive when it is low. In the absence of any signal, the PDN pin floats to TTL high allowing the device to remain active continuously.

The Standby mode leaves the user an option of powering either channel down separately or powering the entire down by selectively removing  $FS_X$  and/or  $FS_R$ . With both channels in the standby state, power consumption is reduced to an average of 1mW. If transmit only operation is desired,  $FS_X$  should be applied to the device while  $FS_R$  is held low. Similarly, if receive only operation is desired, low.

#### **Fixed Data Rate Mode**

Fixed data rate timing, is selected by connecting DCLK<sub>R</sub> to V<sub>BB</sub>. It employs master clock CLK<sub>X</sub>, and CLK<sub>R</sub>, frame synchronization clocks FS<sub>X</sub> and FS<sub>R</sub>, and output TS  $_X$ .

$CLK_X$ , and  $CLK_R$ , serve both as the master clock to operate the codec and filter sections and bit clocks to clock the data in and out from the PCM highway. FS<sub>X</sub> and FS<sub>R</sub> are 8kHz inputs which set the sampling frequency and distinguish between signaling and non-signaling frames by thir pulse width. A frame synchronization pulse which is one master clock wide designates a non-signaling frame, while a double wide sync pulse enables

| Device Status                | Power Down Methods            | Digital Outputs Status                                                                                                                                                         |

|------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Down Mode              | PDN = TTL low                 | $\overline{\text{TS}}_X$ and D <sub>X</sub> are placed in a high impedance state and SIG <sub>R</sub> is placed in a TTL low state within 10µs.                                |

| Stand-by Mode                | $FS_X$ and $FS_R$ are TTL low | $\overline{TS}_X$ and $D_X$ are placed in a high impedance state and SIG <sub>R</sub> is placed in a TTL low state 30ms after FS <sub>X</sub> and FS <sub>R</sub> are removed. |

| Only transmit is on stand-by | FS <sub>X</sub> is TTL low    | $\overline{\text{TS}}_X$ and $D_X$ are placed in a high impedance state within 30ms.                                                                                           |

| Only receive is on stand-by  | FS <sub>R</sub> is TTL low    | $SIG_R$ is placed in a TTL low state within 30ms.                                                                                                                              |

#### Table 1: Power Down Methods

the signaling function.  $TS_X$  is a timeslot strobe/buffer enable output which gates the PCM word onto the PCM highway when an external buffer is used to drive the line.

Data is transmitted on the highway at  $D_X$  on the first eight positive transitions of  $CLK_X$  following the rising edge of FS<sub>X</sub>. Similarly, on the receive side, data is received on the first eight falling edges of  $CLK_R$ . The frequency of  $CLK_X$  and  $CLK_R$  is selected by the CLKSEL pin to be either 1.536, 1.544 or 2.048MHz. No other frequency of operation is allowed in the fixed data rate mode.

#### Variable Data Rate Mode

Variable data rate timing is selected by connecting DCLK<sub>R</sub> to the bit clock for the receive PCM highway rather than to V<sub>BB</sub>. It employes master clocks CLK<sub>X</sub> and CLK<sub>R</sub>, bit clocks DCLK<sub>R</sub> and DCLK<sub>X</sub> and frame synchronization clocks FS<sub>R</sub> and FS<sub>X</sub>.

Variable data rate timing allows for a flexible data frequency. It provides the ability to vary the frequency of the bit clocks, from 64kHz to 4096MHz. Master clocks inputs are still restricted to 1.536, 1.544, or 2.048MHz.

In this mode, DCLK<sub>R</sub> and DCLK<sub>X</sub> become the data clocks for the receive and transmit PCM highways. While FS<sub>X</sub> is high, PCM data from D<sub>X</sub> is transmitted onto the highway on the next eight consecutive positive transitions of DCLK<sub>X</sub>. Similarly, while FS<sub>R</sub> is high, each PCM bit from the highway is received by D<sub>R</sub> on the next eight consecutive negative transitions of DCLK<sub>R</sub>.

On the transmit side, the PCM word will be repeated in all remaining timeslots in the  $125\mu$ s frame as long as DCLK<sub>X</sub> is pulsed and FS<sub>X</sub> is held high. This feature allows the PCM word to be transmitted to the PCM highway more than once per frame, if desired, and is only available in the variable data rate mode. Conversely, signaling is only allowed in the fixed data rate mode since the variable mode provides no means with which to specify a signaling frame.

#### **Precision Voltage References**

No external components are required with the combochip to provide the voltage reference function. Voltage references are generated on-chip and are calibrated during the manufacturing process. The technique use the bandgap principle to derive a temperature and bias stable reference voltage. These references determine the gain and dynamic range characteristics of the device.

Separate references are supplied to the transmit and receive sections. Transmit and receive section are trimmed independently in the filter stages to a final precision value. With this method the combochip can achieve manufacturing tolerances of typically  $\pm$  0.04dB in absolute gain for each half channel, providing the user a significant margin for error in other board components.

#### **Conversion Laws**

The M5913 is designed to operate in both  $\mu$ -law and A-law systems. The user can select either conversion law according to the voltage present on the SIG<sub>X</sub>/ASEL pin . In each case the coder and decoder process a companded 8-bit PCM word following CCITT recommandation G.711 for  $\mu$ -law and A-law conversion. If A-law operation is desired, SIG<sub>X</sub> should be tied to V<sub>BB</sub>. Thus, signaling is not allowed during A-law operation. If  $\mu$  = 255-law operation is selected, then SIG<sub>X</sub> is a TTL level input which modifies the LSB on the PCM output in signaling frames

### TRANSMIT OPERATION

#### **Transmit Filter**

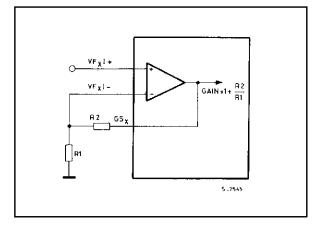

The input section provides gain adjustment in the passband by means of an on-chip uncommitted operational amplifier. This operational amplifier has a common mode range of 2.17V, a maximum DC offset of 25mV, a minimum voltage gain of 5000, and a unity gain bandwidth of typically 1MHz. Gain of up to 20dB can be set without degrading the performance of the filter. The load impedance to ground (GRDA) at the amplifier output (GSx) must be greater than 10k $\Omega$  in parallel high less than 50pF. The input signal on lead VFxI+ can be either AC or DC coupled. The input op amp can also be used in the inverting mode or differential amplifier mode (see figure 3).

A low pass anti-aliasing section is included onchip. This section typically provides 35dB attenuation at the sampling frequency. No external components are required to provide the necessary anti-aliasing function for the switched capacitor section of the transmit filter.

The passband section provides flatness and stopband attenuation which fulfills the AT&T D3/D4 channel bank transmission specification and CCITT recommendation G.712.

The M5913 specifications meet or exceed digital class 5 central office switching systems requirements. The transmit filter transfer characteristics and specifications will be within the limits shown the relative table.

A high pass section configuration was chosen to reject low frequency noise from 50 and 60Hz power lines, 17Hz European electric railroads, ringing frequencies and their harmonics, and other low frequency noise.

Even though there is high rejection at these frequencies, the sharpness of the band edge gives low attenuation at 200Hz. This feature allows the use of low-cost transformer hybrids without external components.

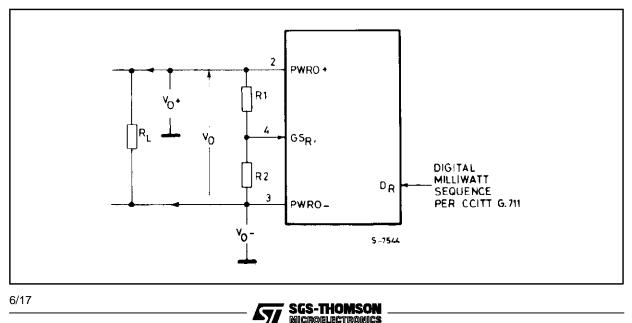

Figure 3: Transmit Filter Gain Adjustment.

#### Encoding

The encoder internally samples the output of the transmit filter and holds each sample on an internal sample and hold capacitor.

The encoder then performs an analog to digital conversion on a switched capacitor array. Digital data representing the sample is transmitted on the first eight data clock bits of the next frame.

An on-chip autozero circuit corrects for DC-offset on the input signal to the encoder. This autozero circuit uses the sign bit averaging technique. In this way, all DC offset is removed from the encoder input waveform.

#### **RECEIVE OPERATION**

#### Decoding

The PCM word at the  $D_R$  lead is serially fetched on the first eight data clock bits of the frame. A D/A conversion is performed on the digital word and the corresponding analog sample is held on

Figure 4: Gain Setting Configuration.

an internal sample and hold capacitor. This sample is then transferred to the receive filter.

#### **Receive Filter**

The receive section of the filter provides passband flatness and stopband rejection which fulfills both the AT&T D3/D4 specification and CCITT recommendation G.712. The filter contains the required compensation for the (sin X)/X response of such decoders. The receive filter characteristics and specifications are shown in the relative table.

#### **Receive Output Power Amplifiers**

A balanced output amplifier is provided in order to allow maximum flexibility in output configuration. Either of the two outputs can be used single ended (referenced to GRDA) to drive single ended loads. Alternatively, the differential output will drive a bridged load directly. The output stage is capable of driving loads as low as 300 ohms single ended to a level of 12dBm or 600 ohms differentially to a level of 15dBm.

The receive channel transmission level may be adjusted between specified limits by manipulation of the  $GS_R$  input.  $GS_R$  is internally connected to an analog gain setting network. When  $GS_R$  is strapped to PWRO–, the receive level is minimized; when it is tied to PWRO+, the level is minimized. The output transmission level interpolates between 0 and -12dB as GSR is interpolated (with potentiometer) between PWRO- and PWRO+. The use of the output gain set is illustrated in figure 4.

Transmission levels are specified relative to the receive channel output under digital milliwatt conditions, that is, when the digital input at  $D_R$  is the eight-code sequence specified in CCITT recommendation G.711.

#### OUTPUT GAIN SET: DESIGN CONSIDERA-TIONS (refer to figure 4)

PWRO+ and PWRO- are low impedance complementary outputs. The voltages at the nodes are:

V<sub>O</sub> at PWRO+

V<sub>O</sub> at PWRO

$V_0 = V_0 + V_0 -$ (total differential response)

R1 and R2 are a gain setting resistor network with the center tap connected to the GS<sub>R</sub> input. A value greater than  $10K\Omega$  and less than  $100K\Omega$  for R1 + R2 is recommended because:

- a) The parallel combination of R1 + R2 and RL sets the total loading.

- b) The total capacitance at the GS<sub>R</sub> input and the parallel combination of R1 and R2 define a time constant which has to be minimized to avoid inaccuracies.

If VA represents the output voltage without any gain setting network connected, you can have:

$$V_{O} = AV_{A}$$

where  $A = \frac{1 + (R_{1} / R_{2})}{4 + (R_{1} / R_{2})}$

For design purposes, a useful form is R1/R2 as a function of A.

$$R1/R2 = \frac{4A-1}{1-A}$$

(allowable values for A are those which make R1/R2 positive)

Examples are:

If A = 1 (maximum output), then  $R1/R2 = \infty$  or V(GS<sub>R</sub>) = V<sub>O</sub>; i.e., GS<sub>R</sub> is tied to PWRO+ If A = 1/2. then R1/R2 = 2

If A = 1/4 (minimum output) then R1/R2 = 0 or V(GS<sub>R</sub>) = V<sub>O+</sub>; i.e., GSR is tied to PWRO+

| <b>DC CHARACTERISTICS</b> ( $T_{amb} = 0$ to 70°C, $V_{CC} = +5V \pm 5\%$ , $V_{BB} = -5V \pm 5\%$ , GRDA = 0V, unless oth- |

|-----------------------------------------------------------------------------------------------------------------------------|

| erwise specified) Typical values are for $T_{amb} = 25^{\circ}C$ and nominal power supply values.                           |

| Symbol           | Parameter                           | Test Conditions                                                     | Min.                     | Тур. | Max.                     | Unit |

|------------------|-------------------------------------|---------------------------------------------------------------------|--------------------------|------|--------------------------|------|

| DIGITAL          | INTERFACE                           |                                                                     |                          |      |                          |      |

| l <sub>IL</sub>  | Low Level Input Current             | $GRDD \le V_{IN} \le V_{IL}$ (note 1)                               |                          |      | 10                       | μA   |

| Іін              | High Level Input Current            | $V_{IH} \le V_{IN} \le V_{CC}$                                      |                          |      | 10                       | μA   |

| VIL              | Input Low Voltage, Except CLKSEL    |                                                                     |                          |      | 0.8                      | V    |

| VIH              | Input High Voltage, Except CLKSEL   |                                                                     | 2.0                      |      |                          | V    |

| Vol              | Output Low Voltage                  | $I_{OL} = 3.2$ mA at $D_X$ , $\overline{TS}_X$ and SIG <sub>R</sub> |                          |      | 0.4                      | V    |

| V <sub>OH</sub>  | Output High Voltage                 | $I_{OH} = 9.6$ mA at $D_X$<br>$I_{OH} = 1.2$ mA at SIG <sub>R</sub> | 2.4                      |      |                          | V    |

| VILO             | Input Low Voltage, CLKSEL (note 2)  |                                                                     | V <sub>BB</sub>          |      | V <sub>BB</sub> +<br>0.5 | V    |

| V <sub>IIO</sub> | Input Intermediate Voltage, CLKSEL  |                                                                     | GRDD<br>-0.5             |      | 0.5                      | V    |

| Viho             | Input High Voltage, CLKSEL          |                                                                     | V <sub>CC</sub> -<br>0.5 |      | VCC                      | V    |

| Cox              | Digital Output Capacitance (note 3) |                                                                     |                          | 5    |                          | рF   |

| CIN              | Digital Input Capacitance           |                                                                     |                          | 5    | 10                       | рF   |

#### Notes:

1. V<sub>IN</sub> is the voltage on any digital pin.

SIG<sub>X</sub> and DCLK<sub>R</sub> are TTL level inputs between GRDD and V<sub>CC</sub>; they are also pinstraps for mode selection when tied to V<sub>BB</sub>. Under these conditions V<sub>ILO</sub> is the input low voltage requirement.

3. Timing parameters are guaranteed based on a 100pF load capacitance. Up to eight digital outputs may be connected to a common PCM highway without buffering, assuming a board capacitance of 60pF.

#### DC CHARACTERISTICS (continued)

| Symbol           | Parameter                                                     | Test Conditions                         | Min.   | Тур.   | Max  | Unit |

|------------------|---------------------------------------------------------------|-----------------------------------------|--------|--------|------|------|

| POWER            | DISSIPATION All measurements made at f                        | DCLK = 2.048MHz, outputs unload         | ded    |        |      |      |

| I <sub>CC1</sub> | V <sub>CC</sub> Operating Current                             |                                         |        | 6      | 10   | mA   |

| I <sub>BB1</sub> | V <sub>BB</sub> Operating Current                             |                                         |        | 6      | 9    | mA   |

| I <sub>CC0</sub> | V <sub>CC</sub> Power Down Current                            | $PDN \le V_{IL}$ ; after 10µs           |        | 40     | 300  | μA   |

| I <sub>BB0</sub> | V <sub>BB</sub> Power Down Current                            | $PDN \le V_{IL}$ ; after 10µs           |        | 40     | 300  | μA   |

| I <sub>CCS</sub> | V <sub>CC</sub> Standby Current                               | $FS_X, FS_R \le V_{IL}$ ; after 30ms    |        | 300    | 600  | μA   |

| I <sub>BBS</sub> | V <sub>BB</sub> Standby Current                               | $FS_X$ , $FS_R \le V_{IL}$ ; after 30ms |        | 40     | 300  | μA   |

| P <sub>D1</sub>  | Operating Power Dissipation                                   |                                         |        | 60     | 100  | mW   |

| P <sub>D0</sub>  | Power Down Dissipation                                        | $PDN \le V_{IL}$ ; after 10µs           |        | 0.4    | 3    | mW   |

| P <sub>ST</sub>  | Standby Power Dissipation                                     | FSX, $FS_R \le V_{IL}$ ; after 30ms     |        | 1.7    | 5    | mW   |

| ANALOG           | INTERFACE, RECEIVE FILTER DRIVER                              | AMPLIFIER STAGE                         |        |        |      |      |

| I <sub>BX1</sub> | Input Leakage Current, VF <sub>X</sub> I+, VF <sub>X</sub> I- | $-2.17V \le V_{IN} \le 2.17V$           |        |        | 100  | nA   |

| Rixi             | Input Resistance, VF <sub>X</sub> I+, VF <sub>X</sub> I-      |                                         | 10     |        |      | MΩ   |

| Vosxi            | Input Offset Voltage, VF <sub>X</sub> I+, VF <sub>X</sub> I-  |                                         |        |        | 25   | mV   |

| CMRR             | Common Mode Rejection, VF <sub>X</sub> I+, VF <sub>X</sub> I- | $-2.17V \le V_{IN} \le 2.17V$           | 55     |        |      | dB   |

| Avol             | DC Open Loop Voltage Gain, GS <sub>X</sub>                    | R <sub>L</sub> = 10K                    | 5000   | 20.000 |      |      |

| fc               | Open Loop Unity Gain Bandwidth, GS <sub>X</sub>               |                                         |        | 1      |      | MHz  |

| Voxi             | Output Voltage Swing GS <sub>X</sub>                          | $R_L \ge 10 k\Omega$                    | - 2.17 |        | 2.17 | V    |

| C <sub>LXI</sub> | Load Capacitance, GS <sub>X</sub>                             |                                         |        |        | 50   | pF   |

| R <sub>LXI</sub> | Minimum Load Resistance, GS <sub>X</sub>                      |                                         | 10     |        |      | kΩ   |

| ANALOG           | INTERFACE, RECEIVE FILTER DRIVER                              | AMPLIFIER STAGE                         |        |        |      |      |

| R <sub>ORA</sub> | Output Resistance, PWRO+, PWRO-                               |                                         |        | 1      |      | Ω    |

| Vosra            | Single-ended Output DC Offset,<br>PWRO+, PWRO-                | Relative to GRDA                        | -150   | 75     | 150  | mV   |

| C <sub>LRA</sub> | Load Capacitance, PWRO+, PWRO-                                |                                         |        |        | 100  | pF   |

## AC CHARACTERISTICS - TRANSMISSION PARAMETERS

Unless otherwie noted, the analog input is a 0dBm0, 1020Hz sine wave<sup>1</sup>. Input amplifier is set for unity gain, noninverting. The digital inputs is a PCM bit stream generated by passing a 0dBm0, 1020Hz sine wave through an ideal encoder. Receive output is measured single ended, maximum gain configuration<sup>2</sup>. All output levels are (sin X)/X corrected.

| Symbol             | Parameter                                                        | Test Conditions                                                                                                                                    | Min.  | Тур.             | Max.  | Unit       |  |  |

|--------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|-------|------------|--|--|

| GAIN AN            | GAIN AND DYNAMIC RANGE                                           |                                                                                                                                                    |       |                  |       |            |  |  |

| EmW                | Encoder Milliwatt Response<br>(transmit gain tolerance)          | $\label{eq:Tamb} \begin{array}{l} T_{amb} = 25^\circ C, \ V_{BB} = - \ 5V, \\ V_{CC} = + \ 5V \end{array}$                                         | -0.15 | ± 0.04           | +0.15 | dBm0       |  |  |

| EmW <sub>TS</sub>  | EmW Variation with Temperature and Supplies                      | ± 5% Supplies, 0 to 70°C<br>Relative to Nominal<br>Conditions                                                                                      | -0.12 |                  | +0.12 | dB         |  |  |

| DmW                | Digital Milliwatt Response<br>(receive gain tolerance)           | $\begin{array}{l} T_{amb} = 25^{\circ}C \hspace{0.1cm} ; \hspace{0.1cm} V_{BB} = - \hspace{0.1cm} 5V, \\ V_{CC} = + \hspace{0.1cm} 5V \end{array}$ | -0.15 | ± 0.04           | +0.15 | dBm0       |  |  |

| DmW⊤s              | DmW Variation with Temperature and<br>Supplies                   | $\pm$ 5%, 0 to 70°C                                                                                                                                | -0.08 |                  | +0.08 | dB         |  |  |

| 0TLP <sub>1X</sub> | Zero Transmission Level Point<br>Transmit Channel (0dBm0) μ-law  | Referenced to $600\Omega$<br>Referenced to $900\Omega$                                                                                             |       | + 2.76<br>+ 1.00 |       | dBm<br>dBm |  |  |

| 0TLP <sub>2X</sub> | Zero Transmission Level Point<br>Transmit Channel (0dBm0) A-law  | Referenced to $600\Omega$<br>Referenced to $900\Omega$                                                                                             |       | + 2.79<br>+ 1.03 |       | dBm<br>dBm |  |  |

| 0TLP <sub>1R</sub> | Zero Receive Level Point<br>Receive Channel (0dBm0) μ-law        | Referenced to $600\Omega$<br>Referenced to $900\Omega$                                                                                             |       | + 5.76<br>+ 4.00 |       | dBm<br>dBm |  |  |

| 0TLP <sub>2R</sub> | Zero Transmission Level Point<br>Transmit Channel (0dBm0)) A-law | Referenced to $600\Omega$<br>Referenced to $900\Omega$                                                                                             |       | + 5.79<br>+ 4.03 |       | dBm<br>dBm |  |  |

| Symbol            | Parameter                                                       | Test Conditions                                                                                            | Min. | Тур.     | Max.                    | Unit           |

|-------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|----------|-------------------------|----------------|

| GAIN TR           | ACKING Reference Level = – 10dBm0                               |                                                                                                            |      |          |                         |                |

| GT1 <sub>X</sub>  | Transmit Gain Tracking Error<br>Sinusoidal Input; μ-law         | + 3 to - 40dBm0<br>- 40 to - 50dBm0<br>- 50 to - 55dBm0                                                    |      |          | ± 0.2<br>± 0.4<br>± 1.0 | dB<br>dB<br>dB |

| GT2 <sub>X</sub>  | Transmit Gain Tracking Error<br>Sinusoidal Input; A-law         | + 3 to - 40dBm0<br>- 40 to - 50dBm0<br>- 50 to - 55dBm0                                                    |      |          | ± 0.2<br>± 0.4<br>± 1.0 | dB<br>dB<br>dB |

| GT1 <sub>R</sub>  | Receive Gain Tracking Error<br>Sinusoidal Input; μ-law          | + 3 to - 40dBm0<br>- 40 to - 50dBm0<br>- 50 to - 55dBm0                                                    |      |          | ± 0.2<br>± 0.4<br>± 1.0 | dB<br>dB<br>dB |

| GT2 <sub>R</sub>  | Receive Gain Tracking Error<br>Sinusoidal Input; A-law          | + 3 to - 40dBm0<br>- 40 to - 50dBm0<br>- 50 to - 55dBm0                                                    |      |          | ± 0.2<br>± 0.4<br>± 1.0 | dB<br>dB<br>dB |

| NOISE             | -                                                               |                                                                                                            |      |          |                         | _              |

| N <sub>XC1</sub>  | Transmit Noise, C-message Weighted                              | $VF_XI+ = GRDA, VF_XI- = GS_X$                                                                             |      | 0        | 13                      | dBrnc0         |

| N <sub>XC2</sub>  | Transmit Noise, C-message<br>Weighted with Eighth Bit Signaling | $VF_XI+ = GRDA, VF_XI- = GS_X$<br>6 th Frame Signaling                                                     |      | 13       | 18                      | dBrnc0         |

| N <sub>XP</sub>   | Transmit Noise, Psophometrically Weighted                       | $VF_XI+ = GRDA, VF_XI- = GS_X$                                                                             |      | (note 3) | - 80                    | dBrnc0         |

| N <sub>RC1</sub>  | Receive Noise, C-message Weighted:<br>Quiet Code                | D <sub>R</sub> = 11111111 Measure at<br>PWRO+                                                              |      | 1        | 9                       | dBrnc0         |

| N <sub>RC2</sub>  | Receive Noise, C-message Weighted:<br>Sign Bit Toggle           | Input to D <sub>R</sub> is 0 code with<br>Sign Bit Toggle at 1KHz Rate                                     |      | 1        | 10                      | dBm0p          |

| N <sub>RP</sub>   | Receive Noise, Psophometrically Weighted                        | D <sub>R</sub> = Lowest Positive Decode<br>Level                                                           |      | -90      | - 81                    | dB0p           |

| NSF               | Single Frequency NOISE End to End<br>Measurement                | CCITT G.712.4.2                                                                                            |      |          | - 50                    | dBm0           |

| PSRR₁             | V <sub>CC</sub> Power Supply Rejection, Transmit Channel        | Idle Channel ; 200mV P-P<br>Signal on Supply ; 0 to<br>50kHz, Measure at D <sub>X</sub>                    |      | - 40     |                         | dB             |

| PSRR <sub>2</sub> | V <sub>BB</sub> Power Supply Rejection, Transmit<br>Channel     | Idle Channel ; 200mV P-P<br>Signal on Supply ; 0 to<br>50kHz, Measure at D <sub>X</sub>                    |      | - 40     |                         | dB             |

| PSRR₃             | V <sub>CC</sub> Power Supply Rejection, Receive Channel         | Idle Channel ; 200mV P-P<br>Signal on Supply ; Measure<br>Narrow Band at PWRO+<br>Single Ended, 0 to 50kHz |      | - 40     |                         | dB             |

| PSRR <sub>4</sub> | V <sub>BB</sub> Power Supply, Rejection Receive<br>Channel      | Idle Channel ; 200mV P-P<br>Signal on Supply ; Measure<br>Narrow Band at PWRO+<br>Single Ended, 0 to 50kHz |      | - 40     |                         | dB             |

| CT <sub>TR</sub>  | Crosstalk, Transmit to Receive,<br>Single Ended Outputs         | $VF_XI+ = 0dBm0, 1.02kHz,$<br>$D_R = Lowest Positive Decode$<br>Level, Measure at PWRO+                    |      |          | - 80                    | dB             |

| CT <sub>RT</sub>  | Crosstalk, Receive to Transmit,<br>Single Ended Outputs         | $D_B = 0dBm0, 1.02kHz,$<br>VF <sub>X</sub> I+ = GRDA, Measure at $D_X$                                     |      |          | - 80                    | dB             |

#### AC CHARACTERISTICS (continued)

#### Notes:

1. 0dBm0 is defined as the zero reference point of the channel under test (0TLP). This corresponds to an analog signal input of 1.064  $V_{rms}$  or an output of 1.503  $V_{rmst}$  ( $\mu$ Law) dual 1.068  $V_{rmst}$  or a output 1.516  $V_{rmst}$  (A-Law)

2. Unity gain input amplifier : GS<sub>x</sub> is connected to VF<sub>x</sub>I, Signal input VF<sub>x</sub>I+; Maximum gain output amplifier: GS<sub>R</sub> is connected to PWRO, output to PWRO+.

3. Noise free: DX PCM Code stable at 01010101.

| A.C. CHARACTERISTICS (CONTINUED | A.C. | CHARACTERISTICS | (continued) |

|---------------------------------|------|-----------------|-------------|

|---------------------------------|------|-----------------|-------------|

| Symbol           | Parameter                                                                          | Test Conditions                                                                                                    | Min.           | Тур.                  | Max. | Unit                 |

|------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------|-----------------------|------|----------------------|

| DISTORT          | ION                                                                                |                                                                                                                    |                | -                     | _    |                      |

| SD1 <sub>X</sub> | Transmit Signal to Distortion, μ-law<br>Sinusoidal Input;<br>CCITT G.712-method 2  | $\begin{array}{l} 0 \leq VF_XI+ \leq -\ 30dBm0\\ -\ 40dBm0\\ -\ 45dBm0 \end{array}$                                | 36<br>30<br>25 |                       |      | dB<br>dB<br>dB       |

| SD2 <sub>X</sub> | Transmit Signal to Distortion, A-law<br>Sinusoidal Input,<br>CCITT G.712-method 2  | $\begin{array}{l} 0 \leq VF_XI+ \leq - \ 30dBm0 \\ - \ 40dBm0 \\ - \ 45dBm0 \end{array}$                           | 36<br>30<br>25 |                       |      | dB<br>dB<br>dB       |

| SD1 <sub>R</sub> | Transmit Signal to Distortion,<br>μ-law Sinusoidal Input ,<br>CCITT G.712-method 2 | $0 \le VF_XI+ \le -30dBm0$<br>- 40dBm0<br>- 45dBm0                                                                 | 36<br>30<br>25 |                       |      | dB<br>dB<br>dB       |

| SD2 <sub>R</sub> | Receive Signal to Distortion, A-law<br>Sinusoidal Input;<br>CCITT G.712-method 2   | $\begin{array}{l} 0 \leq VF_XI\text{+} \leq - \ 30 dBm0 \\ - \ 40 dBm0 \\ - \ 45 dBm0 \end{array}$                 | 36<br>30<br>25 |                       |      | dB<br>dB<br>dB       |

| DP <sub>X1</sub> | Transmit Single Frequency Distortion<br>Products                                   | AT & T Adivisory # 64 (3.8)<br>0dBm0 Input Signal                                                                  |                |                       | - 46 | dB                   |

| DP <sub>R1</sub> | Receive Single Frequency Distortion<br>Products                                    | AT & T Adivisory # 64 (3.8)<br>0dBm0 Input Signal                                                                  |                |                       | - 46 | dB                   |

| IMD <sub>1</sub> | Intermodulation Distortion,<br>End to End Measurement                              | CCITT G.712 (7.1)                                                                                                  |                |                       | - 35 | dB                   |

| IMD <sub>2</sub> | Intermodulation Distortion,<br>End to End Measurement                              | CCITT G.712 (7.2)                                                                                                  |                |                       | - 49 | dB                   |

| SOS              | Spurious Out of Band Signals,<br>End to End Measurement                            | CCITT G.712 (6.1)                                                                                                  |                |                       | - 30 | dBm0                 |

| SIS              | Spurious in Band Signals,<br>End to End Measurement                                | CCITT G.712 (9)                                                                                                    |                |                       | - 40 | dBm0                 |

| D <sub>AX</sub>  | Transmit Absolute Delay                                                            | Fixed Data Rate $CLK_X =$<br>2.048MHz,<br>0dBm0, 1.02kHz Signal at<br>VF <sub>X</sub> I+ Measure at D <sub>X</sub> |                | 300                   |      | μs                   |

| D <sub>DX</sub>  | Transmit Differential Envelope Delay<br>Relative to D <sub>AX</sub>                | f = 500 - 600Hz<br>f = 600 - 1000Hz<br>f = 1000 - 2600Hz<br>f = 2600 - 2800Hz                                      |                | 170<br>95<br>45<br>80 |      | μs<br>μs<br>μs<br>μs |

| D <sub>AR</sub>  | Receive Absolute Delay                                                             | Fixed data rate, CLK <sub>R</sub> =<br>2.048MHz;<br>Digital input is DMW codes.<br>Measure at PWRO+                |                |                       | 190  | μs                   |

| D <sub>DR</sub>  | Receive Differential Envelope Delay<br>Relative to D <sub>AR</sub>                 |                                                                                                                    |                | 10<br>10<br>85<br>110 |      | μs<br>μs<br>μs<br>μs |

## A.C. CHARACTERISTICS (continued)

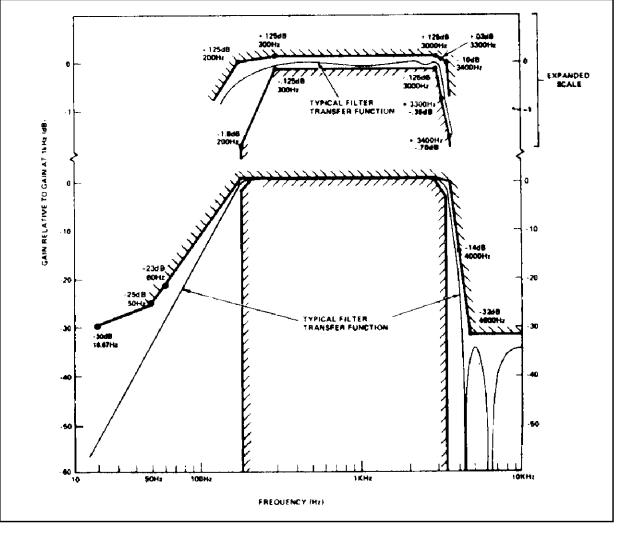

## TRANSMIT CHANNEL TRANSFER CHARACTERISTICS

(Input amplifier is set for unity gain, noninverting; maximum gain output.)

| Symbol          | Parameter                         | Test Conditions                           | Min.    | Тур. | Max.    | Unit |

|-----------------|-----------------------------------|-------------------------------------------|---------|------|---------|------|

| G <sub>RX</sub> | Gain Relative to Gain at 1.02 kHz | 0 dBm0 Signal Input at VF <sub>X</sub> I+ |         |      |         |      |

|                 | 16.67Hz                           |                                           |         |      | - 30    | dB   |

|                 | 50Hz                              |                                           |         |      | - 25    | dB   |

|                 | 60Hz                              |                                           |         |      | - 23    | dB   |

|                 | 200Hz                             |                                           | – 1.8   |      | - 0.125 | dB   |

|                 | 300 to 3000Hz                     |                                           | - 0.125 |      | + 0.125 | dB   |

|                 | 3300Hz                            |                                           | - 0.35  |      | + 0.03  | dB   |

|                 | 3400Hz                            |                                           | - 0.7   |      | - 0.10  | dB   |

|                 | 4000Hz                            |                                           |         |      | - 14    | dB   |

|                 | 4600Hz and Above                  |                                           |         |      | - 32    | dB   |

## Figure 5: Transmit Filter

## A.C. CHARACTERISTICS (continued)

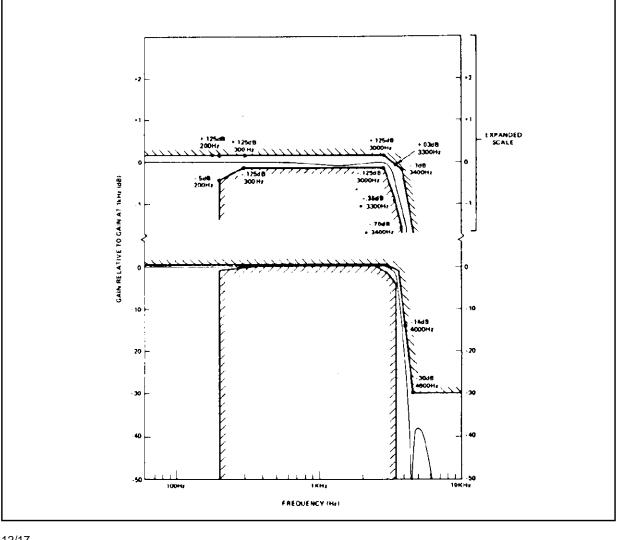

## RECEIVE CHANNEL TRANSFER CHARACTERISTICS

| Symbol          | Parameter                       | Test Conditions                      | Min.    | Тур. | Max.    | Unit |

|-----------------|---------------------------------|--------------------------------------|---------|------|---------|------|

| G <sub>RR</sub> | Gain Relative to Gainat 1.02kHz | 0dBm0 Signal Input at D <sub>R</sub> |         |      |         |      |

|                 | below 200Hz                     |                                      |         |      | + 0.125 | dB   |

|                 | 200Hz                           |                                      | - 0.5   |      | + 0.125 | dB   |

|                 | 300 to 3000Hz                   |                                      | - 0.125 |      | + 0.125 | dB   |

|                 | 3300Hz                          |                                      | - 0.35  |      | + 0.03  | dB   |

|                 | 3400Hz                          |                                      | - 0.7   |      | - 0.1   | dB   |

|                 | 4000Hz                          |                                      |         |      | - 14    | dB   |

|                 | 4600Hz and Above                |                                      |         |      | - 30    | dB   |

## Figure 6: Receive Filter

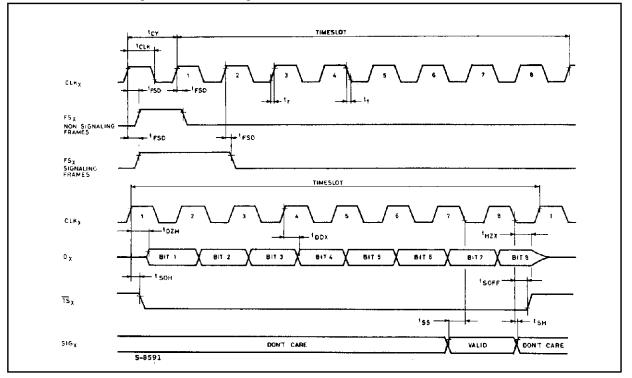

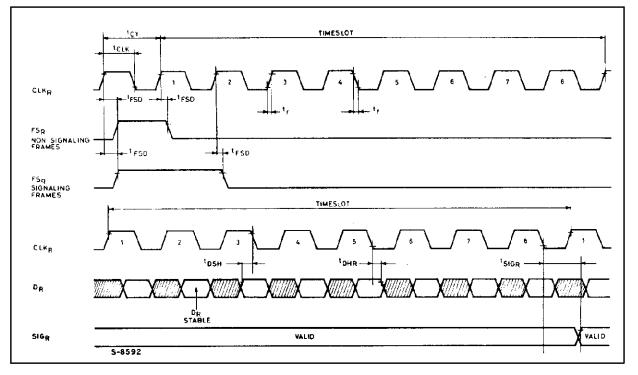

#### **AC CHARACTERISTICS - TIMING PARAMETERS**

| Symbol                          | Parameter                                         | Test Conditions                                    | Min. | Тур. | Max.              | Unit |

|---------------------------------|---------------------------------------------------|----------------------------------------------------|------|------|-------------------|------|

| CLOCK S                         |                                                   |                                                    | •    |      | •                 | •    |

| t <sub>CY</sub>                 | Clock Period, CLK <sub>X</sub> , CLK <sub>R</sub> | $f_{CLKX} = f_{CLKR} = 2.048MHz$                   | 488  |      |                   | ns   |

| t <sub>CLK</sub>                | Clock Pulse Width                                 | CLK <sub>X</sub> , CLK <sub>R</sub>                | 195  |      |                   | ns   |

| <b>t</b> DCLK                   | Data Clock Pulse Width <sup>1</sup>               | $64$ kHz $\leq f_{DCLK} \leq 2.048$ MHz            | 195  |      |                   | ns   |

| tcdc                            | Clock Duty Cycle                                  | CLK <sub>X</sub> , CLK <sub>R</sub>                | 40   | 50   | 60                | %    |

| t <sub>r</sub> , t <sub>f</sub> | Clock Rise and Fall Time                          |                                                    | 5    |      | 30                | ns   |

| TRANSM                          | IT SECTION, FIXED DATA RATE MOD                   | DE <sup>2</sup>                                    |      |      |                   |      |

| t <sub>DZX</sub>                | Data Enabled on TS Entry                          | $0 < C_{LOAD} < 100 pF$                            | 0    |      | 145               | ns   |

| t <sub>DDX</sub>                | Data Delay from CLK <sub>X</sub>                  | 0 < C <sub>LOAD</sub> < 100pF                      | 0    |      | 145               | ns   |

| t <sub>HZX</sub>                | Data Float on TS Exit                             | $C_{LOAD} = 0$                                     | 60   |      | 190               | ns   |

| tson                            | Timeslot X to Enable                              | $0 < C_{LOAD} < 100 pF$                            | 0    |      | 145               | ns   |

| t <sub>SOFF</sub>               | Timeslot X to Disable                             | $C_{LOAD} = 0$                                     | 50   |      | 190               | ns   |

| t <sub>FSD</sub>                | Frame Sync Delay                                  |                                                    | 0    |      | 120               | ns   |

| tss                             | Signal Setup Time                                 |                                                    | 0    |      |                   | ns   |

| t <sub>SH</sub>                 | Signal Setup Time                                 |                                                    | 0    |      |                   | ns   |

| RECEIVE                         | SECTION, FIXED DATA RATE MODE                     | =                                                  |      |      |                   |      |

| t <sub>DSR</sub>                | Receive Data Setup                                |                                                    | 10   |      |                   | ns   |

| <b>t</b> DHR                    | Receive Data Hold                                 |                                                    | 60   |      |                   | ns   |

| t <sub>FSD</sub>                | Frame Sync Delay                                  |                                                    | 0    |      | 120               | ns   |

| tsigr                           | SIG <sub>R</sub> Update                           |                                                    | 0    |      | 2                 | μs   |

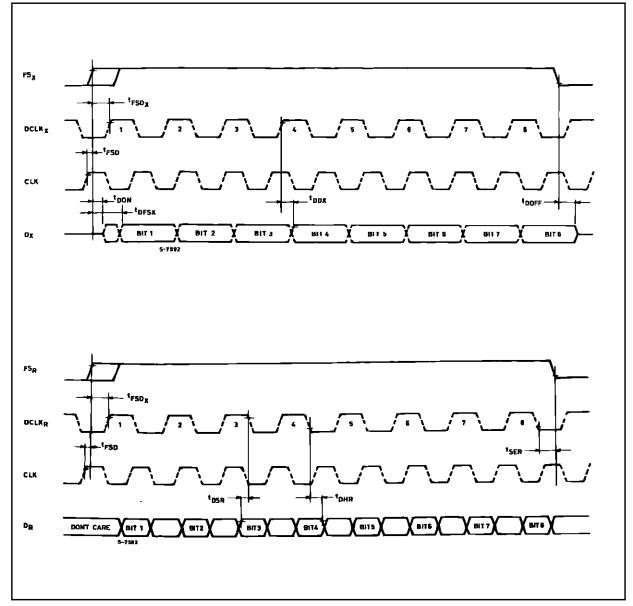

| TRANSM                          | IT SECTION, FIXED DATA RATE MOD                   | DE <sup>2</sup>                                    |      |      |                   |      |

| t <sub>TSDX</sub>               | Timeslot Delay from DCLKx                         |                                                    | -80  |      | 80                | ns   |

| t <sub>FSD</sub>                | Frame Sync Delay                                  |                                                    | 0    |      | 120               | ns   |

| t <sub>DDX</sub>                | Data Delay from DCLK <sub>X</sub>                 | 0 < CLOAD < 100pF                                  | 0    |      | 100               | ns   |

| <b>t</b> DON                    | Timeslot to D <sub>X</sub> Active                 | $0 < C_{LOAD} < 100 pF$                            | 0    |      | 50                | ns   |

| t <sub>DOFF</sub>               | Timeslot to D <sub>X</sub> Inactive               | $0 < C_{LOAD} < 100 pF$                            | 0    |      | 80                | ns   |

| f <sub>DX</sub>                 | Data Clock Frequency                              |                                                    | 64   |      | 2048 <sup>1</sup> | KHz  |

| t <sub>DFSX</sub>               | Data Delay from FS <sub>X</sub>                   | t <sub>TSDX</sub> = 80ns                           | 0    |      | 140               | ns   |

| RECEIVE                         | SECTION, FIXED DATA RATE MODE                     | E                                                  | _    | _    | _                 |      |

| t <sub>TSDR</sub>               | Timeslot Delay from DCLK <sub>R</sub>             |                                                    | -80  |      | 80                | ns   |

| t <sub>FSD</sub>                | Frame Sync Delay                                  |                                                    | 0    |      | 120               | ns   |

| t <sub>DSR</sub>                | Receive Data Setup Time                           |                                                    | 10   |      |                   | ns   |

| t <sub>DHR</sub>                | Receive Data Hold Time                            |                                                    | 60   |      |                   | ns   |

| t <sub>DR</sub>                 | Data Clock Frequency                              |                                                    | 64   |      | 2048 <sup>1</sup> | kHz  |

| t <sub>SER</sub>                | Timeslot End Receive Time                         |                                                    | 0    |      |                   | ns   |

| 64KB OP                         | ERATION, VARIABLE DATA RATE MO                    | DDE                                                |      |      |                   |      |

| t <sub>FSLX</sub>               | Transmit Frame Sync Minimum<br>Downtime           | FS <sub>X</sub> is TTL high for remainder of frame | 488  |      |                   | ns   |

| t <sub>FSLR</sub>               | Receive Frame Sync Miniumum<br>Downtime           | FS <sub>R</sub> is TTL high for remainder of frame | 1952 |      |                   | ns   |

| <b>t</b> DCLK                   | Data Clock Pulse Width                            |                                                    | 10   |      |                   | μs   |

Notes:

1. Devices are available wich operate at data rates up to 4.096MHz; the minimum data clock pulse width for these devices is 110ns

2. Timing parameters  $t_{\text{DZX}},\,t_{\text{HZX}},$  and  $t_{\text{SOFF}}$  are referenced to a high impedance state.

## WAVEFORMS:

Fixed Data Rate Timing - Transmit Timing

NOTE: All timing parameters referenced to  $V_{IH}$  and  $V_{IL}$  except t<sub>DZX</sub>, t<sub>OFF</sub> and t<sub>HZX</sub> which reference a high impedance state.

#### **Receive Timing**

NOTE: All timing parameters referenced to  $V_{IH}$  and  $V_{IL}$

## VARIABLE DATA RATE TIMING

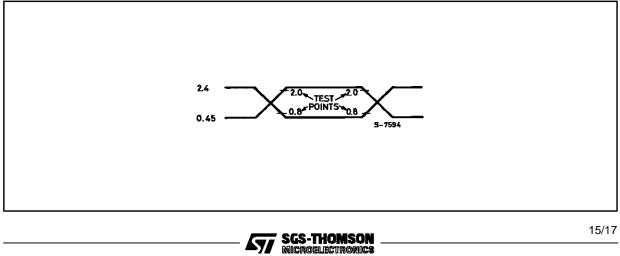

AC Timing Input, Output Waveform

## M5913

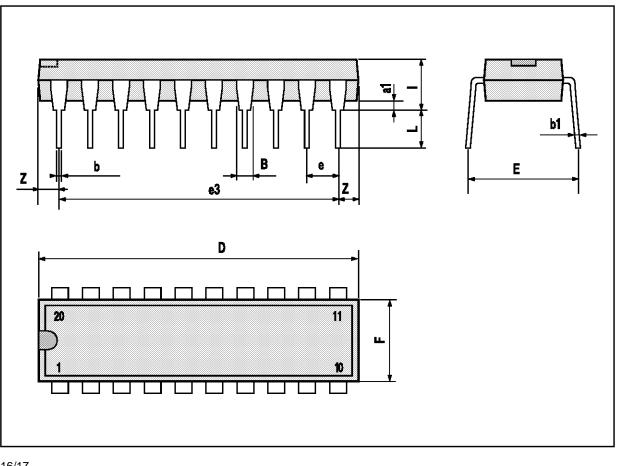

### **DIP20 PACKAGE MECHANICAL DATA**

| DIM. | mm    |       | inch |       |       |       |

|------|-------|-------|------|-------|-------|-------|

| Dim. | MIN.  | TYP.  | MAX. | MIN.  | TYP.  | MAX.  |

| a1   | 0.254 |       |      | 0.010 |       |       |

| В    | 1.39  |       | 1.65 | 0.055 |       | 0.065 |

| b    |       | 0.45  |      |       | 0.018 |       |

| b1   |       | 0.25  |      |       | 0.010 |       |

| D    |       |       | 25.4 |       |       | 1.000 |

| E    |       | 8.5   |      |       | 0.335 |       |

| е    |       | 2.54  |      |       | 0.100 |       |

| e3   |       | 22.86 |      |       | 0.900 |       |

| F    |       |       | 7.1  |       |       | 0.280 |

| I    |       |       | 3.93 |       |       | 0.155 |

| L    |       | 3.3   |      |       | 0.130 |       |

| Z    |       |       | 1.34 |       |       | 0.053 |

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1994 SGS-THOMSON Microelectronics - All Rights Reserved

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thaliand - United Kingdom - U.S.A.