# HMC441LM1

# GaAs PHEMT MMIC MEDIUM POWER AMPLIFIER, 7.0 - 15.5 GHz

### Typical Applications

The HMC441LM1 is a medium PA for:

- Point-to-Point Radios

- Point-to-Multi-Point Radios

- VSAT

- LO Driver for HMC Mixers

- Military EW & ECM

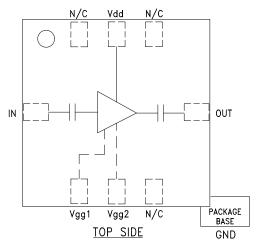

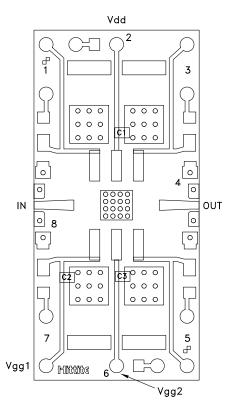

### Functional Diagram

Vgg1, Vgg2: Optional Gate Bias

#### **Features**

Gain: 15 dB

Saturated Power: +21.5 dBm @ 27% PAE

Single Supply Voltage:

+5.0 V w/ Optional Gate Bias 50 Ohms Matched Input/Output Leadless SMT Package, 25mm<sup>2</sup>

### **General Description**

The HMC441LM1 is a broadband 7 to 15.5 GHz GaAs PHEMT MMIC Medium Power Amplifier in an SMT leadless chip carrier package. The amplifier provides 15 dB of gain, 21.5 dBm of saturated power at 27% PAE from a +5.0V supply voltage. An optional gate bias is provided to allow adjustment of gain, RF output power, and DC power dissipation. This 50 Ohm matched amplifier does not require any external components making it an ideal linear gain block or driver for HMC SMT mixers.

## Electrical Specifications, T<sub>A</sub> = +25° C, Vdd = 5V, Vgg1 = Vgg2 = Open

| Parameter                                | Min.      | Тур.  | Max.       | Min. | Тур.        | Max. | Min.        | Тур.  | Max. | Min. | Тур.  | Max. | Units  |

|------------------------------------------|-----------|-------|------------|------|-------------|------|-------------|-------|------|------|-------|------|--------|

| Frequency Range                          | 7.0 - 8.0 |       | 8.0 - 12.5 |      | 12.5 - 14.0 |      | 14.0 - 15.5 |       | GHz  |      |       |      |        |

| Gain                                     | 12.5      | 15    |            | 13.5 | 16          |      | 12.5        | 15    |      | 11   | 13.5  |      | dB     |

| Gain Variation Over Temperature          |           | 0.015 | 0.02       |      | 0.015       | 0.02 |             | 0.015 | 0.02 |      | 0.015 | 0.02 | dB/ °C |

| Input Return Loss                        |           | 9     |            |      | 13          |      |             | 16    |      |      | 16    |      | dB     |

| Output Return Loss                       |           | 14    |            |      | 17          |      |             | 20    |      |      | 17    |      | dB     |

| Output Power for 1 dB Compression (P1dB) | 15.5      | 18.5  |            | 16   | 19          |      | 17          | 20    |      | 16   | 19    |      | dBm    |

| Saturated Output Power (Psat)            |           | 19.5  |            |      | 20.5        |      |             | 21.5  |      |      | 20.5  |      | dBm    |

| Output Third Order Intercept (IP3)       |           | 29    |            |      | 30          |      |             | 30    |      |      | 30    |      | dBm    |

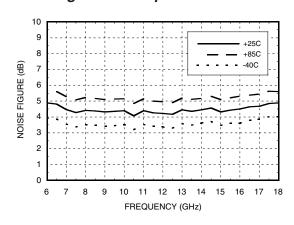

| Noise Figure                             |           | 4.5   |            |      | 4.5         |      |             | 4.5   |      |      | 4.5   |      | dB     |

| Supply Current (Idd)                     |           | 90    |            |      | 90          |      |             | 90    |      |      | 90    |      | mA     |

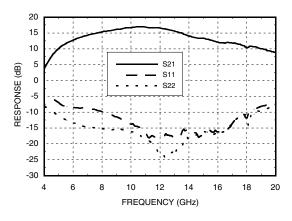

#### **Broadband Gain & Return Loss**

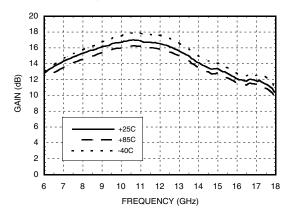

### Gain vs. Temperature

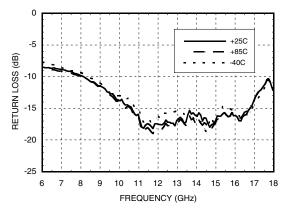

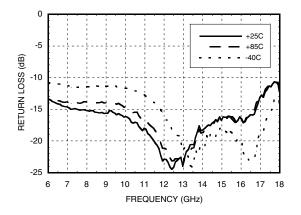

### Input Return Loss vs. Temperature

#### Output Return Loss vs. Temperature

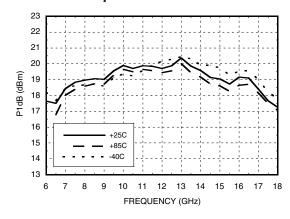

#### P1dB vs. Temperature

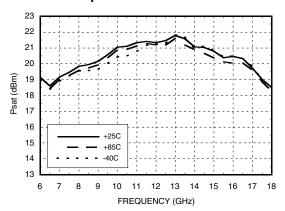

#### Psat vs. Temperature

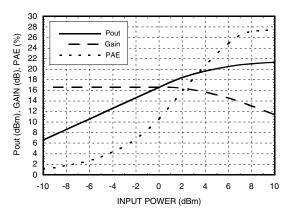

### Power Compression @ 12 GHz

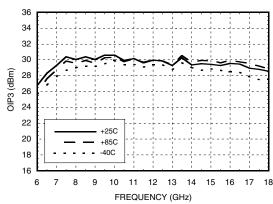

# Output IP3 vs. Temperature

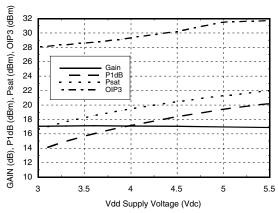

# Gain, Power & OIP3 vs. Supply Voltage @ 12 GHz

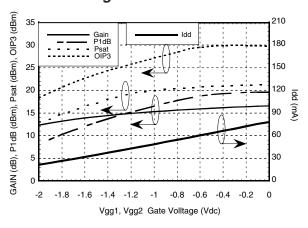

Gain, Power, OIP3 & Idd vs. Gate Voltage @ 12 GHz

### Noise Figure vs. Temperature

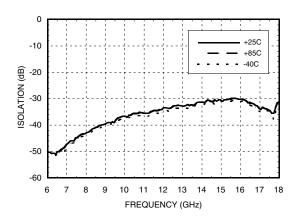

### Reverse Isolation vs. Temperature

### Absolute Maximum Ratings

| Drain Bias Voltage (Vdd)                                      | +6.0 Vdc       |

|---------------------------------------------------------------|----------------|

| Gate Bias Voltage (Vgg1,Vgg2)                                 | -8.0 to 0 Vdc  |

| RF Input Power (RFin)(Vdd = +5.0 Vdc)                         | +20 dBm        |

| Channel Temperature                                           | 175 °C         |

| Continuous Pdiss (T = 85 °C)<br>(derate 10 mW/°C above 85 °C) | 0.9 W          |

| Thermal Resistance (channel to ground paddle)                 | 100 °C/W       |

| Storage Temperature                                           | -65 to +150 °C |

| Operating Temperature                                         | -40 to +85 °C  |

### Typical Supply Current vs. Vdd

| Vdd (V) | Idd (mA) |

|---------|----------|

| +5.5    | 92       |

| +5.0    | 90       |

| +4.5    | 88       |

| +3.3    | 83       |

| +3.0    | 82       |

Note: Amplifier will operate over full voltage range shown above

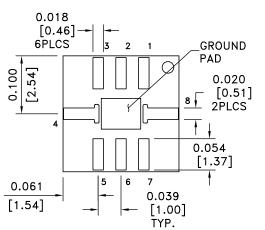

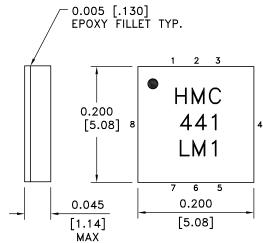

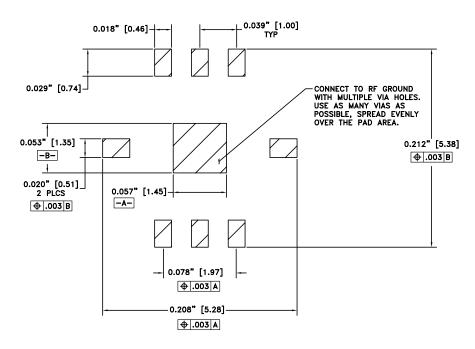

## **Outline Drawing**

#### NOTES:

- 1. MATERIAL: PLASTIC

- 2. PLATING: GOLD OVER NICKEL

- 3. DIMENSIONS ARE IN INCHES [MILLIMETERS].

- 4. ALL TOLERANCES ARE ±0.005 [±0.13].

- 5. ALL GROUNDS MUST BE SOLDERED TO PCB RF GROUND.

- 6. INDICATES PIN 1.

## Pin Descriptions

| Pin Number | Function   | Description                                                                                                                                  | Interface Schematic                   |

|------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 1, 3, 5    | N/C        | This pin may be connected to RF ground.                                                                                                      |                                       |

| 2          | Vdd        | Power Supply Voltage for the amplifier. An external bypass capacitor of 100 pF is recommended.                                               | Vald                                  |

| 4          | RF OUT     | This pin is AC coupled and matched to 50 Ohms from 7.0 - 15.5 GHz.                                                                           |                                       |

| 6, 7       | Vgg2, Vgg1 | Optional gate control for amplifier. If left open, the amplifier will run at standard current. Negative voltage applied will reduce current. | = V <sub>992</sub> , V <sub>992</sub> |

| 8          | RF IN      | This pin is AC coupled and matched to 50 Ohms from 7.0 - 15.5 GHz.                                                                           | RFIN O                                |

|            | GND        | Package bottom must be connected to RF ground.                                                                                               |                                       |

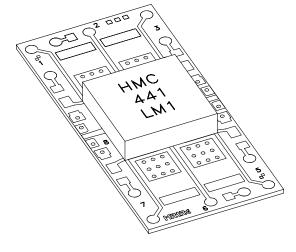

#### **Evaluation PCB**

The grounded Co-Planar Wave Guide (CPWG) PCB input/output transitions allow use of Ground-Signal-Ground (GSG) probes for testing. Suggested probe pitch is 400um (16 mils). Alternatively, the board can be mounted in a metal housing with 2.4mm coaxial connectors.

## **Evaluation Circuit Board Layout Design Details**

| Layout Technique         | Micro Strip to CPWG         |

|--------------------------|-----------------------------|

| Material                 | Rogers 4003 with 1/2 oz, Cu |

| Dielectric Thickness     | 0.008" (0.20 mm)            |

| Microstrip Line Width    | 0.018" (0.46 mm)            |

| CPWG Line Width          | 0.016" (0.41 mm)            |

| CPWG Line to GND Gap     | 0.005" (0.13 mm)            |

| Ground Via Hole Diameter | 0.008" (0.20 mm)            |

| C1 - C3                  | 100 pF Capacitor, 0402 Pkg. |

### Suggested LM1 PCB Land Pattern Tolerance: ± 0.003" (± 0.08 mm)

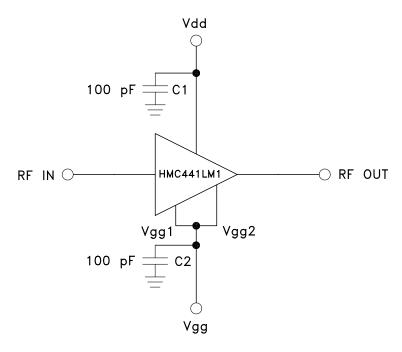

## **Amplifier Application Circuit**

Note: Optional gate bias connections. Vgg1 and Vgg2 may be connected to a common Vgg feed.

### Recommended SMT Attachment Technique

#### Preparation & Handling of the LM1 Microwave Package for Surface Mounting

The HMC LM1 package was designed to be compatible with high volume surface mount PCB assembly processes. The LM1 package requires a specific mounting pattern to allow proper mechanical attachment and to optimize electrical performance at millimeterwave frequencies. This PCB layout pattern can be found on each LM1 product data sheet. It can also be provided as an electronic drawing upon request from Hittite Sales & Application Engineering.

# Follow these precautions to avoid permanent damage:

Cleanliness: Observe proper handling procedures to ensure clean devices and PCBs. LM1 devices should remain in their original packaging until component placement to ensure no contamination or damage to RF, DC & ground contact areas.

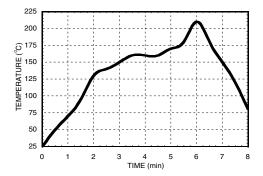

Solder Materials & Temperature Profile: Follow the information contained in the application note. Hand soldering is not recommended. Conductive epoxy attachment is not recommended.

Solder Paste: Solder paste should be selected based on the user's experience and be compatible with the metallization systems used. See the LM1 data sheet Outline drawing for pin & ground contact metallization schemes.

Solder Paste Application: Solder paste is generally applied to the PCB using either a stencil printer or dot placement. The volume of solder paste will be dependent on PCB and component layout and should be controlled to ensure consistent mechanical & electrical performance. Excess solder may create unwanted electrical parasitics at high frequencies.

Solder Reflow: The soldering process is usually accomplished in a reflow oven but may also use a vapor phase process. A solder reflow profile is suggested above.

Prior to reflowing product, temperature profiles should be measured using the same mass as the actual assemblies. The thermocouple should be moved to various positions on the board to account for edge and corner effects and varying component masses. The final profile should be determined by mounting the thermocouple to the PCB at the location of the device.

Follow solder paste and oven vendor's recommendations when developing a solder reflow profile. A standard profile will have a steady ramp up from room temperature to the pre-heat temperature to avoid damage due to thermal shock. Allow enough time between reaching pre-heat temperature and reflow for the solvent in the paste to evaporate and the flux to completely activate. Reflow must then occur prior to the flux being completely driven off. The duration of peak reflow temperature should not exceed 15 seconds. Packages have been qualified to withstand a peak temperature of 235°C for 15 seconds. Verify that the profile will not expose device to temperatures in excess of 235°C.

Cleaning: A water-based flux wash may be used.